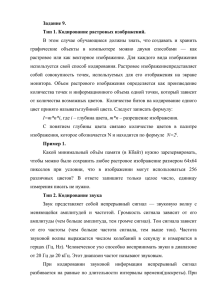

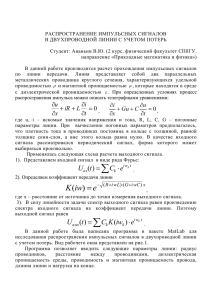

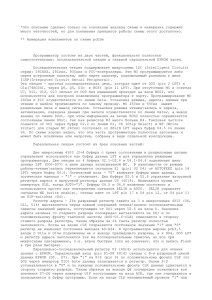

Министерство образования и науки Российской Федерации. ИРКУТСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ Факультет Кибернетики Кафедра Вычислительной техники Наименование кафедры Допускаю к защите Руководитель Э.П. Ланина И.О.Фамилия Проектирование устройства управления и моделирование его работы средствами Multisim Наименование темы ПОЯСНИТЕЛЬНАЯ ЗАПИСКА к курсовому проекту по дисциплине Организация ЭВМ и систем ПЗ обозначение документа Выполнил студент группы ЭВМу-10-1 Ерёмин В.В. шифр подпись Нормоконтролер ФИО Ланина Э.П. подпись Курсовой проект защищен с оценкой Иркутск 2012 г. ФИО ИРКУТСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ЗАДАНИЕ НА КУРСОВОЕ ПРОЕКТИРОВАНИЕ По курсу «Организация ЭВМ и систем» студенту группы ЭВМу-10-1 Ерёмину В.В. Фамилия (инициалы) Тема проекта Проектирование устройства управления и моделирование его работы средствами Multisim Исходные данные: Методические указания проектированию. Вариант №6 Рекомендуемая литература: Букреев И.Н., Уансуров Б.М., Горячев В.И. Микроэлектрон-ные схемы цифровых устройств. -3-е изд., первраб. и доп. - М.: Радио и связь, 1990.- 416 с. по курсовому Справочник по цифровой схемотехнике / В.И.Зубчук, В.П.Сигорский, А.Н. Шкуро. - Киев, Техника, 1990.- 448с. Схемотехника ЭВМ: Учебник для студентов вузов спец.ЭВМ /Под ред. Г.Н.Соловьева. - М.: Высшая школа, 1986.- 391 с. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ: Учеб.пособие для спец.ЭВМ для студентов вузов. -М.: Высшая школа, 1987. - 318 с. Хоуп Г. Проектирование цифровых вычислительных устройств на интегральных микросхемах /Пер. с англ. - М.: Мир, 1984. - 400 с. Графическая часть на ______________ Дата выдачи « 25 » февраля Дата выдачи проекта руководителю « » Руководитель курсового проекта листах 2012 г. 2012 г. Ланина Э.П. Содержание Содержание ............................................................................................................................................. 3 Введение .................................................................................................................................................. 4 1. Постановка задачи .............................................................................................................................. 5 2. Анализ заданных сигналов................................................................................................................. 5 3. Принцип 1 ............................................................................................................................................ 6 3.1 Проектирование схемы устройства управления ........................................................................ 6 3.1.1 Проектирование автомата для получения сигнала A ........................................................ 8 3.1.2 Проектирование автомата для получения сигнала В ........................................................ 9 3.2. Выбор элементов схем, их описания и реализация функций ................................................ 11 3.2.1 Элементы ввода/вывода ..................................................................................................... 11 3.2.2 Логические элементы ......................................................................................................... 12 3.2.3 Счётчик ................................................................................................................................ 12 3.2.4 Сброс .................................................................................................................................... 13 3.3 Реализация функций ................................................................................................................... 14 3.3.1 Реализация функции A ....................................................................................................... 14 3.3.2 Реализация функции B ....................................................................................................... 17 3.4 Разработанная схема ................................................................................................................... 19 4. Принцип 2 .......................................................................................................................................... 22 4.1 Проектирование схемы устройства управления ...................................................................... 22 4.1.1 Проектирование автомата для получения сигнала A ...................................................... 23 4.1.2 Проектирование автомата для получения сигнала В ...................................................... 24 4.2 Выбор элементов схем, их описания и реализация функций ................................................. 25 4.2.1 Элементы ввода/вывода ..................................................................................................... 25 4.2.2 Логические элементы ......................................................................................................... 26 4.2.3 Счётчик ................................................................................................................................ 26 4.2.4 Триггер ................................................................................................................................. 26 4.2.5 Сброс .................................................................................................................................... 26 4.3 Реализация функций ................................................................................................................... 28 4.3.1 Реализация функции A ....................................................................................................... 28 4.3.2 Реализация функции B ....................................................................................................... 30 4.4 Разработанная схема ................................................................................................................... 32 Заключение ............................................................................................................................................ 35 Список использованной литературы .................................................................................................. 36 3 Введение Целью данного курсового проекта является разработка и описание работы устройства управления, вырабатывающего заданную по варианту последовательность выходных сигналов. Необходимо провести анализ заданных последовательностей сигналов, составить функции, описывающие работу устройства, выполнить минимизацию полученных функций, разработать электрическую функциональную схему устройства, и моделировать ее работу в Electronics Workbench. Пакет Electronics Workbench предназначен для моделирования и анализа электротехнических и схемотехнических схем. Данный пакет позволяет моделировать аналоговые, цифровые и цифро-аналоговые схемы большой степени сложности. Имеющиеся в программе библиотеки включают в себя большой набор широко распространенных электронных компонентов. Есть возможность подключения и создания новых библиотек компонентов. Параметры компонентов можно изменять в широком диапазоне значений. Широкий набор приборов позволяет производить измерения различных величин, задавать входные воздействия, строить графики. Все приборы изображаются в виде, максимально приближенном к реальному, поэтому работать с ними просто и удобно. Результаты моделирования можно вывести на принтер или импортировать в текстовый или графический редактор для их дальнейшей обработки. Пакет Electronics Workbench создан компанией National Instruments Electronics Workbench Group, и практически вытеснен программой Multisim той же компании. При разработке данного курсового проекта необходимо применять знания, полученные при изучении следующих предметов: дискретная математика, математическая логика, теория автоматов. 4 1. Постановка задачи Разработать устройство управления, формирующее сигналы на выходах A,B при заданной последовательности импульсов синхронизации CLK, показанных на рисунке 1.1 Рисунок 1.1 Последовательность выходных сигналов 2. Анализ заданных сигналов Имеется входной сигнал CLK, который представляет собой чередование прямоугольных симметричных импульсов одинакового периода. Этот сигнал используется для синхронизации работы всех устройств схемы. Временная диаграмма А (Рисунок 1.1) представлена следующим образом: 3 такта функция А = «1», 2 такта = «0», 4 такта = «1», 2 такта = «0», 5 тактов = «1», 2 такта = «0», 6 тактов = «1», 2 такта = «0». Далее по циклу идет повторение. Рисунок 2.1 Временная диаграмма А Временная диаграмма В (Рисунок 2.2) представлена следующим образом: 5 тактов функция B = «1», 6 тактов = «0», 7 тактов = «1», 8 тактов = «0». Далее по циклу идет повторение. Рисунок 2.2 Временная диаграмма B Мы имеем 8-разрядный счетчик, который считает до 26, а затем производится сброс счетчика. 3. Принцип 1 3.1 Проектирование схемы устройства управления Составим таблицу истинности для проектируемого автомата . Введём обозначения: CLK – тактовый сигнал, Q4, Q3, Q2, Q1, Q0 – выходы счётчика. № такта 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Q4 Q3 Q2 Q1 Q0 CLK Function(A) Function(B) 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 6 17 18 19 20 21 22 23 24 25 26 Сброс 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 1 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 Таблица 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Сброс 7 3.1.1 Проектирование автомата для получения сигнала A Для записи функции, описывающей работу автомата формирующего сигнал A было решено использовать наборы, на которых функция a равна “0”, т.е. запись в виде СКНФ. Запишем СКНФ (Совершенная Конъюнктивная Нормальная Форма) функции a: A (Q 4 vQ 3 vQ 2 vQ1 vQ0 vC lk) & (Q 4 vQ 3 vQ 2 vQ 1 vQ 0 vClk) & (Q 4 vQ 3 vQ 2 vQ 1 vQ 0 vC lk) & (Q 4 vQ 3 vQ 2 vQ 1 vQ0 vClk) & (Q 4 vQ3 vQ 2 vQ 1 vQ0 vC lk) & (Q 4 vQ3 vQ 2 vQ1 vQ 0 vClk) & (Q 4 vQ3 vQ 2 vQ1 vQ 0 vC lk) & (Q 4 vQ3 vQ 2 vQ1 vQ0 vClk) & (Q 4 vQ 3 vQ 2 vQ 1 vQ 0 vC lk) & (Q 4 vQ 3 vQ 2 vQ 1 vQ0 vClk) & (Q4 vQ 3 vQ 2 vQ 1 vQ0 vC lk) & (Q 4 vQ 3 vQ 2 vQ1 vQ 0 vClk) & (Q 4 vQ3 vQ 2 vQ 1 vQ 0 vC lk) & (Q 4 vQ3 vQ 2 vQ 1 vQ0 vClk) & (Q4 vQ3 vQ 2 vQ 1 vQ0 vC lk) & (Q 4 vQ3 vQ 2 vQ1 vQ 0 vClk) Q1 Q0 CLK Q1 Q0 CLK Проведём минимизацию полученной СКНФ, то есть запишем минимальную КНФ функции А, для этого применим метод Карты Карно (Рисунок 3.4.1): Q4 Q3 Q2 Q4 Q3 Q2 000 001 011 010 100 101 111 110 000 - 0 1 1 1 1 - 1 001 1 0 1 1 0 1 - 0 011 1 1 1 0 0 1 - 0 010 1 0 1 1 0 1 - 0 100 1 1 1 0 0 1 - 0 101 1 1 1 0 1 1 - - 111 0 1 1 1 1 1 - - 110 1 1 1 0 1 1 - - Рисунок 3.1.1.1 Карты Карно В результате минимизации СКНФ была получена следующая формула для функции А: A (Q 4 vQ 3 vQ2 vQ1vClk) & (Q3 vQ 2 vQ1vQ0 vC lk) & (Q3 vQ 2 vQ1vClk) & (Q 4 vQ 3 vQ2 vQ1vQ 0 ) & (Q4 vQ 2 vQ1vQ0 ) & (Q 4 vQ 3 vQ 2 vQ1vQ0 vC lk) & (Q4 vQ 2 vQ1vC lk) & (Q4 vQ 2 vQ1vQ 0 vClk) & (Q3 vQ 2 vQ1vQ 0 ) Для функции “Сброс” требуется получить значение “1” на последнем наборе переменных в таблице 1. Запишем полученное выражение: F (Q 4 vQ 3 vQ2 vQ 1vQ0 vClk) 8 3.1.2 Проектирование автомата для получения сигнала В Для записи функции, описывающей работу автомата формирующего сигнал В было решено использовать наборы, на которых функция a равна “1”, т.е. запись в виде СДНФ. Запишем СДНФ (Совершенная Дизъюнктивная Нормальная Форма) функции B. b (Q4 & Q3 & Q2 & Q1 & Q0 & Clk) v( Q4 & Q3 & Q2 & Q1 & Q 0 & C lk) v (Q4 & Q3 & Q2 & Q1 & Q 0 & Clk) v( Q4 & Q3 & Q2 & Q1 & Q0 & C lk) v( Q4 & Q3 & Q2 & Q1 & Q0 & Clk) v (Q4 & Q3 & Q2 & Q1 & Q 0 & C lk) v( Q4 & Q3 & Q2 & Q1 & Q 0 & Clk) v( Q4 & Q3 & Q 2 & Q1 & Q0 & C lk) v (Q4 & Q3 & Q 2 & Q1 & Q0 & Clk) v( Q4 & Q3 & Q 2 & Q1 & Q 0 & C lk) v( Q4 & Q 3 & Q2 & Q1 & Q 0 & Clk) v (Q4 & Q 3 & Q 2 & Q1 & Q0 & C lk) v( Q4 & Q 3 & Q 2 & Q1 & Q0 & Clk) v( Q4 & Q 3 & Q 2 & Q1 & Q 0 & C lk) v (Q4 & Q 3 & Q 2 & Q1 & Q 0 & Clk) v( Q4 & Q 3 & Q 2 & Q1 & Q0 & C lk) v( Q4 & Q 3 & Q 2 & Q1 & Q0 & Clk) v (Q4 & Q 3 & Q 2 & Q1 & Q 0 & C lk) v( Q4 & Q 3 & Q 2 & Q1 & Q 0 & Clk) v(Q 4 & Q3 & Q2 & Q1 & Q0 & C lk) v (Q4 & Q 3 & Q 2 & Q1 & Q 0 & C lk) v(Q 4 & Q3 & Q2 & Q1 & Q 0 & C lk) v(Q 4 & Q3 & Q2 & Q1 & Q 0 & Clk) v (Q 4 & Q3 & Q2 & Q1 & Q0 & C lk) Q1 Q0 CLK Q1 Q0 CLK Проведём минимизацию полученной СДНФ, то есть запишем минимальную ДНФ функции В, для этого применим метод Карты Карно (Рисунок 2): Q4 Q3 Q2 Q4 Q3 Q2 000 001 011 010 100 101 111 110 000 - 1 1 0 1 0 - 0 001 1 1 1 0 1 0 - 0 011 1 0 1 0 1 0 - 0 010 1 1 1 0 1 0 - 0 100 1 0 1 0 1 0 - 0 101 1 0 1 0 0 0 - - 111 1 0 1 1 0 0 - - 110 1 0 1 0 0 0 - - Рисунок 3.1.2.1 Карты Карно 9 В результате минимизации СДНФ была получена следующая формула для функции А: B (Q 4 & Q 2 & Q1 & C lk) v (Q3 & Q 2 & Q1 ) v( Q3 & Q 2 & Q0 & C lk) v( Q 4 & Q 2 & Q1 & Q0 ) v (Q 3 & Q 2 ) v(Q 3 & Q1 & Q 0 & Clk) v( Q 4 & Q3 & Q 2 ) Для функции “Сброс” требуется получить значение “1” на последнем наборе переменных в таблице 1. Запишем полученное выражение: F (Q 4 vQ 3 vQ2 vQ 1vQ0 vClk) 10 3.2. Выбор элементов схем, их описания и реализация функций Для реализации устройства управления потребуются: генератор слов, логические элементы (И, ИЛИ, НЕ), пара четырёхразрядных счётчиков и логический анализатор. Ниже приведены описания этих элементов. 3.2.1 Элементы ввода/вывода Генератор слов (Word Generator) Внешний вид генератора слов показан на рисунке 3.2.1.1 Рисунок 3.2.1.1 Генератор слов Используется для генерации последовательности тактовых сигналов. А также имеется возможность запрограммировать свою собственную последовательность тактовых сигналов. Для проектирования схемы будет использоваться только тактовый выход, который показан на изображении. Логический анализатор (Logic Analyzer) Внешний вид логического анализатора показан на рисунке 3.2.1.2 Рисунок 3.2.1.2 Логический анализатор Используется для вывода последовательностей сигналов работы. 11 3.2.2 Логические элементы Элемент Схема И ИЛИ НЕ Таблица истинности A | B | Y ----------------0 | 0 | 0 0 | 1 | 0 1 | 0 | 0 1 | 1 | 1 A | B | Y ----------------0 | 0 | 0 0 | 1 | 1 1 | 0 | 1 1 | 1 | 1 A | Y ----------0 | 1 1 | 0 Описание A, B - сигналы на входе; Y - сигнал на выходе. Если на входе все “1”, то на выходе “1”, иначе на выходе “0”. A, B - сигналы на входе; Y - сигнал на выходе. Если на входе все “0”, то на выходе “0”, иначе на выходе “1”. A - сигнал на входе; Y - сигнал на выходе. Если на входе “0”, то на выходе “1”. Если на входе “1”, то на выходе “0”. 3.2.3 Счётчик Схема Таблица истинности Сброс | Выходы ----------------------------------RO1 RO2 | D C B A ----------------------------------1 1 | 0 0 0 0 0 X | Счёт X 0 | Счёт Описание 4х разрядный счётчик. A, B, C, D – выходы. CLKA – синхровход. CLKB – счётный вход. R01, R02 – входы установки нуля. 12 3.2.4 Сброс Рисунок 3.2.4.1 Cхема сброса Получая сигналы CLK счетчик считает. Когда счетчик доходит до 26, функция F=1. Она подается на R01, R02 .( Для обнуления счетчика) 13 3.3 Реализация функций 3.3.1 Реализация функции A a (Q 4 vQ 3 vQ2 vQ1vClk) & (Q3 vQ 2 vQ1vQ0 vC lk) & (Q3 vQ 2 vQ1vClk) & (Q 4 vQ 3 vQ2 vQ1vQ 0 ) & (Q4 vQ 2 vQ1vQ0 ) & (Q 4 vQ 3 vQ 2 vQ1vQ0 vC lk) & (Q4 vQ 2 vQ1vC lk) & (Q4 vQ 2 vQ1vQ 0 vClk) & (Q3 vQ 2 vQ1vQ 0 ) (Q 4 vQ 3 vQ2 vQ1vClk) (Q3 vQ 2 vQ1vQ0 vC l k) (Q3 vQ 2 vQ1vClk) (Q 4 vQ 3 vQ2 vQ1vQ 0 ) (Q4 vQ2 vQ1vQ0 ) (Q4 vQ3 vQ2 vQ1vQ0 vC lk) (Q4 vQ 2 vQ1vC lk) (Q4 vQ 2 vQ1vQ 0 vClk) (Q3 vQ 2 vQ1vQ 0 ) 14 Сброс (Q4 vQ3vQ2 vQ1vQ0 vClk) Для построения схемы нужны следующие элементы: 3 элемента И, 9 элементов ИЛИ, 20 элементов НЕ, счётчик (будут использованы 5 разрядов). 15 Рисунок 3.3.1.1 Реализация функции A 16 3.3.2 Реализация функции B b (Q4 & Q 2 & Q1 & C lk) v (Q3 & Q2 & Q1 ) v( Q3 & Q2 & Q0 & C lk) v( Q4 & Q 2 & Q1 & Q0 ) v (Q 3 & Q 2 ) v(Q 3 & Q1 & Q0 & Clk) v( Q4 & Q3 & Q2 ) (Q4 & Q2 & Q1 & C lk) (Q3 & Q2 & Q1 ) (Q3 & Q2 & Q0 & C lk) (Q4 & Q 2 & Q1 & Q0 ) (Q3 & Q2 ) (Q3 & Q1 & Q0 & Clk) (Q4 & Q3 & Q2 ) Сброс (Q 4 vQ 3 vQ2 vQ1vQ0 vClk) 17 Для построения схемы нужны следующие элементы: 8 элементов И, 1 элемента ИЛИ, 18 элемента НЕ, счётчик (будут использованы 5 разрядов). Рисунок 3.3.2.1 Реализация функции B 18 3.4 Разработанная схема В результате проектирования и выбора элементов была получена схема, разработанная в системе Electronics Workbench. Рисунок 3.4.1 Разработанная схема 19 Сигнал А. Сигнал В. 20 Общий вид. 21 4. Принцип 2 4.1 Проектирование схемы устройства управления Составим таблицу истинности для проектируемого автомата . Введём обозначения: CLK – тактовый сигнал, Q3, Q2, Q1, Q0 – выходы счётчика. № такта 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 Q3 Q2 Q1 Q0 CLK Function(A) Function(B) 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 Таблица 2 22 4.1.1 Проектирование автомата для получения сигнала A Для получения такого сигнала потребуется: -Триггер, который будет хранить значение 1 или 0 заданное число тактов. Далее требуется счетчик, который будет считать импульс CLK по подъему до 26(необходимо два четырехбитных счетчика). После этого счетчик сбросится, и триггер устанавливается в противоположное положение. Полный цикл сигнала A выполняется за 26 полных тактов CLK. Представим число 26 в двоичной системе счисления: 11010. Нужна логическая функция F для сброса счетчика, которая бы принимала значение 1, если Clk = 0, Q0 = 1, Q1 = 0, Q2 = 1, Q3 = 1, и значение 0 во всех остальных случаях. Запишем полученное выражение: F (Q3 & Q 2 & Q1 & Q0 & C lk) - функция для сброса счётчика. Запишем СДНФ (Совершенная Дизъюнктивная Нормальная Форма) функции B. A (Q3 & Q2 & Q1 & Q 0 & Clk) v( Q3 & Q2 & Q1 & Q0 & Clk) v (Q3 & Q 2 & Q1 & Q0 & Clk) v( Q3 & Q 2 & Q1 & Q 0 & Clk) v(Q 3 & Q2 & Q1 & Q0 & C lk) v (Q 3 & Q2 & Q1 & Q 0 & C lk) v(Q 3 & Q 2 & Q1 & Q0 & C lk) v(Q 3 & Q 2 & Q1 & Q 0 & C lk) Полученную функцию A подаем на триггер, на синхронизированный вход. На вход D подаем данные с выхода Q . Это нужно для переключения триггера в противоположное состояние Итак, для получения необходимого сигнала потребуется: -Создать блоки для подачи сигнала “1” на элемент “OR1” на 3, 9, 16, 24 тактах сигнала CLK. -Создать блоки для подачи сигнала “1” на элемент “OR2” на 5, 11, 18, 26 тактах сигнала CLK. - Далее требуется счетчик, который будет считать импульсы CLK по спаду до 26. После этого счетчик сбрасывается. Одна микросхема имеет четыре разряда. Нам же необходимо пять. Следовательно, мы имеем две четырёхразрядные микросхемы, образующие счётчик, который считает до 26, а затем производится сброс счетчика и установка триггера в “1”. 23 4.1.2 Проектирование автомата для получения сигнала В ___ ___ F Q0& Q1& Q2& Q3& Q4 - также является функцией для сброса счётчика. Для получения такого сигнала потребуется: -Триггер, который будет хранить значение 1 или 0 заданное число тактов. Далее требуется счетчик, который будет считать импульс CLK по подъему до 26(необходимо два четырехбитных счетчика). После этого счетчик сбросится, и триггер устанавливается в противоположное положение. Запишем СДНФ (Совершенная Дизъюнктивная Нормальная Форма) функции B. В (Q3 & Q2 & Q1 & Q0 & Clk) v( Q3 & Q 2 & Q1 & Q 0 & Clk) v (Q 3 & Q2 & Q1 & Q 0 & C lk) v(Q 3 & Q 2 & Q1 & Q 0 & C lk) Триггер работает потому же принципу что и в случае сигнала А. Полный цикл сигнала B также выполняется за 26 полных тактов CLK. Таким образом F (Q 3 & Q 2 & Q1 & Q0 & C lk) - также является функцией для сброса счётчика. Итак, для получения необходимого сигнала потребуется: -Создать блоки для подачи сигнала “1” на элемент “OR3” на 5, 18 тактах сигнала CLK. -Создать блоки для подачи сигнала “1” на элемент “OR4” на 11, 26 тактах сигнала CLK. - Далее требуется счетчик, который будет считать импульсы CLK по спаду до 26. После этого счетчик сбрасывается. Используем счётчик, аналогичный счётчику сигнала “A”. 24 4.2 Выбор элементов схем, их описания и реализация функций Для реализации устройства управления потребуются: генератор слов, логические элементы (И, ИЛИ, НЕ), пара четырёхразрядных счётчиков и логический анализатор. Ниже приведены описания этих элементов. 4.2.1 Элементы ввода/вывода Генератор слов (Word Generator) Внешний вид генератора слов показан на рисунке 4.2.1.1 Рисунок 4.2.1.1 Генератор слов Используется для генерации последовательности тактовых сигналов. А также имеется возможность запрограммировать свою собственную последовательность тактовых сигналов. Для проектирования схемы будет использоваться только тактовый выход, который показан на изображении. Логический анализатор (Logic Analyzer) Внешний вид логического анализатора показан на рисунке 4.2.1.2 Рисунок 4.2.1.2 Логический анализатор Используется для вывода последовательностей сигналов работы. 25 4.2.2 Логические элементы Элемент Схема И ИЛИ НЕ Таблица истинности A | B | Y ----------------0 | 0 | 0 0 | 1 | 0 1 | 0 | 0 1 | 1 | 1 A | B | Y ----------------0 | 0 | 0 0 | 1 | 1 1 | 0 | 1 1 | 1 | 1 A | Y ----------0 | 1 1 | 0 Описание A, B - сигналы на входе; Y - сигнал на выходе. Если на входе все “1”, то на выходе “1”, иначе на выходе “0”. A, B - сигналы на входе; Y - сигнал на выходе. Если на входе все “0”, то на выходе “0”, иначе на выходе “1”. A - сигнал на входе; Y - сигнал на выходе. Если на входе “0”, то на выходе “1”. Если на входе “1”, то на выходе “0”. 4.2.3 Счётчик Схема Таблица истинности Сброс | Выходы ----------------------------------RO1 RO2 | D C B A ----------------------------------1 1 | 0 0 0 0 0 X | Счёт X 0 | Счёт Описание 4х разрядный счётчик. A, B, C, D – выходы. CLKA – синхровход. CLKB – счётный вход. R01, R02 – входы установки нуля. 4.2.4 Триггер Схема Таблица истинности Описание Изначально триггер установлен в 0. Поэтому на выход A c самого начала подается сигнал Q . 4.2.5 Сброс 26 Рисунок 4.2.5.1 Cхема сброса Получая сигналы CLK счетчик считает. Когда счетчик доходит до 26, функция F=1. Она подается на R01, R02 .( Для обнуления счетчика) 27 4.3 Реализация функций 4.3.1 Реализация функции A A (Q3 & Q2 & Q1 & Q 0 & Clk) v( Q3 & Q2 & Q1 & Q0 & Clk) v (Q3 & Q 2 & Q1 & Q0 & Clk) v( Q3 & Q 2 & Q1 & Q 0 & Clk) v(Q 3 & Q2 & Q1 & Q0 & C lk) v (Q 3 & Q2 & Q1 & Q 0 & C lk) v(Q 3 & Q 2 & Q1 & Q0 & C lk) v(Q 3 & Q 2 & Q1 & Q 0 & C lk) (Q3 & Q2 & Q1 & Q 0 & Clk) (Q3 & Q2 & Q1 & Q0 & Clk) (Q3 & Q 2 & Q1 & Q0 & Clk) (Q3 & Q 2 & Q1 & Q 0 & Clk) (Q 3 & Q2 & Q1 & Q0 & C lk) (Q 3 & Q2 & Q1 & Q 0 & C lk) (Q 3 & Q 2 & Q1 & Q0 & C lk) (Q 3 & Q 2 & Q1 & Q 0 & C lk) Сброс (Q 3 & Q 2 & Q1 & Q0 & C lk) 28 Для построения схемы нужны следующие элементы: 9 элементов И, 1 элементов ИЛИ, 29 элементов НЕ, счётчик (будут использованы 5 разрядов). Рисунок 4.3.1.1 Реализация функции A 29 4.3.2 Реализация функции B В (Q3 & Q2 & Q1 & Q0 & Clk) v( Q3 & Q 2 & Q1 & Q 0 & Clk) v (Q 3 & Q2 & Q1 & Q 0 & C lk) v(Q 3 & Q 2 & Q1 & Q 0 & C lk) (Q3 & Q2 & Q1 & Q0 & Clk) (Q3 & Q 2 & Q1 & Q 0 & Clk) (Q 3 & Q2 & Q1 & Q 0 & C lk) (Q 3 & Q 2 & Q1 & Q 0 & C lk) Сброс (Q 3 & Q 2 & Q1 & Q0 & C lk) Для построения схемы нужны следующие элементы: 5 элементов И, 1 элемента ИЛИ, 16 элемента НЕ, счётчик (будут использованы 5 разрядов). 30 Рисунок 4.3.2.1 Реализация функции B 31 4.4 Разработанная схема В результате проектирования и выбора элементов была получена схема, разработанная в системе Electronics Workbench. Рисунок 4.4.1 Разработанная схема 32 Сигнал А. Сигнал В. 33 Общий вид. 34 Заключение В процессе выполнения данного курсового проекта были получены уравнения заданных функций, проведена минимизация, рассмотрены элементы для разработки схем и разработано устройство управления. Для разработки был использован программный продукт Electronics WorkBench позволяющий разрабатывать цифровые схемы и моделировать их работу. Результат моделирования показывает, что разработанное устройство управления выдаёт правильную последовательность сигналов. 35 Список использованной литературы 1. Кирий В.Г. Теория автоматов. Конспект лекций. Изд. ИрГТУ 2002. 97с. 2. Методические указания по работе с системой моделирования ElectronicsWorkBench 3. Справочник по интегральным микросхемам / Б.В.Тарабрин, С.В.Якубовский, Н.А.Баранов и др. Под ред.Б.В.ТараОрина. - М.: Энергия, 1981.- 816 с. 4. Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. - Челябинск: Металлургия, 1989.- 325 с.(Массовая библиотека. ВыпЛШ). 5. Шило В.Л. Популярные микросхемы КМОП. Справочник. - И.: Издательство "Ягуар". 1993,- 64 с. 6. Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др.; Под ред. С.В.Якубовского. - М.: Радио и связь, 1990.- 496 с. 7. Пухальский Г.И., Новосельцева Г.Я Проектирование дискретных устройств на интегральных микросхемах: Справочник. - м.: Радио и связь, 1990.- 304 с. 8. Бедрековский М.А., Косырбасов А.А., Мальцев П.П. Интегральные микросхемы. - М.: Энергодтомиэдат, 1991. - 272 с. 9. Усатенко СТ., Качения Т.К., Терехова М.В. Выполнение электрически: схем по ЕСКД: Справочник. - 2-е изд., перэраб. и доп. - М.: Издательставо стандартов, 1992.- 316 с. 10. Преснухин Л.Н., Воробьев Я.В.„ Шишкевич А.А. Расчет элементов цифровых устройств: Учеб. пособив / Под ред. Л.Н. Прес-Еухша.- 2-е изд.,перераб. и доп. - М.: Высшая школа, 1991. - 526 с. 36