Лабораторная работа №1 Знакомство с Verilog и симулятором Modelsim

реклама

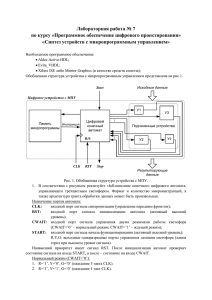

Лабораторная работа №1 Знакомство с Verilog и симулятором Modelsim Цель работы: получение базовых знаний о структуре программы на Verilog, отладка программы с помощью симулятора. Содержание: Краткие теоретические сведения ............................................................................................................... 1 Простейшая программа на Verilog ......................................................................................................... 1 Основные элементы интерфейса ModelSim .......................................................................................... 2 Создание нового проекта .................................................................................................................... 2 Добавление файлов к проекту ............................................................................................................ 3 Открытие существующих проектов ................................................................................................... 4 Компиляция программы ...................................................................................................................... 5 Моделирование работы программы ................................................................................................... 7 Задание для выполнения ........................................................................................................................... 12 Контрольные вопросы ............................................................................................................................... 13 Требования к оформлению отчета ........................................................................................................... 14 Литература. ................................................................................................................................................. 14 Краткие теоретические сведения ModelSim — это система HDL-моделирования цифровых устройств Одна из характерных тенденций современного этапа развития технологии проектирования цифровых систем — применение языков описания аппаратуры HDL (Hardware Description Language) высокого уровня, среди которых наибольшее распространение получили VHDL и Verilog. При этом не только возрастает роль средств моделирования в процессе разработки устройств, но и меняются методы и требования, предъявляемые к процедурам верификации. Для своевременного обнаружения возможных ошибок средства моделирования должны обеспечивать возможность контроля результатов каждого этапа процесса проектирования: создания исходных HDL-описаний, синтеза, размещения и трассировки в кристалл. Такой подход обеспечивает минимальное время разработки устройства и сокращает стоимость этого процесса, так как цена ошибки возрастает с каждым последующим шагом проектирования. Пакет программных средств ModelSim™ корпорации Model Technology (одного из подразделений компании Mentor Graphics) в настоящее время является самой распространенной системой HDL-моделирования. Простейшая программа на Verilog Показанная простейшая программа состоит из ключевых слов module и endmodule, означающих начало и конец блока языка Verilog. top – имя рассматриваемого модуля. С помощью утверждения инициализации, определяемого ключевым словом initial , задаются те инструкции, которые будут выполнены один раз перед началом моделирования работы программы. Системное задание $display позволяет вывести на экран сообщение «Hello world!». module top; initial $display("Hello world!"); endmodule Основные элементы интерфейса ModelSim Создание нового проекта Для создания проекта необходимо открыть программу и выбрать File→New→Project. Откроется окно диалога создания проекта. Заполняем необходимые поля: Имя проекта (Project Name), Путь к проекту (Project Location), Название библиотеки, в которую будут компилироваться объекты проекта (Default Library Name). Для всех задач из курса лабораторных работ досточно пользоваться именем по умолчанию – work. После заполнения этих полей нажимаем кнопку ОК. Добавление файлов к проекту После создания нового проекта появится диалоговое окно, которое позволяет добавить файлы к проекту. Возможны следующие варианты добавляемых файлов: Создать новый файл и добавить его в текущий проект (Create New File), Добавить существующий файл в проект (Add Existing File), Выполнить моделирование библиотечного элемента (Create Simulation). Если требуется добавить новый файл к проекту, то в появившемся диалогов окне ввести имя фала (File Name) и отметить тип этого файла (Add file as type). В итоге всех манипуляций мы должны увидеть окно под названием Project с нашим файлом внутри: Это окно является аналогом менеджера проекта, из него можно управлять файлами проекта и их компиляцией. В нем виден тип файла и его статус, который указывает на то, что есть ошибки при компиляции, либо их отсутствие или то, что файл изменен и не скомпилирован. Для редактирования файлов проекта надо два раза щелкнуть на имени файла в окне Project, после чего откроется окно Source, в котором можно редактировать файл. Открытие существующих проектов Для открытия уже существующего проекта надо выбрать File→Open В открывшемся диалоговом окне в поле Files of type выбрать Project files и из списка имеющихся файлов проекта выбрать нужный. Компиляция программы Перед компиляцией следует сохранить файл (File→Save или просто Ctrl+S). Для компиляции какого-то конкретного файла проекта нажимаем правой кнопкой на имени фала, после чего в контекстном меня выбираем Compile→Compile selected. Для компиляции всех файлов проекта используем меня Compile→Compile All. Сразу изменится статус нашего файла и в окне Transcript появиться сообщение об ошибках (если они есть). Для того, чтобы найти и исправить ошибку щелкаем два раза на сообщении об ошибке. Увидим окно с описанием и местом ошибки. Щелкаем по описанию ошибки два раза. Подсветится место ошибки в окне Source. Судя по описанию ошибки, имеется синтаксическая ошибка. Исправляем, сохраняем файл и компилируем еще раз. Получаем сообщение зеленым цветом в окне Transcript, компиляция выполнена успешно. Моделирование работы программы Моделирование работы программы можно запустить несколькими путями. Меню Simulation→Start Simulation откроет окно Start Simulation. В открывшемся окне, в закладке Design надо выбрать то название библиотеки, в которую скомпилировались объекты проекта (определяется при создании проекта, обычно work) и в раскрывшемся выпадающем списке выбрать имя модуля, моделирование которого мы хотим провести (в нашем примере top). Нажимаем кнопку ОК. Рядом с закладкой Project открывается закладка sim. Нажимаем меню Simulation→Run→Run-All для того, чтобы запустить моделирование на выполнение. Результат выполнения в случае нашего примера мы видим в окне Transcript. В нашем случае это будет печать слов «Hello word!». В общем случае, в зависимости от настроек, могут быть видны различные окна. Их расположение можно сохранять и сбрасывать при помощи меню Layout. Все окна можно включить и выключить через меню View. Наибольший интерес представляют следующие окна: Wave — окно построения временных диаграмм Structure — окно структуры проекта, показывает иерархию проекта, при выборе любой структуры в остальных окнах будут отображаться ее данные Objects — окно сигналов, здесь отображаются сигналы выбранного объекта проекта Processes — показывает существующие процессы и их статус Dataflow — структура процессов, отображает схему протекания данных В ModelSim поддерживается Drag and Drop, поэтому можно перетаскивать элементы из одного окна в другое. Рассмотрим работу с этими окнами на примере более сложного проекта. Начнем моделирование так же, как и в предыдущем примере. Для ускорения моделирования симулятор применяет оптимизацию, которая может изменять внутреннюю структуру модуля. Чтобы увидеть внутренние сигналы модулей откроем окно Optimization options… и выберем опцию Apply full visibility to all modules (full debug mode) в закладке Visibility. После нажатия ОК появятся окна, в которых можно будет увидеть значения сигналов в процессе симуляции (окно Objects). Временные диаграммы изменения сигналов можно увидеть в окне Wave. Для этого надо «перетянуть» название сигналов, которые вы хотите увидеть, в окно Wave. Непосредственно моделирование, Simulation→Run→Run-All. как вы уже знаете, начинается выбором опций Остановить моделирование можно либо нажав кнопку Break либо выбрав меню Simulation→ Break. Текущее значение сигналов можно увидеть в окне Objects. Чтобы увидеть временные диаграммы для всего времени моделирования, используется кнопка Zoom Full. Для того, чтобы увидеть значения сигналов в какой-то определенный промежуток времени используют кнопку Zoom Mode и выбирают необходимый временной диапазон в окне Wave с помощью мыши. Результат выполнения такого масштабирования виден ниже. Завершить режим моделирования можно выбрав меню Simulation→ End Simulation. Задание для выполнения 1. Создать проект в среде Modelsim. 2. Добавить в созданный проект файл со следующей программой и испытательного стенда к ней: `timescale 1ns/100ps module dff(clk, din, dout); input clk, din; output dout; reg dout; always @ (posedge clk) begin dout <= din; end endmodule module dffr(clk, din, rst_n, dout); input clk, din, rst_n; output dout; reg dout; always @ (posedge clk, negedge rst_n) begin if ( !rst_n ) dout <= #6 0; else dout <= #6 din; end endmodule module top; reg clk; reg in_inf; reg rst_n; wire out_inf; //dff D1 (clk, in_inf, out_inf); dffr D2 (clk, in_inf, rst_n, out_inf); initial begin: INIT clk = 0; in_inf = 0; rst_n = 1; end //INIT always begin: GEN1 clk = #15 ~clk; end //GEN1 always begin: GEN2 in_inf = #23 ~in_inf; end //GEN1 always begin: GEN3 if (0 == rst_n) rst_n = #3 ~rst_n; else rst_n = #40 ~rst_n; end //GEN1 endmodule 3. Скомпилировать программу и испытательный стенд к ней. 4. Запустить моделирование программы и испытательного стенда. 5. Продемонстрировать временные диаграммы работы испытательного стенда. Контрольные вопросы 1. В чем состоит сходство между языками программирования и языками описания аппаратуры? 2. В чем состоит принципиальное различие между языками программирования и языками описания аппаратуры? 3. Какие языки описания аппаратуры вы знаете? 4. Какие из них получили наибольшее распространение в современной инженерной практике? 5. Какие возможности по моделирования предоставляет среда Modelsim? Требования к оформлению отчета Эта лабораторная работа не требует оформления протокола. Для получения оценки достаточно продемонстрировать следующие умения: 1. Создать проект. 2. Скомпилировать имеющуюся программу и испытательный стенд к ней. 3. Уметь запустить моделирование имеющейся программы и испытательного стенда к ней. 4. Уметь посмотреть текущее состояние сигналов и их временные диаграммы. Литература. 1. http://model.com/