Осинин И. П. Князьков В. С

advertisement

Федеральное государственное бюджетное

образовательное учреждение

высшего профессионального образования

«Вятский государственный университет»

ВЯТСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

«Роль ВятГУ в развитии

биотехнологии

Кировской области»

Пименов Евгений Васильевич

II Международная конференция

биотехнологов «Международное

сотрудничество и развитие

биотехнологий в Кировской

области»

Министерство

образования и науки

Российской Федерации

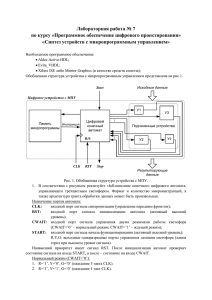

АРИФМЕТИЧЕСКИЙ ПЛИС-УСКОРИТЕЛЬ

С РЕКОНФИГУРИРУЕМОЙ

МИКРОАРХИТЕКТУРОЙ

аспирант Осинин Илья Петрович,

д.т.н., профессор Князьков Владимир Сергеевич

ФГБОУ ВПО «Вятский государственный

университет»

Концепция, способы и особенности

выполнения арифметических

операций в однородном модулярносистолическом процессоре

- Реконфигурируемость микроархитектуры операционной части процессора за счет

динамической настройки вычислительных ядер на выполнение требуемого набора

арифметико-логических операций: сложение, вычитание, умножение, деление и так далее;

- все арифметические операции реализуются с использованием конвейерной техники

вычислений;

- скорость выполнения всех операций обеспечена на частоте базового элемента;

- обеспечена поддержка вычислений в форматах данных 32,- 64,- 128- разрядными числами

с фиксированной запятой за счет обеспечения возможности динамического

конфигурирования операционной части – разбиения среды на независимые процессорные

ядра, причем, «влет»: а) одного 128- разрядного ядра процессора; б) двух 64- разрядных

процессорных ядер; в) четырех 32- разрядных процессорных ядер;

- за счет реконфигурации микроархитектуры однородной вычислительной среды

процессорных ядер обеспечиваются также и выполнение всех арифметических операции в

традиционной позиционной системе счисления;

- обеспечиваются аппаратные преобразования кодов чисел из ППС в СОК и наоборот со

скоростью работы ядер процессора.

ОД.DO

Ядро 2

ОР.DI

40

ОР.DI

Преобразователь

кодов

(конфигурация

2 ядра)

40

40

40

ОД.DO

RgDI3 RgDO3 RgDI1 RgDO1

RgDO1 RgDI1

Преобразователь

кодов

(конфигурация

4 ядра)

RgDI1 RgDO1

40

RgDO0 RgDI0

ОР.DI

ОД.DO

Ядро 3

40

RgDI2 RgDO2 RgDI0 RgDO0

40

Преобразователь

кодов

(конфигурация

2 ядра)

RgDI0 RgDO0

40

ОР.DI

Ядро 1

ОД.DO

Схема структурная процессора

Ядро 4

Системная шина

Арбитр системной

шины

Буфер

FIFO

ОЗУ

Системные УВВ

Процессор состоит их четырех ядер, каждое из которых ведет

параллельную обработку информации в базисе модулярной

арифметики по пяти основаниям.

Поддерживаются вычисления с форматами

данных 32,- 64,- 128- разрядными числами с

фиксированной запятой за счет обеспечения

возможности динамического конфигурирования

операционной части:

а) одного 128- разрядного ядра процессора;

Ядро 1

Ядро 2

Ядро 3

Ядро 4

б) двух 64- разрядных процессорных ядер;

Ядро 1

Ядро 2

Ядро 3

Ядро 4

в) четырех 32- разрядных процессорных ядер.

Ядро 1

Ядро 2

Ядро 3

Ядро 4

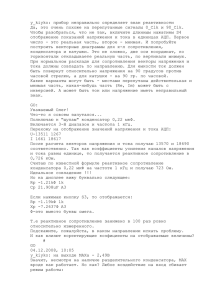

Схема структурная ядра процессора

RgА

0

ШУ2

16 15

P

15

RgDO

RgDO0

RgDI 0

0

320

39

39

RgDO

0

16

P

ШУ3

ШУ1

0

Y

P

P

P

0

ОР

39

RgDI2

P

0

40

Y

15

P

ШУ2

УУТС

ОМК

УУПС

Y

RgDO

ОУ

Y

63

63

40

RgDI10 39RgDI00

ОД2

0

ОК

RgDI

63

Системная шина

RgDO 0

RgDI

320

ШУ1

64

40

39

ОД1

Y

32

RgDO0

RgDI

0

A0

320

39

A2

0 31

КЭШД

порт чт Б

P

Y

0

RgDI320

DO0

КЭШД

порт чт А

Y

УУВС

IRQ

ШУ1

39

31

32

КЭШД

порт зп

RgDO1

БФФА

0 31

0

DO1 0 31DO0 0

DO3

32

31

DI0 0

31

DI1

31

48

0

32

0 31

32

RgDI

31

31

32

A1

ОАР

INT

ШУ2

P

RgDO0

Y

P

Y

Y

ШУ2

0

Y

31

ШУ1

АП

15

RgDI

0

16

КЭШ память процессора поддерживает режим 96- кратного расслоения памяти.

Поддерживается режим параллельной работы КЭШ памяти с четырьмя потоками

данных.

Поддерживается триальный режим работы КЭШ памяти с динамическим

переключением банков.

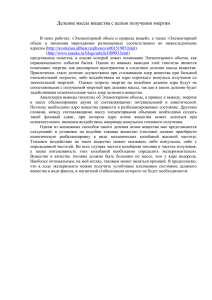

Схема структурная вычислительного

ядра

a1

b1

a2

b2

an

bn

Входная ТП осн. p1

Входная ТП осн. p1

ОВС

Входная ТП осн. p2

Входная ТП осн. p2

ОВС

.

.

.

.

.

.

Входная ТП осн. pn

Входная ТП осн. pn

ОВС

Выходная ТП

основания p1

d1

Выходная ТП

основания p2

.

.

.

d2

Выходная ТП

основания pn

dn

Реконфигурируемость микроархитектуры операционного

устройства обеспечивает динамическую настройку

вычислительных ядер на выполнение арифметико-логических

операций: сложение, вычитание, умножение, деление нацело

и т.д.

Пример реализации операции

вычитания по модулю 5

1 x Входная a1 1 a1

1 x1

a2 1 a2

ТП

2

0 x

0a

3 остатка X a3

3

a1 1

b1 0

clk

a2 1

b2 0

clk

a3 0

b3 1

clk

a4 0

b4 0

D

Cвх

S

БЭ Cвых

1

0

D

0 Cвх БЭ

clk Clk

Clk

D

Cвх

S

БЭ Cвых

1

0

D

Cвх

clk Clk

Clk

D

Cвх

S

БЭ Cвых

1

0

D

Cвх

clk Clk

Clk

D

Cвх

S

БЭ Cвых

1 y Входная b 0 b

1

1

0 y1

b2 0 b2

ТП

2

0

y3 остатка Y b3 1 b3

0

0

D

Cвх

clk Clk

Clk

1

1

1

0

S

Cвых

S

БЭ Cвых

S

БЭ

Cвых

S

БЭ Cвых

1

0

0

clk

1

0

D

Cвх

1

0

Cвх

0

0

Cвх

1

0

s2

S

1

0

s3

0

0

s4

БЭ Cвых

БЭ

Cвых

Clk

D

clk

S

БЭ Cвых

Clk

D

clk

s1

Clk

D

clk

1

0

S

Cвх

S

БЭ Cвых

Clk

s1 Выходная z 0 z

1

1

s2

z2 1 z2

ТП

s3

0z

3

s4 результата z3

Все арифметические операции реализуются с

использованием конвейерной техники вычислений

Схема структурная базового элемента

D Т1 Q

XOR

S

Ñ

D

AND

D Т2 Q

Ñ

Cвх

Clk

Cвых

Скорость выполнения арифметическико-логических операций

обеспечена на частоте работы базового элемента:

TБЭ=tDFF+max{tAND;tXOR}.

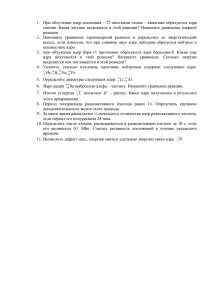

Схема структурная преобразователя

кодов ПСС-СОК

DI

DI[31..0]

32

31

RgDI

0

31

RgDI

Входная ТП

основания p1

415

DO

0

415

DI

DO

0

415

DI

0

DO

7

DI

13

DO

0

13

DI

415

0

6

DO

7

0

13

0

DI

0

Параллельный

сумматор

...

DO

0

13

13

0

...

Блок коррекции

0

DO

416

13

Блок коррекции

6

415

0

0

Входная ТП

основания pn

...

Параллельный

сумматор

13

13

RgDI

416

Параллельный

сумматор

13

DO

31

0

Входная ТП

основания p2

416

415

DI[31..0]

32

DI[31..0]

32

0

DI

0

Блок коррекции

7

DO

0

8

DO

Обеспечиваются аппаратные преобразования кодов чисел из

ППС в СОК и наоборот со скоростью работы ядер

процессора.

Техническая реализация прототипа

процессора

Работоспособность прототипа подтверждается результатами

моделирования функциональных схем процессора в САПР

Quartus II Web Edition фирмы Altera

Техническая новизна

1. Устройству присущ как параллелизм уровня

вычислительных модулей, осуществляющих

независимую обработку вычетов, так и конвейерный

параллелизм внутри каждого вычислительного

модуля

2. В конвейерном режиме результат любой

арифметический операции доступен каждый такт

работы ядра

3. Скорость выполнения всех операций равна скорости

срабатывания одного логического элемента

12

Техническая новизна

4. Регулярность структуры позволяет легко

наращивать количество оснований, по которым

ведутся вычисления, в случае расширения

диапазона представления чисел

5. Становится возможным реализовать вычисления с

переменной разрядностью операндов, выделяя для

этого группы вычислительных модулей

13