Моделирование температурной зависимости субмикронных

реклама

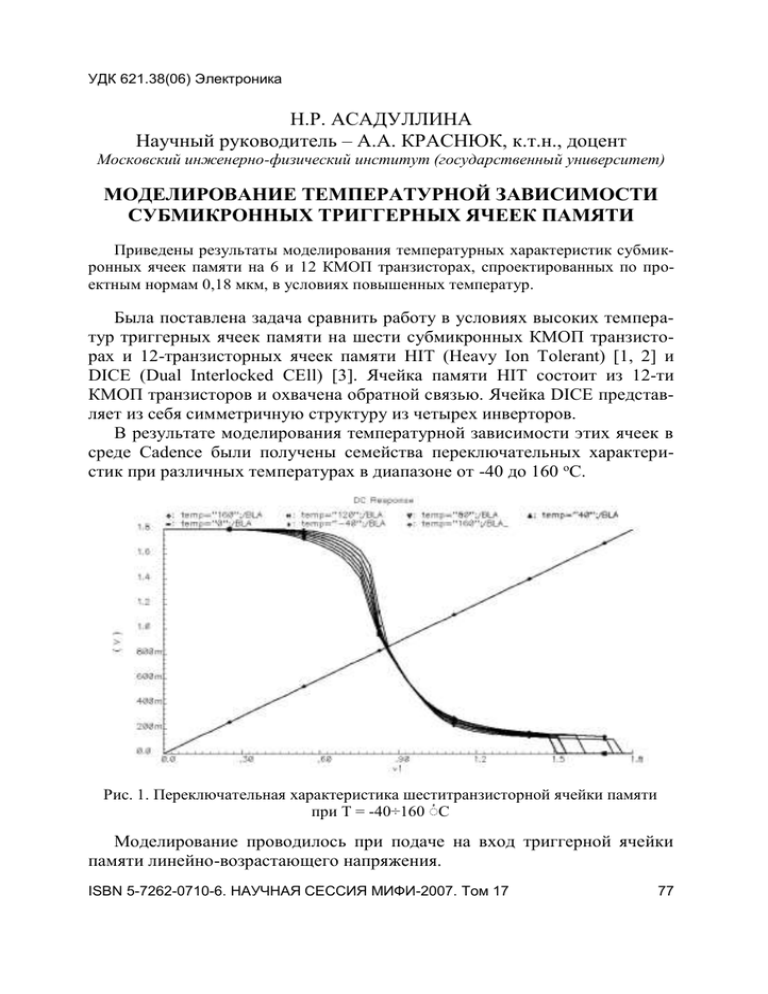

УДК 621.38(06) Электроника Н.Р. АСАДУЛЛИНА Научный руководитель – А.А. КРАСНЮК, к.т.н., доцент Московский инженерно-физический институт (государственный университет) МОДЕЛИРОВАНИЕ ТЕМПЕРАТУРНОЙ ЗАВИСИМОСТИ СУБМИКРОННЫХ ТРИГГЕРНЫХ ЯЧЕЕК ПАМЯТИ Приведены результаты моделирования температурных характеристик субмикронных ячеек памяти на 6 и 12 КМОП транзисторах, спроектированных по проектным нормам 0,18 мкм, в условиях повышенных температур. Была поставлена задача сравнить работу в условиях высоких температур триггерных ячеек памяти на шести субмикронных КМОП транзисторах и 12-транзисторных ячеек памяти HIT (Heavy Ion Tolerant) [1, 2] и DICE (Dual Interlocked CEll) [3]. Ячейка памяти HIT состоит из 12-ти КМОП транзисторов и охвачена обратной связью. Ячейка DICE представляет из себя симметричную структуру из четырех инверторов. В результате моделирования температурной зависимости этих ячеек в среде Cadence были получены семейства переключательных характеристик при различных температурах в диапазоне от -40 до 160 оС. Рис. 1. Переключательная характеристика шеститранзисторной ячейки памяти при T = -40÷160 С Моделирование проводилось при подаче на вход триггерной ячейки памяти линейно-возрастающего напряжения. ISBN 5-7262-0710-6. НАУЧНАЯ СЕССИЯ МИФИ-2007. Том 17 77 УДК 621.38(06) Электроника Дрейф переключательной характеристики шеститранзисторной ячейки памяти при нагреве от -40 до 160 С показан на рис. 1. В качестве примера результатов для 12-транзисторных ячеек представлено переключение HIT ячейки из состояния логической «1» в состояние логического «0» – рис. 2. При возрастании температуры характеристики сдвигаются влево. Было получено, что 12-транзисторные ячейки имеют меньший сдвиг точки переключения при изменении температуры: 142 нВ/ С и 78,5 нВ/ С для шеститранзисторной и 12-транзисторной ячеек соответственно. Напряжение переключения определялось по уровню 0,5*(U1вых – U0вых). Это позволяет говорить о том, что 12-транзисторные 0,18 мкм КМОП ячейки памяти обладают лучшей помехоустойчивостью при изменении температуры. Рис. 2. Переключательная характеристика 12-транзисторной ячейки памяти при T = -40÷160 С Список литературы 1. Bessot D., Velazco R. Design of SEU-Hardened CMOS Memory Cell // RADECS ’93. 1993. INSPEC 4744705. Р. 563. 2. Velazco R., et al. Two CMOS Memory ells Suitable for the Design of SEU-Tolerant VLSI Circuits // IEEE Trans. Nucl. Sci. 1994. Vol. 41. №6. Р. 2229. 3. Calin T., Nicolaidis M., Velazco M. // IEEE Tran. Nucl. Sci. 1996. Vol.43. №6. Р. 2874. ISBN 5-7262-0710-6. НАУЧНАЯ СЕССИЯ МИФИ-2007. Том 17 78