П.В. СТЕПАНОВ Научный руководитель – В.Я. СТЕНИН, д.т.н., профессор

реклама

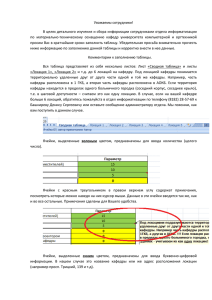

П.В. СТЕПАНОВ Научный руководитель – В.Я. СТЕНИН, д.т.н., профессор Национальный исследовательский ядерный университет «МИФИ» НИИ системных исследований РАН ВЛИЯНИЕ ПРОХОДНЫХ КЛЮЧЕЙ НА ПОМЕХОУСТОЙЧИВОСТЬ ЯЧЕЙКИ ПАМЯТИ DICE Проведен анализ влияния проходных двунаправленных ключей сбоеустойчивость КМОП ячейки памяти DICE с проектной нормой 28 нм. на В режимах чтения и записи в блоках ОЗУ на линиях данных открытой ячейки памяти стоят закрытые двунаправленные проходные ключи. На рис. 1 приведена схема КМОП ячейки памяти DICE[1] и проходных ключей. Возникновение импульса тока на выходе ключа при достаточной его амплитуде приводит к сбою открытой для чтения ячейки памяти. UDD Q11 KлA KлB UDD A C K1 K2 UDD Q21 Q12 UDD B D K3 KлC KлD Q22 K4 Рис. 1. Моделировалось воздействие импульса тока IФ(t) двухэкспоненциальной формы[1] с постоянными времени нарастания τН = 2.5 пс и спада τСП = 5 пс. Моделирование проведено в симуляторе Spectre САПР Cadence для структур по объёмной КМОП технологии с проектной нормой 28 нм с длиной канала 35 нм по моделям mac при напряжении питания 0.9 В и температуре +25˚C. Ширина канала транзисторов ячейки WN = 170 нм, WP = 115 нм; транзисторов ключей WN = 590 нм, WP = 400 нм. Выходные узлы ячейки обозначены как ABCD. Влияния конструктивных связей отражено емкостями узлов СУЗЛА.ДОП = 0.5 фФ. Моделирование проведено с учетом емкости линии данных массива ячеек СBL = 1 фФ, так и отдельной ячейки при СBL = 0 фФ. На рис. 2 приведены критические характеристики, разделяющие области устойчивости (слева) и сбоя состояния ячейки (справа от кривой) при одновременном воздействия импульсов тока на ключи узлов АС (одно семейство зависимостей на рис. 2) или ключи узлов BD (второе семейство зависимостей) в исходном состоянии узлов ABCD1010. QКл.А.КР, фКл 4 3 A C 2 CBL =1 фФ CBL =0 1 AD 0 0 1 2 3 4 QКлС, QКлD, фКл Рис. 2. Сбои при одиночных воздействиях на проходные ключи ячейки одного из узлов не зарегистрированы, что объясняется устойчивостью триггера DICE к одиночным воздействиям на узлы. Воздействие на ключи Кл.B и Кл.D не приводит к сбою ячейки памяти, поскольку NМОП транзисторы выборки препятствуют распространению помехи положительной полярности к узлам B и D в состоянии логического “0”. Воздействие на ключи Кл.А и Кл.B также не приводит к сбою, так как в состоянии AB1010 узлы AB триггера не подвержены сбою [2]. Увеличение емкости линии данных CBL снижает чувствительность ячейки к помехам. Работа проводилась в рамках гранта РФФИ № 12-07-31040 “Разработка методов и средств повышения сбоеустойчивости элементов суб-100 нм КМОП СБИС СОЗУ”. Список литературы 1. 2. Nicolaidis M. Soft errors in modern electronic systems. New York: Springer. 2011. 316 p. Стенин В.Я., Катунин Ю.В., Степанов П.В. Особенности проектирования DICE элементов 65-нм КМОП статических запоминающих устройств с учетом эффекта кратного воздействия отдельных ядерных частиц// Вестник НИЯУ МИФИ. 2013. Т. 2. №3. С. 363−370.