**************** ********* OS Linux

реклама

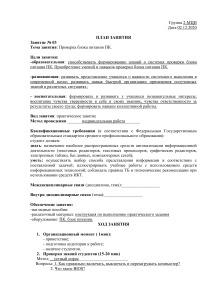

Андрианов Андрей Владимирович [email protected] ЗАО НТЦ “Модуль” Функциональное тестирование IP блоков в составе системы. Доработка IP блока с учетом замечаний программистов. Разработка прототипа драйвера. Управление питанием и/или тактированием различается/отсутствует Регистровая карта блока не является финальной и может меняться в ходе разработки Могут присутствовать аппаратные ошибки Могут присутствовать отладочные аппаратные надстройки Избыточное количество проверок и отладочных сообщений Низкая производительность Большое количество “мертвого” кода, который никогда более не будет использован (#ifdef FPGA_PROTOTYPE). Необходимость переписывания с нуля после выпуска СБИС (худший случай) Скорость разработки намного выше, чем на С. Снижение количества необходимых перезагрузок (Идеально - только в случае аппаратных ошибок). Возможность быстро получить доступ к регистрам IP блока в интерактивном режиме Простой и широкоиспользуемый язык Легко встраивается в приложения Возможность создать stand-alone приложение не требующее зависимостей. Есть JIT-компиляция (luajit). Простота кросс-компиляции (Всего 34 .c файла), нет зависимостей. Один общий драйвер, позволяющий получить доступ к регистрам устройства и обрабатывать прерывания из пространства пользователя Расширение для lua для взаимодействия с драйвером. Библиотека вспомогательных функций на языке lua Дополнительные утилиты Средства для отслеживания типичных аппаратных ошибок в работе DMA (запись за пределы буфера, и т.п.) Защита от “interrupt storm” Запись трейсов записи/чтения регистров в журнал с расшифровкой в произвольном формате Мониторинг состояния регистров В конечной продукции Когда требуется получить максимально достоверные данные о производительности блока Когда требуется протестировать взаимодействие блока с другими подсистемами ядра OS Linux http://github.com/nekromant/lprobe