~

412

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I. FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 40, NO. 6, JUNE 1993

On the Optimization of MOS Circuits

Jiabi Zhu, Student Member, IEEE, and Mostafa Abd-El-Barr, Senior Member, IEEE

Abstract-Optimizing the number of transistors in a complex

MOS gate is significant for minimizing chip area and delay in

VLSI designs. Unfortunately, such optimization process is an NPC problem. The worst case computational complexity of graphoriented algorithms used in existing approaches is exponential in

the number of transistors. In this paper, we address this problem

through the use of bridging switches. We propose a theory

and an algorithm for optimization of MOS switch networks

using an edge-merging technique. The worst case computational

complexity of the heuristic algorithm proposed is O ( n 5 e 2 ) where

,

n is the number of nodes and e is the number of edges in the

switch network.

4 Vdd

Inputs

a

n-net

(a)

I. INTRODUCTION

p-net

S

WITCH network design is an important synthesis method

for MOS circuits. In this method, a Boolean expression is

converted into a complex gate which consists of one or more

switch networks as shown in Fig. 1. An MOS transistor can

be modeled as a voltage-controlled switch as shown in Fig. 2.

It can also be modeled as a labeled edge in a graph. When

the input variable corresponding to the label on the edge is

1 (high level), connection between the two end nodes of the

edge is established. In this way, a logic function is represented

using transistor network(s) such that for some input variable

combinations there is at least one path between two ports

(called the drain and the source which correspond to ports

D and S in Fig. 1, respectively) of the net, while for the other

input combinations there is no path between these two ports.

The AND function is presented as serial edges between the drain

and the source, while the OR function is presented as parallel

edges, as shown in Fig. 3.

Some logic functions can be implemented using fewer

number of transistors in the nonseries-parallel structure. The

edges connecting some intermediate nodes of two (or more)

paths are called bridges. For example, the logic function

Inputs

n-net

Pre-charge

4

F = ab + ade + cd + bce

whose graph representation is shown in Fig. 4(a) can be

implemented using the simpler logic function whose graph

representation is shown in Fig. 4(b). The latter circuit requires

only 5 transistors, as compared to 8 transistors if the network

corresponding to Fig. 4(a) was used (a 37.5% reduction in the

number of transistors).

Optimization of the number of transistors in a circuit is

significant, because a smaller number of transistors usually

leads to a smaller chip area. There exists a number of optimization methods for MOS circuits [ 11-[7]. However, no one

Manuscript received June 9, 1992; March 3 , 1993. This paper was recommended by Associate Editor J. Choma, Jr.

The authors are with the Department of Computational Science, University

of Saskatchewan, Saskatoon, Sask., Canada S7N OWO.

IEEE Log Number 9209004.

(d)

Fig. I .

Four types of MOS circuits. (a) nMOS. (b) Full CMOS. (c) Dynamic

CMOS. (d) Pass-transistor model.

method ensures that the resultant switch network is always

minimal, and also the computational complexity of most

existing methods and algorithms is prohibitively high.

In this paper, we propose a theory and the corresponding

algorithm for optimization of switch networks. The worst case

computational complexity of our algorithm is O ( n 5 e 2 )where

,

n is the number of nodes and e is the number of edges in the

networks. Experimental results are reported in Section V.

1057-7122/93$03.00 0 1993 IEEE

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

ZHU AND ABD-EL-BARR: OPTIMIZATION OF MOS CIRCUITS

413

with more than one term are not considered in Dietmeyer’s

algorithm. Brayton and Rude11 [2], [3] suggest kernels, which

are formed by more than two terms, as divisors to improve

gar

inputx the results obtained by Dietmeyer. For instance, ac d is

I

a kernel of F (shown above). Written in quotient-divisor

source

I

form, F = ( b

representation

e ) ( a c d ) is optimized as 5 literals.

n-channel transistor

switch or contact

in graph

Garuso [4] developed an algebraic factorization method in

Fig. 2. n-channel transistor and its equivalent switch.

which a factored expression of the given two-level function

is obtained as a disjunction of factored expressions of smaller

subfunctions. The results reported in [4] are better than those

reported before.

The factorization approach is suitable for implementing

Boolean functions using multilevel gate circuits. This is because this method always results in tree-like structure exAND

OR

pressions. Although factorization approach has been used to

Fig. 3 . Circuits and graph representations of AND and OR

optimize switch networks, it cannot produce nonseries-parallel

structures. The edge-merging approach is more general than

some

the factorization approach because it can synthesize switch

networks which use bridging switches.

The edge-merging approach is a graph-oriented method

[5]-[7]. In this approach, each literal in a term of a Boolean

expression is counted as one edge. A procedure is then used

to merge any pair of edges which have a common node and

the same literal in the graph representation of the net. A

check is then conducted to see whether this merge is valid.

A valid merge is defined as one which does not change the

logic function represented by the net. If the merge is valid,

then several edges are merged; otherwise, the merge is not

performed. The steps of the algorithm are as follows [6].

Step 1: Form a switch network in which each symbol in a

dnin

dnin

term of the given Boolean function is realized by an edge.

Step2: For each pair of edges which correspond to an

(b)

Fig. 4. Optimizing switch net with bridge. (a) Series-parallel structure. identical variable (a variable and its complement are counted

(b) Bridge structure.

as different variables), perform the following steps:

Step 2.1: If the pair of edges do not have a common

node,

perform edge-changing two-terminal two-isomorphic

11. EXISTING

METHODSFOR MINIMIZING

SWITCHNETWORKS

transformations to make them connected together. If the pair

There are two main approaches reported in the literature of edges cannot joint together, Step 2.2 is skipped.

for optimization of MOS circuits: factorization [ 11-[4] and

Step 2.2: Merge the pair of edges into an edge and check

edge-merging [5]-[7].

the .function represented by the merged network against the

The use of factorization approach results in a (near) min- given switchfunction. If they are the same, the merge is valid;

imum factored expression for a given function using some otherwise the pair of edges cannot be merged.

heuristic algorithms. For example, the function F = abc

Example I : Suppose it is required to optimize the function

ace bd de can be factorized into F = (ac d ) ( d e ) . F given by

Only five transistors are required for the implementation of

F = ABGD+ ABC+ ABD + Z B D + Z B D .

the factorized form of the function, compared to 10 transistors

if the original form of F is implemented.

According to Step 1, a switch network is formed as shown

The basic idea of factorization algorithms is that a divisor in Fig. 5(a) in which each edge corresponds to a literal in

of the function F to be factored is singled out, then F is the original function. Because three edges labeled A and two

divided by this divisor. Such procedure is recursively applied edges labeled are connected together, Step 2.2 is performed.

to the remainder. Computing time and factorization quality The three edges labeled A are merged, and the function of

depend on the strategy of selecting divisors. Dietmeyer [ 11 the merged network is compared with the original function.

seeks, as a divisor, a factor having the largest figure of merit. Because these two functions are the same, the merge is

This is defined as the product of the number of literals in valid. Similarly, the two edges labeled 2 are merged. The

the factor by the number of terms, in F , which holds it. resultant network is shown in Fig. 5(b). The process is now

For example, function F = abc ace bd

de contains repeated starting from Step 2.1. The two edges labeled B

10 literals. Using Dietmeyer’s algorithm, F is factorized as and three edges labeled B are made connected together by

F = ac(b e ) d ( e b ) with 7 literals. However, factors using transformations, as shown in Fig. 5(c). Merge the B

drain

+

+

r

n

+ +

+

+

+ +

+

+

+

+ +

+

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I:

414

FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 40, NO. 6, JUNE 1993

S(source)

B

3

E

8

D

D'

A'

B'

(b)

Fig. 6. Effect of merging of edges. (a) Case 1. (b) Case 2.

5

E

8

A'

B'

D

the validation checks performed in step 2.2 can be avoided,

and hence the computational complexity can be reduced. In

this paper, we propose a synthesis theory and an algorithm

which can be used to achieve such a goal.

D'

E@

8

A'

(d)

Fig. 5.

Edge-merging approach.

and B edges, respectively, and verify the function of merged

network. The network of the optimized function is shown in

Fig. 5(d). The number of transistors required to implement

the optimized function is 10, compared to 16 if the original

function is implemented.

The task of "checking the function realized by a network,"

as required by Step 2.2, is difficult to implement. It is

equivalent to verifying all the paths in the graph. The worst

case complexity of an algorithm to verify all paths in a graph

with e edges is 0(2"/'). A heuristic strategy is difficult to

use here because all involved paths have to be verified. One

possible solution to the prohibitive computing complexity of

this approach is to use the decomposition technique presented

in [8]. However, the partitioning may destroy the relationship

among the edges, and may change the structure of the graph

so that the optimal solution will never be found.

On the other hand, if an algorithm is used whereby only

those edges which can be validly merged are considered, then

111. THECONCEPTS AND THEORY FOR VALID EDGE-MERGES

A modification to the graph representation of a switch net

may, or may not, affect the logic expression realized by the

net. For example, suppose that the literals of edges (A, B)

and (A, C ) in Figs. 6(a) and (b) are the same, say x, where

A . B . C, and N are nodes in the graph representation of the

net. If we combine (A. B)with ( A . C), by merging nodes B

and C, no path will be affected in Fig. 6(a). We call such

merge, a valid merge. However, if we apply the same merging

to the graph representation in Fig. 6(b), path S B A C D will

be shortened to S B D (or S C D ) , and literal x corresponding

to edges (A. B ) and ( A , C ) will be removed from the path,

i.e., the function of the switch net in Fig. 6(b) will change

due to merging edges ( A , B ) and (A, C ) ;hence such merge

is invalid.

Dejinition I : Paths p1 and p 2 are said to be a pair of crossed

paths if the same node N exists on both paths; otherwise, p l

and p z are said to be a pair of noncrossed paths.

The concept of crossed paths is illustrated in Fig. 7. In this

figure, p l ( S - N - A ) and p z ( D - N - B) in Fig. 7(a) are

crossed paths, while p j ( S - C) and p 4 ( D - E ) in Fig. 7(b)

are noncrossed paths.

Dejinition 2: Nodes A and B are said to be a pair of

divergent nodes if there is noncrossed path pair p l and p 2 ,

such that path p l is between node A and the source (or the

drain), and path p2 is between node B and the drain (or the

source); otherwise, nodes A and B are said to be a pair of

convergent nodes.

In Fig. 7, paths p l and p 2 are crossed, while paths p 3 and

p4 are noncrossed. Therefore, nodes A and B in Fig. 7(a) are

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

415

ZHU A N D ABD-EL-BARR: OPTIMIZATION OF MOS CIRCUITS

(b)

(b)

Fig. 7. Crossedhoncrossed path pair and convergent/divergent node pair.

(a) Crossed path pair and convergent node pair. (b) Noncrossed path pair and

divergent node pair.

Fig. 8. Redundant path. (a) The circuit. (b) Graph representation

convergent node pair while nodes C and E in Fig. 7(b) are

divergent node pair.

Dejinition 3: If there is a convergent node pair on a path,

then that path is said to be redundant, and the part of the path

in which the convergent node pair exists is called redundant

part; otherwise the path is said to be nonredundant.

In Fig. 8 , nodes A and B are convergent node pair, therefore the path S N A B N D is redundant. The logic expression

represented by the graph in Fig. 8 is completely determined

by subgraph S N D , and is independent of subgraph N A B N ,

i.e., part N A B N is redundant. This implies that we can do

any modification within part N A B N without affecting the

expression represented by the graph.

Dejinition 4: Consider subgraph GI = ( N I . E’) of graph

G, where N‘ is a node set, and E’ is an edge set. Path p

is said to be independent of subgraph GI, if the following

operations do not change the logic expression associated with

path p which exists between the source and the drain of graph

G:

1) deletion of edge e, for any E E’ and/or

2) addition of edge e, for any e = ( n I ,7 1 , ) . where 1 1 , and

ri, E

NI.

It should be noted that only the deletion and/or addition of

an isolated node (a node that is connected to no edges in a

graph) will not change the logic expression represented by a

graph. Notice also that a path between the source and the drain

is independent of its redundant part. For example, in Fig. 8 the

path between S and D is independent of the redundant part

N A B N . In what follows we will use “a path is independent

of a set of edges” and “a path is independent of subgraph GI”

to mean the same thing.

Lemma 1: If node A and node B are convergent node pair

in graph G, then any path between the source and the drain

of graph G is independent of the edge(s) between node A and

node B , regardless of whether nodes A and B or either of

them is on a given path.

Proofi Consider a path p between the source and the

drain. There are two cases.

Fig. 9.

Illustration of Lemma 2

Case 1: Both node A and node B are on p . Because A

and 8 are convergent, p is redundant and the edge(s) in

set E = ( P , I e L = ( A . B ) } constitute a redundant part.

Therefore, the logic expression represented by p is independent

of E .

Case 2: None of A and B or only one of them, is on p. In

this case, no edge among E is part of p . Therefore the logic

expression represented by p is independent of E .

[Q.E.D.]

As an example, consider the network graph representation

shown in Fig. 8. The removal of the convergent nodes A and

B or the insertion of a new edge between them will not change

the logic expression of the network.

Dejinition 5: Ports of a subgraph G I with respect to path

p are defined as the nodes in G1 through which p enters to

or leaves from GI.

In Fig. 9, node A and B are the ports in G I with respect

to p , where p consists of p 1 and 112.

Lemma 2: Consider the graph representation of a network

as shown in Fig. 9. Let node set N = ( N , } is such that there

exist edges e: = ( N , . A ) and e:/ = (N,. B ) connecting N ,

with both nodes A and B . Assume that nodes A and B are

convergent in the absence of edge set E1 = { e , I e , = (N,. A )

or P , = ( N , , B ) , for all N , E N } . If A and B are the only

two ports in G1 = ( N U { A , B } , El U Ez) for path p , where

edge set E2 = (e* I e* = ( A , B)}, then path p between the

source and the drain is independent of the subgraph GI.

Proofi Because A and B are the only two ports in G1

for p , when El U E2 are taken away, p is divided into two

part p l and p 2 . However, in absence of El and since A and

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 40, NO. 6, JUNE 1993

416

c

N2

dh/

Fig. 10. Example of Lemma 2.

(b)

(b)

Fig. 1 1 .

Illustration of Lemma 3. (a) Before modification. (b) After

modification.

B are convergent, p l and p z must meet at a node no $! N .

Therefore the edges of p in El U E2 are the redundant part of

p. Therefore p is independent of G1.

[Q.E.D.]

Consider the graph representation shown in Fig. 10. The

path between the drain and the source via node C is independent of the edges ( N I ,A ) , ( N I ,B),(N2, A ) , and ( N 2 ,B ) .

That is, the logic expression associated with the path would

not change if some of these edges were removed or if even

some new edges were added among nodes N I , N2, A, and B.

Lemma 3: Consider the graph representation of a network

as shown in Fig. 1 l(a). Let edge sets E’ = {e: 1 e: = ( A , B ) } ,

E” = {e: I e: = ( A , C ) } , and E* = {e* 1 e* = ( B , C ) } .

Assume that nodes B and C are convergent node pair in the

absence of E’ and E”. If for every e: E E’ (e: E E”), there

exists an e: E E” ( e l E E’) such that the literals of e: and e;

(e: and e>j are the same, then node C can be merged together

with node B, and E” and E* can be removed, as shown in

Fig. 1 1(b), without affecting the logic expression represented

by the graph.

Before proving this lemma, let us informally explain its

meaning first. In the assumption, the edges between nodes A

and B are same as the edges between nodes A and C. The

assumption that “nodes B and C are convergent node pair in

the absence of E’ and E“” means that one need not to worry

about the paths from node B to node C , as proved in Lemma 2.

Proof: From Lemma 2 we know that the paths which

enter and leave G I = ( { A , B , C } , E’ U E” U E * ) through

nodes B and C are independent of G1, so we need not consider

these paths. What we need to prove then is to show that

the paths which enter and leave G1 through A-B, and A-C

remain unchanged if edge sets E’ and E” are merged together.

Fig. 12. Example of a redundant node ( A ) . (a) Before modification.

(b) After modification.

For the nonredundant paths passing through A and B , there

are two routes: A-B, and A-C-B. Since the logic expression

of paths A-B is the same as that of paths through A-C, then

the logic expression of path A-B combined with path A-C-B

is the same as that of path A-B. That is, we need not consider

path A-C-B. Because the edges { ( A , B ) } remain unchanged,

the logic expression of the paths through A and B remain

unchanged after B and C are merged. Similar argument can

be stated about path A-B-C. Therefore, the literals of the

paths A-C remain unchanged after C is merged with B , and

[Q.E.D.]

hence the merging of B with C is valid.

Lemma 3 allows the removal of the redundant edges in E”

and E*.

Dejinition 6: Consider the graph representation shown in

Fig. 12(a). Node A is said to be redundant, if for every edge

from A, for example, e: = ( A , C;), where Ci is a node,

C; # A , and C; # B, there exists an edge e: = ( B , C;)

such that the literals of e: and e r are the same.

Lemma 4: A redundant node (e.g., node A in Fig. 12(a))

and its associated edges can be removed without affecting the

function of the net (see Fig. 12(b)).

Proof: Consider subgraph G1 = (N, E) in graph G,

where node set N = { A , B } U {C;} and edge set E = {e 1

e = ( A , B ) or ( A , C;) or ( B , Ci),for all Ci}, as shown in

Fig. 12(a). From the assumption we know that all the edges

connected to A and B are in E, and that any path between

the source and the drain of graph G can enter and leave G1

only through node Ci, i.e., {Ci} is the set of ports of G I .

Consider a path passing through Ci and Cj where Ci # Cj.

There are two routes between C;and Cj, i.e., C;-A-Cj and

Ci-B-Cj. From the definition of a redundant node, we know

that the literals of these two paths are the same. Therefore, we

[Q.E.D.]

can validly remove A and its associated edges.

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

ZHU AND ABD-EL-BARR: OPTIMIZATION OF MOS CIRCUITS

417

(b)

(b)

Fig. 13. Modifying the switch net into bridge structure. (a) Before modifying.

(b) After modifying.

The following lemma allows us to obtain optimized switch

nets using bridges.

Lemma 5: Consider a graph GI = ( N , E) where the set of

nodes N = { A , B , C, D } and the set of edges E = El U E2,

as shown in Fig. 13. Suppose that El = {el, ez, e3, e4}

C)}, where el = ( A , B ) , e2 =

and E2 = {e, I e, = (B,

( B , D ) , e3 = ( A , C), and e4 = (C, D ) . Let the literals of

e l , e2, eg, and e4 are x, yz, xy and z , respectively. Assume

that B and C are convergent node pair in the absence of E l ,

then G1 can be reduced into G’, = ( N , E’), as shown in Fig.

13(b), where E’ = {el, e4, e5} U E2, e5 = ( B , C), and the

literal of e5 is y (the common literal between e2 and e3).

Proot From Lemma 2 we know that any path which

enters and exits GI through B and C is independent of GI.

So what needs to be done is to prove that the paths which

enter and exit G1 through A and D , A and B , A and G, B

and D , and C and D are independent of GI. Because of the

symmetry, it is sufficient to consider only the paths entering

and leaving G1 through A and D , A and B,and A and C.

The path entering and leaving G1 through A and B in G1

remains unchanged in G’,. The path which passed through A

and C in GI will pass through el and e5 in G:. The literals

o f ~ t h epath, xy, remain unchanged in G’,.

Now consider the path which enters and exits GI through

A and D. There are two routes for nonredundant paths:

1 ) el-eg-eq, where eo E Ea. These paths remain unchanged in G:.

2 ) e1-e2 or e3-e4. These paths are changed into el-es-eq

in G’, . Their literals, however, remain unchanged, i.e.,

xyz.

[Q.E.D.]

In the general case, x, U, and z can be one or more literals,

and node A and node D can be the same node, as shown in

Fig. 14(a). In the latter case, edges e2 and e3 can be reduced

into edge e5, as shown in Fig. 14(b). An example for the

application of Lemma 5 is shown in Fig. 15.

Fig. 14. Example of a 3-node bridge. (a) Before modifying. (b) After

modifying.

Fig. 15. Example of application of Lemma 5. (a) Original circuit. (b)

Optimized circuit.

IV. PROPOSED ALGORITHM

FOR

OPTIMIZATION

OF SWITCHNETS

In this section, we propose an algorithm for optimization of

switch networks. A basic step in the optimization process is to

verify the ConvergentJdivergent relationship between any pair

of nodes in the graph representation of a given function. The

worst case computing complexity of an exhaustive algorithm

for this problem is 0(2e/2), where e is the number of edges

in the graph. This is because all paths from all nodes to the

source and the drain should be checked.

We introduce a heuristic algorithm, using procedure Relationship as shown in Fig. 16, to address such problem. The

basic idea of this algorithm is that when we verify convergenvdivergent relationship between two nodes, we identify a

path pl (PATH1 in Fig. 16) from a node n1 (node1 in Fig. 16)

to the source and another path p2 (PATH:! in Fig. 16) from

another node n2 (node2 in Fig. 16) to the drain. If these two

paths are noncrossed (see Definition I), then the nodes are

divergent. Otherwise, we try to modify these crossed paths

such that they become noncrossed. This modification can be

done by decoupling a node which belongs to the two paths

from at least one of these paths (see Fig. 17). In this figure, the

common node no (node0 in Fig. 16) belongs to both paths pl

and pa. Part (b) of the figure shows how to decouple this node

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

~

418

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: FUNDAMENTAL THEORY AND APPLICATIONS,VOL. 40, NO. 6, JUNE 1993

Relationship(node1, node2)

(IF(must-intersect(node1 ,source,node2,drain)==TRUE

AND must-intersect( node2,source,nodel ,drain)==TR UE)

THEN

ELSE

RETURN(C0NVERGENT);

RETURN(UNDETERM1NED);)

must_intersect(node, ,source,nodep,drain)

(Reset the marks of all nodes:

Find a path from node, to the source:

IF(the path does not exist) THEN RETURN(TRUE);

Find a path from node2 to the drain:

IF(the path does not exist) THEN RETURN(TRUE);

undetermined-flag=O;

FOR(nodeo E common nodes on both paths--updated)DO(

Mark nodeOas PATH2;

Find a path from node, to the source (with the nodes other than marked PATH2);

IF(the path does not exist) THEN(

Mark nodeOas PATH1:

Find a path from node2 to the drain (with the nodes other than marked

PATH1);

lF(the path does not exist) THEN

IF(undetermined-flag==O) THEN

RET URN(T R U E) ;

E LSE RET URN(UN DETERMINED));

ELSE ( Mark nodeOas PATHl :

Find a path from node2 to the drain (with the nodes other

than marked PATH1);

IF(the path exists) THEN undetermined-flag=l :

ELSE mark nodeOas PATH2;

1

1

ELSE

undetermined-flag=l ;

1

RETURN(FALSE);}

Fig. 16. Algorithm for finding the relationship between a node pair.

from p l . If such modification is possible, then we conclude

that the nodes are divergent; otherwise, they are convergent.

If there are more than one common nodes between p l and

p 2 , as shown in Fig. 18, the case will be much more involved.

Suppose that in the first iteration, pl = (nl, c1, c2, e , S )

and p2 = ( 1 2 2 , a, C I , cp, D),as shown in Fig. 18(c). There

are two common nodes c1 and c2 between paths p l and p 2 .

According to the algorithm shown in Fig. 16, the common

nodes are marked as belonging to either p l , or p 2 , or none

(three choices). If c1 were arbitrarily marked as belonging to

p a , then c2 could be marked as belonging to p ~ and

, paths

p l = (711, b, e , S) and p 2 = ( 7 ~ 2 a, , c1, c2, D ) become not

crossed as shown in Fig. 18(d). If, however, c1 is arbitrarily

marked as belonging to pl (see Fig. 18(c)), then the next step is

to mark ca. If c2 can be marked as belonging to one or none of

p l and p a , then we know that 7 ~ and

1

n2 are divergent. But if c2

cannot be marked, as shown in Fig. 18(e), then the relationship

between nl and 712 cannot be determined, and the other two

possible choices for marking c1 have to be considered one at

a time.

In the general case, suppose that there are m common nodes,

then there will be 3m choices for marking these nodes. To

speed up the algorithm, each common node is considered only

once thus limiting the computing complexity to O(m).

The node pair which the algorithm verifies as “UNDETERMINED’ (see lines 5 and 23 in Fig. 16) may be divergent,

or they may be convergent. In this case, we cannot use

Lemmas 3 and 5 to optimize the network. This will cause the

algorithm to sometimes produce suboptimal results. However,

the operations performed by the algorithm are always valid.

The computational complexity of loop FOR (line 13 in Fig.

16) in “must-intersecto” is O ( n ) ,where n is the number of

nodes. In that loop the complexity of finding a path from

a node to the source (or the drain) is O ( e ) , where e is

the number of edges. Therefore, the complexity of verifying

ConvergenVdivergent relationship is O(ne).

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

419

ZHU AND ABD-EL-BARR: OPTIMIZATION OF MOS CIRCUITS

fDra’”

d Source

(a)

t

Dra’n

(b)

Fig. 17. Finding the relationship between two nodes. (a) First step: find 1’1

and 1’2. (b) Second step: Decouple common node i t ” .

The algorithm shown in Fig. 19 makes use of the above

algorithm, and is used to minimize MOS switch networks.

This algorithm uses a “greedy strategy.” When more than one

optimizing situations are available at a given step, the merge

which causes the largest number of literals to be removed

is performed. This strategy helps preventing the optimization

process from being stuck in a “local minima.”

In optimizing the number of transistors, two other heuristic

strategies are used. In the first one, higher priority in selecting

the paths to be merged is given to longer path (paths with

more literals). This strategy will cause all paths in the network

to have comparable lengths during optimization. The other

strategy considers the ratio of the number of literals of a path to

be merged to the total number of literals of that path such that

edges will not be broken into too small pieces. For example,

merging 2 literals of an edge which has 3 literals in total is

given higher priority than merging 2 literals of an edge with

5 literals.

The computing complexity of each step in the algorithm

shown in Fig. 19 is listed in Table I. In the worst case, the

computational complexity of this algorithm is 0 ( n 5 e 2 ) .

v.

IMPLEMENTATION AND RESULTS

The algorithm presented above was implemented on a SunSparc 2 workstation using C language under Unix operating

system. The input of the algorithm is the graph representation

of logic function obtained using Quine-McCluskey algorithm

[9]. We offer the following example to illustrate the use of the

proposed algorithm to minimize MOS networks.

Example 2: Suppose that it is required to implement the

function

F = abzf

+ abh + aceg + abce + bc&f + bcdh + deg + bde.

1”

(e)

Fig. 18. Case in which there are two common nodes. (a) Original circuit.

(b) Graphical representation of the circuit. (c) Paths 1’1 and p 2 found in the

first iteration. (d) If c1 is assigned to p r . p1 should detour c1. (e) Because

c1 is assigned to p 1 , 1’2 should detour c1.

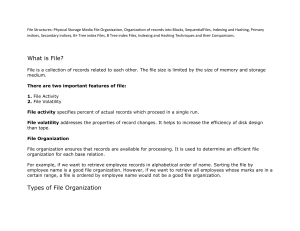

TABLE 1

COMPUTING COMPLEXITY OF THE

ALGORITHM

..........................................................

STEP 1

STEP 2

The original switch net without any minimization is shown in

Fig. 20. The corresponding graph is shown in Fig. 21(a). The

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

420

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I:

FUNDAMENTAL THEORY AND APPLICATIONS. VOL. 40. NO. 6. JUNE 1993

STFP 1: Find the redundant edge set which contains the

maximum number of edges, and merge them. Repeat this

procedure until no redundant edges can be found.

STEP 2: Find the redundant node which involves the maximum

number of edges, and remove it and its related edges (using

Lemma 4). Repeat this procedure until no redundant nodes can

be found.

STFP 9: Find a sub-graph which satisfies the condition in

Lemma 5, and change it into a bridge-based structure (using

lemma 5). Repeat this procedure until no such sub-graph can be

found.

) Until (no further optimization can be obtained);

Fig. 19. Algorithm for minimizing MOS switch net

function name

Example 2

f4

fs

_f 6f13

number of transistors

results in [4]

results in [lo]

QUICK-FACTOR alg. FACT alg.

results of

this paper

C P U time (sec)

using

our algorithm

-

-

10

10

< 0.01

69

33

36

38

58

29

35

38

58

28

32

38

56

28

32

0.58

0.25

0.33

0.17

optimization process based on Lemmas 3 and 4 is shown in

Fig. 21(a)-(d). Based on Lemma 5, a bridge can be formed,

as shown in Fig. 21(d)-(e). The optimized circuit is shown

in Fig. 22.

The algorithm has been applied to five of the example

functions given in [4] and [ 101. The results obtained are listed

in Table 11. The average number of transistors obtained using

our algorithm is fewer than those obtained using the algorithms

in [4] and [lo]. It should be noted that the algorithm in [4] is

specifically for series-parallel networks, and cannot produce

nonseries-parallel networks. Our algorithm can produce both

series-parallel and nonseries-parallel networks. Therefore, the

method proposed in this paper is also suitable for synthesis

of multilevel gate circuits. The graph representation of circuit

f4” from [4] and that obtained using our algorithm are shown

in Fig. 23, where the numbers on the edges are used to identify

literals in the function.

“

REMARKS

VI. CONCLUDING

Minimizing the number of transistors in a complex MOS

gate is significant for VLSI implementations. Unfortunately,

this process is an NP-C problem. Edge-merging algorithms

used in existing techniques has an exponential time complexity. In this paper, we propose the concepts and a theory

governing the optimization of MOS net using only valid

operations. A heuristic algorithm with a worst case time

complexity of O(n5e2),where n is the number of nodes and

e is the number of edges in the switch network, is given.

I

I

36

I

source

Fig. 20. Original switch net for Example 2 (30 transistors).

Examples illustrating the quality of the results obtained using

the proposed algorithm are reported.

It should be pointed that some improvements can be made to

the algorithm to keep some special optimal results from being

ignored. For example, in Fig. 6(b), if edge ( B , S) or (C, D )

contains literal ‘‘2,”then the merging of node B with node

C is valid. Another example is that if edge ( B , S) contains

literal “y” while edge (C, D )contains literal ‘‘3’’in Fig. 6(b),

the merging of node B with node C is also valid. Lemmas 2,

3, and 5 can be modified such that these cases are considered.

However, when there is more than one path from node B to

the source and/or from node C to the drain, the computational

complexity of verifying the above cases may be prohibitively

high. A tradeoff between the computational complexity and

the optimization quality is thus made in the algorithm.

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

~

42 1

ZHU AND ABD-EL-BARR: OPTIMIZATION OF MOS CIRCUITS

Drain

0

a

Lde

L

Source

SO”],

Fig. 22. Bridge net for Example 2 (10 transistors).

Drain

0

f

4

2

de

I

de

Drain

NO (drain)

I

Source

(d)

Drain

20:

n

a

Graph representation of circuit f4. (a) Result from [4].

(b) Result optimized using the algorithm in this paper.

d

1

Source

(e)

Fig. 21.

(b)

Fig. 23.

Optimization process applied to Example 2.

Since heuristic strategy is used in finding the relationship

among nodes, the algorithm proposed in this paper may give

suboptimal results in cases where the circuits (graphs) have too

many “common nodes” bewteen pl and p2 (see Section IV).

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.

422

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I:

It is well known that performance concerns limit the number of series pull-up and pull-down transistors in practical MOS networks. This problem can be solved through a

modification of the edge-merging methods as follows. The

networks optimized by edge-merging methods can be decomposed into series-parallel parts and nonseries-parallel parts.

The series-parallel parts can be mapped into multilevel gate

circuits if charge-sharing in these parts is a problem. Only the

nonseries-parallel parts should be implemented using complex

gates.

FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 40, NO. 6, JUNE 1993

computing, VLSI layoi

Jiahi Zhu (S’92) received the B.Eng. degree in

computer science and engineering and M.Eng. degree in electrical engineering from Tsinghua University, Beijing, People’s Republic of China in 1985

and 1990, respectively, and the M.Sc. degree in

computer science from University of Saskatchewan,

Saskatoon, SK, Canada, in 1992.

Following his graduate studies, he joined SED

System, Inc., in Saskatoon, designing products of

low-level network protocol conversion for satellite

communication. His interests are in fault tolerant

circuit optimization, and computer networks.

REFERENCES

D. L. Dietmeyer, “Logic design automation of fan-in limited NAND

networks,” IEEE Trans. Compur., vol. C-18, pp. 11-22, Jan. 1969.

R. K. Brayton, R. Rudell, A. Sangiovanni-Vincentellim,and A. Wang,

“Multilevel logic optimization and the rectangular covering problem,”

in Proc. ICCAD-87, Nov. 1987, pp. 66-69.

R. K. Brayton, “Factoring logic functions,” IBM J. Res. Develop., vol.

31, no. 2, pp. 187-198, Mar. 1987.

G. Caruso, “Near optimal factorization of Boolean functions,” IEEE

Trans. CAD, vol. 10, no. 8, pp, 1072-1078, Aug. 1991.

D. L. Dietmeyer, Logic design ofdigird sysrems.Allyn and Bacon, 197 1.

M. Wu, W. Shu, and S. Chan, “A unified theory for MOS circuit design

switching network logic,”Int. J. Electron., vol. 58, no. I , pp. 1-33, 1985.

Z. Kohavi, Swirching and Finite Automata Theory. New York:

McGraw-Hill, 1970.

M. Dagenais, “Efficient algorithmic decomposition of transistor groups

into series, bridge, and parallel combinations,” IEEE Trans. Circuits

Syst., col. 38, no. 6, pp. 569-581, June 1991.

E. McCluskey, Logic Design Principles. Englewood Cliffs, N.J.:

Prentice-Hall, 1986.

Y. Xu and M. Abd-El-Barr, “Switch-level minimization of logic functions,” submitted for publication.

Mostafa H. Ahd-El-Barr(M’WSM’M)) received

the B.Sc. and M.Sc. degrees in electrical engineering

in 1973 and 1979, respectively, from Cairo

University, Egypt, and the Ph.D. degree in electrical

engineering (computer group) from the University

of Toronto, Ont., Canada, in 1986.

In 1986 he joined the Faculty of the Department of Computational Science, University of

Saskatchewan, Saskatoon, Canada. where he is

currently a Professor. He is also an Associate Member of the Deoartment of Electrical Engineering

at the same University. His research interests include VLSI design and

implementation of algorithms, CMOS testability, fault-tolerant computing, and

multiple-valued logic systems design. He is the author and/or the coauthor

of more than SO scientific articles published in journals and symposia

proceedings. He has served and/or is currently serving on a number of

technical committees for conferences and symposia including the International

Symposium on Multiple-valued Logic (ISMVL), and the Midwest Symposium

on Circuits and Systems. He is a member of the ACM.

Authorized licensed use limited to: Ben-Gurion University of the Negev. Downloaded on August 26,2020 at 09:17:00 UTC from IEEE Xplore. Restrictions apply.