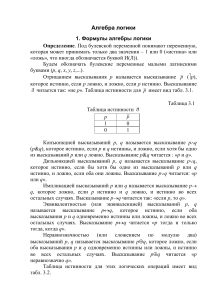

Логический элемент

реклама

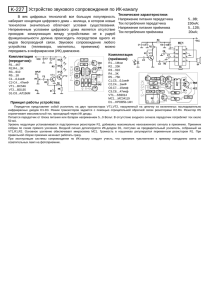

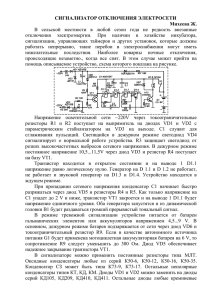

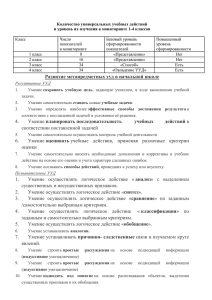

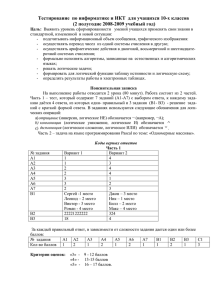

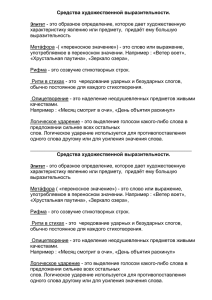

Логический элемент – простейшая структурная единица цифровой электроники, выполняющая определенную логическую операцию над двоичными переменными Цифровой логический сигнал представляет собой чередование двух четко определенных логических уровней В отличии от переменной в обычной алгебре логическая переменная имеет только два значения, которые называются логическим нулем и логической единицей. Логический нуль и логическая единица обозначаются соответственно 0 и 1. В алгебре логики 0 и 1 не числа, а логические переменные. Для большинства логических схем эти уровни характеризуются напряжениями Для большинства логических схем эти уровни характеризуются напряжениями 0В (0,4В) – логический ноль, 3 – 5 В – логическая единица В алгебре логики существуют три основных операции между логическими переменными: логическое умножение (коньюкция), логическое сложение (дизьюнкция) и логическое отрицание (инверсия). По аналогии с алгеброй чисел в алгебре логики используют следующие обозначения операции: Логическое умножение Логическое сложение Логическое отрицание Y = X1X2 = X1·X2 = X1X Y = X1+X2 = X1X2 YX Закон или правило Логическое умножение Логическое сложение 1. Коммутативный закон X1.X2= X2·X1 (2.1.) X1+X2= X2+X1 (2.2.) 2. Ассоциативный закон X1(X2X3)= (X1X2) X3 ( 2.3.) X1+(X2+X3)= (X1+X2)+X3 (2.4.) 3. Дистрибутивный закон X1·(X2+X3)= X1X2+X1X3 (2.5.) X1+X2X3= =(X1+X2)·(X1+X3) (2.6.) 4. Правило склеивания X1·(X1+X2)= X1 (2.7.) X1+X1X2= X1 (2.8.) 5. Правило повторения X·X=X (2.9.) X+X=X (2.10.) 6. Правило отрицания 7. Правило двойной инверсии X X 0 XX 8. Теорема Де Моргана X1 X 2 X1 X2 9. Операции с 0 и 1 X+0=X (2.17.) X+1=1 (2.19.) X X 1 (2.13) X1 X 2 X1 X2 X·1=X (2.16.) X·0=0 (2.18.) X1 & Y X2 Y X1 X2 Таблица истинности для логического умножения Х1 0 0 1 1 Х2 Y 0 1 0 1 0 0 0 1 X1 Y 1 X2 Y X1 X2 Таблица истинности для логического сложения Х1 0 0 1 1 Х2 Y 0 1 0 1 0 1 1 1 X1 1 Y Y X1 X2 X2 Таблица истинности для логической функции «Исключающее ИЛИ» Х1 0 0 1 1 Х2 Y 0 1 0 1 0 1 1 0 Исключающе е И НЕ ИЛИ ИЛИ НЕ Входные И ИЛИ переменные Y X1 X 2 Y X1 X 2 Y X1 X 2 Y X1 X 2 Y X1 X 2 X1 X2 Y Y Y Y Y 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 1 0 0 0 0 1 1 1 1 2 & 1 1 1 3 1 2 1 0 3 1 2 & 3 1 2 1 0 3 1 2 1 3 Техноло гия ИЛЭ Выполняемые базовые функции K раз K об U0 U1 В U пом t здр.ср Pcc В нс мВт лэ f пер триг, МГц 830 2-8 0,4 2,4 0,8 18-32 10 1035 И – НЕ 10 2-8 0,5 2,7 0,8 6 19-2 45100 ЭСЛ ИЛИ – НЕ 8 2-5 1,6 1,0 0,1 3-5 2540 125300 КМОП ИЛИ – НЕ 820 2-4 0, Uп 0,3 UП 601200 0,002 1030 ТТЛ ТТЛШ И – НЕ К6500(GaAs на 1 МГц 3-6 1000 +5В14 R1 R3 R5 VT4 VT1 1 VT2 2 3 VT5 R4 R2 VD1 VD3 VD2 VT3 Общ 7 Рис. 4.1. Принципиальная схема основного элемента интегральной схемы транзисторно - тразисторной логики +5В14 R1 R3 R5 IПОТ 0 IВХ VT4 VT1 IВЫХ IБ VD3 , 1 VD1 VD2 RН Uвых Общ Рис. 4.3. Принципиальная схема основного элемента интегральной схемы транзисторно - транзисторной логики при низком входном напряжении 7 +5В 14 1 UВХ 1 2 R1 VT1 R3 IБ О IБ VT2 VT5 R2 VD1 UВЫХ 3 VD2 IБ R4 IВЫХ VT3 Общ 7 Рис. 4.2. Распределение токов и напряжений при высоком входном логическом уровне +12 Вход VT1 Выход VD1 VT2 Общ Рис. 3.1. Принципиальная схема КМОП-инвертора