Понятие логического базиса

реклама

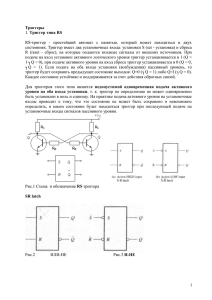

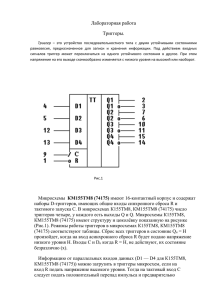

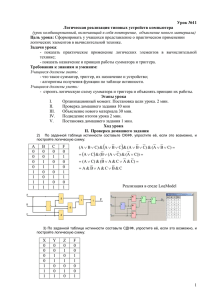

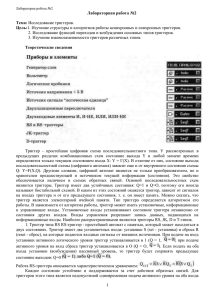

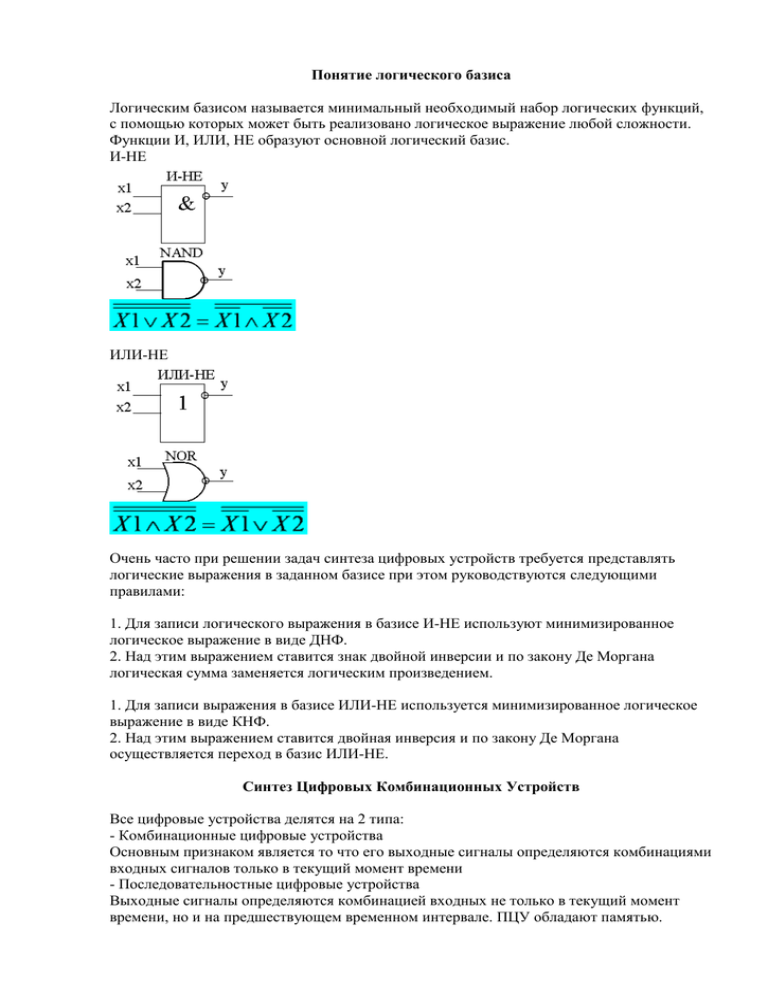

Понятие логического базиса Логическим базисом называется минимальный необходимый набор логических функций, с помощью которых может быть реализовано логическое выражение любой сложности. Функции И, ИЛИ, НЕ образуют основной логический базис. И-НЕ ИЛИ-НЕ Очень часто при решении задач синтеза цифровых устройств требуется представлять логические выражения в заданном базисе при этом руководствуются следующими правилами: 1. Для записи логического выражения в базисе И-НЕ используют минимизированное логическое выражение в виде ДНФ. 2. Над этим выражением ставится знак двойной инверсии и по закону Де Моргана логическая сумма заменяется логическим произведением. 1. Для записи выражения в базисе ИЛИ-НЕ используется минимизированное логическое выражение в виде КНФ. 2. Над этим выражением ставится двойная инверсия и по закону Де Моргана осуществляется переход в базис ИЛИ-НЕ. Синтез Цифровых Комбинационных Устройств Все цифровые устройства делятся на 2 типа: - Комбинационные цифровые устройства Основным признаком является то что его выходные сигналы определяются комбинациями входных сигналов только в текущий момент времени - Последовательностные цифровые устройства Выходные сигналы определяются комбинацией входных не только в текущий момент времени, но и на предшествующем временном интервале. ПЦУ обладают памятью. Синтез любого цифрового устройства заключается в построении его структурной схемы, которая реализует заданные правила его работы с помощью минимального количества элементов заданного базиса. Выполняется последовательно: 1. Записывается условие работы цифрового устройства: a. словесно b. таблица истинности; c. логическим выражением; d. номерами состояний; e. карты Карно. 2. Запись и минимизация логического выражения аналитически [с помощью законов алгебры логики] либо графически [карты Карно]; 3. Запись минимизированного логического выражения в заданном логическом базисе; 4. Составление структурной семы устройства на логических элементах заданного базиса. Типовые КЦУ Функционально законченные узлы, реализованные на основе элементарных логических элементов: Дешифратор (декодер) – КЦУ, которое выполняет операцию преобразования n – разрядного 2го кода в m-разрядный унитарный двоичный код. Дешифратор с числом выходов 2 в степени н называю полным иначе не полный. Из таблицы видно, что каждой комбинации трех входных элементов соответствует 8 разрядный двоичный код причем единица в этом коде присутствует только в одном из разрядов. Код в котором единица только в одном разряде называется унитарным. Единица появляется на том выходе дешифратора номер которого совпадает с номером комбинации установленной на входе. Демультиплексор – КЦУ, который выполняет функцию коммутация одноразрядного цифрового сигнала D на один из выходов y, причем управление коммутацией производится с помощью сигналов адреса. Из таблицы видно, что информационный сигнал D коммутируется на тот выход демультиплексора, номер которого совпадает с комбинацией адресных сигналов х3, х2, х1. Если на вход D подать логическую единицу, то мультиплексор превратится в дешифратор. Мультиплексор – КЦУ, который выполняет функцию коммутации одного из разрядов цифрового сигнала Di на единственный выход y. Управление коммутацией производится сигналами адреса х2, х1. Из таблицы видно, на выход коммутируется тот вход мультиплексора номер которого совпадает с комбинацией сигнала адреса. Полусумматор – КЦУ, который выполняет операцию арифметического сложения двух одноразрядных двоичных чисел. Сложение одноразрядных чисел применяется крайне редко, а для сложения много разрядных двоичных чисел эта схема не годится. У них отсутствует код переноса. Поэтому используют полный сумматор. Полный сумматор - выполняет функцию сложения трех одноразрядных двоичных чисел. A + B + C0 Такие схемы позволяют строить много разрядные сумматоры: Трех разрядный двоичный сумматор: C2 – Перенос из старшего разряда. Как следует из рисунка, сигнал меж разрядного переноса подается на вход переноса следующего разряда сумматора. A2A1A0 + B2B1B0 = 2 1 0 Арифметико-логическое устройство. Является узлом, который позволяет выполнять арифметические и логические операции над целыми двоичными числами. Это АЛУ позволяет выполнять операции над 4-х разрядными двоичными числами. Входы: А0-А3 – входы первого операнда В0-В3 – входы второго операнда М – режим [Mode], если =0, то арифметические операции, если =1 то, логические. S0-S3 - тип арифметической или логической операции С0 – входной перенос при арифметических операциях. Выходы: F0-F3 – 4-х разрядный результат операции А=В – 1, если операнд А=В С4 – перенос из старшего разряда при арифметических операциях P, G – используются при наращивании разрядности АЛУ Последовательностные цифровые устройства. ПЦУ – устройства, выходные сигналы которых, в отличие от КЦУ, зависят не только от входных сигналов в текущий момент времени, но и от сигналов на предшествующем интервале. Если в КЦУ базовой ячейкой являлся логический элемент, то в ПЦУ – триггер. ПЦУ могут быть: Асинхронные – переключение производится в момент времени определяемы информационными сигналами. Синхронные – момент переключения определяется специальным сигналом синхронизации. ПЦУ различаются по типу входов: Потенциальные – устройства с такими входами, реагируют на уровень входного сигнала. Динамические – [/] динамический вход с активным перепадом от нуля к единице, [o] – от 1 к 0, реагируют только на указанный перепад входного сигнала. Описание работы ПЦУ с помощью таблиц состояний. Триггеры Триггер – простейшее ПЦУ, которое имеет два устойчивых состояния и может хранить один бит данных. В основе любого триггера лежит бистабильная ячейка. R – Reset – установка «0» S – Set – установка «1» Положительная обратная связь (ПОС D1-D2). Верхний выход Q – прямой, нижний Q – инверсный. Благодаря наличию ПОС эта ячейка обладает свойствами: 1. Ячейка может находится в одном из 2-х устойчивых состояний. Состояние «0» - Q=0, неQ=1; Состояние «1» - Q=1, неQ=0; 2. Выходы ячейки являются парофазными (сигналы на прямом и инверсном выходах всегда противоположны.); 3. Перевести ячейку из одного устойчивого состояния в другое можно только внешним сигналом; 4. Переход ячейки из одного состояния в другое происходит лавинообразно под действием ПОС. RS-триггер Если 0 на входах RS, то триггер установится в режим хранения. Если на R подать 1 то триггер установится в состояние 0, режим установки нуля. Если на S подать 1 то триггер установится в состояние 0, режим установки нуля. Если 1 на входах RS, то триггер установится в любое из состояний, поэтому режим называется запрещенным. Если этот триггер выполнить на элементах И-НЕ, то получим RS-триггер с инверсными входами. Для такого триггера активными уровнями будут являться уровни логического нуля. Схема асинхронна. RSC-триггер Схема синхронна. Если С=0, состояние триггера не меняется, это режим хранения. Если С=1, то режим определяется сигналами на входах R и S: Три верхних – входные сигналы Т-триггер Единственный триггер, содержащий один информационный вход. Из таблицы видно: Триггер будет менять свое состояние на противоположное (переключаться) от каждой единицы поступающей на вход Т. D-триггер Синхронный триггер с одним информационным входом D. При наличии сигнала синхронизации, на выходе триггера Q устанавливается тот уровень, который присутствует на входе D. tз – время задержки. Сигнал на выходе триггера, появляется с некоторой задержкой относительно сигнала на входе D. Максимальное время задержки может быть равно периоду следования импульса синхронизации. Такой триггер часто используют для формирования временных задержек цифровых последовательностей. Триггер часто называют триггером задержки. JK-триггер Синхронный триггер с 2мя информационными входами установки J,K. В триггере отсутствует запрещенный режим работы. Т.е. триггер может использоваться как синхронный RS-триггер, либо как счетный Т-триггер. Перевести триггер в режим счета можно с использованием следующих схем включения: Типовые ПЦУ Функционально законченные узлы, построенные на триггерах различных типов. Их особенность, они могут запоминать информацию. Параллельный регистр. Предназначен для хранения n-разрядного двоичного слова( кодовой комбинации) в течении некоторого интервала времени. Регистры выполняют роль запоминающих устройств малой емкости. Их часто называют регистрами памяти. В регистре могут использоваться триггеры различных типов, однако чаще всего применяют Д-триггеры. Это четырехразрядный параллельный регистр. Основу регистра составляют 4 Д-триггера. Информационные входы каждого триггера являются внешними входами данных д3,д2,д1,д0, а прямые выходы каждого триггера образуют 4х разрядный выход данных q3,q2,q1,q0. Входы сброса R всех триггеров объединяются, и на них подается общий сигнал сброса (очистки). Для подачи общего сигнала разрешения записи объединяются коды С. Для того чтобы выполнить очистку регистра на вход R следует подать активный уровень (0) при это все триггеры установятся в состояние 0 т.е. произойдет очистка регистра. Для записи кодовой комбинации в регистр: 1. На входе сброса R установить пассивный уровень (1); 2. На входах данный д3,д2,д1,д0 установить запоминаемую кодовую комбинацию; 3. На вход разрешении записи С подать импульс записи. Передним фронтом (перепадом от 0 к 1) этого импульса, установленная на входах Д комбинация запишется в триггеры регистра и появится на выходах Q. Информация хранится до записи новой либо до выключения питания. Регистр сдвига Предназначены: 1. Хранения записанных двоичных кодовых комбинаций; 2. Преобразования последовательного двоичного кода в параллельный; 3. Преобразования параллельного двоичного кода в последовательный; 4. Выполнение операций сдвигов, записанного двоичного слова на определенное количество разрядов вправо или влево; 5. Реализации временных задержек цифровых последовательностей; 6. Формирование циклически повторяющихся кодовых последовательностей. Д3-Д0 – входы параллельной загрузки, ДС – вход последовательной загрузки, Ц – вход синхронизации, Р – вход сброса и очистки (инверсный). Может быть построен на разных триггерах. Регистр сдвига образован д-триггерами соединенными последовательно. В вычислительной технике часто используют упрощенное обозначение, как показано на рисунке: Предположим, что перед началом работы регистр очищен, т.е. на всех выходах 0.