Лекция №13 «Технологии проектирования ИСПС» . Реализация цифровых фрагментов в форме полузаказных

advertisement

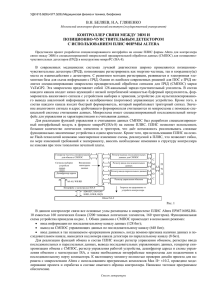

Курс «Информационные технологии в проектировании ЭВС» Лекция №13 «Технологии проектирования ИСПС» 11.3. Реализация цифровых фрагментов в форме полузаказных кристаллов (продолжение) Максимальное совпадение между характеристиками ПЛИС и БМК может быть обеспечено при совмещении в одном лице фирмы-изготовителя MPGA и фирмыизготовителя FPGA/CPLD и при наличии у нее соответствующих типов БИС. В таком случае наиболее рациональным представляется предварительная реализация проекта в форме ПЛИС. Ведущие фирмы-производители схем ПЛИС Хilinx и Altera стараются поддержать такое направление. И та и другая фирма выпускают БМК, соответствующие определенным схемам ПЛИС. В качестве примера проектной процедуры конвертации проекта на рис. 2.11 приведена процедура переноса проекта, реализованного на БИС фирмы Altera типа АРЕХ20КЕ или АРЕХ20КС, в форму БМК. Из рисунка видно, как много проверок содержит конвертационная процедура, включая проверку основных проектных правил и ограничений DRC (Design Rule-Check). В том числе, показано формирование файлов для автоматической генерации тестовых последовательностей для оборудования как общего назначения ATPG (Automatic Test Pattern Generation), так и встроенных блоков памяти ESB (Embedded System Blocks). Фирма Altera анонсировала в 2001 году выпуск БМК типа HardCopy. Семейство БМК этого типа позволяют поддерживать методологию конвертации проектов из ПЛИС типа APEX с минимальным риском иметь расхождение в поведении прототипа и конечного продукта (при условии, что логическая емкость приборов лежит в диапазоне от 400 тыс. до 1,5 млн. вентилей). Минимизация достигается сохранением всех основных ресурсов ПЛИС типа APEX при переводе ее реализации в жесткие соединения вместо соединений, определяемых памятью конфигурации. 1 Особенностью процедуры конвертации является отсутствие необходимости у проектировщика вмешиваться в ее процесс. Этот процесс не требует от проектировщика разработки и создания специальных средств тестирования (типа генерации Test-Bench), разработки тестовых векторов или временного и функционального моделирования. Естественно, что определенные тестовые проверки разработчик выполнял при разработке и проверке реализации своего проекта на ПЛИС типа APEX. Для проведения миграции требуются выходные файлы работоспособного проекта, сгенерированного САПР Quartus II для БИС типа APEX. На выполнение процесса конвертации и изготовление функциональных прототипов фирма Altera затрачивает порядка 8 недель, для выпуска промышленной партии требуется около 16 – 18 недель. Экономическая выгода применения БМК типа HardCopy видна из следующих сравнительных данных. Стоимость изготовления комплекта масок для БИС с проектными 2 нормами 0,13 мкм и с шестью слоями металла, которая выполняется по технологии стандартных ячеек, превышает 750 тыс. долларов. Поскольку к этой стоимости необходимо добавить дополнительные расходы фирмы-изготовителя БМК на подготовительные операции к проектированию и производственному процессу, то общая сумма расходов превышает 1 млн. долларов. Для проектирования БМК типа HardCopy фирма Altera обещает затраты на уровне 300 тыс. долларов. Фирмы, специализирующиеся на производстве полузаказных БИС, также стараются поддерживать технологии конвертации проектов, выполненных на схемах типа ПЛИС, что делает целесообразным проектирование по ветви FPGA-ASIC. Однако временное отставание фирм-изготовителей БИС БМК в выпуске схем, соответствующих определенному классу схем ПЛИС, от темпов снижения цены на перспективные типы ПЛИС фирмами-производителями БИС ПЛИС часто создает ситуацию, когда экономически невыгодно отказываться от выпуска продукции на основе схем ПЛИС. Целесообразность конвертации проектов из ПЛИС в форму БМК может следовать не только из экономических соображений. Как правило, помимо большей уверенности в работоспособности проекта, этот подход дает и определенные дополнительные выгоды, например, допускает работу на больших системных частотах, меньшую стоимость, меньшую потребляемую мощность и т. д. Еще одним важным моментом, который следует учитывать при поиске рациональной формы реализации конечного продукта, является отработанность у фирм технологии конвертации проектов ASIC-ASIC. Наличие таких технологий создает предпосылки для сохранения у проекта резервов за счет простоты перевода в реализации с другими и более перспективными характеристиками. Необходимость таких переводов может быть связана как с экономическими соображениями (схемы с меньшими топологическими нормами, как правило, имеют лучшие эксплуатационные характеристики и стоят дешевле), так и с возможностью реализовать проект с другими электрическими или эксплуатационными характеристиками (примером может служить перевод проекта на современные значения напряжения питания, включение проекта в систему со смешанными выходными напряжениями и т. д.). Современное возрастание сложности проектов заставляет искать технологические варианты реализации проектов с гарантированными свойствами. Одним из основных путей увеличения надежности проектирования при условии сокращения времени на проектирование является увеличение доли уже отработанных и проверенных или просто стандартных решений. Варианты реализации стандартных решений и способы их использования проектировщиком могут существенно отличаться. Непрерывно увеличивается число фирм, специализирующихся на разработке библиотек стандартных фрагментов для различных типов и видов ASIC продукции (IP-core). Процесс добавления такого стандартного фрагмента может иметь различную технологическую реализацию. Чаще всего фрагменты разрабатываются и записываются на одном из языков описания аппаратуры и вставляются в проект перед процедурой синтеза. Реже используются варианты добавления стандартных фрагментов на этапах топологического проектирования, хотя именно топологическая оптимизация может резко улучшить временные характеристики фрагмента при сохранении его размеров. Для БМК фирма-разработчик IP-core должна обеспечить простоту переноса топологии стандартного фрагмента (систему межсоединений) на произвольное место среди массива вентилей. Для технологии стандартных ячеек может использоваться как перенос топологии стандартной ячейки на любое место массива ячеек, так и фиксированное размещение в кристалле стандартных фрагментов. Фирма AMI для фрагментов первого типа, в зависимости от их сложности, использует название мегаячейка (megacell) или информационный функциональный блок (datapath function), a для второго типа — скомпилированный блок (compiled block). Скомпилированные блоки (в подавляющем большинстве случаев это те 3 или иные вариакты блоков памяти) оптимизированы по площади, скорости и потребляемой мощности, но могут размещаться только в заранее определенных местах кристалла. 4