УДК 004.421.4 КАЛИНИН П.В., РОЖКОВА Л.О., ПОТАНИН С.И.

реклама

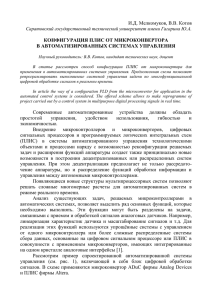

УДК 004.421.4 КАЛИНИН П.В., РОЖКОВА Л.О., ПОТАНИН С.И. P.V. KALININ, L.O. ROZHKOVA, S.I. POTANIN РАЗРАБОТКА АРХИТЕКТУРЫ ПЛИС ОБРАБОТКИ ИЗОБРАЖЕНИЙ С НЕСКОЛЬКИХ ВИДЕОКАМЕР DEVELOPMENT OF ARCHITECTURE OF THE FPGA PROCESSING IMAGES FROM MULTIPLE CAMERAS В статье рассматривается вопрос построения устройства на основе ПЛИС, которое способно обрабатывать информацию, поступающую с нескольких камер. Ключевые слова: ПЛИС, проектирование, архитектура, модули. The article discusses the issue of building device based on FPGA, which is able to process information coming from multiple cameras. Keywords: FPGA, design, architecture, module. ВВЕДЕНИЕ ПЛИС – программируемая логическая интегральная схема, которая может реализовывать определенные логические функции с помощью программных методов. Физическое ограничение быстродействия большинства современных процессоров – это последовательное выполнение команд. Архитектуры ПЛИС, за счет аппаратного распараллеливания вычислений, частично лишены этого ограничения, поэтому могут использоваться для более сложных и масштабных проектов. В настоящее время подход к проектированию больших систем заключается в грамотном сочетании архитектур ПЛИС и обычных процессоров, при котором появляется возможность обработки информации в реальном времени. С использованием таких технологий осуществляется реализация алгоритмов, предназначенных для специальных областей применения, в которых необходимо жесткое соблюдение временных ограничений. ОПИСАНИЕ УСТРОЙСТВА На базе ПЛИС можно создать устройство, которое способно получать и обрабатывать изображение с нескольких камер в режиме реального времени. Его основная функция – одновременный захват с нескольких камер как фото-, так и видео-изображения и построения панорамы. Эта технология может быть использована в устройствах, с помощью которых осуществляется как художественная, так и научная съемка. Данное устройство разработано для установки на гексакоптер и получения панорамного изображения местности. На рисунке 1 приведена структурная схема устройства, состоящая из модулей: 1. Массив камер на базе CMOS-матрицы фирмы Micron. Матрица MT9P031 является 1/2.5-дюймовой CMOS-матрицей с числом активных пикселей 2592H х 1944V. Она поддерживает в себя такие функции камеры, как кадрирование, биннинг, режим пропуска столбцов и строк, режим моментального снимка. Матрицу можно запрограммировать с помощью простого двухпроводного последовательного интерфейса. Максимальная частота кадров в режиме полного разрешения составляет 15fps. 2. Модуль оперативной памяти. Динамическая память SDRAM на 64 мегабита, которая представлена четырьмя банками, работает при напряжении 3.3 V. Внутренняя конфигурация настроена как quad-bank с синхронным интерфейсом. Рисунок 1 – Структурная схема 3. Модуль процессора реализован на микросхеме семейства MAX 10. Эта микросхема позволяет выполнять следующие функции: обработка исходных данных, управление экспозицией, формирование протокола связи с процессором, обрезка кадра, управление матрицей. Программа обработки изображения реализована на языке Verilog. 4. Модуль питания - набор микросхем, которые формируют разные напряжения питания. 5. Модуль связи. Передача обработанного изображения требует высоких скоростей передачи информации, составляющие десятки, сотни Mb/c. В данном устройстве используется последовательный интерфейс, реализованный на стандарте LVDS. Принцип работы Изображение снимается массивом камер, после чего передается в модуль процессора. Далее происходит обработка полученных данных, состоящая из следующих этапов: 1. Коррекция дисторсии. При съемке образуется искривление изображения (линейное увеличение объектов изменяется по полю зрения), которое корректируется программными средствами. 2. Коррекция виньетирования (затемнения краев изображения относительно центра, образующегося при съемке). 3. При неисправности одной из камер и потере пикселей на изображении применяется алгоритм дополнения недостающих пикселей. Если «битый» пиксель попадает в область перекрытия камер, то он восполняется из изображения другой камеры; если же нет, то применяется операция «сглаживания», то есть получения среднего значения из характеристик соседних пикселей. 4. Применение аффинных и перспективных преобразований, необходимых для сшивки полученных изображений в панораму. 5. Упаковка полученного изображения в протокол MIPI После этого итоговые данные отправляются на модуль связи, из которого могут передаваться на внешние носители. Управление модулем процессора осуществляется через интерфейс USB. Модуль оперативной памяти необходим для хранения промежуточных результатов обработки изображения. В перспективе предполагается организация конвейерной обработки данных, при которой необходимость в модуле памяти отпадет и будет нужен только небольшой оперативный буфер. ЗАКЛЮЧЕНИЕ В результате построения архитектуры, базирующейся на ПЛИС, было создано устройство, позволяющее получать и обрабатывать изображение с нескольких камер. СПИСОК ЛИТЕРАТУРЫ 1) 1/2.5-Inch 5Mp CMOS Digital Image Sensor MT9P031 Data Sheet, Rev. G – Режимдоступа: http://datasheet4u.com/datasheet/M/T/9/MT9P031_AptinaImagingCorp oration.pdf.html 2) BeMicro Max 10 Getting Started User Guide, Version 14.0 – Режимдоступа: http://download.siliconexpert.com/pdfs/2014/11/26/1/19/1/93/arrowd_/ manual/bemicrom10_getting_started.pdf Калинин Павел Валерьевич ФГБОУ ВПО «Госуниверситет – УНПК», г. Орел Студент группы 31-ИТ Email: [email protected] Рожкова Лидия Олеговна ФГБОУ ВПО «Госуниверситет – УНПК», г. Орел Студент группы 31-ИТ Email: [email protected] Потанин Степан Иванович ФГБОУ ВПО «Госуниверситет – УНПК», г. Орел Студент группы 31-ИТ Email: [email protected]