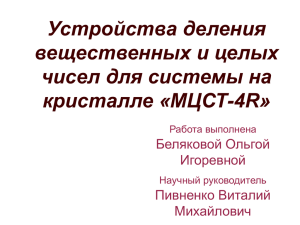

ОАО «ИНЭУМ им. И.С. Брука», ЗАО «МЦСТ» Пивненко В. М

реклама

ОАО «ИНЭУМ им. И.С. Брука», ЗАО «МЦСТ» Пивненко В. М.; ведущий инженер; email:[email protected]; тел.84991350388 Эсула О. И.; м.н.с.; email:[email protected]; тел.84991350388 Организация устройств деления в микропроцессорах разработки ЗАО «МЦСТ» Арифметическое устройство (АУ) в микропроцессоре исполняет целочисленные и вещественные операции (сложение, умножение, деление и др.). АУ состоит из 2 групп исполнительных устройств, образующие два канала, один из которых выполняет целочисленные и вещественные операции, а другой - только целочисленные операции. В микропроцессорах (МП) «R500» и «Эльбрус» использованы мощные устройства деления, вырабатывающие 9 битов частного за такт. В МП «Эльбрус» устройство деления работает и в поточном режиме. Целочисленные и вещественные операнды обрабатываются одним устройством. Скорость вычислений очень высокая и слабо зависит от соотношения величины операндов. Целые числа необходимо преобразовать к вещественному виду, а результат вычисления — снова к целому. Недостатком совместной реализации двух видов делений является невозможность полного распараллеливания целочисленной и вещественной арифметики. В МП «МЦСТ-4R» устройства целочисленного и вещественного делений находятся в разных кластерах. Из соображений экономии площади устройство целочисленного деления спроектировано по классической схеме (1 бит частного за такт). Такая схема не очень эффективна для больших значений делителя и малом частном, а также в случае, когда делитель мал, а делимое велико. Увеличения быстродействия устройства целочисленного деления можно достигнуть совмещением операндов по старшим значащим битам, что позволяет исключить пустые итерации. Это дает возможность планировать цифру частного по старшим битам операндов и использовать любой подходящий алгоритм из арсенала вещественного деления для сокращения общего количества итераций (несколько битов частного в каждой). При использовании SRT-алгоритма не требуется вычисления точного знака частичного остатка, что позволяет исключить из цикла полноразрядное суммирование. Остаток делимого сохраняется в избыточной форме, в виде сумм и переносов. Цифры частного также формируются в избыточной форме, а в конце операции приводятся к нормальному виду. Отсутствие сумматора с приведением переносов существенно сокращает время одной итерации и позволяет выполнить несколько шагов за один машинный цикл. Существуют реализации, где более простые схемы с получением 2 битов за такт соединены каскадно для получения 4 битов.