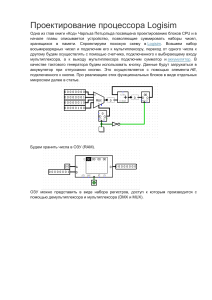

Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования САНКТ-ПЕТЕРБУРГСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ПЕТРА ВЕЛИКОГО (ФГАОУ ВО СПбПУ) Институт электроники и телекоммуникаций Высшая школа электроники и микросистемной техники ОТЧЕТ ПО ЛАБОРАТОРНОЙ РАБОТЕ Мультиплексор (семестр 8) Студент группы 4931104/00301 Преподаватель 14.03.2024 А.В. Усанов подпись, дата инициалы и фамилия 14.03.2024 В.А.Антропов подпись, дата инициалы и фамилия Санкт-Петербург 2024 Цель работы Реализация мультиплексора 4 в 1 в программном пакете Xilinx ISE: На уровне потока данных На уровне логических вентилей С использованием оператора «?» Задание на выполнение лабораторной работы: 1) Реализовать все три вида мультиплексоров 2) Проанализировать и сравнить результаты моделирования для всех трёх реализаций мультиплексора 3) Проанализировать и сравнить нетлисты после трансляции и маппирования. 2 1 Устройство мультиплексора Мультиплексор 4 в 1 – это устройство, позволяющее с помощью двух управляющих сигналов подключать свой выход к одному из четырёх входов. В таблице 1 представлена таблица истинности мультиплексора 4 в 1 Таблица 1 – таблица истинности мультиплексора 4 в 1 S1 0 0 1 1 S0 0 1 0 1 Out I0 I1 I2 I3 Где S1 и S0 – управляющие сигналы, Out – выход мультиплексора, I0 – I4 – входы. Такой мультиплексор можно описать выражением: (𝑠̅1 ∧ 𝑠̅0 ∧ 𝑖0 ) ∨ (𝑠̅1 ∧ 𝑠0 ∧ 𝑖1 ) ∨ (𝑠1 ∧ 𝑠̅0 ∧ 𝑖2 ) ∨ (𝑠1 ∧ 𝑠0 ∧ 𝑖3 ), соответствует схема, приведённая на рисунке 1. Рисунок 1 – схема мультиплексора 4 в 1 3 которому 2 Реализация на уровне логических вентилей Логические вентили представляют собой наиболее простые компоненты логической схемотехники, такие как элементы и, или, не, или не, и не, исключающее или, с различным числом входов. Для реализации схемы представленной на рисунке 1 был написан код, приведённый в листинге 1. Листинг 1 – Код реализации мультиплексора на уровне логических вентилей module four_to_one_muxlogven(out, i0, i1, i2, i3, s1, s0); output out; input i0, i1, i2, i3, s1, s0; wire s1n, s0n; wire y0, y1, y2, y3; not (s1n, s1); not (s0n, s0); and (y0, i0, s1n, s0n); and (y1, i1, s1n, s0); and (y2, i2, s1, s0n); and (y3, i3, s1, s0); or (out, y0, y1, y2, y3); endmodule Первым делом создаётся модуль, названный four_to_one_muxlogven. Он имеет 7 выводов, названия которых перечислены в скобках. Далее указывается что выходом мультиплексора является вывод out, а остальные выводы являются входами. Следующие две строки отвечают за создание внутренних промежуточных переменных wire. Последующие семь строк кода создают и связывают между собой логические вентили в соответствии со схемой, где первым элементом в скобке является выход вентиля, а последующими – входы. Endmodule выполняет роль вышеописанного модуля. 4 «закрывающей скобки» кода 3 Реализация на уровне потока данных Написание кода на уровне потока данных характерно тем, что, в отличии от уровня логических вентилей, здесь не задаются конкретные компоненты логической схемотехники, а лишь указывается выражение, описывающее связь выходного значения блока с входными. Для реализации схемы представленной на рисунке 1 был написан код, приведённый в листинге 2. Листинг 2 – Код реализации мультиплексора на уровне потока данных module four_to_one_muxdataflow(out, i0, i1, i2, i3, s1,s0); output out; input i0, i1, i2, i3, s1, s0; assign out = (~s1 & ~s0 & i0)|(~s1 & s0 & i1)|(s1 & ~s0 & i2)|(s1 & s0 & i3); endmodule Первым делом создаётся модуль, названный four_to_one_muxdataflow и указываются его входы и выходы, аналогично предыдущему листингу. Далее с помощью указывается assign выходное значение мультиплексора, а вернее логическое выражение, связывающее его входы и выход в соответствии с выражением, казанным в первом пункте, где ~ обозначает отрицание, & - логическое «и», | - логическое «или». 5 4 Реализация с использованием оператора «?» Оператор «?» является тернарным оператором условия, работающий по следующей схеме: УСЛОВИЕ ? ИСТИНА : ЛОЖЬ, где условие – значение имеющее логический ноль или единицу, истина – значение используемое при условие=1, ложь – значение, используемое при условие=0. Для реализации схемы представленной на рисунке 1 был написан код, приведённый в листинге 3. Листинг 3 – Код реализации мультиплексора с использованием оператора «?» module four_to_one_muxcond(out, i0, i1, i2, i3, s1,s0); output out; input i0, i1, i2, i3, s1, s0; assign out = s1 ? (s0 ? i3 : i2): (s0 ? i1 : i0) ; endmodule Код аналогичен предыдущему случаю за исключением 4 строки, в которой и используются тернарные операторы «?». Таким образом, если S1=0 и S0=0 на выходе будет i0, S1=0 и S0=1 на выходе будет i1, S1=1 и S0=0 на выходе будет i2, S1=1 и S0=1 на выходе будет i3, 6 5 Блок тестовых воздействий Блок тестовых воздействий необходим для проверки работоспособности разработанного устройства. В нём указываются входы и выходы схемы, а также какие значения и в какие моменты времени необходимо на них подать для проведения тестирования. В листинге 4 приведён код блока тестовых воздействий Листинг 4 – Код блока тестовых воздействий module four_to_one_mux_TB; reg i0; reg i1; reg i2; reg i3; reg s0; reg s1; wire out1; wire out2; wire out3; four_to_one_muxlogven uut1 (.out(out1), .i0(i0), .i1(i1), .i2(i2), .i3(i3), .s1(s1), .s0(s0)); four_to_one_muxdataflow uut2 (.out(out2), .i0(i0), .i1(i1), .i2(i2), .i3(i3), .s1(s1), .s0(s0)); four_to_one_muxcond uut3 (.out(out3), .i0(i0), .i1(i1), .i2(i2), .i3(i3), .s1(s1), .s0(s0)); initial begin i0 = 0; i1 = 0; i2 = 0; i3 = 0; s1 = 0; s0 = 0; #100; i0=1; i1=0; i2=0; i3=0; #50 $display ("i0= %b, i1= %b, i2= %b, i3= %b,", i0, i1, i2, i3); s1=0; s0=0; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); i0=0; i1=1; i2=0; i3=0; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); s1=0; s0=1; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); i0=0; i1=0; i2=1; i3=0; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); s1=1; s0=0; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); i0=0; i1=0; i2=0; i3=1; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); s1=1; s0=1; #50 $display ("s1= %b, s0= %b, out1= %b, out2= %b, out3= %b", s1, s0, out1, out2, out3); end endmodule Первым делом указывается название блока тестовых воздействий и перечисляются переменные типа wire и reg. Переменным типа reg можно присваивать значения в процессе тестирования модуля. Далее инстанцируются все три созданных мультиплексора, входы и 7 выходы которых соединяются с заданными выше переменными. Входы всех мультиплексоров подключены вместе, а выходы раздельно, чтобы можно было отслеживать их результаты. Все переменные сбрасываются в ноль, после чего производится ожидание в течении 100 условных единиц времени. После этого нулевому входу присваивается логическая единица, а все мультиплексоры уже переключены на свои нулевые входы, в результате чего на выходах должны быть единицы – значения с нулевого входа. Далее эта проверка повторяется со всеми остальными выходами. Для наглядности приход управляющих сигналов и изменение значений входов происходят рассинхронизированно. Это позволяет убедиться, что мультиплексоры действительно передают входное значение на выход, а не просто всё время работы сохраняют на своём выходе логическую единицу. На рисунке 2 представлены временные диаграммы, полученные в результате моделирования разработанных мультиплексоров, а на рисунке 3 – результаты вывода в консоль. Рисунок 2 – временные диаграммы Рисунок 3 – результаты вывода в консоль Видно, что все три мультиплексора работают и выдают одинаковые результаты. Информация в консоли соответствует временным диаграммам и таблице истинности мультиплексора. 8 6 Нетлисты Нетлист можно определить как схему вентилей с их межсоединениями. На этапе трансляции происходит перевод из текстового HDL описания модулей в промежуточную схему, пригодную для дальнейшей оптимизации. На рисунках 4, 5 и 6 представлены нетлисты после трансляции для мультиплексоров на уровне логических вентилей, потока данных и с использованием тернарного оператора «?» соответственно. Рисунок 4 – нетлист после трансляции для мультиплексора на уровне логических вентилей 9 Рисунок 5 – нетлист после трансляции для мультиплексора на уровне потока данных Рисунок 6 – нетлист после трансляции для мультиплексора с использованием тернарного оператора «?» 10 Из представленных нетлистов видно, что первые две реализации оказались идентичны. В первом случае количество вентилей, и их связи были сразу определены в момент текстового описания модуля. Во втором случае выражение (𝑠̅1 ∧ 𝑠̅0 ∧ 𝑖0 ) ∨ (𝑠̅1 ∧ 𝑠0 ∧ 𝑖1 ) ∨ (𝑠1 ∧ 𝑠̅0 ∧ 𝑖2 ) ∨ (𝑠1 ∧ 𝑠0 ∧ 𝑖3 ) было представлено при трансляции через соответствующие элементы логической схемотехники. Учитывая, что это выражение соответствует схеме, представленной на рисунке 1, реализация нетлиста, повторяющего нетлист для уровня логических вентилей вполне ожидаемо. В третьем случае нетлист оказался отличным от двух предыдущих. Мультиплексор 4 в 1 был реализован на основе 3 мультиплексоров 2 в 1. Действительно, условный оператор «?» можно представить как мультиплексор 2 в 1, где управляющим сигналом является «условие», а входами варианты «истина» и «ложь». Такая реализация и была произведена при трансляции. Следующим шагом после трансляции являются оптимизация и маппирование. Маппирование – это преобразование нетлиста из базовых вентилей к набору вентилей из библиотеки. То есть использование вместо отдельных элементов «и» «или» «не» и др. сразу готовых «блоков», имеющихся в библиотеке и на кристалле выбранного ПЛИС. Нетлисты для всех трёх мультиплексоров после маппирования оказались идентичны. Они представлены на рисунке 7. 11 Рисунок 7 – нетлисты после маппирования Видно, что всю работу выполняет микросхема lut6. Она имеет обозначение DFD5DAD08F858A80, её внутренняя схема представлена на рисунке 8. Рисунок 8 – схема DFD5DAD08F858A80 12 Логическое выражение, описывающее работу микросхемы имеет следующий вид: O = ((I0*!I2*I3)+(!I0*!I2*I4)+(!I0*I2*I5)+(I0*I1*I2)), что и является выражением для мультиплексора 4 в 1. Таким образом можно сделать вывод, что для всех трёх вариантов в итоге используется lookup table, соответствующую мультиплексору 4 в 1. 13 имеющий таблицу истинности, ЗАКЛЮЧЕНИЕ В результате работы были реализованы мультиплексоры 4 в 1 на уровне логических вентилей, потока данных и с использованием тернарного оператора «?». Все три реализации были протестированы и оказались работоспособными, их временные диаграммы идентичны, а их работа соответствует таблице мультиплексора. Были получены и сравнены нетлисты после трансляции и после маппирования. Подводя итог, можно сказать, что эта лабораторная работа позволяет студентам ознакомиться с принципами работы в Xilinx ISE и устройством мультиплексоров, а так же этапами разработки. Полученные знания будут полезны для дальнейшего обучения и работы по специальности. 14