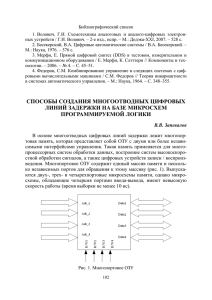

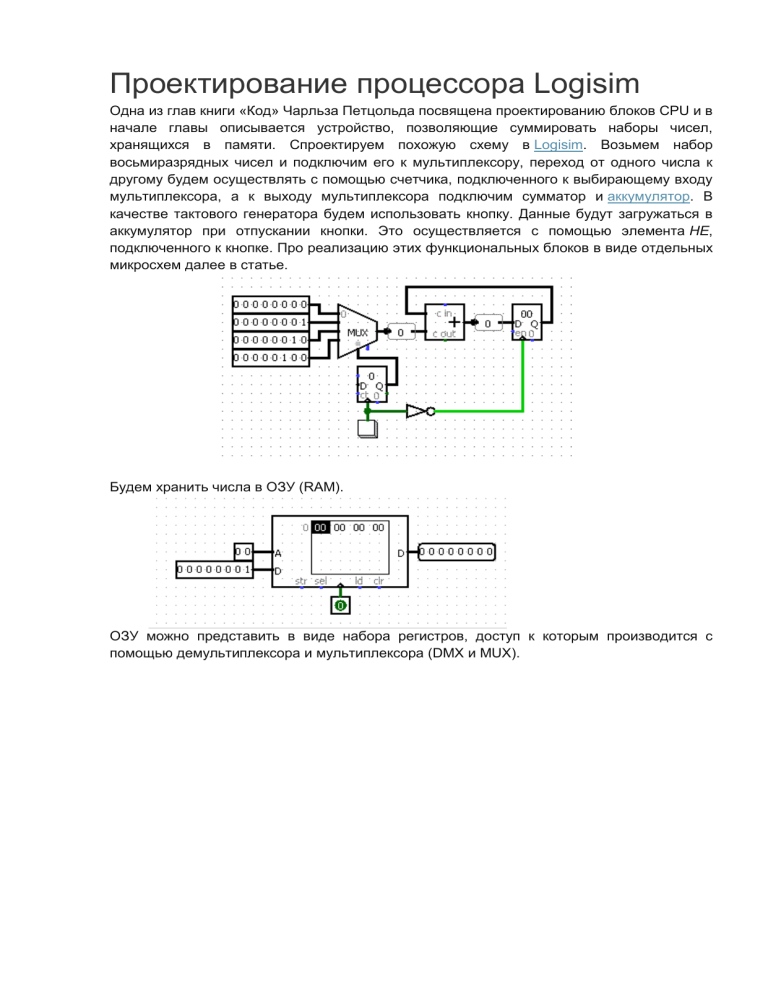

Проектирование процессора Logisim Одна из глав книги «Код» Чарльза Петцольда посвящена проектированию блоков CPU и в начале главы описывается устройство, позволяющие суммировать наборы чисел, хранящихся в памяти. Спроектируем похожую схему в Logisim. Возьмем набор восьмиразрядных чисел и подключим его к мультиплексору, переход от одного числа к другому будем осуществлять с помощью счетчика, подключенного к выбирающему входу мультиплексора, а к выходу мультиплексора подключим сумматор и аккумулятор. В качестве тактового генератора будем использовать кнопку. Данные будут загружаться в аккумулятор при отпускании кнопки. Это осуществляется с помощью элемента НЕ, подключенного к кнопке. Про реализацию этих функциональных блоков в виде отдельных микросхем далее в статье. Будем хранить числа в ОЗУ (RAM). ОЗУ можно представить в виде набора регистров, доступ к которым производится с помощью демультиплексора и мультиплексора (DMX и MUX). Гарвардская архитектура Предположим, в ОЗУ хранится набор чисел, а нам нужно сложить все числа и сохранить результат (в свободную ячейку). Будем хранить команды («сложить» и «сохранить») в одном ОЗУ, а обрабатываемые числа — в другом. Такой способ хранения является отличительным признаком Гарвардской архитектуры. Команда «1» будет записывать число из сумматора в аккумулятор, команда «2» будет записывать число из аккумулятора во 2-ое ОЗУ. Архитектура фон Неймана Далее, будем хранить инструкции и данные в одном ОЗУ. Такой способ хранения является отличительным признаком архитектуры фон Неймана. В первых четырех разрядах восьмиразрядной ячейки памяти будет храниться команда, во вторых четырех разрядах будет храниться адрес (прямая адресация). Будем загружать адрес и команду в отдельные регистры, а затем с помощью мультиплексора переходить по сохраненному адресу. Для записи данных в ОЗУ будем сначала загружать данные во временный регистр Temp (иначе в ОЗУ запишутся инструкции, а не данные), а потом в аккумулятор Асс. Запись данных в Temp и Асс будем производить по заднему фронту. Будем складывать, например, числа 2 и 3, которые лежат в ячейках 8 и 9, а сохранять результат в ячейку с адресом a. Добавим также возможность совершать безусловные переходы. Реализуем устройство, в котором будет выполняться всего одна команда — команда безусловного перехода. Для этого на счетчик, генерирующий адрес, будем отправлять четыре младших разряда (собственно, адрес), а на порт загрузки будем подавать команду, хранящуюся в старших разрядах ячейки памяти. Например, для прыжка в ячейку с адресом 2 используется команда 82. Добавим команду безусловного перехода в предыдущую схему. Добавим к схеме терминал для демонстрации того, как ассемблерные инструкции преобразуются в машинный код. 1110000 Добавим конечный автомат для обработки последовательностей поступающих символов. Семизначный код буквы «i» равняется 1101001 Семизначный код буквы «n» равняется 1101110 Семизначный код буквы «p» равняется Автомат переходит в следующее состояние, если после букы «i», а затем «n» поступает буква «p» Добавим команду out