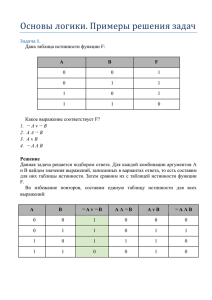

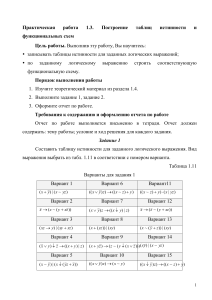

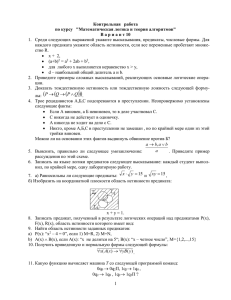

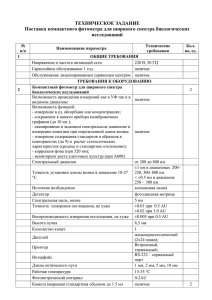

Федеральное бюджетное государственное учреждение Высшего профессионального образования РОССИЙСКИЙ ГОСУДАРСТВЕННЫЙ ГИДРОМЕТЕОРОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ Кафедра «Морских информационных технологий» Отчет по лабораторной работе №3 По дисциплине: «Схемотехника» Тема: «Исследование основных видов регистров в ALTERA MAX+PLUS II» Выполнили: студенты гр. КВ-Б19-2 Оханов Р.А. Преподаватель: Большаков В.А. Санкт-Петербург 2022 Исследование основных видов регистров в ALTERA MAX+PLUS II Цель работы: исследование регистров с параллельной записью информации и сдвигового регистра. 1. Исследование регистра Модуль 74112 Данный модуль содержит: • инверсные входы предварительной асинхронной установки 1PRN, 2PRN и сброса 1CLRN, 2CLRN; • информационные входы 1J, 1K и 2J, 2K; • входы синхронизации 1CLK, 2CLK (синхронизация осуществляется отрицательным фронтом импульса); • выходы прямые 1Q, 2Q и инверсные 1QN, 2QN. В диапазоне 0-300 ns видна работа первого JK триггера, который в данном случае работает под управлением асинхронных инверсных входов установки и сброса (1PRN и 1CLRN). • Прямой выход 1Q устанавливается в 1 при 0 на входе 1PRN и 1 на входе 1CLRN. Это видно на диапазоне 0-150 ns. (I строка таблицы истинности). • Прямой выход 1Q устанавливается в 0 при 1 на входе 1PRN и 0 на входе 1CLRN. Это видно на диапазоне 150-300 ns. (II строка таблицы истинности). • Комбинация 1PRN = 0, 1CLRN = 0 является запрещённой. Это видно на диапазоне 300-1000 ns. (III строка таблицы истинности). В диапазоне 300-1000 ns видна работа второго JK триггера, в котором в данном случае функции входов управления и сброса выполняют входы 2J и 2K. На входы 2PRN и 2CLRN подана логическая единица. Синхронизация осуществляется отрицательным фронтом импульса на входе 2CLK. • Прямой выход 2Q устанавливается в 1, а 2QN в 0 при 1 на входе 2J и 0 на входе 2K. Это видно на диапазоне 320-340 ns. (V строка таблицы истинности). • При 2J = 1 и 2K = 1 в момент синхронизации происходит переключение. Это видно на диапазоне 360-380 ns. (VII строка таблицы истинности). • Прямой выход 2Q устанавливается в 0, а 2QN в 1 при 0 на входе 2J и 1 на входе 2K. Это видно на диапазоне 480-500 ns. (VI строка таблицы истинности). • При 2CLK = 1 значение на выходах 2Q и 2QN сохраняются (вне зависимости от 2J и 2K). Это видно на диапазоне 340-360 ns. (VIII строка таблицы истинности). Тоже самое происходит в момент синхронизации при 2J = 0 и 2K = 0. Это видно на диапазоне 440-450 ns. (IV строка таблицы истинности). 2. Исследование регистра Модуль 74273 Модуль содержит: • восемь информационных входов D; • инверсный вход сброса CLRN; • синхронизирующий вход CLK; • восемь прямых выходов Q. • Ввод информации – параллельный. На диаграмме, представленной выше, видна работа регистра модуль 74273. На входы D1…D4 подаётся логическая единица, на входы D5…D8 подаётся логический ноль. • При CLRN = 0 на всех выходах Q1…Q8 устанавливается ноль (вне зависимости от CLK и D1…D8). Это видно на диапазоне 0-100 ns. (I строка таблицы истинности). • В момент синхронизации при CLRN = 1 и D = 1 на соответствующих выходах Q устанавливается 1. В данном примере на выходах Q1…Q4. Это видно на диапазоне 123-160 ns. (II строка таблицы истинности). • В момент синхронизации при CLRN = 1 и D = 0 на соответствующих выходах Q устанавливается 0. В данном примере на выходах Q5…Q8. Это видно на диапазоне 123-160 ns. (III строка таблицы истинности). • При CLK = 1 и CLRN = 1 значение на всех выходах Q сохраняется (вне зависимости от D). Это видно на диапазоне 160-200 ns. (IV строка таблицы истинности). 3. Исследование регистра Модуль 74198 Модуль содержит: • вход установки CLRN; • синхронизирующий вход CLK; • входы выбора режима работы S1 и S0; • последовательные входы приема данных SLSI (сдвиг данных влево) и SRSI (сдвиг данных вправо); • параллельные входы приема данных A, B, C, D, E, F, G и H; • выходы QA, QB, QC, QD, QE, QF, QG и QH. 3.1 Преобразование последовательного кода в параллельный. • Ввод информации – последовательный. • Сдвиг – вправо. В данном случае регистр исследуется, как преобразователь последовательного кода в параллельный. На всём диапазоне видно преобразование последовательного кода в параллельный в режиме сдвига вправо. Был использован следующий вариант подачи сигналов: SRSI – вход, через который подаётся последовательный код; S1 = 0, S0 = 1 – установка режима сдвига вправо. Выходной сигнал формируется, начиная с QA. Работа регистра в данном режиме соответствует IV и V строкам таблицы истинности. • Ввод информации – последовательный. • Сдвиг – влево. На всём диапазоне видно преобразование последовательного кода в параллельный в режиме сдвига влево. Был использован следующий вариант подачи сигналов: SLSI – вход, через который подаётся последовательный код; S1 = 1, S0 = 0 – установка режима сдвига влево. Выходной сигнал формируется, начиная с QH. Работа регистра в данном режиме соответствует VI и VII строкам таблицы истинности. 3.2 Преобразование параллельного кода в последовательный. • Ввод информации – параллельный. В данном случае регистр исследуется, как преобразователь параллельного кода в последовательный. Для этого был задействован режим параллельной загрузки входной информации (S1 = 1; S0 = 1 при CLRN = 1), а затем сдвиг вправо (S1 = 0, S0 = 1). Ввод осуществляется через входы A, B, C, D, E, F, G и H, а вывод осуществляется через QH или QA (в данном случае через QH). Преобразование параллельного кода в последовательный в данном случае соответствует III, IV и V строке таблицы истинности. Вывод: в ходе выполнения данной лабораторной работы мы изучили работу регистров с параллельной записью информации и сдвигового регистра.