Основы цифровой электроники (учебное пособие "ЛЭТИ")

advertisement

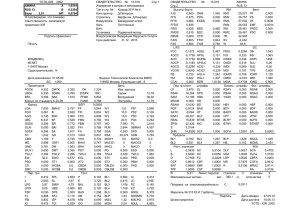

1 ОСНОВЫ ТЕОРИИ ПЕРЕКЛЮЧАТЕЛЬНЫХ ФУНКЦИЙ 1.1 Основные аксиомы, теоремы и тождества алгебры логики Обозначения переменных – x, y, z. Возможные значения переменных 0 и 1 (булева алгебра). В алгебре логики определены: Отношение эквивалентности (=). Операции: Дизъюнкция (или, or, ) : x y , аналоги x or y , x + y ; Конъюнкция (и, and, &, ) : x & y , x y , аналоги x and y , x y ; Инверсия (отрицание, не, not) : x , y , аналоги not x , ~ x . Свойства отношения эквивалентности: Рефлексивность: x x Симметричность: если x y , то y x Транзитивность: если x y и y z , то x z Аксиомы алгебры логики (АЛ): Эквивалентность (есть только два значения): x 0 , если x 1 x 1 , если x 0 Дизъюнкция: 0 0 0 , 0 1 1 0 1, 1 1 1 0 1 0 0 1 1 1 1 Конъюнкция: 0 0 0 , 1 0 0 1 0 , 1 1 1 0 1 0 0 0 1 0 1 Отрицание: 0 1, 1 0 1 Теоремы АЛ: 1. Идемпотентные зоны: x x x ; x x x 2. Коммутативные: x y y x ; x y y x 3. Ассоциативные: ( x y) z x y z 4. Дистрибутивные: x y z x y z x y z x y x z x y z x y x z Порядок выполнения операций в логическом выражении: 1. Конъюнкция или скобки; 2. Дизъюнкция. 5. Двойственности (де Моргана) x y x y : ; x y x y 6. Отрицания: x x 1 ; x x 0 0 x x ; 1 x x 1 x 1 ; 0 x 0 Таблица истинности «ИЛИ» 0 1 x x 0 0 1 x x 1 1 1 1 1 x x 1 x 1 Таблица истинности «И» x x 1 1 x 0 1 x x 0 0 0 0 0 1 0 1 x x x 0 x x 0 x x x x x y x ; x x y x 7. Двойного отрицания: 8. Поглощения: Доказательство: x x y x 1 x y x 1 y x 1 x 9. Склеивания: x y x y x ; x x y x y x y x y x ; x x y x y Операция сумма по модулю 2 (исключающее ИЛИ): Сумма по модулю – остаток от деления самого числа на модуль. Сумма по модулю два ( , xor) x y , аналог x xor y x y x y x y x y x y x y 2 x 0 x 0 x Таблица истинности «Исключающее ИЛИ» 0 1 x x 0 0 1 x x 1 1 0 x x x x x 1 0 x x x 0 1 Свойства Коммутативность: x y y x Ассоциативность: x y z x y z Дистрибутивность: x y z x y x z Порядок выполнения операций в логическом выражении: 1. Конъюнкция () ; 2. Сумма по модулю два ( ); 3. Дизъюнкция ( ) . 1.2 Позиционные системы счисления Любое целое положительное последовательности символов: число можно представить в виде en1...e p ...e1e0. Вес каждого символа е р равен q p ( q – основание системы счисления). e p 0, 1, , q 1 E en 1e p e1e0 q n 1 e pq p p 0 Примеры десятичная система e p 0, 1, , 9 ; 208310 2 103 0 102 8 101 3 100 ; двоичная система e p 0, 1 ; восьмеричная система e p 0, 1, , 7 ; шестнадцатеричная система e p 0, 1, , 9, A, B, C, D, E, F . 3 Таблица чисел в 2,8,10,16 -ичных системах счисления Основание системы счисления (q) Основание системы счисления (q) 10 16 2 10 8 2 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 А B C D E F 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 000 001 010 011 100 101 110 111 Одному символу 16-ичной системы счисления соответствуют Одному символу 8-ичной системы счисления соответствуют 4 двоичных символа ( 24 16 ) 3 двоичных символа ( 23 8 ) Примеры: 1210 С16 11002 148 201510 ____16 ____ 2 ____8 2015 -16 41 -32 95 -80 15 16 125 -112 13 16 7 201510 = 7DF16 = 0111 1101 11112 011 111 011 1112 = 37378 4 Перевод чисел в десятичную систему счисления 110112 ___10 Вес 24 q2 1 3758 ___10 Вес q 8 23 1 2AC16 ___10 Вес q 16 22 0 21 1 20 1 1 24 1 23 0 22 1 21 1 20 27 82 3 81 7 80 5 3 82 7 81 5 80 253 162 161 160 2 A C 2 162 10 161 12 160 684 Операции - сложение / вычитание X xn1,.., x0 , Y yn1,.., y0 S X Y 24 23 22 21 20 1 s4 1 1 1 s3 1 0 0 s2 1 1 0 s1 0 1 1 s0 1 1 1 0 24 23 22 21 20 1 1 1 1 s3 1 0 0 1 s2 1 0 1 1 s1 0 1 1 0 s0 + – - умножение s4 1 X xn 1,.., x0 , Y yn 1,.., y0 S X Y s2n 1,.., s0 5 вес разряда =X=1410 =Y=1110 =S=2510 =S c (carry, перенос) вес разряда =X=2510 =Y=1110 =S=1410 =S c (заем) 27 26 25 24 + 0 1 0 p5 1 0 p6 1 p7 1 0 0 0 p4 23 22 21 20 1 1 1 1 0 1 1 p3 1 0 1 0 0 0 1 0 1 1 1 1 1 p2 1 p1 1 p0 вес разряда =X=1310 =Y=1110 =P0=1310 =P1=2610 =P2=010 =P3=10410 =P=14310 =P - деление X Y D R – 1 1 1 1 – 1 0 1 – – – 2 1 1 1 5 3 2 1 1 1 0 1 1 0 =X 0 7 3 =R 1 1 1 0 1 0 0 1 0 =X 0 0 0 1 0 1 1 0 0 1 0 1 1 1 1 3 9 =Y =D 1 1 1 0 0 0 1 1 1 =Y =D =R Двоично-десятичный код (код 8-4-2-1, binary-coded decimal, BCD) – каждый десятичный разряд числа записывается в виде его четырёхбитного двоичного кода. 010 0000 ; 110 0001 ;... ; 910 1001 Пример 202310 0010 0000 0010 0011 6 операции над BCD числами + 5 4 9 + 0 0 1 1 1 0 0 0 0 1 0 1 правило – если код результата больше 1001, то надо прибавить 0110 + 1 5 9 4 + + 1 1 0 1 1 0 0 1 0 1 1 1 0 0 1 1 0 1 1 0 0 0 > 1 0 0 1 4 Код Грея Пример кода с соседним кодированием чисел, когда соседние числа отличаются только одним битом. B b2 , b1, b0 – двоичный код G g2 , g1, g0 – код Грея Правило перевода двоичного числа в код Грея G B B , где – сдвиг числа на один разряд вправо g k bk bk 1 , k 0,1,..., n 2 g n 1 bk 1 b2 0 0 0 0 1 1 1 1 b1 0 0 1 1 0 0 1 1 b0 0 1 0 1 0 1 0 1 g2 0 0 0 0 1 1 1 1 g1 0 0 1 1 1 1 0 0 g0 0 1 1 0 0 1 1 0 0 0 1 1 7 0 0 0 1 0 1 1 0 1 1 1 0 1 1 Перевод кода Грея в двоичное число bk bn 1 bn 2 ... bk 1 bk bn 1 g k 1 b2 0 0 0 0 1 1 1 1 b1 0 0 1 1 0 0 1 1 b0 0 1 0 1 0 1 0 1 g2 0 0 0 0 1 1 1 1 g1 0 0 1 1 1 1 0 0 , k 0,1,..., n 2 g0 0 1 1 0 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 0 1 1 1 1 1 = 0 1 0 = 0 1 = 0 0 1 = 0 1 1 Унитарный код – содержит символ «1» только в одной позиции n-разрядного кода. Пример. Представить числа 0, 1, 6, 7 в виде восьмиразрядного унитарного кода 08 0000 0001 ;18 0000 0010 ; 68 0100 0000 ; 78 1000 0000 1.3 Переключательные функции Переключательная функция – это логическое выражение, содержащее переменные, соединенные между собой операциями алгебры логики. f f xn , xn1, ..., x1 , так как все x p 0,1 , то общее число точек, определяющее функцию равно 2 0 0, 0,, 0 1 0, 0, ,1 n 2n 1 1,1,,1 Функция двух переменных задается в четырех точках, каждая функция представляется 4-разрядным десятичным числом (столбец в таблице). 8 Таблица основных операций АЛ i x2 x1 x2 x1 x2 x1 x2 x1 f 0 0 0 0 0 0 a0 1 0 1 1 0 1 a1 2 1 0 1 0 1 a2 a3 3 1 1 1 1 0 Функция называется полностью определенной, если она задана «0» или «1» в каждой из 2n точек. Функция называется неполностью определенной, если она не задана хотя бы в одной точке. Функция не заданная в одной точке доопределяется двумя способами. Функция не заданная в m ( m n ) точках доопределяется 2m способами. Символ ”Ф” – неопределенное значение функции. Если значения не заданы ни в одной точке, тогда это полностью неопределенная функция ( ħ ). Логические элементы, выполняющие операции АЛ, представленных в таблице выше. Обозначения США Обозначения РФ 1 & =1 1 9 1.4 Принцип и закон двойственности Принцип двойственности: Если f ,0,1/ ,& g ,0,1/ ,& , где xn ,..., x1 , то f ,1,0 / &, g ,1,0 / &, Пример: Если 1 0 1 , то 0 &1 0 То есть если «0» и «1» заменить и также поменять операции конъюнкции и дизъюнкции, то результат не изменится. Закон двойственности: f / ,& f / &, , где xn ,, x1 , xn ,, x1 Пример: Если f x2 x1 x2 x1 , то f x2 x1 x2 x1 Введем обозначения, которые будем использовать в дальнейшем: n n V x p xn x1 ; p 1 x p xn x1 p 1 тогда закон двойственности: n n p 1 p 1 V xp xp n n p 1 p 1 x p V x p 1.5 Теоремы разложения Любую функцию n переменных можно разложить по переменным x p : f xn ,, x p ,, x1 x p f xn ,,0,, x1 x p f xn ,,1,, x1 Пример: x y x 0 y x 1 y x y x y По принципу двойственности: f xn , x p , x1 x p f xn ,1, , x1 & x p f xn ,0, , x1 10 1.6. Первичные термы, минтермы, макстермы и их свойства Переменные, инверсии переменных, их конъюнкции и дизъюнкции называются термами. Первичные термы – это сами переменные x p и их инверсии x p . Обозначим xp ep x p , e p 0 , x , e 1 p p e тогда x p p e p x p e p x p e p x p , где e p 0 или 1. Основные соотношения: 0 1 1. x p1 x p x p ; x p0 x p x p 2. xp 3. x p ep ep xp ep xp ep 1, x p e p 0, x p e p Минтерм (обобщение конъюнкции) – функция n переменных вида n Ki x p ep , p 1 где xn ,, x p , , x1 , i en e1, e p 0 или 1 Свойства минтермов: 1. 1 , i в одной точке Ki 0 , j i n 1.1 Ki i e p p 1 ep 1 ; где i en e p e1 , i en e p e1 2. Ki K j 0 , при i j 2n 1 3. V Ki 1 i 0 Минтермы двух переменных: Ki x2e2 x1e1 где x2 , x1 K0 x2 x1 , K1 x2 x1, K2 x2 x1 , K3 x2 x1 , 11 Пример: найти K5 функции трех переменных n 3 , x3 , x2 , x1 i 510 1012 K5 x13 x20 x11 x3 x2 x1 imax 2n 1 7 i 0,1,,2n 1 , т.е. существует всего 2n различных минтермов Макстерм (обобщение дизъюнкции) – функция n переменных, равная инверсии от минтерма n M i Ki x p ep p 1 n V xp ep p 1 n V xp ep , p 1 где xn ,, x p , , x1 , i en e p e1 Свойства макстермов: 0 , i в одной точке 1. M i 1 , j i 2. M i M j 1, при i j 2n 1 3. Mi 0 i 0 Макстермы двух переменных: M i x2e2 x1 e1 где x2 , x1 M 0 x2 0 x10 x2 x1 M1 x2 x1 , M 2 x2 x1 , M 3 x2 x1 Пример: найти M 5 функции трех переменных n 3 , x3 , x2 , x1 i 510 1012 M 5 x31 x20 x11 x30 x12 x10 x3 x2 x1 imax 2n 1 7 i 0,1,,2n 1 , т.е. существует всего 2n макстермов 12 различных 1.7. Формы представления переключательных функций Теорему разложения применим n раз по всем переменным. Пример для функции двух переменных: f x2 , x1 x2 f 0, x1 x2 f 1, x1 x2 x1 f 0,0 x1 f 0,1 x2 x1 f 1,0 x1 f 1,1 x2 x1 f 0,0 x2 x1 f 0,1 x2 x1 f 1,0 x2 x1 f 1,1 x20 x10 f 0,0 x20 x11 f 0,1 x21 x10 f 1,0 x21 x11 f 1,1 3 3 i 0 i 0 V x2e2 x1e1 f e2 , e1 V f i Ki , где Ki x2e2 x1e1 , x2 , x1 , i e2 , e1 , i e2e1 Так как f i ai и ai 0,1 , тогда СДНФ (совершенная дизъюнктивная нормальная форма): 3 f Vai Ki . i 0 «Совершенная» означает, что все члены одинаковой размерности. «Дизъюнктивная» – выполняется операция дизъюнкции произведений термов. «Нормальная форма» означает последовательное выполнение не более двух операций (конъюнкции и дизъюнкции). Операция инверсии в расчет не берется. Пример. Задана таблица истинности i x3 x2 x1 f 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 x3 x2 x1 x3 x2 x1 4 1 0 0 0 x3 x2 x1 x3 x2 x1 5 1 0 1 0 6 1 1 0 1 7 1 1 1 1 СДНФ: f K1 K3 K 6 K 7 x30 x20 x11 x30 x21 x11 x31 x21 x10 x31 x21 x11 13 Логический элемент (ЛЭ) – устройство, реализующее одну из основных операций АЛ. Логическая схема – схема, составленная из конечного числа ЛЭ. Если логическая схема полностью описывается переключательными функциями, то ее называют комбинационной схемой (КС). У комбинационных устройств состояние выхода однозначно определяется набором входных сигналов (текущим состоянием) и не зависит от предыдущего состояния. Критерий сложности схемы – число первичных термов, входящих в запись. Порядок схемы – число последовательно включенных логических элементов. КС для СДНФ: & & 1 & & Данная КС является схемой второго порядка. СКНФ Совершенная конъюнктивная нормальная форма (СКНФ) может быть получена инверсией СДНФ. «Конъюнктивная» означает, что выполняется операция конъюнкции нескольких логических слагаемых. f 2n 1 ai M i , i 0 14 M i , ai 0 где ai M i . 1 , a 1 i Доказательство f 2n 1 2n 1 2n 1 2n 1 i 0 i 0 i 0 i 0 V ai Ki ai Ki ai Ki ai M i Пример: i x3 x2 x1 f 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 1 1 1 1 СКНФ: f M0 M 2 M 4 M5 x x 1 0 0 3 x2 x1 1 0 1 3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 КС для СКНФ: 1 1 x30 x2 0 x10 x30 x2 1 x10 & 1 1 Данная КС является комбинационной схемой второго порядка. 15 1.8. Минимизация переключательных функций Проблема представления СДНФ и СКНФ состоит в сложности схемы и большого числа первичных термов. Именно поэтому требуется минимизация. Контерм (конъюнктивный терм) – функция n переменных вида n Ki , j ( x p ep p 1 e ' xp p ) , где i en e p e1 , j en' e p' e1' , i j x ep , e e ' p p p e e xp p xp p ' 1 , ep ep ' Ограничения: 1. , i j , чтобы избежать повторов. K1,3 существует, K3,1 – не существует. 2. e p e p ' K1,3 существует, т.к. i, j (001, 011) , K1,2 – не существует, т.к. i, j (001, 010) , Пример: Найти K1,3 функции трех переменных n 3 x3 , x2 , x1 i 110 0012 , j 310 0112 K1,3 x30 x30 x20 x21 x11 x11 x3 1 x1 x3 x1 K1,3 x30 x20 x11 x30 x21 x11 x3 1 x1 x3 x1 Таким образом для функции n переменных существует всего 3n различных контермов. 16 Пример обратной задачи: Найти i, j для Ki, j x5 x3 функции шести переменных n 6 Ki , j 1 x5 1 x3 1 1 x60 x51 x40 x30 x20 x10 x61 x51 x41 x30 x21 x11 i 0100002 1610 ; x5 x3 j 1110112 5910 Два минтерма Ki и K j назовем соседними, если они различаются только одним первичным термом. Пример: для n 3 : K3 x3 x2 x1 K7 x3 x2 x1 – соседние Каждый минтерм имеет по n соседних минтермов из 2n возможных. Принципы минимизации Дизъюнкцию двух соседних минтермов можно заменить контермом, не зависящим от одной переменной: K1 K3 x3 x2 x1 x3 x2 x1 x3 x2 x2 x1 x3 x1 K1,3 Дизъюнкцию четырех минтермов, где каждый имеет по два соседних, можно заменить контермом, не зависящем от двух переменных: K1 K3 K5 K 7 x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 x1 x2 x2 x3 x3 x1 K1,7 минтермов, где каждый имеет по 2m1 соседних, можно заменить контермом, не зависящем от m переменных. Дизъюнкцию 2m МДНФ (минимальная дизъюнктивная нормальная форма) – функция, содержащая минимально возможное число первичных термов. f VKi, j i, j Для минимизации групп из 2m минтермов используется способ на основе таблиц (диаграмм Вейча или карт Карно). 17 1.9. Диаграмма Вейча Диаграмма Вейча (ДВ) состоит из 2n клеток, каждая клетка которой соответствует одной точке задания функции. Пример.: ДВ – 3 , n 3 , 23 8 f x3 x1 5 7 3 1 4 6 2 0 x2 Аналог – карты Карно x3, x2 f 1,0 1,1 0,1 0,0 x1 1 5 7 3 1 0 4 6 2 0 K0 x3 x2 x1 x30 x20 x10 , K4 x3 x2 x1 x31 x20 x10 Соседние клетки (клетки, которые имеют общая грань) отличаются только в одной переменной. Пусть минтерм Ki 1 только в одной точке ДВ , тогда в этой клетке i надо поставить символ «1». Введем обозначения: «Один-клетка» – клетка ДВ, где стоит «1» «Ноль-клетка» – клетка ДВ, где стоит «0» Область, содержащая 2m «один-клеток» – m -куб. Правила минимизации: 1. Для отыскания МДНФ, надо минимальным числом m -кубов покрыть все «один клетки». 2. m -кубу, покрывшему 2m «один клеток» соответствует контерм, не зависящий от m переменных. 18 3. Прямоугольные области в ДВ могут состоять из 2m «один клеток» (1, 2, 4, 8,…). 4. Покрытие следует начинать с выбора тех «один-клеток», которые могут войти только в один m -куб и покрываются m -кубами максимального размера. 5. Если «один-клеток», входящих только в один m -куб нет, то следует рассмотреть несколько вариантов минимизации. Пример 1 (из таблицы прошлого параграфа): x3 f x1 0 1 1 1 0 1 0 0 МДНФ f x3 x2 x3 x1 x2 Пример 2 : f x3 x1 1 1 0 0 1 1 0 1 МДНФ f x3 x2 x1 x2 ДВ – 4 , 24 16 f x4 x2 10 14 6 2 11 15 7 3 9 13 5 1 8 12 4 0 x3 19 x1 Пример 3: f x4 Решение 1 x2 1 0 0 1 0 1 1 0 0 1 1 0 1 1 1 1 f x3 x1 x2 x1 x3 x1 x1 x3 f x4 x2 1 0 0 1 Решение 2 0 1 1 0 f x3 x1 x3 x2 x3 x1 0 1 1 0 1 1 1 1 x1 x3 Пример 4 f x4 x2 0 1 0 0 1 1 0 0 0 1 0 0 0 0 0 0 x3 f x4 x2 x1 x4 x3 x2 x4 x3 x1 КС второго порядка 20 x1 1.10. Представление функций в различных минимальных формах Пример f x4 x2 0 0 0 0 1 0 0 1 1 1 0 1 1 0 0 1 x1 x3 МДНФ f x3 x1 x3 x2 x4 x2 x1 МНФ в базисе «И-НЕ» получается из МДНФ двойным отрицанием f x3 x1 x3 x2 x4 x2 x1 x3 x1 x3 x2 x4 x2 x1 Схема для МНФ в базисе «И-НЕ» Схема для МДНФ & & & & 1 & & 21 & МКНФ (получается из МДНФ инверсной функции): f x4 x2 1 1 1 1 0 1 1 0 0 0 1 0 0 1 1 0 x1 x3 МКНФ f x2 x1 x4 x3 x3 x2 x3 x1 x2 x1 x4 x3 x3 x2 x3 x1 МНФ в базисе «ИЛИ-НЕ» (из МКНФ двойным отрицанием) f x2 x1 x4 x3 x3 x2 x3 x1 x2 x1 x4 x3 x3 x2 x3 x1 Схема для МНФ в базисе «ИЛИ-НЕ» Схема для МКНФ 1 1 1 1 & 1 1 1 1 22 1 1.11. Минимизация неполностью определенных функций Если функция не определена в m точках, то при реализации она может быть доопределена 2m способами. Из этих способов выбирается тот (или те), которые обеспечивают минимальную форму (минимальное число первичных термов). Пример: x4 f x2 0 0 Ф 0 0 0 1 0 Ф 0 Ф Ф 1 Ф 1 1 x1 x3 Решение 1 Решение 2 f x4 x2 0 0 1 0 0 0 1 0 0 0 1 0 1 1 1 1 f x4 x2 x1 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 x3 x3 f x4 x3 x2 x1 f x4 x3 x3 x2 23 x1 Пример: Найти шесть различных МДНФ функции, заданной ДВ. x4 f x2 1 1 0 0 Ф 1 Ф Ф 0 Ф 1 1 1 1 Ф 1 x1 x3 Решение 1 Решение 2 f x4 x2 1 1 0 0 1 1 1 1 0 0 1 1 1 1 1 1 f x4 x2 x1 1 1 0 0 1 1 1 1 0 0 1 1 1 1 1 1 x1 x3 x3 f x4 x2 x4 x1 x2 x1 f x4 x1 x2 x1 x4 x2 Решение 3 Решение 4 f x4 x2 1 1 0 0 0 1 0 0 0 1 1 1 1 1 1 1 f x4 x2 x1 1 1 0 0 0 1 1 0 0 1 1 1 1 1 1 1 x1 x3 x3 f x4 x3 x4 x1 x4 x2 f x4 x1 x3 x1 x4 x2 24 Решение 5 Решение 6 f x4 x2 1 1 0 0 1 1 0 0 0 0 1 1 1 1 1 1 f x4 x2 x1 1 1 0 0 1 1 0 0 0 0 1 1 1 1 1 1 x1 x3 x3 f x4 x2 x4 x2 x2 x1 f x4 x2 x4 x1 x4 x2 1.12. Перехо́дные процессы в КС. Критические состязания в КС. Синтез КС, свободных от состязаний. Пример: f x3 x1 0 0 f x3 x2 x3 x1 – МДНФ 1 1 1 0 1 0 x2 f x3 x3 – неизвестное состояние при Пусть x2 x1 1 , тогда перехо́дном процессе, т.к. сигналы идут через разные ЛЭ. КС для МДНФ, приведенной выше & 1 & 25 На практике в ЛЭ присутствует задержка. Классификация задержек: 1. Типовая tз typ 2. Минимальная tз min 3. Максимальная tз max Состязаниями в ЛЭ называют неодновременность появления выходных сигналов при одновременных изменениях входных сигналов. Критические состязания – такие состязания, в результате которых функция на выходе меняется более одного раза. Пусть tз tз x3 x3 f Пусть tз tз ⟵ КС x3 x3 f КС → 26 Для исключения критических состязаний необходимо обеспечить в любой момент времени переключение только одного из всех входных сигналов (в примере – x3 ). Любые две соседние «один клетки» на ДВ должны быть покрыты соответствующим m -кубом. f x3 x3 1 1 f x2 x3 x3 x1 x2 x1 f x3 x1 0 0 1 1 1 0 1 0 x2 Получили ДНФС (дизъюнктивная нормальная форма свободная от состязаний) Пример: x4 f x2 0 1 1 0 0 1 1 0 1 1 0 0 1 1 1 1 МДНФ: f x3 x2 x4 x2 x2 x1 x1 x3 Покрываем кубами все соседние непокрытые клетки. : x4 f x2 0 1 1 0 0 1 1 0 1 1 0 0 1 1 1 1 x3 x1 ДНФС: f x3 x2 x4 x2 x2 x1 x4 x3 x3 x1 27 1.13. Закон двойственности для КС Схему, выполненную на ЛЭ «И-НЕ» можно заменить схемой на ЛЭ «ИЛИ-НЕ» с обязательным инвертированием всех входных и выходных сигналов. Пример: f x3 x2 x3 x1 x3 x2 x3 x1 С другой стороны, инверсия от МДНФ: f x3 x2 x3 x1 x3 x2 x1 x3 Схема в базисе «И-НЕ» & & & Схема в базисе «ИЛИ-НЕ» 1 1 1 28 2. ЦИФРОВЫЕ АВТОМАТЫ 2.1. Потенциальные и импульсные сигналы Существуют два вида воздействия входного сигнала на схему: Потенциальное, когда входной сигнал воздействует в течение длительного времени, а любое изменение этого входного сигнала приводит к изменению сигнала на выходе схемы. Длительность воздействия больше длительности переходных процессов. Импульсное, когда входной сигнал сначала изменяет свое состояние 0 1 или 1 0 , после чего отключается и дальнейшее его изменение не воспринимается схемой. Длительность воздействия соизмерима с длительностью переходных процессов. Оператор перехода dx x t t x t x* x , где x* – значение в предыдущий момент времени. 1 2 3 4 x dx Моменты времени 1. dx 0 1 0 2. dx 1 1 0 𝑥∗ & 1 29 3. dx 1 0 1 4. dx 0 0 0 Проведем аналогию и для переключательной функции df f * f f * f , где f * – значение функции в предыдущий момент времени, f – значение функции в текущий момент времени. Проведем анализ основных логических функций: f x dx x * x x * x , т.е. при 0 1 dx 1 f x2 x1 d x2 x1 x2* x1* x2 x1 x2* x1* x2 x1 x1 x1* x2 x2 x2* x1 x2 dx1 x1 dx2 f x2 x1 d x2 x1 x2* x1* x2 x1 x2* x1* x2 x1 x1* x2* x2 x2* x1* x1 x1* dx2 x2* dx1 Пример: Цифровой умножитель частоты на два x dx dx x* x x * x x x* =1 𝑥∗ x dx dx x dx dx 30 Пример: Дано условное графическое обозначение (УГО) элемента В дальнейшем будем пользоваться следующими обозначениями: CT 1 С1 С2 при при H H 2 H1 dH 1 – определено, т.к. * d H 2 H1 d H1 H 2 H1 dH 2 H 2* d H1 1 Решения логического уравнения * 1. H1 dH 2 1 , тогда H1 0 – потенциальный и одновременно H2 – импульсный 2. H 2* d H1 1 , тогда H 2 1 и одновременно H1 Видно, что один (потенциальный) – разрешает/запрещает работу, второй воздействует перепадом 0 1 или 1 0 (импульсный). При переключении потенциального сигнала необходимо детально проанализировать, что произойдет в схеме. Если одновременное переключение недопустимо, тогда должны одновременно выполняться условия: H1 dH 2 0 H 2 d H1 0 H1 H2 31 2.2 Классификация логических схем Логические схемы (ЛС) Комбинационные схемы (КС) Последовательностныесхемы (ПС) Асинхронные автоматы (АА) Асинхронные потенциальные автоматы Синхронные автоматы (СА) Асинхронные импульсные автоматы в КС значения выходных сигналов в данный момент определяются значениями входных сигналов в тот же момент времени. в ПС значения выходных сигналов зависят не только от входных сигналов, но и от предыдущих значений выходных сигналов. Для хранения предыдущих значений выходных сигналов в состав цифрового автомата (ЦА) вводят элемент памяти. АА – изменяет свое состояние под воздействием всех входных сигналов. АА называют потенциальными если воздействуют потенциальные сигналы. АА называют импульсными если воздействуют импульсные сигналы. СА – в них присутствуют информационные сигналы, которые только разрешают или запрещают изменение состояния (всегда потенциальные) и специальный тактовый сигнал – он изменяет состояние автомата (всегда импульсный, в момент перепада 0 1 или 1 0 ). 32 2.3 Основная модель асинхронного потенциального автомата Основная модель асинхронного потенциального автомата (АПА) показана на рисунке ниже: KC xn x1 – состояния входа, zl z1 – состояния выхода Qm Q1 - внутреннее (текцщее) состояния автомата, Qm Q1 - следующее состояния автомата. Функция переходов Qr Qr t Qr Qr t t 33 Граф переходов На рисунке: Окружности – внутренние состояния. Ветви – входные сигналы. Если говорят, что состояние неустойчивое. Если говорят, что состояние устойчивое. Пути перехода из одного состояния в другое: 1. Простой. 2. Сложный (через промежуточные внутренние состояния в новое устойчивое состояние). 3. Автоколебательный процесс (нет устойчивого состояния). Условия синтеза: 1. В схеме не должно быть автоколебательного процесса. 2. КС должна синтезироваться свободной от состязаний. 3. Состояния входа должны меняться только на соседние (т.е. отличаться только одним входным сигналом). 4. Длительность задержки t должна быть больше длительности переходных процессов в КС. 5. Входные сигналы x p должны изменяться с частотой не выше f max , при которой между двумя последовательными изменениями состояний входных сигналов должны успеть закончиться все переходные процессы. 34 6. В автомате не должно возникать критических состязаний в элементах памяти (неодновременное появление Qr при одновременном изменении входных сигналов Qr ). Условия 1 и 6 – необходимые (если не выполнить условие, то автомат не может работать правильно). Условия 2–5 – достаточные (если не выполнить условие, то автомат может работать правильно). Критические состязания – состязания, приводящие к неправильной работе автомата. Для исключения состязаний любые два внутренних состояния, между которыми возможны переходы, должны отличаться только одним сигналом. Пример графа переходов. 00 01 10 11 2.4 Асинхронный потенциальный R-S – триггер УГО R-S–триггера S S R R T Q S – set – сигнал установки Q 1 R – reset – сигнал сброса Q 0 35 Q Q – устойчивое состояние RS 0 S 1 R 0 Q 1 R 1 S 0 Q 0 S R 1 - запрещенное состояние Q Ф На рисунке изображена модель асинхронного потенциального R-S – триггера КС S + Q Q R Таблица истинности для асинхронного потенциального i R S Q Q+ 0 0 0 0 0 1 0 0 1 1 2 0 1 0 1 3 0 1 1 1 4 1 0 0 0 5 1 0 1 0 6 1 1 0 Ф 7 1 1 1 Ф 36 R-S – триггера Диаграмма Вейча R Q 0 Ф 1 1 0 Ф 1 0 𝑄+ S S R Q Q RS 0 Q S R Q S R Q – в базисе «И-НЕ» & & УГО R-S–триггера T 𝑆 𝑅 Q S R 𝑄 37 S и R перейдут одновременно в «1», то состояние устройства Если зависит от задержек в логических элементах: 1. 𝑡з𝑄 = 𝑡з𝑄 – генератор 𝑓 = 1⁄2𝑡 з 2. 𝑡з𝑄 < 𝑡з𝑄 – устойчивое 𝑄 = 0, 𝑄 = 1 3. 𝑡з𝑄 > 𝑡з𝑄 – устойчивое 𝑄 = 1, 𝑄 = 0 R-S триггер можно построить и в базисе «ИЛИ-НЕ» 1 1 УГО R-S–триггера T 𝑆 𝑅 Q S R 𝑄 38 Осциллограммы работы R-S триггера 𝑆 𝑅 𝑄 ? 𝑄 tперех.проц. 2t з На практике R-S–триггер используется, как устройство хранения информации (элементарный блок памяти). Функции возбуждения R-S–триггера Поскольку R-S – триггер часто является элементом памяти для других типов триггеров, необходимо рассчитать функцию связи значений на входе, как функцию от выходных сигналов. КС S тр Rтр Q T S R Синтез сводится к определению входных сигналов S тр и Rтр , такие сигналы называются функцией возбуждения R-S –триггера. Rтр f 2 Q, Q S тр f1 Q, Q 39 Таблицы истинности для R-S –триггера. Q Q+ SТР RTP 0 0 0 Ф 0 1 1 0 1 0 0 1 1 1 Ф 0 Обобщение таблицы Q 0 1 SТР Q+ ħ Q+ RTP ħ𝑄 + 𝑄+ Sтр K1 K3 Q Q Q Q Q Q Q Q Q Q R тр K2 K0 QQ Q Q Q Q Q QQ Q Ф , Q 1 Q 0, Q 0 Ф , Q 1 Q 0, Q 0 2.5 Асинхронный потенциальный D-L – триггер УГО D-L–триггера D (data) – данные L (load) – загрузка L0 Q Q L 1 Q D T 𝐷 𝐿 D L 40 Q Варианты синтеза 1. КС D + Q Q L Таблица истинности для асинхронного потенциального D-L – триггера i L D Q Q+ 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 1 1 1 1 Диаграмма Вейча L Q 0 1 1 1 0 1 0 0 𝑄+ D 41 Q D L L Q D Q D L L Q D Q Триггер Эрла & & & & Достоинство – при L 1 – время записи tL1 2t з Недостаток – нужен дополнительный сигнал L Не выпускается в виде ИС, но входит в БИС, как элемент памяти. 2. на R-S – триггере (выпускается в виде готовой ИС) D L КС S тр Rтр Q T S R 42 Диаграммы Вейча 𝑄+ L Q 0 1 1 1 0 1 0 0 D Воспользуемся функцией возбуждения R-S – триггера Q 0 1 SТР Q+ ħ Q+ RTP ħ𝑄 + 𝑄+ S тр L Q 0 Ф Ф Ф 0 1 0 0 Q Rтр L 1 0 0 0 Ф 0 Ф Ф D D Sтр D L Rтр D L D L L Sтр D L Rтр D L L по свойству x y x y y 43 & & (1) (3) & & (4) (2) Анализ: 1. D L 1 2. L 1, D 0 Sтр 0 Rтр 1 S тр 1 Rтр 0 Q 1 путь сигнала 1 3 4 t з 3t з Q 0 путь сигнала 1 2 4 3 t з 4t з Недостаток – задержка в два раза больше по сравнению с триггером Эрла. Временная диаграмма L D Q 44 2.6 Асинхронный потенциальный D-L-R – триггер УГО D-L-R-триггера D D (data) – данные L L (load) – загрузка T Q R R (reset) – сброс Вариант а – приоритет входа L LR0 Q Q L 1, R 0 Q D L 0, R 1 Q 0 R L 1, R 1 Q L Q D 0 1 0 0 0 1 0 0 0 1 1 1 0 1 0 0 Q D S тр L R 0 1 0 0 0 Ф 0 0 0 Ф Ф Ф 0 1 0 0 Rтр L R Q Ф 0 Ф Ф 1 0 1 1 1 0 0 0 Ф 0 Ф Ф D Q D Sтр D L Rтр DL RL RD D L L R L D Sтр D L D L L RL D D LL D LR D L L R Rтр D L L R 45 & & (1) (4) & 1 & (2) (3) (5) Проверка – при D L R 1 Q 1 (приоритет загрузки) Анализ схемы 1. L 1 D 1 R путь сигнала 1 4 5 , t з 3t з 2. L 1 D 0 R 0 путь сигнала 1 3 5 4 , t з 4t з 3. L 0 D 0 R 1 путь сигнала 1 3 5 4 , t з 4t з 46 Вариант б – приоритет входа R LR0 Q Q L 1, R 0 Q D L 0, R 1 Q 0 R L 1, R 1 Q L Q 0 0 0 0 0 0 0 0 0 0 1 1 1 0 1 0 0 D S тр L R 0 0 0 0 0 0 0 0 0 Ф Ф Ф 0 1 0 0 Rтр L R Q Ф Ф Ф Ф 1 1 1 1 1 0 0 0 Ф 0 Ф Ф D D S тр D L R Rтр D L R S тр DL R D L R Rтр D L R D L L R 47 Q Q & 1 (1) (3) & (5) & & 1 (2) (4) (6) Проверка – при D L R 1 Q 0 (приоритет сброса) Анализ схемы 1. L D R 1 путь сигнала 3(4) 6 5 , t з 3t з 2. L 1 D 0 R 0 путь сигнала 1 2 4 6 5 , t з 5t з 3. L 1 D 1 R 0 путь сигнала 1 3 5 6 , t з 4t з 48 2.7 Основная модель синхронного автомата KC D T D T Условия синтеза автомата. – Изменения тактовому в схеме сигналу происходят по (импульсное воздействие), остальные сигналы только запрещают или разрешают смену состояния. – Переходные процессы в КС не влияют на работу, если частота f Н ниже их длительности. Qr Dr – Чтобы произошла смена состояния автомата должно измениться состояние элементов памяти. – Критические состязания в схеме не страшны, так как они проявляются во время между тактовыми сигналами. – Неважны переходные процессы в элементах памяти, так как они анализируются в дискретные моменты времени. Условия корректной работы: x p dH 0 Dr dH 0 49 2.8 Синхронный D– триггер УГО синхронного D– триггера D H D T T dH 1 dH 1 | H Таблица истинности для синхронного D – триггера i dH D Q Q+ 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 1 1 1 1 Диаграмма Вейча dH Q 0 1 1 1 0 1 0 0 𝑄+ D Q DdH QdH DdH 0 Синхронный триггер синтезируется не менее чем из двух асинхронных триггеров.. 50 D & & & & & & & & H 1 1 Запись D 1 1 & D 0(1) 1 & & 1(0) & 0(1) H 1(0) & 1 & & 0 0 1 & 1 0 1(0) 0(1) Запись D 0 D 0 & 1 0 & & 1 & 1(0) H 1(0) & 1 1 & & 0(1) 1 1 0(1) 51 & 1(0) 0(1) Фирмы выпускают D R и D R-S триггеры, в них 2 3 асинхронные потенциальные сигналы имеют больший приоритет D/R – триггер УГО D/R – триггера 1 4 D T R Q R DdH QdH DdH 0 D/R-S – триггер УГО D/R-S – триггера S Q S R DdH QdH DdH 0 RS 0 T D R 1 2 3 4 5 6 52 7 8 Функция возбуждения D – триггера Q DdH QdH Так как D f (Q ) , при dH 1 D Q Значения входа D опрашиваются только в момент спада тактового сигнала. 2.9 Синхронный J-K –триггер УГО синхронного J-K –триггера Q Q dH 0 J dH 1 T K J K 0 Q Q J 1, K 0 Q 1 J 0, K 1 Q 0 J K 1 Q Q Таблица истинности для синхронного J-K – триггера i J K Q Q 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0 Диаграмма Вейча для dH 1 J Q 1 0 0 1 1 1 0 0 K Q QJ QK 53 𝑄+ обобщение Q (QJ QK )dH QdH QJdH QKdH QdH QJdH Q( KdH dH ) QJdH Q K dH =QJdH QKdH KdH (при выводе использовано свойство y x x y x ) Тогда Q QJdH QKdH (J K )dH 0 J-K/R – триггер УГО синхронного J-K/R –триггера J Q R (Q J dH Q K dH ) T K R J-K/R-S – триггер УГО синхронного J-K/R-S –триггера Q+ S R (Q J dH Q K dH ) (J K )dH 0 SR 0 S J T K R 54 1 2 3 4 5 6 7 8 Функция возбуждения J-K – триггера Q QJ QK При dH 1 Q0 Q J K J QQ Q Q 1 J K Q K QQ Q 2.10 Синхронный T – триггер УГО синхронного T – триггера T Q Q dH 0 dH 1 T T 0 Q Q T 1 Q Q Q i dH T Q 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0 Диаграмма Вейча dH Q 1 0 1 1 0 1 0 0 T 55 𝑄+ Q QTdH QdH QT QTdH Q(dH T ) Q T dH Q T dH Q TdH Q Q TdH TdH 0 Функция возбуждения T – триггера При dH 1 Q Q T доказательство Q Q Q Q T T T Q Q Свойство замены триггеров Q QTdH QTdH Q QJdH QKdH при J K T J-K –триггер превращается в T–триггер 2.11 Асинхронный импульсный dT – триггер T Q Q dT Как синтезировать из других типов: 1. из T триггера T 1 Q Q dH QdH QdH 2. из J - K триггера J K 1 Q QdH QdH Q dH 3. из D триггера Q DdH QdH DQ Q QdT QdT 56 3. СЧЕТЧИКИ 3.1 Счетчики. Классификация Счётчиком по mod M называют автомат, имеющий M циклически изменяющихся внутренних состояний. 1 … 2 … В соответствии со способом координирования внутренних состояний счётчики подразделяются на: 1. Двоичные (по mod 2n ), где коды внутренних состояний закодированы последовательными n -разрядными двоичными числами от 0 до 2n 1 . Двоичный счётчик преобразует число пришедших импульсов в двоичный код этого числа; 2. Двоично-десятичные внутренних mod 10 – состояний 4-x которых разрядные закодированы счётчики, коды последовательно цифрами 0...9 ; коды 10...15 в счёте не используются; 3. На регистрах сдвига с соседним кодированием внутренних состояний, которые получаются при прохождении через регистр периодической последовательности «0» и «1»; В соответствии с порядком изменения внутренних состояний двоичные и двоично-десятичные счётчики делятся на: 1. Суммирующие (Up) – каждое следующее состояние на 1 больше предыдущего; 2. Вычитающие (Down); 3. Реверсивные (Up-Down). В зависимости от типа триггеров счетчики разделяют на: 1. Синхронные (все триггеры имеют единый тактовый сигнал); 2. Асинхронные (последовательное соединение D- или dT- триггеров) 57 3.2 Синтез синхронного счётчика по mod 8 111 001 010 110 … … Выразим Q2 , Q1 , Q0 f Q2 , Q1, Q0 Q2 Q2 Q0 1 0 1 0 1 1 0 0 Q2 Q0 T2 0 1 1 0 0 0 0 0 Q1 Q1 Q1 Q2 Q0 1 0 0 1 0 1 1 0 T1 Q2 Q0 1 1 1 1 0 0 0 0 Q1 Q1 Q0 Q2 Q0 0 0 0 0 1 1 1 1 Q2 Q0 Q1 T0 1 1 1 1 1 1 1 1 Q1 Синтез счётчика сводится к определению функции возбуждения триггеров, из которых он создан. Самые простые варианты – на Т- триггерах (из D-, J-K- , T-) Для определения функции возбуждения нужно знать Qr в каждой точке. 58 Вариант решения на D-триггере: Функция возбуждения Dr Qr D2 Q2 Q2 Q1 Q2 Q0 Q2Q1Q0 D1 Q1 Q1Q0 Q0 Q1 Q1 Q0 D0 Q0 Q0 Главный недостаток – сложная схема. Вариант решения на Т-триггере: Q , Q 0 r r Функция возбуждения Tr Qr Qr Qr , Qr 1 T0 1 T1 Q0 T2 Q1Q0 Введем обозначение P – сигнал переноса; P3 Q2Q1Q0 Схема для Т-триггера: 1 T T & T УГО счетчика по mod 8 СT 8 С Q 0 1 2 59 T T Временные диаграммы работы: 1 2 3 4 5 6 7 8 Синхронный двоичный счётчик преобразует поступивший на его вход тактовый сигнал в двоичный код числа по модулю 2. Задержка выходного сигнала относительно тактового равна задержке в одном триггере вне зависимости от числа ступеней. Для упрощения схемы используют асинхронный импульсный двоичный счётчик на основе Т-триггеров. В нём нет единого тактового сигнала, входной сигнал воздействует на Q0 , а далее входной сигнал каждого последующего триггера является выходным сигналом предыдущего. Q0 Q0 dH Qr Qr dQr 1, r 1,2,... Т Т Т H С 𝑄0 С 𝑄1 60 С 𝑄2 1 2 3 4 5 6 7 8 Плюсы: Простота схемы. Минусы: Задержка появления выходного кода относительно входного равна времени задержки в n триггерах ( t з n t зтр ); За счёт последовательного срабатывания появляются кратковременные промежуточные внутренние состояния (ложные значения). Пример асинхронного счётчика. СT16 С R СT16 С R 393 Q 0 1 2 3 Q 0 1 2 3 Q0 (Q0 dH ) R Qr (Qr dQr 1) R R – приоритет Для восьмиразрядного счетчика t з 8t зтр 61 Пример синхронного счётчика 1 C1 С2 СT16 R 1 C1 С2 R СT16 4520 Q 0 1 2 3 Q 0 1 2 3 d ( H1 H 2 ) d ( H1H 2 ) H1*dH 2 H 2*d H1 1 H1*dH 2 1 H1 0; H 2 H 2*d H1 1 H 2 1; H1 Для восьмиразрядного счетчика t з 2t зтр 3.3 Двоичные счётчики и делители частоты. Делитель частоты – это устройство, которое на выходе формирует сигнал с частотой в M раз ниже чем на входе: f fout in M Любой двоичный счётчик является делителем частоты входного (тактового) сигнала на M 2n . В отличие от делителя частоты счётчик должен иметь много выходов (по числу разрядов выходного кода), поэтому делитель частоты не может одновременно являться счётчиком. Пример: делитель на 2r1 , где r 0,3,...,13 div 14 ↑ R 4020 62 3.4 Двоичные счётчики с синхронной загрузкой данных и асинхронным (161) и синхронным (163) сбросом D 0 1 2 3 L P0 E СT16 Q 0 1 2 3 161 R (163) R – максимальный приоритет обнуляет внутреннее состояние 1, запрет загрузки L 0, загрузка с d30 1, счет разрешен P0 E 0, счет запрещен Режим счёта: T0 P0 E r 1 Tr P0 E Q j , r 1,2,3 j 0 3 P4 E Qr r 0 в ИС 161 R обладает максимальным приоритетом над всеми остальными сигналами и сам производит обнуление всех разрядов в ИС 163 R лишь разрешает обнуление, а сам сброс происходит по фронту тактового сигнала H 63 74161(четырехразрядный синхронный двоичный счетчик с асинхронным сбросом) 74163(четырехразрядный синхронный двоичный счетчик с синхронным сбросом) 3.5 Каскадирование ИС последовательным переносом двоичных счётчиков D L P0 E CT 16 Q 0 1 2 3 D L P0 E CT 16 Q 0 1 2 3 D L P0 E CT 16 Q 0 1 2 3 R D1 P4 R D2 P4 R D3 P4 с D1 меняет внутреннее состояние по каждому такту; D2 – каждые 16 тактов; D3 – каждые 256 тактов. 3 P4 E Qr 1 r 0 7 7 r 4 r 0 P8 E Qr Qr 1 11 11 r 8 r 0 P12 E Qr Qr 1 Счётчик разрядности 4m остаётся синхронным (один тактовый сигнал). Сигнал переноса P4 имеет задержку t зP 4 . При суммарном времени задержки t з mt зP 4 больше одного такта схема перестаёт работать. 64 0 1 14 … 15 16 254 255 256 4094 4095 4096 … … … … … … … … Главным минусом схемы является резкое понижение максимальной частоты по сравнению с одной микросхемой. Решением данной проблемы является каскадирование с параллельным переносом. 3.6 Каскадирование интегральных схем двоичных счетчиков с параллельным переносом D1 7 7 r 4 r 4 P8 E Qr Qr 1 D2 D3 11 11 r 8 r 4 P12 E Qr Qr При параллельном переносе Р8 не зависит от Р4 и длительность Р8 1 равна 16 тактам. При переходе через остальные ИС сигнал переноса хоть и задерживается, но не достигает 16 тактов, поэтому граничная частота остается практически неизменной, сравнимой с одной ИС. 65 Q30 P12 P8 P4 0 0000 0000 0000 0 0 0 1 0000 0000 0001 0 0 0 14 0000 0000 1110 0 0 0 15 0000 0000 1111 0 0 1 16 0000 0001 0000 0 0 0 239 0000 1110 1111 0 0 1 240 0000 1111 0000 0 1 0 241 0000 1111 0001 0 1 0 255 0000 1111 1111 0 1 1 256 0001 0000 0000 0 0 0 4079 1111 1110 1111 0 0 1 4080 1111 1111 0000 1 1 0 4081 1111 1111 0001 1 1 0 4095 1111 1111 1111 1 1 1 4096(0) 0000 0000 0000 0 0 0 Q110 Q118 Q74 16 тактов 16 тактов P4 P8 1 каждые 256 тактов P4 P12 1 каждые 4096 тактов 0 1 14 … 15 16 239 240 241 254 … … … … … 66 255 256 4079 4080 4094 4095 4096 … … … … … 3.7 Изменение в модуле пересчета счетчиков Двоичный счетчик считает по mod M , где M 2n , n – число разрядов. Можно уменьшить модуль пересчета (т.е. меньше, чем 2n ) двумя способами. 1. аппаратный, когда счетчик достигает значения М 1, КС вырабатывает сигнал R 0 , который обнуляет счетчик (161) или разрешает обнуление по тактовому сигналу (163). 1 L СТ 16 Q C 0 P0 1 E 2 Пример для 1 3 P4 R 67 (161) или (163) 161 (асинхронный сброс) 1 0 2 1 3 2 4 3 5 4 0 6 1 7 2 3 163 (синхронный сброс) 1 0 2 1 3 2 4 3 5 4 6 0 7 1 2 В синхронном счетчике все процессы привязаны к тактовому сигналу, поэтому использование сигнала сброса R не будет уменьшать граничную частоту. В асинхронном – за период такта меняются два состояния, поэтому происходит снижение граничной частоты, кроме того малая длительность импульсов Qr приводит к возможной неправильной работе другой схемы. «–» аппаратной реализации – нужны дополнительные КС для каждого модуля пересчета 68 «+» – не меняет функции счетчика, т.е. коды внутренних состояний 0...М 1 равны числу пришедших на счетчик импульсов по mod M . 2. программный – изменение модуля пересчета происходит с записью в счетчик числа d . L P4 – сигнал разрешения записи равен сигналу переноса После состояния «15» (1111) где P4 1 , счетчик перейдет не в состояние «0», а в состояние, определяемое загружаемым числом d . 1 D 0 1 2 3 L C P0 E 1 R 1 СТ 16 Q 0 1 2 3 0 1 2 d=2 15 P4 14 1 «+» – не надо каждый раз изменять схему при изменении модуля M , нужно лишь изменить загружаемое число d «–» – исчезает связь между числом пришедших импульсов и кодом внутреннего состояния, поэтому схема перестает быть счетчиком и используется только как делитель частоты. 69 3.7 Каскадирование двоичных счетчиков с последовательным и параллельным переносом а. последовательный перенос 1 D L P0 E CT 16 R D1 Q 0 1 2 3 1 P4 D L P0 E CT 16 R D2 M 24m d L P4m 0 1 14 … 15 Q 0 1 2 3 1 P4 D L P0 E CT 16 Q 0 1 2 3 R D3 P4 1 m 1,2,3,... 16 254 255 256 4094 … … … … … … … … 4095 4096(d) Минус данной схемы – резкое понижение граничной частоты работы из-за роста задержки переднего фронта P4m , где задержка может быть оказаться больше периода тактового сигнала. Выход – параллельный перенос, где P8 имеет длительность 16 тактов и t з не снижается на граничной частоте. 70 Пример. Делитель на M 25 с последовательным переносом. d11..0 212 M 4096 M Загружаемое число d11..0 4071 71 б. параллельный перенос (тип 1) 1 L P4m D L P0 E CT 16 R D1 Q 0 1 2 3 1 P4 D L P0 E CT 16 Q 0 1 2 3 R D2 P4 1 D L P0 E CT 16 Q 0 1 2 3 R D3 P4 1 M 24m 15 d При m3 P12 L m2 P8 L M 4081 d M 241 d Минусом схемы является потеря 15-ти элементов деления, т.е. максимальный коэффициент деления ниже на 15. 4079 4080 4081(d) … 72 Делитель на M 25 с параллельным переносом. d11..0 212 15 M 4081 M Загружаемое число d11..0 4056 73 в. параллельный перенос (тип 2) 1 D L P0 E CT 16 R D1 Q 0 1 2 3 P4 1 D L P0 E CT 16 Q 0 1 2 3 R D2 P4 M 24 m d L P4m P4 При m3 L P12 P4 M 4096 d m2 L P8 P4 M 256 d 4079 4080 4094 … 4095 4096(d) … … … … 74 1 D L P0 E CT 16 Q 0 1 2 3 R D3 P4 & Делитель на M 25 с параллельным переносом. d11..0 212 M 4096 M Загружаемое число d11..0 4071 . 75 3.8 Реверсивные счётчики Реверсивные счётчики внутренних состояний. могут менять направление изменения 0000 1111 Для положительных и отрицательных чисел используется дополнительный код. n 1-й разряд – знак числа «0» – «+», «1» – «–» Отрицательное число кроме знакового разряда содержит n -разрядное положительное число, равное дополнением числа до знакового разряда, т.к. знаковый разряд имеет максимальный вес. 1 8 7 1111 1000 0111 0.x, x 0 1.w, x 0 X д w 2n x Выпускаются реверсивные счётчики с теми же возможностями, что и обычные счётчики (с асинхронным и синхронным сбросом). Пример. ИС 169 U D L P0 E U CT 16 R 169 T0 P0 E Q 0 1 2 3 r r j 0 j 0 Tr UP0 E Qr U P0 E Qr 3 3 j 0 j 0 P4 UE Q j U E Q j P4 76 3.9 Каскадирование реверсивных двоичных счетчиков с последовательным и параллельным переносом (синтез делителей частоты) а. последовательный перенос D L P0 E U 0 U CT 16 Q 0 1 2 3 0 U D1 1 CT 16 Q 0 1 2 3 D2 1 P4 R D L P0 E U P4 R 0 U 1 D L P0 E U CT 16 D3 R Режим сложения U 1 L P4m M 24m d m 1,2,3,... Пример. Делитель на M 25 . Последовательный перенос L P12 . d11..0 234 M 4096 M 4071 Режим вычитания U 0 L P4m M d 1 m 1,2,3,... Q110 Q118 Q30 P12 P8 P4 257 0001 0000 0001 1 1 1 256 0001 0000 0000 1 0 0 255 0000 1111 1111 1 1 1 17 0000 0001 0001 1 1 1 16 0000 0001 0000 1 1 0 15 0000 0000 1111 1 1 1 1 0000 0000 0001 1 1 1 0 0000 0000 0000 0 0 0 Q74 77 Q 0 1 2 3 P4 257 256 255 … 17 16 15 … … … … … … … 1 0 d Пример. Делитель на M 25 . Последовательный перенос L P12 . Режим вычитания d11..0 M 1 24 б. параллельный перенос (тип 1) 0 U 1 D L P0 E U CT 16 Q 0 1 2 3 D1 R P4 0 U 1 D L P0 E U CT 16 Q 0 1 2 3 U P4 1 D2 R D L P0 E U CT 16 Q 0 1 2 3 D3 R P4 Режим сложения U 1 L P4m Пример. M 24m 15 d Делитель на M 25 . Параллельный перенос L P12 . Режим сложения d11..0 234 15 M 4081 M 4056 78 Режим вычитания U 0 L P4m M d 14 16 15 d … Делитель на M 25 . Параллельный перенос L P12 . Режим Пример. вычитания d11..0 M 14 39 в. параллельный перенос (тип 2) 0 U 1 D L P0 E U CT 16 Q 0 1 2 3 0 U D1 R 1 P4 D L P0 E U CT 16 Q 0 1 2 3 U P4 1 D2 R D L P0 E U CT 16 Q 0 1 2 3 1 D3 R P4 Режим сложения U 1 L P4m P4 M 24m d Пример. Делитель на M 25 . Параллельный перенос L P4 P12 . Режим сложения d11..0 234 M 4096 M 4071 79 Режим вычитания U 0 L P4m P4 16 M d 1 15 1 0 d … … … … … Пример. Делитель на M 25 . Параллельный перенос L P4 P12 . Режим вычитания d11..0 M 1 24 3.10 Сдвигающие регистры Сдвигающий регистр – синхронный автомат, выполненный на Dтриггерах, функции возбуждения которых равны: D r Qr 1(r 1,2...) D0 DS (data serial ) Сдвигающий регистр – устройство дискретной задержки входного сигнала DS на 1,2,,n тактов. 80 1 1 1 0 0 1 1 0 0 1 1 1 0 0 1 1 0 1 0 1 Обычно кроме сдвига в cдвигающем регистре присутствует синхронная загрузка: 1 загрузка L 0 сдвиг Примеры схем регистров сдвига Наличие сигнала L даёт возможность преобразования параллельного кода в последовательный. 81 1 1 1 0 1 1 1 0 1 1 Пример преобразования последовательного кода в параллельный на регистре сдвига. 1 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 Символ в схеме означает возможность перевести выход в z-состояние. Zсостояние или высокоимпедансное состояние – такое состояние выхода ИС, при котором сопротивление между этим контактом и остальной схемой очень велико. Вывод, переведённый в z-состояние, ведёт себя как не подключенный к схеме. Внешние устройства, подключенные к этому выводу, могут изменять напряжение на нём по своему усмотрению, не влияя на работу схемы. И наоборот – схема не мешает внешним устройствам менять напряжение на контакте. Используется в микропроцессных системах, где данные передаются по одним и тем же проводам между несколькими устройствами. 82 3.11 Каскадирование сдвигающих регистров Каскадирование происходит в соответствии с законом функционирования D0 DSD1 , Dr Qr 1 , D4 DSD 2 Q3 Промышленно выпускается схема, где кроме DOr есть отдельный выход Q3 , который не переводится в z-состояние. D1 D2 3.12 Реверсивный сдвигающий регистр Реверсивный сдвигающий регистр может сдвигать входную последовательность как в сторону старших разрядов, так и в сторону младших. Сдвиг в сторону старших разрядов – DS0 Сдвиг в сторону младших разрядов – DS3 83 Сдвиг Dr Qr 1 D0 DS0 Сдвиг Dr Qr 1 DS3 D3 M1 M0 Режим 0 0 0 1 Dr Qr хранение Dr Qr 1 сдвиг влево 1 1 0 1 Dr Qr 1 сдвиг вправо Dr DPr загрузка D0 M1 M 0Q0 M1M 0 DS0 M1 M 0Q1 M 1M 0 DP0 D3 M1 M 0Q3 M1M 0Q2 M1 M 0 DS3 M1M 0 DP3 Служит для преобразования PI/SO младшими разрядами вперёд и для целочисленного деления на 2k (каждый сдвиг вправо – деление на 2). При каскадировании реверсивных регистров сдвига надо обеспечить два соединения: 1. сдвиг влево Q3 D1 DS0 D 2 2. сдвиг вправо Q4 DS3 D1 M1 0 M0 0 D0 Q0 Dr Qr Dm 1 Qm 1 0 1 1 0 DS0 Q1 Qr 1 Qr 1 Qm 2 сдвиг влево DS m 1 сдвиг вправо 1 1 DP0 DPr DPm 1 хранение загрузка 84 3.13 Синтез счётчиков на регистрах сдвига 1 0 1 0 1 0 0 0 4 1 1 2 1 0 3 1 0 1 5 1 0 Пример: синтез счетчика по mod 6. 0 1 3 7 6 4 0 Q2 Q1 Q0 Q2 Q1 Q0 0 0 0 0 0 1 0 0 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 0 0 0 0 0 7 D2 Q1 D1 Q0 DS Q2 85 0 6 Q2 Q2 Q0 Ф 1 1 0 0 1 Ф 0 Q1 Q2 D2 Q1 Q1 Q2 Q0 Ф 1 1 1 0 0 Ф 0 Q1 Q1 D1 Q0 Q0 Q2 Q0 Ф 0 1 1 0 1 Ф 1 Q1 Q0 DS Q2 86 3.14 Шинные драйверы и приемопередатчики ЛЭ с z -состоянием имеют специальный вход для перевода выходов в z-состояние т.е. DI , OE 1 DO z -сост, OE 0 Можно объединять выходы по «монтажное или» BD BD Используется в микропроцессорных системах для подключения схем памяти и внешних устройств к системной шине для постоянной связи только с одним устройством. Остальные в это время переводят выходы в z -состояние. 87 Существуют два класса устройств: 1. Шинные драйверы (BD) передают данные в одном направлении 2. Приемопередатчики (TR/RC) передают данные в двух направлениях (для связи локальной и системной шин) TR/RC 3.15 Дешифраторы Дешифратор (DC) –комбинационная схема, имеющая n входов и 2n выходов, которые реализуют на выходах минтермы n -переменных Qi Ki Обозначается DC n 2n . Пример DC 2 4 DC DC преобразует n -разрядный двоичный код в 2n -разрядный унитарный код. Унитарный код имеет «1» только в одном разряде Если DC реализует все минтермы, то его называют полным, если DC реализует не все минтермы, то неполным (например DC 4 10 ) 88 Пример каскадирования DC. Построить полный DC 4 16 из двух неполных дешифраторов DC 4 10 Qi Ki x4e4 x3e3 x2e2 x1e1 , x4 , x3 , x2 , x1 , i e2e1 Полные DC промышленно не выпускаются поскольку их можно легко получить из DMX. 3.16 Дешифраторы двоичного кода в код семисегментных индикаторов Преобразование двоичного кода в код семисегментных индикаторов. 89 Существуют схемы управления с общим катодом и общим анодом Таблица истинности для схемы Пример реализации дешифратора общий анод x3 x2 x1 x0 a b c d e f g 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 1 ... ... ... ... 1 1 1 1 0 1 1 1 0 0 0 Динамическая индикация на примере двух разрядов Схема общий анод Схема общий катод 90 Управление динамической индикацией на примере четырех разрядов Seg7..0 Dig3..0 Dig0 Dig1 Dig2 Dig3 Seg7..0 на HG1 на HG2 на HG3 на HG4 на HG1 на HG2 на HG3 … Дли исключения эффекта мерцания частота обновления информации должна быть не ниже 50 Гц. 91 3.17 Демультиплексоры и их каскадирование Демультиплексором (DMX) 1 2n называется КС, имеющая n адресных входов, один информационный вход E и 2n выходов. В DMX входной сигнал E коммутируется на один из 2n выходов, номер которого задается значением адресных сигналов. DMX DMX Fi E Ki () DC Fi Ki () При E 1 DMX превращается в DC Пример для ИД4 92 Fi ' E1E2 Ki () Fi '' G1G2 Ki () ( x2 x1), i (0...3) При каскадировании DMX сигнал E может использоваться для включения Е 1 и выключения Е 0 других схем. Правила каскадирования: 1. По требуемому числу каналов определяется необходимое число адресных сигналов 2. Выбирается (или задается) тип DMX, где в каждой известно число адресных сигналов 3. Общее число адресных сигналов делится на две группы: младшие поступают на все каскадируемые схемы, задавая номер выхода E ; старшие выбирают одну из каскадируемых ИС, которую включают. Пример. Построить демультиплексор демультиплексоров DMX1 2 Qi Ki x2e2 x1e1 , x2 , x1 , i e2e1 0 0 1 0 1 1 93 DMX 1 4 из набора DMX DMX DMX Пример DMX 1 8 на ИС ИД4/155. DMX Верхняя половина Fi E1E2 x2 x1 Ex3x2 x1 Нижняя половина Fi G1G2 x2 x1 E x3x2 x1 94 Пример DMX 1 32 на четырех ИС ИД7/138. n 5 – число адресных сигналов, x5 , x4 сигналы выбора ИС 1 1 e e e e e e Fi E x50 x40 x33 x22 x11 Fi E x50 x14 x33 x22 x11 i (00e3e2e1) i (01e3e2e1) выходы 0...7 выходы 8...15 e e e e e e Fi E x15 x40 x33 x22 x11 Fi E x15 x14 x33 x22 x11 i (10e3e2e1) i (11e3e2e1) выходы 16...23 выходы 24...31 95 Применение демультиплексоров. Разработка дешифратора для управления внешними устройствами. Пример управления включением восьми устройств на ИС 74168 (DMX1 8 ). 74138 Даны адреса внешних устройств: port_IO_0 = 20h..27h port_IO_1 = 28h..2Fh Задача – по указанным адресам синтезировать дешифратор для управления восемью внешними устройствами. Решение Представим адреса в двоичной системе счисления port_IO_0 = 0010 0000..0010 0111b port_IO_1 = 0010 1000..0010 1111b Для создания схемы дешифратора адресов внешних устройств, обязанной обеспечить заданные адреса port_IO_0 20h и port_IO_1 28h, фиксируем значения разрешающих адресных сигналов BA7 = 0, BA5 = 1, а на адресные входы С, B и A подаем сигналы BA6, BA4 и BA3 (сигналы BA2–0 не поступают на схему). 96 Адресация внешних устройств Сигнал BA7 BA6 BA5 BA4 BA3 BA2–0 Адрес Селектируемое устройство 0 0 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 xxx xxx xxx xxx 20h–27h 28h–2Fh 30h–37h 38h–3Fh CS70 0 0 0 1 1 1 1 1 1 0 0 1 1 1 0 xxx xxx xxx 60h–67h port_IO_4 68h–6Fh port_IO_5 70h–77h port_IO_6 CS78 0 1 1 1 1 xxx 78h–7Fh port_IO_7 CS20 CS28 CS30 CS38 CS60 CS68 BA[7..0] port_IO_0 port_IO_1 port_IO_2 port_IO_3 CS20N CS28N CS30N CS38N CS60N CS68N CS70N CS78N Дешифратор адресов схем внешних устройств BA[7..0] CS20N CS28N CS30N CS38N CS60N CS68N CS70N CS78N Временные диаграммы работы дешифратора адресов схем внешних устройств 97 3.18 Мультиплексоры 2 в 1 и их каскадирование n Мультиплексоры (MUX) 2n 1 выполняют функцию обратную DMX т.е. коммутируют 2n входов на один выход, причем номер входа, который коммутируется на выход, задается значением адресных сигналов Пример MUX 4 1 2n 1 DO V DIi Ki () i 0 n Ki () x pp p 1 Фирмы выпускают два типа MUX 1. Со стробирующим сигналом Е 2n 1 DO E V DIi Ki () i 0 98 e 2. С z – состоянием входа (выход 0Е) 2 1 V DI K (), OE 1 DO i 0 i i z сост,OE 0 n Принципы каскадирования: Выбор числа адресных сигналов, их разбиение на группы, выбор числа и типа схем. Отличие – выходы собираются (коммутируются ) на базе MUX для объединения Построить мультиплексор MUX 4 1 из набора мультиплексоров MUX 2 1. 0 0 1 0 1 1 99 MUX MUX MUX Пример MUX 16 1 D2 D1 1 100 15 DO V DIi Ki () i 0 i e4e3e2e1 e e e D1: x40 x33 x22 x11 , i 0...7 e e e D 2 : x14 x33 x22 x11 , i 8...15 x4 x3 x2 x1 Пример. Записать минтермы 6 переменных и проставить на этом основании номера входов для стандартного подключения 6 адресных сигналов (сигналы x3, x2, x1 задают номер входа, который подключается к выходу схем D8-D1, а сигналы x6, x5, x4 подключают один из 8 выходов к общему выходу). D1 D8 000e3e2e1 111e3e2e1 101 3.19 Двоичные сумматоры Рассмотрим пример расчета суммы двух n-разрядных чисел S X Y sn X xn 1,.., x0 xn 1 ... x1 yn 1 ... y1 x0 y0 sn 1 ... s1 cn c2 s0 c1 Y yn 1,.., y0 c (carry) перенос Суммирование выполняется по правилам двоичной арифметики. 1. Суммируется всегда три числа с одинаковым весом x p , y p , c p 2. Значение суммы равно единице, если из трех суммируемых чисел единице равно одно или три. 3. Разряд переноса равен единице, если из трех слагаемых единице равны два или три. xp 0 0 0 0 1 1 1 1 yp 0 0 1 1 0 0 1 1 cp 0 1 0 1 0 1 0 1 sp 0 1 1 0 1 0 0 1 сp+1 0 0 0 1 0 1 1 1 xp cp xp sp 0 1 0 1 1 0 1 0 cp yp c p 1 1 1 1 0 0 1 0 0 yp sp xp yp cp доказательство s p x p (c p y p y p c p ) x p (c p y p y pc p ) x p ( y p c p ) x p ( y p c p ) 102 c p 1 x p y p x pc p y pc p Схемотехническая реализация одноразрядного сумматора FA (Full Adder) – полный сумматор НA (Half Adder) – неполный сумматор cp xp yp sp =1 =1 & & HA1 HA2 FA 1 сp+1 УГО одноразрядного сумматора xp yp A0 SM C1 сp+1 B0 cp C0 S0 sp При каскадировании задержка выходного сигнала нарастает с повышением разрядности суммируемых чисел. Примеры выпускаемых сумматоров 103 Примеры каскадирования X x3 ,.., x0 Y y3 ,.., y0 S s4 s3 ,.., s0 c4 s3 ,.., s0 X x11,.., x0 Y y11,.., y0 S s12 s11,.., s0 c12 s11,.., s0 3.20 Умножители двоичных чисел Входные данные X xn1...x1x0 , Y ym1... y1y0 Результат P X Y m 1 X yj2j j 0 104 Пример для n m 4 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 вес разряда =X=1310 =Y=1110 1 1 1 0 0 1 1 1 0 1 1 0 1 1 0 0 1 1 0 0 1 1 0 1 =P0=1310 =P1=2610 =P2=010 =P3=10410 1 0 0 0 1 1 1 1 p7 p6 p5 p4 p3 p2 p1 p0 =P=14310 =P + Примеры реализации P X Y A B , где X xn 1...x1x0 , Y ym1... y1 y0 A an 1...a1a0 , B bm1...b1b0 Базовый элемент sp ap xp y p + xp yp ap bp cp+1 sp bp cp+1 105 3.20 Прямой и дополнительный коды Прямой код Не годится для суммирования чисел. Используются только для умножения и деления. 0.x, x 0 1.x, x 0 X np Пример 6 0.110 6 1.110 106 Пример +6+ (–5) 0. 1 1 0 [+6]пр 1. 1 0 1 [–5]пр 0. 0 1 1 = Sпр Дополнительный код +X доп X пр X доп 1.W X доп 2n X 2n 2n (2n X ), W где W X 1. Доказательство W 2n X 2n 1 X 1 n n p 1 p 1 2 p 1 x p 2 p 1 1 n (1 x p )2 p 1 1 p 1 n x p 2 p 1 1 X 1 p 1 Пример 77 50 77доп X 7710 4 D16 10011012 50доп 50доп 0.011 0010 X 011 0010 X 1 011 0011 77доп 1.011 0011 1. 0. 1. 0 0 1 1 1 1 1 0 0 1 1 –77 1 0 0 1 0 +50 0 0 1 0 1 = Sдоп 107 Для перевода воспользуемся свойством Если W 2n X , то X 2n W W 1 Тогда Sдоп 1.110 0101 W 110 0101 Sдоп 27 W 0011010 W 1 0011011 27 Пример 2 25доп 3доп X 2510 1916 110012 X 310 316 000112 25доп 0.11001 3доп 0.00011 25доп 3доп X 2510 1916 110012 X 00110 X 310 316 000112 X 11100 X 1 00111 X 1 11101 25доп 1.00111 3доп 1.11101 25 –25 0 0. 1. 0. 1 1 0 0 1 +25 0 0 1 1 1 –25 0 0 0 0 0 = 0=Sдоп 3 –25 –22 0. 1. 1. 0 0 0 1 1 +3 0 0 1 1 1 –25 0 1 0 1 0 = –22 =Sдоп 01010 10101 1 101102 2210 108 –25 –3 –28 1 1 1 0 1 –3 0 0 1 1 1 –25 0 0 1 0 0 = –28 =Sдоп 00100 11011 1 111002 2810 1. 1. 1. –3 25 22 1. 0. 0 1 1 1 0 1 –3 1 1 0 0 1 +25 1 0 1 1 0 = +22 =Sдоп 3.21 Приоритетные шифраторы Дешифраторы – устройства преобразования m разрядного двоичного кода m в 2 –разрядный унитарный. Приоритетные шифраторы (PRCD) выполняют обратное преобразование, с учетом приоритета сигнала. Приоритетный шифратор 4x2 I3 I2 I1 I0 A1 A0 0 0 0 1 0 0 0 0 1 Ф 0 1 0 1 Ф Ф 1 0 1 Ф Ф Ф 1 1 Приоритетный шифратор 8x3 109 Назначение сигналов: EI (Enable Input)- сигнал включения шифратора, GS (Group Signal) – сигнал, подтверждающий наличие хотя бы одной единицы на входах Ik EO (Enable Output) – выходной сигнал разрешения, указывающий на отсутствие сигналов возбуждения Ik при включенном шифраторе EI=1 A2,A1,A0 – разряды выходного двоичного кода Применение приоритетных шифраторов Преобразование двоичного кода в унитарный для обслуживания одного устройства из m возможных с учетом их приоритетов. На выходах F7 F6 F5 F4 F3 F2 F1 F0 – инверсный унитарный код числа. I7 I6 I5 I 4 I3 I 2 I1 I0 1 1 1 1 0 1 1 1 1 1 0 1 0 1 1 1 A2 A1A0 011 101 A2 A1 A0 F7 F6 F5 F4 F3 F2 F1 F0 = 100 010 = K0 K1 K2 K3 K4 K5 K6 K7 1 1 1 0 1 1 1 1 1 1 1 1 1 0 1 1 3.22 Цифровые компараторы Входные данные X xn1...x1x0 Y yn1... y1y0 Результат f 1 при X Y f 0 при X Y Варианты схемотехнической реализации элемента 110 3 f ( ) V x p y p p0 7 e Пример готового решения 8-разрядный цифровой компаратор, выполняющий функцию f ( ) 7 V p0 Ap B p 3.23 Устройства сравнения чисел Входные данные X xn1...x1x0 e e e f () DO V y33 y22 y1e1x33 x22 x1e1 i0 Y yn1... y1y0 Результат 111 0, Feq F X Y 1, X Y 0, Flo F X Y 1, X Y 0, Fhi F X Y 1, X Y X Y X Y X Y Поразрядная операция: F X p Yp F X p Yp F X p Yp F X p Yp F X p Yp F X p Yp F X p Yp F X p Yp F X p Yp Схема сравнения 4-разрядных двоичных чисел Функционирование схемы 112 3.24 Спецификация схем памяти Типы 1. ПЗУ (read only memory, ROM) – энергонезависимая память для программ и таблиц констант 2. ОЗУ (random access memory, RAM) – энергозависимая память для временного хранения данных 2.1 статические ОЗУ (SRAM) – ячейка памяти выполнена на триггере 2.2 динамические ОЗУ (DRAM) – ячейка памяти на конденсаторе. Конденсатор проще реализовать аппаратно, чем триггер, поэтому объем больше. Поскольку конденсатор разряжается, то помимо режима записи и чтения вводится режим регенерации (восстановления заряда на конденсаторе). 2.3 FIFO (first in – first out) – память, не использующая внешних адресов. Адреса записи и чтения формируются внутри схемы. Адресация производится двумя кольцевыми счетчиками. Обозначение схемы памяти 2n m Основной параметр схемы памяти – её объем, определяемый числом адресных сигналов n. n 10 11 12 20 Объем Обозначение 1 024 1k 2 048 2k 4 096 4k 1 048 576 1M Кроме количества ячеек памяти существует второй параметр – разрядность шины данных m , т.е. число разрядов, хранящихся в одной ячейке. Addr[n-1..0] 0 1 2 Data[m-1..0] m бит m бит m бит … Примеры обозначения схем памяти: 2k×8 – 2048 ячеек по 8 бит (1 байт) в каждой 256×16 –256 ячеек по 16 бит (2 байта) в каждой 113 2n 1 m бит 2k×9 – 2048 ячеек по 9 бит (1 байт информации + проверочный символ). В каждой ячейке один разряд выделен для проверки правильности записи и чтения. Идея основана на двукратном расчете суммы по модулю два всех бит информации при записи и чтении. Подобный способ проверки позволяет обнаружить любую однократную ошибку. Пример реализации схемы ОЗУ и принципов его работы К рис. 1.21 DCR (Decoder Row) – дешифратор строк, DCC (Decoder Column) – дешифратор столбцов, Kr, Kc – минтермы m и n – m переменных. К рис. 1.22 DI (Data Input) – входные данные, DO (Data Output) – выходные данные, WE (Write Enable) – разрешение записи, OE (Output Enable) – разрешение выхода, CS (Chip Select) – выбор кристалла. 114 К рис. 1.23 tAS – время установки адреса (Address Setup Time), tW – минимальная длительность активного уровня сигнала записи tH – время удержания данных (Data Hold Time), tCW = tAS + tW + tH – длительность цикла записи (Write Cycle Time). Пример ОЗУ объемом 2k×8 RAM 11 8 В ПЗУ все то же самое, но без сигнала MEMW . 115 WE , Пример микропроцессорной системы. CPU D A k RAM ROM C D A m n A C n m D m AB DB CB k–n A DC CS0 CS1 AB (Address Bus) DB (Data Bus) CB (Control Bus) Встроенные блоки памяти в ПЛИС 2048 1 2k 1 могут быть реконфигурированы в иные блоки 1024 2 1k 2 , 512 4, 256 8 M4k – 4096 1 4k 1 , 2k 2,1k 4,512 8 / 9,256 16 / 18 M9k – 8192 1 8k 1 , 4k 2, 2k 4,1k 8 / 9, 512 16 / 18 M144k 147 456 1,... 116 C 3.25 Стандартные ИС В зависимости от технологии изготовления цифровые ИС делятся на семейства: 1. TTL (Transistor–transistor logic, ТТЛ, транзисторно-транзисторная логика) 2. CMOS (Complementary metal–oxide–semiconductor, КМОП, на основе комплементарных МОП–транзисторов) 3. ЭСЛ (эмиттерно-связанная логика) 4. ЛЭ на AsGa ЛЭ ТТЛ серии Базовый элемент – многоэмиттерный транзистор Пример реализации функции 2И-НЕ Рис. 2 Рис. 1 Рис. 3 Рис. 1 – Принципиальная схема простейшего элемента ТТЛ серии Рис. 2 – Принцип расчета задержки переключения ИС Рис. 3 – Обозначение на схемах транзисторов в диодами Шоттки. Примечание к рис.3. Введение в структуру ТТЛ схем диодов Шоттки позволяет транзисторам быстрее входить в режим насыщения, как следствие снижаются задержки при переключении и повышается быстродействие. 117 Параметры зарубежных ИС серий SN74 Серии ИС 74 74L 74H 74S 74LS 74ALS 74AS 74F tpd, нс P, мВт/ вент IIH, мкА IIL, мА Fmax, МГц 10 33 6 3 9,5 4 1,5 2 10 1 22 19 2 1 22 4 40 10 50 50 20 20 20 20 –1,6 –0,18 –2 –2 –0,4 –0,1 –0,5 –0,6 35 3 50 125 45 50 200 130 IOH, мА IOL, мА n tpdP, пДж –0,4 –0,2 –0,5 –1,0 –0,4 –0,4 –2,0 –1,0 16 3,6 20 20 8 8 20 20 10 10 10 10 20 20 40 33 100 33 132 57 19 4 33 8 74 — базовая ТТЛ-серия. Первая серия, выпускавшаяся фирмой Texas Instruments ( t PD 10 нс, P 10 мВт); 74L — серия с пониженным энергопотреблением, заменена серией LS, а также КМОП-микросхемами, значительно превосходящими её по экономичности ( tPD 33 нс, P 1 мВт);, 74H — повышенная скорость. Использовалась в 1960-70 гг. и была заменена S-серией ( tPD 6 нс, P 22 мВт); 74S — с диодами Шоттки (Schottky). Устарела, её превосходят серии 74AS и 74F (( tPD 3 нс, P 9 мВт); 74LS — с диодами Шоттки и пониженным энергопотреблением (Low Power Schottky) ( tPD 9.5 нс, P 2 мВт); 74AS — улучшенная с диодами Шоттки (Advanced Schottky) ( tPD 1.5 нс, P 22 мВт); 74ALS — улучшенная с диодами Шоттки и пониженным энергопотреблением (Advanced Low Power Schottky) ( tPD 4 нс, P 1 мВт); 74F — быстрая (Fast) с диодами Шоттки ( tPD 2 нс, P 4 мВт). Лучшими в настоящее время считаются серии ALS и F Сравнительные характеристики ИС Серии ИС Диапазон рабочих температур, oC Напряжение питания, Vcc, В SN54 SN74 SN84 –55 … +125 0 … +70 –25 … +85 4,5 … 5,5 4,75 … 5,25 4,75 … 5,25 Серии: SN74 – пластиковый корпус SN54 – военная сборка SN84 – промежуточное 118 Особенности ТТЛ схем 1. существует входной ток высокого и низкого уровня I IL 2 мА I I Н 20 мкА 2. Выходные токи IOL 8..20 мА IOH 0,2..0,4 мА 3. Уровни 0 и 1 UOH 2.4..2.7 В UOL 0,4 B 4. Ток потребления I cc зависит от тока в нагрузке 5. Ток потребления I cc зависит от t pd . Чем выше I cc , тем ниже t pd 6. Качество серии определяется произведением t pd и P (время задержки на мощность потребления) ИС 7400 (4x2И-НЕ)в DIP корпусе Уровни напряжение для входов и выходов "0" и "1" для логики ТТЛ для напряжения 5.В (4,5..5,5В) Выход «1» Вход VCC +5В «1» 2,4..2.7В «0» VCC +5В 2,0В 0,4..0,5В «0» 0В 119 0,8В 0В ЛЭ КМОП серии Диоды на входе – защита изоляции затвора от пробоя Резистор на входе – не позволяет скачку тока короткого замыкания передаваться в незаряженную входную емкость затворов При этом защищается выход предыдущего инвертора от импульсной перегрузки. Выходные диоды –защита выхода от пробоя между n– и n+ областями. Также защита от ошибочной перемены полярности питания. Реализация логических элементов на полевых транзисторах Логический элемент НЕ VDD A=1 120 Z=0 VDD A=0 Z=1 Логический элемент И-НЕ VDD A=1 B=1 Z=0 VDD A=0 Z=1 B=1 Логический элемент ИЛИ-НЕ VDD A=1 B=0 Z=0 121 VDD A=0 B=0 Z=1 . Параметры ИС КМОП-серий серии ИС CMOS CD4000 HC/HCT AHC/AHCT AC/ACT LVC ALVC VDD, В tP, нс IOH/IOL, мА IDD 5–15 5,0 5,0 5,0 3,3 3,3 150–50 30 5,2 7,0 6,5 3,0 0,5/0,5 6/6 8/8 24/24 24/24 24/24 40 пФ ? 64 пФ ? ? Особенности: 1. Входные токи практически равны нулю (переключение полевых транзисторов происходит напряжением) 2. Выходное напряжение 1 и 0 максимально по амплитуде ( VDD и 0) 3. Потребление тока в статическом состоянии отсутствует, ток потребляется только в момент переключения и расходуется на заряд/разряд паразитных емкостей 1 I DD VDD C f 2 Поэтому в таблицах указываются емкости вместо токов. 122 КМОП ТТЛ 50МГц Современные серии КМОП НС (high speed CMOS) – высокая скорость (время переключения 30 нс) АНС – усовершенствованные (время переключения 5 нс) АС – время переключения 7нс при выходном токе 24 мА Семейство АС «+» : симметричный выход и большие выходные токи Не потребляют мощности в статическом режиме «–» при переключении возникают перепады в мощности потребления, что приводит к скачкам напряжения «–» первых семейств КМОП – они неустойчиво срабатывают от выходов ТТЛ 1 U порогКМОП VDD 2,5 В U out min ТТЛ 2,4 В 2 Семейства АСТ, НСТ, АНСТ имеют входные цепи, как у ТТЛ и обеспечивают совместимость ТТЛ и КМОП серий. 123 Уровни напряжение для входов и выходов "0" и "1" для логики КМОП: – для напряжения 5.В Выход «1» Вход VDD +5В «1» 4.95В VDD +5В 3.5В «0» «0» 0,05В 0В 1,5В 0В – для напряжения 15.В Выход «1» Вход VDD +15В «1» 14.95В VDD +15В 11В «0» «0» 0,05В 0В 4В 0В Особенности сопряжения выходов ТТЛ схем со входами КМОП с использованием подтягивающего резистора (pullup). 124 Выход ТТЛ Вход КМОП VCC +5В «1» «1» VDD +5В 3.5В 2,4..2.7В «0» «0» 0,4..0,5В 0В 1,5В 0В – для случая VCC=VDD=5В – для случая VCC VDD 125