УДК 621,369.218

ББК 32.834. I

1

Оглавление

Гриф выдан Министерством образования и науки Украины

(письмо J\; I Ф/1 SI-'W? or 20.04.{№>

Б1 2

Бабак В. П., Корченко А. Г., Тимошенко Н. IL, Филоиенко С. Ф.

VHDL: Справочное пособие по основам языка, — м.: Изда¬

тельский дом «Додэкп-ХХК 2008. — 224 с.: ил. (Серия •■Програм¬

мируемые системы»).

ISBN 978-5-94120-169-3

Прслсган.тяст собой пишии n кури » язык VHDLII пред н извинена joiHCueiporooiii.Tкомлення е базовыми концептуальными положениями ною язык». К .шиной книге

ирниодятся базовые принципы пар1ллслыюго11ро1раммнронамин, положенные о основу

языка VHDL. а также принципы организации VHDL-ÿÿÿÿÿÿÿ и взаимосвязь компонен¬

тов проект» с физическими процессами, протекающими и реальных цифровых

устройствах, Содержит многочисленные практические примеры проектирования цифровык устройств, it частности цифровых устройств специального назначении (кринтолрбнессороа}.

Рассчитана на студентов, изучающих язык VHDL, и том числе и и рамках учебных

курсов, посвященных проектированию устройств зашиты информации,

Принятые сокращения

Глава I. Введение

Глава 3. Базовая структура VHDL-ÿÿÿÿÿ . . .

3.1.

защищены. Никакая часть лого издания нс может быть кос про и заедена

или любыми средствами, электронными или механическими, включая

фотографированне, ксерокопирование или иные средства копирования или сохранения

информации, бет письменного разрешения издпгольегни

irp.iira

и любой форме

■

,

.9

10

13

Глава 2. Уровни представления и формы абстракции цифровых систем 14

£

IS11N 97K-5-94I20- 169-3

.9

Современные языки проектирования цифровых устройств

1.2. Краткая характеристика языка VHDL

1.3, Этапы проектирования с использованием VHDL

УДК 621.369.218

Издательский дом -Дадэка-ХХ!

.8

] . I.

пек 32.Ш.1

Ike

..

......

...

20OS

Коианюк Ю, С , 200*

Серия «Программируемые системы"

18

.18

Общие сведения

.

3.2, Объявление интерфейса

3,3. Архитектура проекта

3.3 I . Архитектура проекта в поведенческой форме

3,3.2. Архитектура проекта в структурной форме . .

3.4. Библиотеки и пакеты

4.4. Числа..

4.5. Символы, строки и битовые строки

....

26

26

.33

.... 37

Глава 4. Лексические элементы языка VHDL

4.1. Идентификаторы

4,2. Ключевые слова

4.3. Зарезервированные слова

22

37

38

.-

39

,4П

41

4 яОлкаление

Oziae.ÿHtic

Глава 5, Программные элементы данных; константы, переменные

л сигналы ,

.

. ....

.

.

5.1. Константы

5.2. Переменные

5.3. Сигналы

.43

44

...

6.1. Встроенные типы данных пакете STANDARD. . ....

6.3.

.42

.

Глава б. Тилы данных

6.2,

.42

Пользовательские типы Н подтипы

6.2.1.Физические типы . . .

6.2,2. Перечислимые типы

6,2,3. Композитные пользовательские типы

Преобразование типов

.

..

6,4. Атрибуты

6.4.1,Атрибуты сигналов

6.4.2.Скалярные атрибуты

6,4,3, Атрибуты массивов

7.1. Логические операции

7.2, Операции отношений

7.3. Операции сдвига

7.4. Операции сложения

7.5. Унарные операции

7.6. Операции умножения

..

....

7.7. Вспомогательные операции

7.8. Символы комментария

7.9. Математические выражения

9.3. Сслсктншшм установка аначенпй сигналом

50

Глава 10. Структурная форма проекта

.

.....

- . ...

8.4. 1 , Базовая форма цикла

8.4.2. Итерационная форма шита WHILE ... LOOP

8.4.3, Итерационная форма никла FOR ..

LOOP

...

....

106

10.1. Оператор COMPONENT

64

Глава 1 1, Примеры VHDL-ÿÿÿÿÿÿÿÿ ЦУ различного назначения . .

71

.73

,73

74

.79

то

84

86

89

89

91

92

92

.98

I0O

105

10.2, Оператор PORT МАР

.72

.

.....

,97

102

61

.77

8.!. Явно заданный оператор PROCESS

8.2. Оператор условной передачи управления If

8.3, Оператор выбора CASE

8.4. Оператор цикла LOOP

8.4.4. Операторы NEXT и EXIT

49

.75

Глина 8. Поведенческая форма проекта: явно заданный

оператор Process

.

...47

. .70

... .

Глава 9. Поведенческая форма проекта: неявно жданный

оператор PROCESS ,

Простая параллельная установка значений сигналов ,

70

.

,

Условная установка значения сигнала

.69

..

..........

.......

...

9.1

68

Глава 7. Операции и символы операций

8.7. Пример VHDL- проекта

9.2,

64

... 65

.

93

94

95

8.5. Оператор ожидании WAIT

Я. 6. Оператор NU LL

,47

5!

Ч

я 5

.

М>7

115

115

1 J . 1 . Проекты ЦУ общего назначении . . , .

1)5

II 1.1 Логический элемент AND на *1 входа

1)6

II 1.2. Логический элемент OR на 2 входа

117

11.] . 3 . Л огический эле мент О R J ia 4 инвере нык входа

119

1 1 . 1 .4, Логический элемент NOR ил 3 входа , . . ,

120

11.1.5. Логический элемент XOR па 2 и хода

11.1,6. 4 -битный буфер логический усилитель. . ,

121

122

11.1.7. 8-бнтный буфер с тремя состояниями без обратной связи

11.1.8. 4-клналмтый мультиплексор 4х 1

122

с сигналом разрешения выбора номера канала

,

123

11.1.9 Демультиплексор 1 х4

II.1.10. 4-битный последовательный сумматоре фиксирован ной тонкий .. 124

125

11.1.11. 8 -битный сумматор с ускоренным переносом

11,1.12. 4 -битный каскадный вычитательс фиксированной точкой

126

11,1,13. 8-бнтный сумматор со сквозным пенником с уче том знаков битов 127

11,1.14. Универсальный плрлллельный арифметический процессор ,

129

1 1.1.15.4-битный компаратор е .знали юм никои сравниваемых чисел

... 130

и выбором режимов сравнения

131

.

1 1.M6, 8-бнтный контроллер четности

11.1 17, Простой IJ-ÿÿÿÿÿÿÿ. переключаемый передним фронтом тактового

132

импульсе

.

.

132

.

1 1,1.18. 1J-ÿÿÿÿÿÿÿ с асинхронным сбросом

31,1.19, D-ÿÿÿÿÿÿÿ с асинхронной предустановкой

133

1 1.1.20. D-ÿÿÿÿÿÿÿÿ асинхронным Сбросом и асинхронной предустановкой 134

134

1 1 .1,21. 1>-трштерс синхронным сбросим

... 135

! 1 ,1 .32, D- триггер с синхронной предустановкой

......

.

6 ■ Оглавление

Ошв-тие ■ 7

И . 1.33. D-ÿÿÿÿÿÿÿ с синхронным сбросом н сигналом, разрешающим

приход оче|мднаго тактового импульса

] 1.1.24. D-ÿÿÿÿÿÿÿ- зашелка

1 1.1.25. D-ÿÿÿ гср-эашелка со стробирующим сигналом

1 1 Л.26. 8- битный накапливающий счетчик со счетным входом

и асинхронным сбросом

136

137

137

.

138

11.1.27. S-ÿÿÿÿÿÿ накапливающий счетчик с синхронной загрузкой

н асинхронным сбросом

Ml 2S- 8-СнтныИ никаплиааюший/иы читающий счстчнк с выбором

направлении счета

...

.. ,

1 1 . 1 . 29.N -Си гмыи н а капл нвающий с четчик со счстн ыч входом.

синхронной загрузкой и асинхронным сбросом

11.1 1(1. Синхронный 4-бнтный ЦИКЛНЧССК11Й сдвнглпый регистр вправо

с параллельным входом и выходом

11.131. Универсальный синхронный 4 -битный сдвиговый регистр вправо

с параллельным входом и выходом

11.1,32. Расширитель разрядности шины знаковыми разрядами .

11,1 ,3J. VNDI.-npoeiCT расширителя разрядности шины нулями

11 .1 ,34, 8-йцтнад лиунайрлвленнпл шина с тремн состояниями ....

11.1 .36. Процессор возведения в степень N

.

1 1.1.36. Процессор нахождения факториала

1 1 1.37. Процессор нахождений натурального логарифма

1 1.1.38. Процессор нахождения квадратного корни, . . ,

1 1.1 39. Процессор, конвертирующий 16-ричныс значения в данные гип.ч

.

139

140

141

......

142

144

145

147

148

149

149

150

152

.

sidjogic_vcc(or ..... ....

153

1 1.2, Проекты НУ специального назначения

1 1,2. 1 Гоператор тактовых импульсов с периодам следовании 100 нс

и скважность» 505в

.

..

154

154

1 1.2.2. Комбинированный генератор псевдослучайных чисел с выходными

значениями разных типов

1 1.2,3, Многофункциональный конвертер типов данных. . .

1 1 .2.4,1клочислснныН чультнили кативший криитопроцсссор

L 1.2,5, Символьный адшпнмнмн крнптопроцессор

1 1.2,6. Подстановочный символьный криптопрОИессор

1 1.2.7.Перестановочный битовый крнптопроцсссор,

1 1.2.8 ,Крнптопроцсссор на базе сдвиговых операции

1 1.2-9 Кринтоироцсссор с многоуровневой системой шифрования,

формульный метод

1 1.2.10. Криптопроиеесор, реализующий метод эллиптических кривых

1 1.3. Проекты ЦУ специального назначения повышенного уровня

.

11.3. 1, Файловый криптопроиессор циклического сдиш л

1 1.3.2, Файловый KSA- криптопроиессор

...

168

... 170

.

сложности

154

156

157

158

161

16?

166

177

177

184

1 1 .3.3, Файловый криптопроцессор Нижние ра.

Приложение. Основы языка VHDL» реферативном изложении . ,

192

,

. 199

199

П.1. Язык VIIDL кпк универсальный язык проектирования ЦУ

201

....

. ..

П.2. Концептуальные положения языка VHDL.......

204

Г1..3. Объявление ннтср гсйса проекта . .

2%

П.4. Программные Элементы данных языка VHDL ....

П.5. Поведенческая форма проекта на основе ятю заданного

.

210

оператора PROCESS

П.6. Поведенческая форма проекта на основе неявно заданного оператора

212

PROCESS

21-1

П.7. Структурная форма проекта

...

ГЛАВА

Принятые сокращения

ллу

оно

ПО

САПР

СБИС

НУ

[iv;ic

УУЗС

СУЗС

— арифметико-логическое устройство.

оператор параллельной обработки.

программное обеспечение,

система автоматизированного проектирования.

сверхбольшая интегральная схема.

цифровое устройство.

простая установка значения сигнала.

условная установка значения сигнала.

— селективная установка значения сигнала.

1

ВВЕДЕНИЕ

1.1. Современные языки проектирования

цифровых устройств

VNDL. является аббревиатурой от Very liiÿh speed integrated circuits

Hardware Description Language, что переводится как зпык описании устроиств ни сверхбольших интегральных схемах (СВИС). В середине

1 980-х гг. Министерство обороны США и IEEE11 спонсировали разра¬

ботку згою языка описания цифровой аппаратуры с целью получе¬

нии простого и использовании средства проектирования н моделиро¬

вания логических схем для всех этапов разработки электронных сис¬

тем. начиная от модулей микросхем и кончая крупными

вычислительными системами. Первая версия стандарта была издана и

1987г. (IEEE 1076-I987E Очередные версии выхолили в 1991, 1993,

1996, 1997. 1999. 7000 и 2002 гг. 13 настоящее время действует стандарт

VHDL, наложенный в документе IEEE 1076-2602 н являющийся про¬

мышленным стандартом, который широко используется для описа¬

нии работы цифровых систем. И июне 2606 г. была опубликована вер¬

сия 3.0 проекта стандарта VIIDL-20O6, в который пошли все дочерние

стандарты, разработанные в ходе создания стандартов VHDL (IEEE

—

IЕЕЕ (Ins!i t me of E leei lit а I and Elect ion ic lingi nic rs И 1 ICTHTJT и нженерои тю

электротехнике и радиоэлектронике, ИИЭР) — международная организация,

созднннпя и США в 1963 г. Является разработчиком рллпстанлартов для локальных

пычислительных систем, втом числе по кабслышВ системе, фм лпсскоП топологии

Лримич. ро),

н методам доступа к среде передачи данных

1.Z Кроткая характеристика языка УН Hi ■ П

Ю ■ Г.та 1. Введение

1064, 1076.2, 1076.3). а также добавлены другие усовершенствования,

ла кис как интерфейс с языками высокого уровня C/C++ и ряд других.

В РФ язык VHDL закреплен стандартом ГОСТ РФ 50754-95 «Язык

описания аппаратуры цифровых систем VHDL. Описание языка».

В данной книге рассмотрены основные положения языка VHDL,

которые определены в стандарте IEEE 1076-1993, поскольку наследую¬

щие изменения (за исключением пока еще разрабатываемого

стандарта

VHDL-2006) были несущественными. Кроме того, псе последующие

стандарты VHDL, включая VHDL-2006, обеспечивают соимсстнмостьс

проектами, разработанными в соответствии со стандартом

1076-1993.

Еще одним представителем языков описания цифровой аппаратуры

является язык Vferilog. или Vvrilog HDL, Разработчики \feri1og сделали его

снптакспс очень похожим на синтаксис языка С. \fcrilog имеет препро¬

цессор, очень похожий на препроцессор языка С, а основные управля¬

ющие конструкции \ferilog также подобны одноименным конструкциям

языка С. В настоящее время действует стандарт \fcrilog, нзложепный в

документе IEEE 1364-2005, который представляет собой несколько до¬

работанный вариант очень популярного среди приверженцев

\fcrilog

стандарта IEEE 1364-2001 . Язык Vertlog применяется в промышленнос¬

ти так же широко, как и VHDL. поскольку оба этих языка позволяют

описывать и имитировать работу сложных цифровых систем.

Третьим представителем языков VHDL я ваяется язык

ABEL

(Advanced Boolean Equation Language

расширенный язык двоичных

уравнений), который был разработан в 1983 г. для создании проектов

цифровых устройств посредством программируемых логических уст¬

ройств ( PLD Programmable Logic Devices). Язык ABEL менее мощен,

чем VHDL и \ferilog, б частности нс позволяет проектировать устройства на перепрограммирусмых логических матрицах FPGA (Field

Programmable Gate Arrays), поэтому он менее популярен в нромышленности, хотя осе еще находит своих сторонников.

—

—

1 .2. Краткая характеристика языка VHDL

Хотя язык VHDL внешне выглядит так же, как н другие традицион¬

ные языки программирования (поскольку имеет литералы,

разделите¬

ли, операторы и т. д.), он обладает некоторыми

н ы ми хпра ктсрнсти камн.

важными отличитель-

Проекты цифровых устройств (ЦУ), созданные с помощью языка

VHDL, имеют, как правило, иерархическую структуру.

проектируемый модуль (субблок проекти¬

• Каждый автономный

руемого ЦУ) имеет;

строго определенный интерфейс взаимодействия с другими

модулями;

точную спецификацию внутреннего устройства просктируемого модуля. опнсывающую концепцию и функционирова¬

икс модуля.

модулей VHDL-ÿÿÿÿÿÿÿÿ могут использовать

Спецификации

*

или математические алгоритмы, описывающие их работу-, или

описание аппаратной структуры проектируемого модуля. В соот¬

ветствии с уровнями абстракций проектов описание модуля может иметь поведенческую или структурную форму.

проекта основывается на со* Моделирование алгоритма работы

управления,

бытийном принципе

моделирование протекания

• VHDL-ÿÿÿÿÿÿ позволяет выполнять

схемах, временной

электрических

параллельных процессов в

параметров.

анализ сигналов и их

инструментальными средствами синтеза

• VHDL поддерживается

проектирования (САПР)

автоматизированного

н системами

обеспечения (ПО), котопрограммного

многих производителей

рыс могут создавать прямо из описания VH DL-ÿÿÿÿÿÿÿ его аппа¬

ратную реализацию (связанные между собой структуры логичес-

•

—

—

ких элементов, содержащихся о СБИС).

можно проектировать, моделировать и синте¬

зировать практически любое ЦУ, начиная от простой комбина¬

ционной схемы до законченной микропроцессорной системы на

СБИС.

Перечисленные выше характеристики языка VHDL как специали¬

зированного языка описания ЦУ реализуются с помощью следующих

языковых средств:

• Библиотеки и пакеты. архитектура проекта.

* Проекты; интерфейс и

• Подпрограммы: функции и процедуры. числовые, физические.

перечислимые,

• Скалярные типы данных:данных;

константы, переменные, сигна¬

Программные элементы

* Используя VHDL,

•

лы, порты, идентификаторы.

1.3. Этапы проектирована с цглшьишнили I IIP! ■ 13

1 2 ■ J'.iana I. Вшк/ше

*

*

•

Via геми гимсскмс операции: логические, отношений, арифмети¬

ческие.

Программные операции: установка значений сигналов, присвое¬

ние значений переменным, реализация связи портов и сигналов.

Математические выражении: логические, алгебраические, логи¬

ко-алгебраические.

* Операторы объявления

•

•

программных элементов данных.

Операторы комбинаторной логики: простой установки значении

сигнала (ПУЗС). условной установки значения сигнала (УУЗС),

селективной установки значения сигнала (СУЗС), оператор

process, оператор реализации компонента port map.

Операторы регистровой логики: оператор process, ПУЗС, опе¬

ратор условной передачи управления, оператор цикла, оператор

выбора.

В отличие от процедурных языков программирования, языковые

средства которых обеспечивают выполнение вычислений над абстрак¬

тными данными и управление ими, VHDL-ÿÿÿÿÿÿ описыпаст ЦУ, учигыиая его многогранность. поведение, структуру, функциональные и

физические свойства, а также взаимодействие со специальной аппара¬

турой, физически реализующей проект ЦУ и СБИС,

Остановимся особо на некоторых важных отличиях языка VHDL.

VHDL по существу является языком параллельного программирования,

т. е. в его конструкции существуют операторы, соответствующие логи¬

ческим вентилям,

операторы обрабатываются (т. е, вычисляются)

\\о пара;ие.1ыюму принципу. Суть данною принципа состоит в гом, что,

как только сигнал, содержащийся в описании проектируемого ЦУ, из¬

меняет свое значение (говорят, что «происходит событие на сигнале»),

все операторы, принимающие участие в его обслуживании, мгновенно

запускаются на выполнение и одновременно выдают конечный ре¬

зультат. Поэтому такие операторы называются операторами параллель¬

ной обработки (ОПО) (concurence operator). Программа, написанная на

VIII)]. (каки на любом другом HDL-ÿÿÿÿÿ, например Mnilog), моделируст физическое поведение системы (как правило, цифровой), енгнзлы в которой распространяются мгновенно, (акая программа позволя¬

ет формировать временную спецификацию (время задержки распро¬

странения сигнала на логическом элементе), а также описывать

систему как соединение различного рода компонентов, или функцио¬

нальных блоков.

1 .3. Этапы проектирования с использованием

VHDL

В подавляющем большинстве случаев аппаратная реализация про¬

екта ЦУ с использованием VHDL протекает и соответс гимн со следую¬

щими

этапами:

Разработка иерархической блок-схемы проекта. Выяснение базового

конструктивно-технологического метода и стандартных блоков

на уровне структурной схемы. Поскольку большие логические

проекты являются, как правило, иерархическими, использова¬

ние VHDL позволяет легко разбить проект на модули (субпро¬

екты) и определить их интерфейсы.

Программирование. Запись VHDL-ÿÿÿÿ дли модулей и

их

интер¬

фейсов.

программного кола VH DL- проекта дли выяв¬

ления синтаксических ошибок, а также проверка его совмести¬

мости с другими модулями, li ходе компиляции также собирает¬

Компиляция. Анализ

ся внутренняя информация о структуре проекта, которая

необходима для моделирования работы проектируемого ЦУ.

Моделирование. Определение и применение входных воздействий

к откомпилированному коду проекта с наблюдением выходных

реакций. Моделирование может выполняться как в форме фун¬

кционального контроля, т, е. проверки логики работы проекта без

учета временных соотношений и задержек распространения

сигналов на логических элементах, так и в качестве одного из

этапов верификации завершенного проекта.

Синтез. Преобразование VHDL-ÿÿÿÿÿÿÿÿ в набор примитивов или

логических элементов, которые могут быть реализованы с уче¬

том конкретной технологии.

Компоновка, монтаж н разводка. Отображение проекта на карте

синтезирующих элементов, содержащихся » СБИС.

Временной анализ. Получение фактических задержек реализован¬

ной и СБИС цифровой схемы проекта с учетом длины соедине¬

ний, электрических нагрузок и других известных факторов.

ГЛАВА

2

УРОВНИ ПРЕДСТАВЛЕНИЯ И ФОРМЫ

АБСТРАКЦИИ ЦИФРОВЫХ СИСТЕМ

Глава 2. Уровни представлении и формы абстракции цифровых систем ш

[5

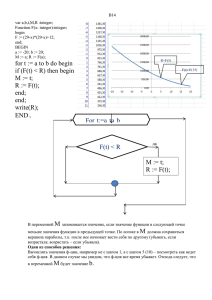

Как видно но Рис. 2.1. цифровая система может быть описана но

уровне комгюнснюи (транзисторов, диодов, логических племен гон),

на уровне архитектуры (структурной схемы, содержащей ЛЛУ,

регистры, компараторы и т.д,), на уровне автономной системы (ПК.

рабочей станнин, сервера и г л.), а также на уровне приложении

(программных модулей, входящих в состав систем более высокого

уровня).

Различные формы абстракции цифровой системы дают иозможиость сохранять описание и проект как комплексную управляемую

систему. На Рис. 2,2 показаны различные формы абстракции.

Цифровая система на языке VHDL может быть представлена на

различных уровнях и различными формами абстракции. Представле¬

ние цифровой системы на нескольких уровнях абстракции показано

на Рис. 2.1,

ПрИЛОЖвНИЙ

ГР

А +

в

Поведен ноская

Структурная

форма:

форма:

поток данных

I

Системы

Рабочие станции

’

межкомпонентные

алгоритм

1

I

!

ПК

s <-

связи

ran

Онэичвекэя

реализация

I I

Серверы

i’uc. 2.2. Формы абстракции: поведенческая, структурная и физическая

Я

А лшооурп

Компоненты

Z?

<

-W-

о-

/Уте, 2. /, 1 1редсм имение цифровой системы на нескольких уровнях абстракции

—

Первичная и наивысшая форма абстракции

это поведенческая

(behavioral) форма, которая позволяет описывать систему и терминах

того, что она делает (или как она ведет себя), а не и терминах ее элементовлибо компонентов и соединений между ними. Поведенческая

форма представления определяет зависимость между входными л вы¬

ходными сигналами, Поведенческая форма может быть булевым

(Boolean) выражением либо более абстрактным описанием, например

описанием межрегистровых пересылок (register transfer) иди описанием

в алгоритмической форме,

..........

......

Глава 2. Урании представления и формы сфрпщркцми цифровых систем я 17

16 ■ Г.юна 2. Уровни пряктм ‘опт и формы чЗстрикшш цифровых систем

и качсстпе пример»

поводе нчсско;! формы раеемот-

рпм Простое jÿTpuiicruo SIREN, которис ВЫдаСТ СИГНаЛ П(ЙгДуПр.еЖДеЮм {warningj веяЮТй рдэт кош ™ШоЕияьн$гй ключ вставлен в за*

мокзажпглкйя flgnit j on .onJ, если дверь открыта (DOC reopen) или

отстегнут реме]ijs; безо пасноети г i :it _of fj. I!» повела

уровне это словесное on иелние может быть выражено как;

шнеком

■

warning

-

iflniti a..on

and (Do r_open or seaibeltÿoffJ

Структурная <stru6lural> форма, c другой стороны, прсжмиикч

как на flop логических элементов и ком по центов, которые

с

чаны между собой гаким образом! чтобы нимол нить нужную функцию.

Гтруктурмуюфот'му предела вяв и ИЯ можно сравнить со схемным ре (не¬

мцем связанных логических вентилей. Структурный уровень является

нстоЦ

свЦ

...

.....

реализации

сис¬

окончательным Представлением физическом

Структурное

представление рассмотренного выше примера по¬

темы.

казано на lJirc. 23.

о

DOOR

IGNITION

SBELT

с

В1

WARNING

32

Рис. 2.3, Структурное прсдстпилсияс усграПетм si HEN

Как говорилось выше, я тык VI!DL позволяет описать цифровую

систему м и структурном, и й{поведенч&!кой форме. При этом гюиеденческая форма может быть реализована п одном из двух стилей: в виде

но/пока данных (dm a HT>VL si>te) и в

виде (atanrimiic

.......

алгоритмическом

style).

Представ] сние сметемы и виде потока данных позволяет описать

систему с учетом направления потока переметаемых через нее ламЭтот стиль характерен дгш описания поведении системы на уров¬

не

пересылок.

При представлении системы в алгоритмическом виде поведение

системы описывается с помощью операторов (operator). При этой для

описания поведения системы могут использоваться кик операторы лераш'лъноЦ обработки (concurrent), которые выполняются параллельно,

межрегистровых

как только

денные поступают на входы, тли м

посхедовЩерыше

которые выполняю! е я последовательно и по¬

рядке их записи. Язык VHDL допуск нет как параллельную, так п последоительную установку значений сигналов, которые определяют

способ н порядок их выполнения. Примеры обоих представлений бу¬

дут даны в но следую!них главах книги,

(sequential) операторы,

ГЛАВА

3

3, /, Общие сведения ш 19

БАЗОВАЯ СТРУКТУРА VHDL-ÿÿÿÿÿ

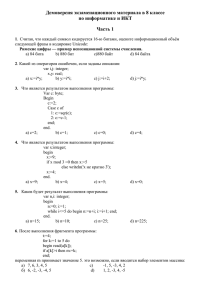

Оператор ы языка VHO L

1

I

Л

ЁСпгэ«агят<1Л№)1Ы1

Sntp-iFinpi- 0(1'ЬРвкГЧМН

&ЫП&№ИИ«№ЫЧ1

WpftlPfM

иярч/Э «тям

1 Argp£#A;q ПРИРГН IjMtl t*}

2 Двямгвпдоы провети

CtrhitM-ÿÿ*!'

?J rÿÿp«U4lilMK ВМЫПЦГ 2Й -11Г|»1»*ш1шЗ

ВЁтрННМиЙ И ПСГЬМШГВтгМви

В1ЦЦНП«!РЫ

e Sr«*iqp pragapti.

COfiPpMHIUÿJ

!!4MI!U|BNNtCPCrfl

■

Т*ГЮ6

■

3.1. Общие сведения

Проект любого ЦУ на языке VHDL -- з го прежде всего программа,

которая содержит ключевые и зарезервированные слова. Эти слова не

могут использоваться как имена сигналов или как идентификаторы. В

языке VHDL ключевые слова, зарезервированные слова и определяе¬

мые пользователем идентификаторы нечувствительны к регистру.

Строки с комментариями в VHDL-ÿÿÿÿÿÿÿÿÿ начинаются с двух

смежных дефисов (--) и при компиляции игнорируются компилято¬

ром так же, как символы конца строки и пробелы.

VHDL — это строго типизированный язык. Это означает, что все

программные элементы данных (константа, переменная, сигнал)

должны явно объявляться с обязательным указанием типа элемента.

Тип, указанный в объявлении программного элемента данных, опреде¬

ляет информационные характеристики этого элемента, диапазон до¬

пустимых числовых значений, которые может принимать этот про¬

граммный элемент, а также операции, которые могут над ним выпол¬

няться. Кроме того, в языке VHDL, в отличие от других строго

типизированных языком, не допускаются операции над разнотипными

элементами без предварительного преобразования типов.

В языке VHDL (как и и классических языках программирования)

из ключевых, зарезервированных слов и других лексических элементов

строятся образования, которые принято называть операторами. Опе¬

ратором в языке VHDL считается любая запись, начинающаяся с клю¬

чевого слова и заканчивающаяся символом точки с запятой

Диа¬

грамма, иллюстрирующая одну из возможных классификации опера¬

торов, показана на Рис, 3.1.

ОГЧ**ТврУ ■Ицус’ТИК.А

фвд/иы ГЦИИеТРВЛРРМР ПРНЛЯ

Сг«р|'йпи

ef*f»iepmiJib

■ Wtffiiiep- bayl п

■ егччяггер ««4

»gHni-n-l00*Jt*jrit;

•

тазечан-ныс lÿnKiiM*)

* ivrUBTO

* fttprai jiignall

tj

*

4. ИЬзль

r.

tjSBS

ыгягы:

iMrwi .nmiMujj

гаыЕЬиоторнаА пагод*

4y»lsi|rt* [ftincllnn’l

ii

ЦУ

-OfteNnUPBl

<41“>

anepnopf рпйийЬр

-СЛйркЛДй еег.Г Lg'itrbiian

гранта

спорим ptfit euLji

амягори $ц*евкй* цу

п&№£вач№Ы1рА Срагмярвврй|» гагн№

\

(PFB>?«ÿ*IX*3

npwnp» iÿs**rleii

7.

, 0, 1 «МЭ Г ггч («‘ÿFBI***!?)

(HjMSiaiBBSlJ ГЬйрнииы* лет? Hi

utrfe ЦЗНЬ1ЛХ |ÿcFnMflfti

i.)

В МИ**

нь*.

(blit. kb! тгйиЧ.0 г,

lri.-.]*F, F»* !, 4iP*«,

■Tti_LwiJtÿvee L J r, c&MABtflir,

wa s*sГйкеа r.'H c

ь= =

нHI объ я а-чiwnпялЬ5зят?ш»и

tÿ*.

гри

PiBSFWB

г

змГ'».ТУГИ

Н$*<нс ОДЬтА

OfWpatCp ресвшии

Ij

V** *ЧЬ *1* i{ j"j

я

WMpawp рымь**

PI——-—

*

j

I

‘Эпьргиц трюетоё

yclz wa w ггагажнл

уелйневчи агененРЛ

гзияапа |.СУ9С||

сигнзг a (fflVSG]

-

«

Crt*ptT0p-fWC4* yST*»-S4

МЧВИч*

щук;.

ФГарНГВД iiijbE

« тгирнгж HowsteftHm

«

смparse мкми -рс1#дури

ГГ яр Я' эр ыюм фумидо

з сз'арагор if

’

даиинмм струят/р ч фчр«РЦГ

ПрМйГяЬЧМ«Я ItJWft. WWW

енп#равп{ии*( nepwwiÿ qRfiiAn-

ПРИ1ИЧМ4ИВ 3.

£г Ярви гр c4r*»rni«?*

twonepmpfci. Гта;-

№ lorloj

rJs*c г адом*■*-*

ычрлтер ргччимгр

я «&т*рнГ5& иш11

ИВ *СГрМ4-»ы(

LMJIJ

;

j ;

Criftpirap

ус/

з

тгарвггр пним keep

янон J,4T:SH&|K(3 3Hfr*P*4> G*T*3l“4 (¥УЭС|<

пргыуямь* ItnjR Biiiflfc’iJg ЦУ rt»би-ядсрнё* гЮгока дагр пчи ОПО

Vue. 3. !. Классификация оператореш языка VIi DL

В языке VHDL операторы с точки зрения их функционального

программного назначения (как при поведенческой, так и при струк¬

турной методологии описания проектов) принято делить ив лис основ¬

ные группы;

• Операторы объявления программных элементов данных и их ти¬

пов, компонентов проектируемого ЦУ. их интерфейсов и архи¬

тектур, пользовательских типов, а также функций и процедур.

• Выполняемые операторы.

Кроме основных операторов в языке VHDL принято выделять еще

одну группу операторов, которую называют вспомогательными операторами передачи упрощения.

20 ■ lluwa

J, l, Общие сведения ■

Базовая структура УН1)1.-1/кш.ш

С точки зрения конструктивного устройства операторы обеих

примято подразделять на дна класса:

*■ Простые (однострочные) операторы. Простой оператор представ¬

ляет собой текстовую запись, располагающуюся, как правило, на

одной строке, которая не содержит других операторов,

• Составные (многострочные) операторы. Составной оператор пред¬

ставляет собой текстовую запись, занимающую, как правило.

много строк, которая содержит другие операторы.

Е! структуре языка VHDL. имеется д ш фундаментальных опера горл

(составные по своему конструктивному устройству), которые подде¬

рживают принцип системного проектирования. Принцип системного

проектирования предполагает, что любое проектируемое ЦУ рассмат¬

ривается как автономная подсистема, которая должна иметь:

• идентификатор (т. е. должна быть объявлена);

• способность взаимодействовать с другими проектируемыми под¬

системами посредством своею интерфейса (входиых/выходных

портов);

• описание внутренней структуры или алгоритма функционирова¬

1'рупп

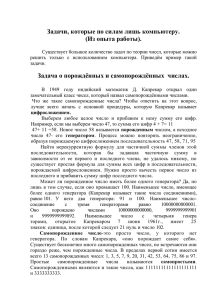

входные и выходные интерфейсные сигналы, в то время как

архитектура представляет собой набор таких взаимосвязанных программных элементов. как подчиненные компоненты, операторы

ПНС1ШШС

параллельных вычислений, последовательные

операторы, подпрограммы (Рис. 3,2). 11 типичном проекте содержится

несколько таких взаимосвязанных объектов, предназначенных для вы¬

полнения преобразований, в ходе которых и обеспечивается собствен¬

process, операторы

но требуемая функциональность проекта.

VHDL-ÿÿÿÿÿÿ

Порты

Интерфейс

(огоратор entity)

in

out

incut

Архитектура

(егюряюр

architecture)

псслй»тс**ткч»ные

ния.

-I -

Такими фундаментальными операторами в языке VHDL являются

олеранры, ОНО,

елерзисы *>««■»,

операторы:

entity

.. end entity

architecture

..

(orepniapw

CCL«por.BHt‘i

I

.;

end architecture

I

..;

Проект НУ, или его компонент, описанный с помощью языка

VHDL, хранится и файле, который обычно снабжается расширением

VHD.

Представленный в виде VHD-ÿÿÿÿÿ проект ЦУ может содержать

другие объекты (лодсисгсмы), которые в тиком случае являются под¬

чиненными компонентами системы верхнего уровня.

Любой компонент, независимо от того, является ли он автономным

либо подчиненным компонентом, или же системой верхнего уровня, в

спою очередь является совокупностью интерфейса (entity) и архи¬

тектуры (architecture).

1) объявлении интерфейса (entity declaration) содержится объявле¬

ние портов (ports declaration) проектируемого компонента е внешним

миром. Объявление портов проектируемого компонента определяет

21

■u;'-,

—-

n*r.

Й¥1#9»НЧ

Щ*

л

I

№*ар«вАс

ни".1;1 sAtl Ну)

tJg

ШИИЬч**«■*»!>

iittcTjEwi

*(rv

wa-ÿÿÿ

;ПаЯ,ПрЙф1(ДМи

I

Пцш

KhOL JMeifl

-Т*у.

" .4Mi*4gMiut|i

t:

Нитцфй*с

WV4—

«сЬгьм

адй11ммй

гН■ ■'.v

S*£.J&L\3£mi

и s:I

*4 иъ ГМ ■ALHjl

шч

И

В

Ш\

Ш

Гиг, ,J,2. VHDL-npotKT, П|Х;лпавляя собой «люкун чисть инттрфсДся и архитемури, может исполкомть оувпроокты в качестве компоисятоп, а также пшил в ка¬

честве компонента и VHDL-ÿÿÿÿÿÿÿ Солсе иыеокого уровня иерархия

11 ■

{'лани 2.

3.2. Оймадаше интерфейса и

Fiusoew! структура УНШ-фаНш

3.2. Объявление интерфейса

кой вид:

entity '.ШЯ_КСШ0НЕ‘НТ2 is ( generic

port ( СЯГНЛП1 ! рожны Til!ГГ

i

JGJKIW?

•

'-'т.

елешм) i )

сигнал! : режим run;

СНГ HQJtNi

end [entity.

—

bit_vector.

.

;

Как видно из приведенного синтаксиса, объявление интерфейса

начинается с ключевого слова entity, за которым указываются

имя проектируемого компонента и ключевое слово 1в. Далее в объяв¬

лении интерфейса с помощью ключевого слова port размещается

объявление портов, Объявление интерфейса всегда заканчивается

ключевым словом and, после которого могут указываться ключевое

явлении интерфейса можно опускать),

Входящие в конструкцию объявления интерфейса проектируемого

компонента (т. е. проектируемого НУ) элементы имеют следующее на¬

значение:

* ИМ Я-КОМПОНЕНТА

определенный пользователем иденти¬

— списоквнешние

фикатор проекта.

•

та).

разделяемых запятыми идентнф и кагоров,

интерфейсные сигналы (порты проек¬

— ключевое слово, показывающее направление действия

сигнала (порта):

режим

• in ключевое слово, используемое для объявления входных

сигналов;

■

out — ключевое слово, используемое для объявления выход¬

ных сигналов. Значения выходных сигналов могут считываться другими проектами;

bit

—

character,

std_logic

I!

—

состоящим

(0 to 7);

■

слово entity, а также имя компонента (дна последних элемента н объ¬

представляющих

Boolean,

может принимать значение или 0. или I;

, bit vector

зарезервированное слово, показывающее,

что сигнал, переменная или константа являются вектором ,

всегда

* сигнал;

—

stc„ulcgic.

релин run);

1 ЖЧ_Х0Ш0>Ш7Л‘:

•

—

ключевое слово, используемое :UIH объявления

внутренних сигналов. Значения сигнала с этого порта могут

читаться только внутри архитектуры проекта;

ключевое с,юно, используемое для объявления сиг¬

■ inout

налов, которые могут быть как входными, гак И ВЫХОДНЫМИ,

тип зарезервированное слово, используемое для объявления

определенного пользователем типа сигнала, переменной или

константы, Примерами встроенных типов являются: bit,

buffer

■

В соответствии с синтаксисом языка VHDL объявление интерфей¬

са проектируемого компонента начинается с ключевого слова entity

и определяет имя компонента, а также содержит объявление входных и

выходных портов, Общий синтаксис объявления интерфейса имеет та¬

Д-1

•

■

■

.

*

из значений типа bit, например bit „vector

Btd_logic_vector,

std_uiogic,

std_le>gic,

s t d_u 1og i c_v e c: t or — зарезервированные слова, показы¬

вающие, что сигнал, переменная или константа могут прини¬

мать одно из девяти значений, отражающих его силу и реаль¬

ные физические значения. В проектах ЦУ предпочтительнее

использовать типы Btd._logic, std_ui ogic, чем типы bit,

bit „vector;

ос слово, означающее, чт о сиг¬

boolean

нал, переменная или константа могут принимать одно из

двух значений: TRUE или FALSE;

integer — зарезервированное слово, означающее, что сиг¬

нал, переменная или константа могу! принимать одно целое

значение, пои алию тес и указа; t н ы й дна i ia зон;

зарезервированное слово, означающее, что сигнал,

real

переменная или константа могут принимать одно веществен¬

ное значение, попадающее в указанный диапазон;

зарезервированное слово, означающее, что

'rhat денег

сигнал, переменная иди константа могут принимать значе¬

.....

.............

—

—

ние пе'гатаемого ASC 1 1 -символа:

зарезервированное слово, означающее, что сигнал

г. пш

или константа снабжены единицей измерения времени,

—

24 в {.та 3. Вашая структура VHDl..-<j*uua

•

generic (общие обьяоления) i

3,2. Обшеыеиие интерфейса * 25

объявление generic является

факультативным и определяет локальные константы, используе¬

мые для задания временных параметров и разрядности (напри¬

мер, разрядности шины) проектируемого ЦУ. В объявлении

generic могут указываться значения, не пользу мыс по умолча¬

нию. Синтаксис для объявления generic следующий:

generic (

ння кс>нствнты1: тип [.= значение]

нмя_ цонстан?к2 ; тип \ ;? значение]

имя_константнЯ1

;

;

тин [: -значение] I;

Лля примера НУ SIREN, структурное представление которого по¬

казано на Рис. 2,3, объявление интерфейса имеет следующий вид:

--

Припер объявления интерфейса лля ЦУ SIREN 1Рис. 2,3

entity SIREN la

port (DOOR, IGNITICH, 53ELT; in std_lorjic;

WARNING :

out

Std_logiC);

end SIREN;

общем случае it физической цифровой системе сигнал может прини¬

’ X 1 (неизвестное значение),

мать бинарные значения j или

(безразличное состояние) и

(неициалнзиропанное значение),

рял других (полный перечень значений приведен п подразд. 6,2.2). Оп¬

ределение типа E'.:d_logic находится п пакете :::td_logic_i 1 б -1

библиотеки iceu, Тип определяет набор значений, которые объект

1

1

может иметь.

Приведем сше два примера объявлений интерфейсов проектируе¬

мых объектов.

Объявление интерфейса 8-битного мультиплексора 4x1

entity mux4_to.J ie

port (10,11, 12,13: in 3tdLl03ic_vector (1 downto 0);

downto C ; j ,ÿ

СУТ1: out stcLlogic_vectoi

er.d тш4_то_1;

Объявление интерфейсе D- триггера со входами установки и сброса

entity dff_sr is

port (D, CL.K, S, R; in f--d_lcgic;

C , Qnot : out . 1 d_log i с I :

end d£f_ni-;

1

Как видно из объявления, проектируемый интерфейс имеет иден¬

тификатор SIREN, содержит три входных порта (DOOR, IGNITION* IE

SSILT) ii один выходной порт (WARNING). Обратите внимание на норядок их размещения и наличие в оформлении точек: с запятой1. Вход¬

ные порты обозначены с помощью ключевого слона in, а выходные

- с помощью ключевого слова

out. Так как язык VHDL является

языком со строгим контролем типов, и объявлении каждого порта

имеется указание о его информационном типе. Тип определяет набор

значений, которые могут присваиваться объекту (и данном случае —

сигналу). 13 этом проекте мы использовали тип std_Iogic. Это на¬

иболее предпочтительны)) тип для цифровых сигналов. В отличие oi

типа bit, который обеспечивает поддержку только бинарных значе¬

ний 1 или '0', типы :;td_iogic и stdLulogic позволяют при¬

сваивать соответствующим элементам данных одно из девяти значе¬

1

ний.

Использование типа std_logic и stcLulogie дает возможность

точнее описать значения сигналов физической цифровой системы. Н

Примечание. В языке VHDL любой конструктивный элемент, начина¬

некоторым ключевым словом и заканчивающийся ключевым сло¬

вом end и символом « /» (точка с запятой), принято называть составным

оператором. Однако операторы могут быть не только составными, т. е.

содержащими в себе другие операторы ( часто говорят , что составные

операторы «содержат тело*), но и простыми. Простые операторы раз¬

мещаются обычно в одной строке, не имеют ключевого слова end it

ющийся

всегда заканчиваются символом « ; » (точка с запятой).

Анализируя синтаксис объявления интерфейса, можно заключить

следующее: любой проект ЦУ реализуется и языке VHDL с помощью

end (entity] . . . ;. Этот оператор по своей

оператора entity,

конструкции является составным оператором и содержит другие опе¬

раторы. Так, и приведенных выше примерах составной оператор имеет

н своей конструкции оператор port ( .

. ) ;.

2(i К

Рима 3, Битовая структура

3,3, Архитектура проекта Ш 17

3-3. Архитектура проекта

Архшгюшура проекта (агсщйсшге body) определяет логику работы

схемы проектируемого ЦУ, г. е. уста напли наст алгоритм работы ЦУ. и

форму ее реализации {поведенческая иди структурная).

Примечание. Как eotfopiuocb выше, VHDL-ÿÿÿÿÿÿ ЦУ может иметь

разные формы представлена.л; поведенческую, структурную гин их комби-

нацию.

Синтаксис объявления архитектуры проекта имеет следующий вид:

architecture Ихя архитектуры (А ИХЯ_К0Н1ШЕКТА in

Объявления:

-- КОЬ!ПСИ&!!ТОЯ

-- сигналов

--

—--

—

--

begin

--

констант

функций

процедур

вычисления

архитектуры

ТИПОВ

Интерфейс и архитектура (поведенческая форма) дцухвходовото

логического элемента AND

Выполняемые оператору параллельной обработки.

entity AN I i is

port (ini, in2; in sta_].CÿiC;

:_1 gijc)|

И l : Out

Архитектура проекта в поведенческой форме

П опелем ческа я форма архитектуры проекта, представленного

Рис. 2.3, и мест следу гош isii вид:

architecture

behflV of SI REN

на

in

begin

WAKilMC <=

значения

..

end f awhit ecture ) Имя_ , архитектурi:;

3.3.1.

ьстстомя его си таксиса требованиям языка VHDL. li рассматриваем

мои примере компонент SIREN но ймеет;|вно оформленного раздела

объявлений вследствие его ненадобности:. Основная часть архитектуры

проекта шздел выполняемых операторов параллельном обработки)

начинается ключевым еловом begin. Он обычно содержит описание

внутреннего устройства (т. и. функциональности) проекта в форме бу¬

левых функции, оформленных в виде операторов параллельной Обра¬

ботки ЯЗЫКА VHDL

Как говорилось |ышс, Поведенческая форма проекте может быть

описана несколькими способами. № частности, в этом Примере основ¬

ная часть архитектуры проекта содержит один npocroi i оператор уста¬

сигнала, ti дай ном операторе имеется символ * *, ко¬

новки

торый означает, что сипи ту, стоя тему еле ва Ьт символа -■ », устанав¬

выражения, стоящего справа от

ливается результат

Ос нон мал часть архитектуры проекта заканчивается

символа г.ключевым словом end, которое может дополняться ключевым словом

architecture is именем архитектуры.

проекта.

Рассмотрим еик два примера оформлении

not TJOJR ana IGHITIO!) or (not j&BELT and IGNITION Г ;

end bebav;

В строке заголовка архитектуры проекта присутствует i где цти фи ка¬

гор архитектуры {в данном примере behav),. который играет роль

имени архитектуры и связывает эту архитектуру с объявлением интер¬

J) качества имени архитектуры может использоваться

фейса :

любой цдектифп каток выбираемый пользой и ел ем, при условии соот-

--

end AHD2(

architecture

behavioral J of .!Я0/ is

bEgin

Olitl <- ini and ir.2 r

end ;x]iavioral_2 j

Интерфейс и архитектура (поведенческая форма) двухвходового

логического элемента XNOR

entity КША2

la

port (л, В:

7, ;

In SCtLIoglC;

out stiLiugie :

Г

end XN0R2r

—

architecture i.iiimvicu i lÿjtntsi oC XN0R2 ia

Объявляю» внутренних сигналов К н

У,

3.3, Архитектура проекта

28 ■ Глава 3. Бажова» структура yfiDL-tfuiwia

signal X, T: i;ed_lo{iie;

begin

X

A ar.d 3;

У

.not A) and : not В) г

X or У;

2

end I . -ha v ior а 1 _xno r j

Операторы установки значения сигнала («<=*) в этих примерах со¬

держат логические операции and, or и not. Кроме указанных, в та¬

ких операторах могут использоваться операции nand, nor, хог и

xnor.

ш

29

Архитектура проекта в структурной форме

3.3.2.

Проект, показанный на Рис. 2.3, можно также создать, используя

структурную форму архитектуры, которая сводится к описанию проекга через майор логических элементов, или компонентой, и связей меж¬

ду н\ входами и выходами. Вариант такого структурного описания

имеет следующий вид:

architecture f;r: • of SiBEh' ip

Объявление компонентов .1

■

component AMPS

m2: in std_logic;

out I : out nr d_l: Tie} ;

port (ini,

Примечание. Следует особо заметить, что операторы установки то¬

чении сигнала (signal assignment statement) и вышеупомянутых примерах

жинются операторами параиелъной обработки (concurrent processing).

Такие операторы выполняются параллельно, когда один паи больше сигна¬

лов, входящих в состав выражений, которые расположены в правой части

оператора, изменяют свое значение (т. с. когда хотя бы на одном из еигttaioft происходит событие). Например, когда сигнал порта л изменит

свое значение, одновременно изменят свои значения внутренние сигналы :<

и у, которые в свою очередь одновременно (во всяком случае о идеале)

заставят последний оператор модифицировать значение сигнала на

выходном порту ". (В реальных цифровых системах при распространении

сигналов может существовать задержка, связанная с этими изменени¬

ями.)

Физические 1{У управляются данными, и также событиями, возиика¬

ющими при изменении донных. То есть событие, которое происходит на

одном из сигналов, приводит к появлению события на другом сигнале, и

т, д. Выполнение операторов детерминировано потоком изменении точе¬

ний сигналов, т. с. определена последовательностью возникновения собы¬

тий на сигналах. В результате такого принципа функционирования

порядок, и котором операторы параллельной обработки располагаются в

основной части архитектуры проекта, может быть любым. Иными сло¬

вам, если разместить оператор 7. перед операторами X и у. конечный

результат от этого не изменится. В ином состоит главное опыичие

языка VHDI . от языков программирования, в которых операторы выпол¬

няются последователь но или путем вызова процедур.

or.d component ;

component 0R2

port I

ini, in2 : in 3-a_logic;

out stcSÿliTicj г

out

end component:

component КДТ1

port i ini : in ;t;l_ logic;

out 1: out sttL'ogieP;

end component:

-- Объявление сигнйлон, испопъэувкнх для связей

3i, B2: sUL-iogie:

signal 1х,:;к_зйТ,

begin

Операторы реализации компонентов.

U0 : NOT 1 port map (DOOR, DODRJ'ICT) j

:

HI : N Ti port map ! SBRI.'l , .'PF.t.T

U2-. AND2 port nap (IGNITION, OOORJJOT, BU:

U3: AND 2 port map (IGNITION, SBELT_NQT , B2};

УА : OR,' port map (SI, 32, WARNING})

and acructj

--

компонент. н,

.

Если архитектура проекта имеет структурную форму, после заго¬

ловка архитектуры располагаются объявлений компонентой, которые

предполагается использовать в проекте- !! приведенном выше примере

проекта SIRoN использованы два двух входовых логических элемента

AND, один двухвходовой логический элемент OR и инвертор- Эти ком¬

поненты должны быть определены, г, с, их VHi>l.-проекты должны

уже существовать (объявления интерфейсов этих проектов приведены

в предыдущих примерах). Все VHDL- проекты компонентов ЦУ также

II Лрхшлекщра щхнкта ш 31

30 ■ Глава I Базовая структура VHDL -tfxiina

могут быть сохранены н виде одного пакета (package). доступ к которому можно получить включая объявления библиотек к пакетов и затоловок проекта (с.м. ДЕьлее разд. 3,4). Объявления компонентов содержат

описания входных (например, ini. in2) и выходных (например,

out 1) портов,

Затем необходимо определить внутренние связи путем объявления

именованных сигналов В нашем примере эти внутренние сигналы име¬

ют имена D00R_K07. SBELT_;-:OTT HI, 32 (слг. Рис. 2.3), Обратите внима¬

ние на то, что и объявлении сигнала всегда требуется указывать его тин.

При структурной форме в разделе выполняемых операторов архи¬

тектуры проекта (г. е, после ключевого слова begin) должны распола-

ыш.с>1 операторы реализации компонентов, а также операторы, опи¬

сывающие взаимосвязь компонентов между собой, Каждый оператор

реализации создает новый уровень иерархии и начинается е имени ре¬

ализуемого экземпляра компонента (например, U0), сопровождаемого

двоеточием, идентификатором самого компонента и ключевым сло¬

ном port map, 1оВОрЯТ, что оператор port map рент иэуст между ком¬

понентные связи объявляемого в нем конкретного экземпляра компо¬

нента.

В частности, н рассматриваемом примере междукомпонентные

связи экземпляра U0 компонента NOT) определены посредством «ознционной (неявной) реализации: внешний сигнал DOOR соответствует

входу ini логического компонента MOTI, а внутренний сигнал

DCORJIOT выходу компонента NQT1, Точно так же для экземпляра

и?:-. AND2 мерные дна сигнала (л;кг: неги гоок_кот) соответствуют

входам ini н in2 компонента АМШ соответственно, а сигнал в1

выходу out 1 этого компонента.

Альтернативный метод определения межкомпонентных связей со¬

стоит в использовании именованной (явной) релнзапии связей между

портами. В этом случае синтаксис оператора реализации имеет следу¬

ющий вид:

—

.,

U0:

U2:

N3:

U'l:

фические изображения больших интегральных ЦУ. Таким образом, не¬

сложно прийти к заключению о том, что иерархическое проектирова¬

ние всегда предпочтительнее, чем одноуровневое.

Давайте рассмотрим использование иерархической технологии

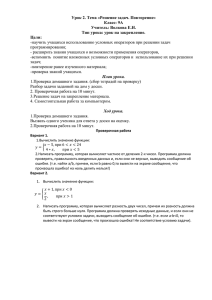

проектирования на примере проекта 4-битного сумматора, показанно¬

го на Рис. 3.3, Как известно, любой полный однобитный сумматор мо¬

жет быть описан следующими булевыми выражениями, используемы¬

ми для получения суммы (sum) и сигнала переноса (carry),

sum я (АФ В) © С;

—

сигнал', порт? - сигнал?,

компонент pore map (порт:

nopriv »> сигнала) s

N0T1 port тар (ini -> DOOR, out 1 => DOQRJNOT) ;

HOTl port map (ini => SBELT, out 1 => $BELT_NOT> ;

AND2 port map (ini : IGNITION, in2 > DOOB_NOT, out 1

B‘,'r;

AHD2 port map (ini => IGNITION, in?

SBELT „NOT, R2);

0R2 port map (ini > 01, in2

Б2, out 1 => EARNING) :

Экземпляр:

Ц1:

внимание на то, что порядок, н котором эти операторы

приведены в разделе выполняемых операторов архитектуры проекта,

не имеет никакого значения и не сказывается на конечном результате.

так как эти операторы выполняются параллельно, Это объясняется

тем, что схемное решение, которое описано этими операторами (гм.

Рис. 2.3), нс зависит от порядка расположения операторов, поскольку

оно фактически определяется списком выбранных компонентов и

жестко установленными соединениями между ними,

Теперь вернемся к тому обстоятельству, что структурная с|отрма ар¬

хитектуры, как уже отмечалось выше, позволяет создать иерархичес¬

кий VJ-fDL-ÿÿÿÿÿÿ, Е! котором заранее определенные компоненты мож¬

но использовать многократно. То же самое относится и к самому высо¬

коуровневому проекту, который и свою очередь может являться

компонентом для проекта еще более высокого уровня иерархии, и г, д.

Это свойство VHDL-ÿÿÿÿÿÿÿÿ позволяет значительно упростить гра¬

Обратите

carry = АВ + С(А© В).

Ь(3)

j

b

FA

carry е

ОД

■

■

зит(З)

•

■

IVc,

а{2)

Ь(2)

Iь т -fit*

Г

Ccutl

0(3)

од

FA

carry с

sum(2)

Ш

ИИ

а(1)

Ь а

FA

carry с

?игп{1}

Ь(0)

э<0)

1

&

cm

л

FA

■

carry с С(0) Cin

sum(0)

.и. Схем л 4 fiHTHorot ум Miimpn, построенная ha полных однобитных сумм,порах

■

32 ■ Г ниш 3. Бд-мнмя структура У/Ю1.-г/уи.ш

3.4. Б\&тотеки и пакеты

В VII DL- проекте Fои R л I т ADD мы определим субпроект (т, с,

VHDL-ÿÿÿÿÿÿ более низкого уровня иерархии) полного однобитного

сумматора FULLADDER, а затем используем его в качестве компонента

основного проекта. Обратите внимание на то. что архитектура

f u I. :add( : с.и -hav проекта FULLADDER имеет компонентную форму,

поскольку в ней не нужно использовать несколько экземпляров одно¬

го и того же компонента. Архитектурой fouradder_s true tore про¬

екта FOUR в г:ADD, имеющей структурную форму, реализуется четыре

экземпляра полного олнобитлого сумматора. Обратите внимание так¬

же на ключевое слово use, задействованное is проекте FOURBITADD, с

помощью которого к проекту подключаются внешние библиотеки и

пакеты (подробнее о них рассказывается далее),

-- Пример проекта 1 -битного сумматора.

library 1Сйе:

us о : ео f. at d_ioti i o_ 1 о 4 . Ш;

-- Субпроект полного одкдбитког: сумматора.

?

'

xor b) xar c ;

I and Ы

or {c and (a xor b) } ;

end ful ladder Jjehav;

* (a

■

J

'

вА-А

br c:

in

sttLloflic;

s;un, carry: out stcLlcgic) ;

end component;

begin

FA 0 : PULL ADDER

port nap

:

i

( C' ; ,

FA1: FULLADDER

port nap la(J

'

,

bf 0 )

C i ft , £ illn { 0 1 , с ( 1 I ) :

Ы1)

C<1-, SuaHl)

c(2':i;

FA2 i FULLADDER

port mnp fa 12), bi21

i

Ci2 ■,

:;on|2)

c(3::

j

уровням иерархического проекта. Однако для облегчения восприятия

текстов VHDL-ÿÿÿÿÿÿÿÿ на практике желательно назначать более ос¬

мысленные и уникальные имена.

J

3.4. Библиотеки и пакеты

Основной проект 4-битного сумматора.

library ij

UBS i :оз. :U . J_ : r i ; _.l 164 .all;

Объявление интерфейса FOURS JTADD.

--

--

entity FOURBITADD is

in s td„.l on ic_ vector (3 down to 0);

Cin: in std„logic;

sum: out std_logic_veetor (3 downto 0) ;

port (a, b:

Cout, V: out StcLlOgic );

ond FOURBITADD;

-- Архитектура проекта FOURBITADD,

port d,

Обратите внимание на то, что в проекте 4-битного сумматора ис¬

пользованы те же самые имена для входных портов, что и для портов

полною однобитного сумматора (они названы , и Ь). Это нс вызывает

проблем и языке VHDL, так как ли названия относятся к различным

а

begin

■

signal

end Eoutudd*n „at j ueturo;

'

rum

* lot

’ 1Ы.I -J<

nf FOURS I'TADL ie

[4 downto 0)

std_3ogie_vector

e:

conponent FULLADDER

architecture t

part map (all), b ■: 3 f , С{3), зит 1 3 ) , c{4

V <= c ( 3 ; коx c < 4 ] ;

Cout <= c(4l;

Объявлокио интерфейса FDLLArDER .

entity FULLADDER is

)i

?

port i a, b, c: in std„lojic;

V OV

;um, carry : out std_logic( ,'

end FULLADDER;

-- Архитектура лроехта FULLADDER.

architecture fulladdtr Jbehav of FULLADDER i6

I

carry

33

FA3 : FULLADDER

-■

I

Ш

Со

Ццйшотено (library) u VHDL

это нечто вроде каталога, и котором

компилятор получает недостающую информацию, используемую в

разрабатываемом проекте, но отсутствующую в явном виде в самом

проекте. В качестве пакета (package) компиляторы VHDL используют

библиотечные файлы или модули, которые содержат объявления на¬

иболее задействованных объектов: типов данных, компонентов, сигна¬

лов, процедур и функций и т. н. Применение пакетов позволяет подоб¬

ные объекты многократно использовать » разных VHDL-ÿÿÿÿÿÿÿÿ.

Например, как отмечалось выше, тип данных 8td__.logic опреде¬

лен и макете ieee.std_logic_U64, который входит в библиотеку

ЗЛ $<&шшекяЩ&хкяш я 35

34 Ш Гш#а 3. Hthvsex сщ/пцтура VflBL-'ÿÿ и!

Поэтому, чтобы и VHDL- проекте 1 1 <е ею;г ьюемът ь 'LL 111 etd logic,

требуется подключить к проекту соответствующие библиотеку и ткет.

Эти операции выполняются я начале VHDL- проекта с помощью кдЫ:

чсных ел on library и ива фотаетегиеннез, мл пример, таким Образом:

%«b.sbd_igHicjfll£i4.all:

Расширение . al]

означает» что и

Объектов,

всех

Описания

ieee . atdÿlogi 1 i G 4 .

проекте можно пенольюлать

содержащихся

и

пакете

Большинстио САПР VHDL поддерживают работу с библиотекой

ieee, 13 состав которой ВХОДЯТ СЛСДУЮШНС пакеты:

* Bto_.iogic_1164. Содержит определения оснонмых типов дан¬

ных.

* etd_.logic_arith. Содержит арифметическое

ции преобразования

ЬшныЦ

и

функции* функ¬

ергшнения. работающие с такими типами

как signed, unsigned, integer, st:d_ulogic,

Btd_logic, std_logic_unsigned и stcLlogicÿvector,

* 6td._logic._misc. Содержит определения

пов данных, а также

ESC помогательных

ти¬

подтипов, констант и функций, используе¬

0bd_logic_llSJ,

пикетом

мых

Чтобы заде iici во ватт, любой из этим пакетов, нужно включить в со¬

став проекта операторы объявления требуемых библиотек и пакетоЕ!

шд!

--

TI'JJJO

пакета .

library j.

ieee.sijS

Очень популярной библиотекой также является библиотека

5YN0PSYS, которая содержит пакет SYWOPSYS. attributes.-, all с

он и сап ними атрибутов:

library SVHOPSYSJ

use SYN0B5YS /it tributes- all;

может спадать и затем подключить к проекту

собственный пакет. Объявление пакета должно удовлетворять следую¬

щему синтаксису:

ЦУ

лфщ лфеета

oner avopiC

or.d package body

HaiLpn

■

1

I

лда

дакегл)

: i i - i IL‘ логические

■

функции AND2, 0R2, NAND2 , KOR2 ,

xoai и т. д. необходимо npeaiafpit ггельно определить как компоненты.

использовать

потом качестве и разрабатыпрежде чем их можно будет

функции р качестве

логические

насмон проекте. Определить базов ы&

од в U:_l one таким

можно,

именем

например»

в пакете С

ком лонентоа

образом:

-- юиерфейс пакета.

library i'

—

—

цпе

!■■

std.

.

■

I И -1 . 1 1 1

и

package baaic_£dllc is

о&ьяэгтеаие лж2 .

component

AND2

ganorlc HJE1AY! tine ;-:j r,:;) ;

port (:ni, LLI2; in s;<i_icgic; out 1: out Std_l sic;';

йг.й component /

объявление

component

use ieee.&tdJogi<_ll64 .-nil;

ues

logricÿaritfcallj

ua о ; ее e , st d_l og1e_u ns igned, d i.1 ;

Разработчик

Сбг-Jfe Л?ИИЯ_.ТЙК(? ГА

and package х.т-г. .ттйл'агл;

package body гШИ_РД Jfena is

library ieee;

use

- Интерфейс 1»кет«.

ияц_паквта i&

package

ОКЙ

.

)R;

|DELAY : Ь::г.Г' : 5 r.s ) г

port linlr ir,2: in £td_logLer out

end component;

end package 1» ; i с June;

■■

generic

li out stdÿlogic: г

течо вякета.

library ieee;

use iee e , 6tljLlogic_ 11 6Ж al 1:

package body bagic_fuilC ie

- 2 -входовый в (штиль find

entity A-4D2 to

generic (DELAY: time);

port '

I. L П Г : in ."ÿ:_] (

r:.c;

out 1: out std_J

end ЮЛЯ)

architecture

.

-li l_con»: of WED-1 in

34 ■ Глава л Базовая структура

ГЛАВА

bogln

Out! <= ini and i7.2 after DELAY;

end niorfol.jcanej

"ÿ

2 -МЯОДОВЕШ

ВСНТИЛЬ

4

ЛЕКСИЧЕСКИЕ ЭЛЕМЕНТЫ ЯЗЫКА VHDL

CR

•Utlty

in

F

generic DELAY; l. i:i„|;

ini,

port

inj|

end Ж.2;

architecture

№

in stcLlcoicj out

l#l_ ;onc2 of M.Ttf

out

std_lcgi

Ц

begin

Outl

:nl or ir.2 after DELAY;

end тс

_сойв2;

end package body baaic_furLc;

Обратите снимание на 70, что

интерфейсе

макпа и лсдтазделе

component указано время задержки 5 нс (DELAY; Same : =5 лб}.

Следует заметить, что явное указание времени задержки игнорируется

многими инструментальными средствами синтеза. I* конструкции раз«и;мою пакета использован встроенный тип ntd .logic, кото¬

рабе

рый объявлен и пакете sttxj;9gic_li§4. Для достижения видимости

описании типа eta._logi е из

макета в него низ каче¬

ны операторы library 1.0в.О7 иTIME ioee. std_logicm1164 all;.

СозданЙШ пакет должен Гиль отко MI им провал и помещен в поль¬

зовательскую библиотеку Такую библиотеку можно именовать как

ity_fun-T- Чтобы использовать компшеспты из пользоваталДвВЬй биб¬

лиотеки ijy_£uncs н создаваемой проекте требуется подключить эту

библиотеку : .у

тс н пакет bo:-. i.c

С ПОМОЩЬЮ операторов сле¬

......

и

разрабатываемо

■

.

■

дующего вила:

library ieee, myÿfunc;

!№(

.-j ii_l 10-1 al; ,

MI .

: лу_£ unci,biisi „func.all;

.

.

Внимание! Язык VHDL допускает перечисление имен библиотек и

Макетов после ключевых слан library и use соотастепшетю, разделяя

чх запятыми Естественно, что можно обтинть и создаваемом проекта

библиотеки и пакеты с тмощью отдельных операторов, как показано

дли примера 4-биЩюж сумматора.

4.1 Идентификаторы

......

(identifier*)

это определяемы! пользОртслем

используемые для обозначения программны* объектов ( просион копе*

то Et, интерфейсов архитектур, пакетов, сигналов, перемс

таит, ком ги тс и то в и лр,} И VHDL-проекта*. Пиша уже приводил псе,

примеры идентификаторов для входных к выходных си пталов, а также

Идентификаторы

СЛОЕ!!!,

для объявлений Интерфейсов н аркнтекгуп проектов- Мри выборе

адоитифнкатэдйп следует соблюдать ел еду пни не прешила:

Идентификатор может содержать прописные и (или) строчные

* символы

латинскою алфавита и цифры (А., ж a.„it, 0...9Й разде¬

символон подчерки1Йния,

одним

ляемые

символом II идентификаторе должен быть символ лйтйН* первым

|лфавнтаСимвол подчеркинация не может пьете» первым

скою

иди последний символом идентификатора,

идентиф ика¬

* Использовать подряд два символа ттоич ер киипнзтя в

горе запрещается.

Строчные и прописные сим молы латинскою алфавита и иденти¬

*

фикатор считаются одинаковыми, т. е, идентификаторы .-,Г:(52,

АШ2 или ап12 равнозначны. Другими словами, ндентмткагоры не чувствительны к регистру спивав,

длину:

* Идентификатор может пме о» любую

0, My_gatel,

При меры корректных идентификаторов: XI 0,

_Х10.

идентнфн катерок:

некорректных

ПpilMCpJ.I

ту, н .и. ейinput, gate- input,

3S ■ Глава 4. Лексические элементы языка VHDL

Идентификаторы, создаваемые но приведенным выше правилам,

называют базовыми идентификаторами (haze identifier). Однако эти

правила часто слишком ограничивал разработчиков, не позволял со¬

здавать имена сигналов с особыми свойствами. Например, если н

VHDL-ÿÿÿÿÿÿÿ требуется обозначить сигнал RES ВТ с активным низ¬

ким уровнем, проще всего использовать идентификатор \ RESET. Огра¬

ничения, наложенные на базовые идентификаторы, сняты в группе так

называемых расширенных идентификаторов (extended identifier). К рас¬

ширенным идентификаторам применяются нее те же правила, что и

для базовых, иос учетом следующих особенностей:

* Расширенные идентификаторы могут начинаться и заканчивать¬

ся символом обратной косой черты «\»,

* Расширенные идентификаторы должны отличаться от зарезерви¬

рованных слов, ключевых слов и любых других базовых мденгнфикаторов. Например можно использовать расширенный иденти¬

фикатор \if , который нс будет восприниматься компилятором в

качестве ключевого слова if,

* Внутри расширенного идентификатора также может содержаться

символ обратной косой черты. В такой ситуации он должен пред¬

варяться дополнительным символом обратной косой черты, г, е,

данных символов внутри расширенного идет нфика гора должно

быть два.

Расширенные идентификаторы поддерживаются только в версии

языка VHDL-93. R версии VHDI -87 они отсутствуют.

Примеры корректного оформления расширенных идентификато¬

ров; Input, .Input' , \ input #1\, \Rst\ \аэ\,

4.2,

Ключевые слова

Некоторые идентификаторы и о пользуются системой проектировакак ключевые слова (keyword) для организации особых, специфи¬

ческих конструкций языка (операторов языка). Эти ключевые слова не

могут применяться как идентификаторы для сигналов или объектом.

которые мы определяем в создаваемом проекте. Некоторые из этих

ключевых слов приводились ранее: in, out. or. and, port, map, and

и T, д. Ключевые слова часто выделяются САПР VIII)] полужирным

шрифтом или цветом. Полный список ключевых слов языка VHDL:

■1.3. Зарезервированные сши

dba

access

niter

Alia*

all

and

architecture

exit

£11«

(or

f unct ion

generate

generic

array

group

guarded

aaeert

attribute

IE

impure

begin

blocfe

in

inertial

body

incut

buf far

bus

case

component

is

not

a ignal

null

of

others

shared

ala

all

ага

ar 1

subtype

out

package

to

on

open

or

transport

units

library

proconu

pure

range

record

linkage

reglater

reject

«ait

when

disconnect

literal

loop

map

downto

mad

configuration

constant

else

nand

elaif

end

entity

new

next

nor

rem

report

return

rol

Л9

then

port

postponed

procedure

label

*

type

unaffected

until

use

variable

while

with

xnor

xor

ror

select

severity

4.3. Зарезервированные слова

Некоторые идентификаторы являются в конкретных САПР VHDL

зарезервированными. Зарезервированные идентификаторы использу¬

ются для указания информационных характеристик (типов) програм¬

мных объектов в операторах их объявлений- В частности, зарезервиро¬

ванными идентификаторами являются такие идентификаторы, как

bit, bit ..vector, atd .logic, etd logic vector и т.д. Зарезер¬

вированные идентификаторы запрещено применять в качестве базовых

идентификаторов.

Стандарт VHDL- 8 7 поддерживает следующие зарезервированные

слова: bit. bit. vector, integer, float, atring, character.

4.5. Ош/Mikj, строки и битовые строки ■ 41

40 ■ Глава 4. Лексические шменян языка VHDL

Стандарт VHDL-93 дополняет этот перечень следующими зарезер¬

вированными идентификаторами: otd _logic, 0td.,logic_vector,

std_logic_signed, std_logic_unsigned.

4.5. Символы, строки и битовые строки

4.4. Числа

мер:

По умолчанию числа, или числовые литералы, в языке VHDL пред¬

ставляются в десятичной системе счисления. Язык VHDL поддержива¬

ет работу с целочисле иными (Integer) и действительными (real)

литералами. Целочисленный литерал состоит из целого числа без деся¬

тичной точки, а действительный литерал всегда содержит десятичную

точку Экспоненциальное представление как целых, так и действитель¬

ных чисел поддерживается путем использования символов «е» или

«е». Ятя целочисленных литералов экспонента должна всегда быть

t юл Ожител ьн ым ч ислом ,

Примеры целочисленных лнтсралоп: 12 10 25653 12е+б

Примеры шкественных литералом: : , , ?.ъ б.?.б з не 2

Число 12 является комбинацией операция минус н целочислен¬

ного литерала.

Язык VHDL также поддерживает работу с числами других систем

счисления, Такие числа принято называть базированными литералами.

Синтаксис представления базированных литералов имеет вид

ба?сЗт’,-исло11

.

Ниже приведено несколько примеров представления десятичных

чисел L 6 н 29 с помощью базированных литералов для разных основа¬

ний систем счисления.

• Двоичная система: 2s.00lc* (эквивалент десятичного числа

•

ie>; 2 IT 1 1 0К1 (эквивалент десятичного числа 2f>).

Восьмеричная система: 8 #22 (десятичное 18); 8 it ЗБ (десятичное

29).

• Шестнадцатеричная система: 1 б в 12#

(десятичное 29).

(десятичное L8); J6#1D#

Для повышения наглядности при записи больших чисел допускает¬

ся вставлять символы подчеркивания между группами цифр ( напри

мер,

тетродами)

базированного

литерала,

например

2Р1001_1101_1100_0 010#1 Э(Ш5_123# ит, и.

-

Отдельные символьные литералы, используемые с коде VHDLпроекта, должны заключаться в одинарные прямые кавычки, напри¬

'8'

■а'

Строки символов заключаются и двойные кавычки, например;

’ Пример

строки . "

двойник кавичек внутри строки куано удваивать

соответствующий №-:йол. "

"Пример " ' пчо1.оянойн " стрэки."

"Для

использования

В состав строки может Сыть включен любой печатаемый символ.

Битовая строка (bit-string) представляет собой последовательность

значений, представленных в виде набора битов. Чтобы указать, что

строка является не обычным текстом, а битовой строкой, последняя

должна предваряться символом, который обозначает основание систе¬

мы счисления. 13 частности, для обозначения двоичной системы счис¬

ления нс пользуется символ в, восьмеричной символ о, а шестнадца¬

—

теричной

символ х, Например: в"И00_Ю01я, Ь'чооюи",

О " 311 ■ , О р 11 3 " , X " С 9 " , х " 4Ь " .

Вникание! Следует заметить, что при записи битовых строк в шест¬

надцатеричной системе счиоеиин каждая цифра соответствует одной

тетради. Поэтому битовая строка ЬЧООХ 01 1 ", представля¬

поскольку последняя соот¬

ющая 7 бит, не равна битовой строке

ветствует 8 битам. По этой же причине битовая строка о“113“

(9 бит ) нс равна битовой строке х " 4Ь " (8 бит).

ГЛАВА

5

ПРОГРАММНЫЕ ЭЛЕМЕНТЫ ДАННЫХ:

КОНСТАНТЫ, ПЕРЕМЕННЫЕ

И СИГНАЛЫ

Любой программный элемент данных в языке VHDL прежде чем

использовал ься в проекте, должен быть объявлен (declared) с указанием

шна (type) н значения (value). Программным элементом данных может

быть константа (constant), переменная (variable), сигнал (signal), а также

фаи-i (Шс). До енх пор мы имели дело с сигналами, которые использо¬

вали как входные или выходные порты или п качестве внутренних свя¬

зей. Сигналы можно рассматривать как программное представление

проводников (wire) в схемном решении. Сигналы могут иметь текущее

значение и определенный набор возможных значений, являясь функ¬

циями операторов устаноеки значения еигнала (signal assignment ). Пере¬

менные и константы используются а качестве вспомогательных про¬

граммных элементов, используемых для моделирования поведения

схем, с операторах process, подпрограммах-процедурах и подпро¬

граммах-функциях, подобно тому как они используются в других язы¬

ках программирования, Давайте кратко обсудим назначение и синтак¬

сис каждого класса этих программных элементов данных.

5.1,

Константы

5.2. Переменные т 43

В операторе объя плени» константы может отсутствовать та часть

объявления, в которой укатывается начальное значение константы,

т. е. [ : началыюе_знрчсн«е } , Константы могут быть объявлены в

=

разделе объявлений архитектуры проекта, В этом случае константа яв¬

ляется видим ой и пределах всей архитектуры того проекта, и котором

она объявлена. Константы, объявленные в разделе объявлений оператора process, видимы только в пределах этого оператора process н

могут использоваться только в этом конкретном операторе. Константы

могут также объявляться в пакетах. Если константы имеют одинако¬

вый тип и одинаковое начальное значение, их идентификаторы можно

перечислять и операторе объявления в виде списка, отделяя одно имя

от другого запятой.

Ниже приведены примеры операторов объявлений констант.

constant RISE_FAIib_THE: time := 2 ns;

4 ns;

constant DELAY! ; timeЛИГ, FALi._TlMt: rime-:

constant

constant D.\TA_BUS : intept-r: 1.6 j

=

i ns;

5.2. Переменные

—

Переменная это программный элемент данных, который в про¬

цессе моделирования работы проекта может принимать любое, по

всегда единственное значение и определенный момент. В другой мо¬

мент переменная может иметь другое значение. Значение переменной

может быть модифицировано оператором присваивания значения пе¬

ременной. При этом считается, что значение переменной модифици¬

руется оператором присваивания значения немедленно (т. е. без временой задержки), как только этот оператор выполнен, Переменные

должны объявляться только и подразделе объявлений оператора

имеет следующий синтаксис:

Константа — это программный элемент данных, значение которо¬

го остается всегда настоянным в процессе моделирования н работы

проекта. Объявление программной величины константы имеет следу¬

process. Объявление переменной

constant кия_кси :тянты-.

variable CHTR_BIT: bit : 3;

variable VAR1 : boolean J FALSE]

to 2'ЭТ :

variable ЛУИ: integer range

variable ST2_BIT; bit_ve«or i. ■' downto Q);

ющий синтаксис:

тип (

:= начальнсе

эн-зчение]

;

начальна нмчеяле] ;

Ниже приведены примеры операторов объявлений переменных.

variable )ия_лереяенноЙ; тип [

=ÿ

44 ■ {'.шла 5. Программные з.кмснты teM: константы, переменные и пинты

U рассмотренном примере переменила -;зк является целым чис¬

лом, которое имеет диапазон от 0 до 256 н начальное значение 16 и на¬

чале процесса моделирования, В четвертом примере определен бито¬

вый вектор STS_BrT, содержащий S элементов, к каждому из которых

можно обращаться но имени переменной с указанием индекса бита н

векторе: зт$_вгг (7} STS_BIT {б), ... STS_BIT (01.

Как говорилось выше, значение переменной может модифициро¬

ваться с помощью оператора присвоения значения переменной. Этот

оператор имеет следующий синтаксис:

истечении которой следует присвоить сигналу результат вычисления

соответствующего выражения, например:

;

пн

г. А хог

В) after