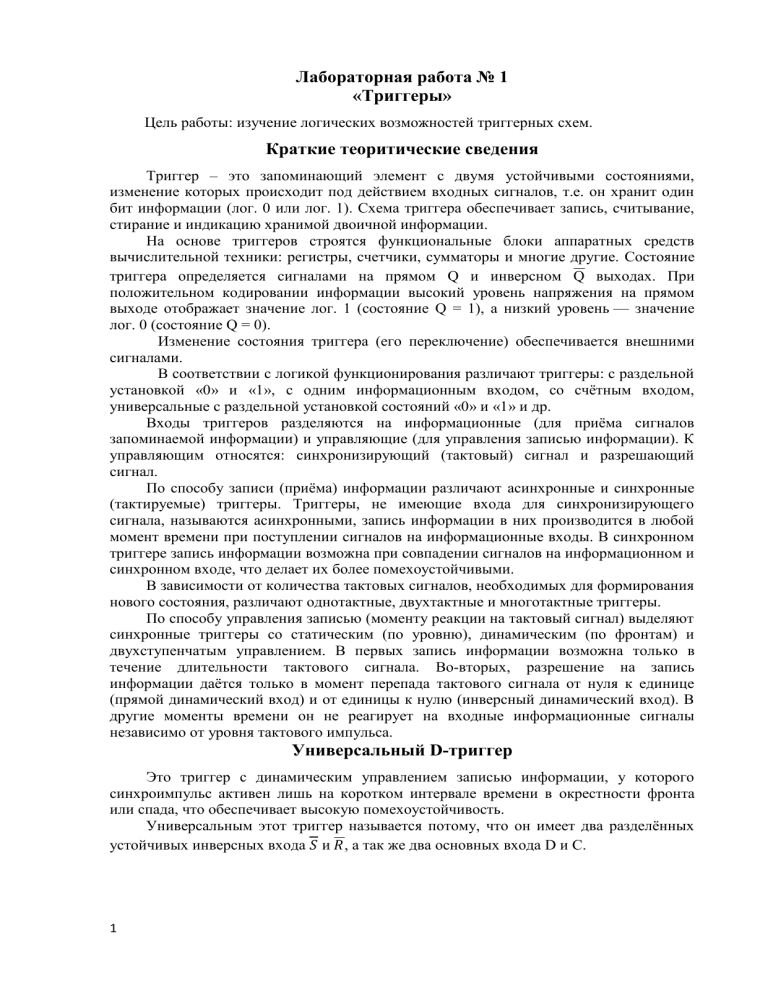

Лабораторная работа № 1 «Триггеры» Цель работы: изучение логических возможностей триггерных схем. Краткие теоритические сведения Триггер – это запоминающий элемент с двумя устойчивыми состояниями, изменение которых происходит под действием входных сигналов, т.е. он хранит один бит информации (лог. 0 или лог. 1). Схема триггера обеспечивает запись, считывание, стирание и индикацию хранимой двоичной информации. На основе триггеров строятся функциональные блоки аппаратных средств вычислительной техники: регистры, счетчики, сумматоры и многие другие. Состояние триггера определяется сигналами на прямом Q и инверсном Q выходах. При положительном кодировании информации высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние Q = 1), а низкий уровень — значение лог. 0 (состояние Q = 0). Изменение состояния триггера (его переключение) обеспечивается внешними сигналами. В соответствии с логикой функционирования различают триггеры: с раздельной установкой «0» и «1», с одним информационным входом, со счётным входом, универсальные с раздельной установкой состояний «0» и «1» и др. Входы триггеров разделяются на информационные (для приёма сигналов запоминаемой информации) и управляющие (для управления записью информации). К управляющим относятся: синхронизирующий (тактовый) сигнал и разрешающий сигнал. По способу записи (приёма) информации различают асинхронные и синхронные (тактируемые) триггеры. Триггеры, не имеющие входа для синхронизирующего сигнала, называются асинхронными, запись информации в них производится в любой момент времени при поступлении сигналов на информационные входы. В синхронном триггере запись информации возможна при совпадении сигналов на информационном и синхронном входе, что делает их более помехоустойчивыми. В зависимости от количества тактовых сигналов, необходимых для формирования нового состояния, различают однотактные, двухтактные и многотактные триггеры. По способу управления записью (моменту реакции на тактовый сигнал) выделяют синхронные триггеры со статическим (по уровню), динамическим (по фронтам) и двухступенчатым управлением. В первых запись информации возможна только в течение длительности тактового сигнала. Во-вторых, разрешение на запись информации даётся только в момент перепада тактового сигнала от нуля к единице (прямой динамический вход) и от единицы к нулю (инверсный динамический вход). В другие моменты времени он не реагирует на входные информационные сигналы независимо от уровня тактового импульса. Универсальный D-триггер Это триггер с динамическим управлением записью информации, у которого синхроимпульс активен лишь на коротком интервале времени в окрестности фронта или спада, что обеспечивает высокую помехоустойчивость. Универсальным этот триггер называется потому, что он имеет два разделённых устойчивых инверсных входа 𝑆 и 𝑅, а так же два основных входа D и C. 1 Рис. 1.1 Условное обозначение триггера D Установочные входы 𝑆 и 𝑅 являются приоритетными, т.е. если хотя бы один из этих входов является активным (𝑆 = 0 или R = 0), триггер на сигналы, подаваемые на входы D и C, не реагирует. Причём при подаче сигналов 𝑆 = 0; 𝑅 = 1 триггер переходит в состояние «1», при другом сочетании сигналов 𝑆 = 1; 𝑅 = 0 триггер переходит в состояние «0». Комбинация входов 𝑆 = 0 и 𝑅 = 0 является запрещенной, т.к. триггер в этом случае работает неправильно (формирует на входах 𝑄 = 1 и 𝑄=1, что противоречит правилам математической логики). Если установочные входы триггера пассивны (т.е. 𝑆 = 1; 𝑅 = 1), то он переключается под воздействием сигналов, подаваемых на входы D и C. При подаче на вход C переднего фронта сигнала (т.е. перепада «0» → «1») триггер переходит в состояние, соответствующее состоянию входа D. На перепад «1» → «0» (на входе C) данный триггер не реагирует, т.е. сохраняет своё состояние. Логика работы триггера D иллюстрируется временной диаграммой, представленной на рис. 1.2. Эта диаграмма разделена на 4 части. На первом этапе на установочные входы 𝑆 и 𝑅 подается запрещенная комбинация сигналов 𝑆 = 0 и 𝑅 = 0, при которой триггер работает неправильно (𝑄 = 𝑄 = 1 и 𝑄 = 1). На втором этапе на входы 𝑆 и 𝑅 подаётся «команда» установки триггера в состояние «0», т.е. подается комбинация сигналов 𝑆 = 1; 𝑅 = 0 и триггер из «неопределенного» состояния переходит в состояние «0» (𝑄 = 0). Рис. 1.2 Временная диаграмма работы триггера D 2 На третьем этапе на входы 𝑆 и 𝑅 подаётся «команда» установки триггера в состояние «1», т.е. 𝑆 = 0; 𝑅 = 1 и триггер «выполняет» эту команду (т.е. переходит в состояние «1», 𝑄 = 1). На всех первых трёх этапах триггер на сигналы, подаваемые на входы D и C, не реагирует. Только на четвертом этапе, когда 𝑆 = 1; 𝑅 = 1, триггер «копирует» состояние входа D и в момент прихода на вход C перепадов «0» → «1», т.е. в моменты времени 𝑡1 и 𝑡2 , переключается в соответствующее состояние. Пример выполнения Для построения схемы подключения генератора сигналов к входам D-триггера используются следующие элементы: D-триггер (T1), J-K триггеры (TT1, TT2, TT3), ключ (K1), генератор одиночных импульсов (ГОИ), генератор импульсов (ГИ), логический анализатор (ЛА). Для исследования логики работы триггера D генератор сигналов собирается на триггерах J-K (или используется счётчик на J-K триггерах). Схема подключения генератора сигналов к входам D-триггера изображена на рис. 1.3. На все незадействованные в схеме генератора сигналов входы триггеров J-K подаются сигналы логической «1», что обеспечивает работу этих триггеров в счетном режиме (см. таблицу). Временная диаграмма работы D-триггера изображена на рис. 1.4. 3 4 Рис. 1.3 Схема подключения генератора сигналов к входам D-триггера Рис. 1.4 Временная диаграмма работы D-триггера Универсальный триггер J-K Этот триггер, так же как и D-триггер, с динамическим управлением записью информации. Он называется универсальным по той же причине, что и D-триггер (наличие входов 𝑆 и 𝑅). Эти входы так же являются приоритетными. Логика переключения J-K триггера при подаче сигналов на установочные входы совпадает с логикой переключения триггера D. Только при подаче сигналов 𝑆 = 1; 𝑅 = 1 (на установочные входы) триггер J-K реагирует на сигналы, подаваемые на входы 𝐽, 𝐾, 𝐶 и переключается в соответствии со следующими правилами: Триггер анализирует состояние входов 𝐽 и 𝐾 в момент подачи на вход 𝐶 переднего фронта сигнала (т.е. перепада «0» → «1»), а переключается (устанавливает значения на выходах 𝑄 и 𝑄) в момент поступления на вход 𝐶 заднего фронта сигнала (перепад «1» → «0»), т.е. в момент окончания сигнала на входе 𝐶. Такие триггеры за счет наличия этого свойства называют триггерами с внутренней задержкой (на время, равное длительности сигнала, подаваемого на вход 𝐶) и обозначаются на функциональных схемах двумя буквами TT (рис. 1.5). Рис. 1.5 Условное обозначение J-K триггера Логика работы триггера J-K при 𝑆 = 1; 𝑅 = 1 (т.е. по сигналам, подаваемым на входы 𝐽, 𝐾 и 𝐶) представлена в табл. 1.1 и показана на временной диаграмме (рис. 1.6). 5 Таблица 1.1 № п/п 1 После окончания В момент подачи на подачи вход С переднего сигнала фронта сигнала (tп.ф.) на вход С (tз.ф.) J K Q (tп.ф.) Q (tз.ф.) 0 0 0 0 2 0 3 0 0 1 1 0 1 0 4 0 1 1 0 5 1 0 0 1 6 1 0 1 1 7 1 1 0 1 8 1 1 1 0 Комментарий Триггер не реагирует на сигнал, подаваемый на С Триггер переходит в состояние «0» (или сохраняет состояние «0») Триггер переходит в состояние «1» (или сохраняет состояние «1») Триггер переходит в противоположное состояние (счётный режим) Номер строки в таблице, соответствующий данному периоду временной диаграммы. Рис. 1.6 Временная диаграмма работы триггера J-K Пример выполнения Для построения схемы подключения генератора сигналов к входам J-K триггера используются следующие элементы: D-триггеры (T1, T2, T3, T4), J-K триггер (TT1), ключ (K1), генератор одиночных импульсов (ГОИ), генератор импульсов (ГИ), логический анализатор (ЛА). Для исследования логики работы J-K триггера генератор сигнала собирается на Dтриггерах (или используется счетчик на D-триггерах). Схема подключения генератора сигналов к входам J-K триггера изображена на рис. 1.7. Временная диаграмма работы J-K триггера изображена на рис. 1.8. 6 7 Рис. 1.7 Схема подключения генератора сигналов к входам J-K триггера 8 Рис. 1.8 Временная диаграмма работы J-K триггера Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. 9. Наименование работы. Цель работы. Краткие теоретические сведения Вариант задания. Схема подключения генераторов сигналов к входам триггеров. Таблицы истинности и временные диаграммы работы триггеров D и J-K. Временная диаграмма работы. Анализ полученных результатов и выводы. Подпись исполнителя. Контрольные вопросы 1. Что такое триггер? 2. Какие типы триггеров Вы знаете? 3. Каков принцип работы триггеров D и J-K. 4. Разъясните понятие асинхронной работы триггера. 5. Как различают триггеры с логикой функционирования? 6. Как различают триггеры по количеству тактовых сигналов? 7. Как различают триггеры по способу управления записью? 8. Объясните счетный режим работы триггера. 9. Разъясните понятие универсального триггера. 10. Назовите динамические параметры триггеров. Литература 1. Бабич Н.П., Жуков И.А. «Компьютерная схемотехника», К., «МК-ПРЕСС», 2012 9 Лабораторная работа № 2 «Регистры» Цель работы: изучение структуры и исследование работы регистров. Краткие теоретические сведения Регистр – это объединение триггеров, позволяющее единообразно оперировать с множеством, как правило, связанных между собой, переменных (разрядов), составляющих информационное слово. Регистры состоят из разрядных схем, которые содержат триггеры и другие логические элементы. С помощью регистров осуществляют прием, хранение, выдачу данных, перемещение (сдвиг) информационного слова в сторону младшего или старшего разряда, поразрядные логические операции. Регистры входят практически в любое устройство цифровой вычислительной техники. Регистры классифицируют: а) по количеству линий передачи переменных: одна линия связи для передачи информации между разрядными схемами – однофазные, две линии связи, то есть передаются прямой и инверсный сигналы, - парафазные; б) по системе синхронизации: однотактная – обработка данных осуществляется с помощью одной последовательности сигналов или двухтактная (многотактная) – используются две (несколько) последовательности; в) по способу приему и выдачи данных: параллельные – прием или выдача осуществляется одновременно со всех разрядов, последовательные или сдвигающие – данные принимаются и выдаются разряд за разрядом и последовательно-параллельные. Последние имеют входы-выходы последовательного и параллельного типа. В параллельных регистрах разрядные схемы не обмениваются информацией между собой. Общими для разрядных схем таких регистров являются цепи синхронизации, установки в состояние 0 или 1, записи входных данных, разрешения выхода, т.е. цепи управления. На рис. 2.1 приведена схема параллельного регистра на D-триггерах, имеющего общие вход установки нуля и записи данных по фронту синхронизирующего сигнала. В некоторых случаях выходные каскады регистра дополняют схемами с тремя устойчивыми состояниями, позволяющими подключать регистр непосредственно к шинам. Кроме того, регистр может содержать элементы, разрешающие прием или выдачу данных. Рис. 2.1 Схема параллельного регистра 10 Параллельный регистр может быть построен и на триггерах других типов, например, RS-триггерах. Для того, чтобы уменьшить время приема данных, входную информацию подают одновременно по двум линиям на входы S и R, то есть парафазным кодом. В этом случае предварительную установку регистра в состояние ноль (единицу) проводить не требуется. Большинство регистров строят на основе D-триггеров с записью информации фронтом или срезом импульса. Условное графическое изображение параллельного регистра показано на рис. 2.2. Параллельные регистры являются основой блоков регистровой памяти или регистровых файлов. Они позволяют хранить, например, четыре четырехразрядных слова с возможностью независимой и одновременной записи одного слова и чтения другого. Рис. 2.2 Обозначение Такой блок содержит четыре одинаковых параллельных параллельного регистра регистра, информационные входы которых объединены. Сдвигающие или последовательные регистры представляют собой цепочку разрядных схем, связанных цепями переноса. В них каждый тактовый импульс перезаписывает (сдвигает) содержимое триггера каждой разрядной схемы в триггер соседней разрядной схемы без изменения порядка следования единиц и нулей (хранимой информации). Входы и выходы этих регистров последовательные. При сдвиге информации вправо после каждого тактового импульса бит из более старшего разряда сдвигается в младший, а при сдвиге влево – наоборот. На рис. 2.3 показана схема последовательного регистра, обеспечивающего смещение информации вправо. На рис. 2.4 приведены временные диаграммы работы этого сдвигающего регистра. Если в регистре не содержалось единиц, например, он был обнулен сигналом установки нуля (R), а на входе поддерживалась единица только во времени формирования одного импульса синхронизации (СИ), то каждым очередным импульсом синхронизации она будет перемещаться в триггер соседней разрядной схемы. Таким образом, единица, поступившая на D вход регистра, окажется на его выходе (последнем триггере DDn) после поступления n импульсов синхронизации. Рис. 2.3 Последовательный регистр, смещающий данные вправо 11 Рис. 2.4 Временная диаграмма работы последовательного сдвигающего регистра (сдвиг вправо) На рис. 2.5 показана схема последовательного регистра, обеспечивающего сдвиг информации влево. В этой схеме выход триггера текущей разрядной схемы соединен с входом триггера не следующей, как это было в ранее рассмотренной схеме, а предыдущей разрядной схемы. В реверсивном сдвигающем регистре входы триггера текущей разрядной ячейки соединены с выходами триггеров как предыдущей, так и последующей разрядной ячейки, но с помощью элементов 2И-2И-ИЛИ и управляющих сигналов «Сдвиг данных вправо» или «Сдвиг данных влево» разрешается работа только одних из этих связей. Рис. 2.5 Последовательный сдвигающий регистр (сдвиг влево) Условные обозначения сдвигающих регистров вправо, влево и реверсивных показаны соответственно на рис. 2.6a, рис. 2.6б, рис. 2.6в. Схема реверсивного сдвигающего регистра на D-триггерах приведена на рис. 2.7. 12 Рис. 2.6 Условные обозначения сдвигающих регистров Кольцевые сдвигающие регистры могут быть использованы при построении счетчиков с постоянно взвешенными кодами, для которых число единиц и нулей в каждом устойчивом состоянии постоянно. Простейшим счетчиком этого класса является счетчик Джонсона, работающий в коде Либау-Крейга. Он реализуется на сдвигающем регистре с одной инверсной связью между пятым и первым разрядом, схема приведена на рис. 2.8. Рис. 2.7 Реверсивный сдвигающий регистр на D-триггерах 13 Рис. 2.8 Счетчик Джонсона Применяются различные типы регистров. Несколько типов являются многофункциональными (универсальными). Многофункциональность обеспечивается объединением в одной и той же микросхеме узлов, позволяющих реализовывать различные операции. Выбор операции, выполняемой в данное время, производится активизацией необходимых узлов с помощью управляющих сигналов. Регистры широко используются для хранения данных, например, на их основе строится статическая оперативная память, накапливающий сумматор, преобразователи параллельных кодов в последовательные и наоборот, и другие устройства. Пример выполнения На рис. 2.9 приведена схема регистра на J-K триггерах, осуществляющего сдвиг влево. Временная диаграмма его режима работы изображена на рис. 2.10. 14 15 Рис. 2.9 Схема 4-х разрядного регистра на JK-триггерах, реализующего сдвиг влево В данной схеме используются логический анализатор (ЛА 150 HZ), функциональный генератор (ГФ частота «10 Hz») с переключателем (П «DIPSW1»), генератор одиночных импульсов (ГОИ «Ster_Voltage») с ключом (К «DIPSW1»), световые индикаторы (CLK, 1-4) и JK-триггеры (D1-D4 «JK_FF»). Устанавливаем схему в исходное состояние. D1, D2, D3 – в состояние нуля, D4 – в состояние единицы (это можно наблюдать по световому индикатору 4). После этого подаем сигналы с генератора импульсов. Идет сдвиг единичного сигнала влево, с D4 на D3, затем на D2 и на D1. Этот сдвиг виден на временной диаграмме. Рис.2.10 Временная диаграмма режима работы регистра Контрольные вопросы 1. Определите назначение регистра. 2. Объясните работу сдвигающего регистра. 3. Определите время сдвига в регистре. 4. Какова возможность преобразования кода в схеме? 5. Какие типы регистров существуют? 6. Какие поразрядные логические операции выполняются на регистрах. 7. Определите неисправности в схеме. 16 Варианты заданий Разработать схемы изученных регистров и счетчика Джонсона, используя Dтриггеры, j-k-триггеры (табл. 2.1). Таблица 2.1 Вариант Сдвиг влево D Сдвиг вправо Реверсивный Счетчик сдвиг n=3 Джонсона j-k D j-k D 1 + + + + 2 + + + + 3 + + + + 4 + + + + j-k 5 + + + 6 + + + 7 + + + + 8 + + + + + + 9 + + + + 10 + + + + 11 + + + + 12 + + + + + + 13 + + 14 + + + 15 + + + Содержание отчета 10. Наименование работы. 11. Цель работы. 12. Краткие теоретические сведения. 13. Вариант задания. 14. Пример выполнения схем регистров и счетчика Джонсона. 15. Временная диаграмма работы. 16. Анализ полученных результатов и выводы. 17. Подпись исполнителя. Литература 17 D + + 1. Шестеркин А.Н. – Система моделирования и исследования радиоэлектронных устройств Multisim10 - ДМК Пресс, 2012 г. Лабораторная работа № 3 «Счётчики» Цель работы: изучение схемы двоичных счетчиков; построение и исследование счетчиков и пересчетных схем с заданным числом состояний. Краткие теоретические сведения Счетчик – цифровое устройство, определяющее, сколько раз на его входе появится определенный логический уровень, т.е. он подсчитывает содержащиеся во входных сигналах переходы с уровня логического 0 к уровню логической 1. При входном сигнале, имеющем форму последовательности импульсов, счётчик ведёт счёт поступающих на вход импульсов. Числа в счетчике представляются некоторыми комбинациями состояний триггеров. При поступлении на вход очередного уровня логической 1 в счетчике устанавливается новая комбинация состояний триггеров, соответствующая числу, на единицу большому предыдущего числа. Таким образом, счетчик представляет собой логическое устройство последовательностного типа, в котором новое состояние определяется предыдущим состоянием и значением логической переменной на входе. Счетчики подразделяются на простые и реверсивные. Простые счетчики работают в режиме сложения – суммирующие счетчики, либо в режиме вычитания – вычитающие счетчики. Реверсивные счетчики реализуют оба режима счета. Быстродействие счетчика зависит от реализации межразрядных соединений. Существует три основных способа передачи сигналов переносов: последовательный, параллельный и групповой. Групповой перенос представляет комбинацию параллельного переноса в группе и последовательного между группами разрядов счетчика или наоборот. В счетчике с последовательным переносом на вход следующего старшего разряда счетчика подается сигнал непосредственно с выхода предшествующего младшего разряда, поэтому триггеры счетчика переключаются последовательно: выходной сигнал на последнем старшем разряде появляется только после срабатывания всех младших разрядов. На рис. 3.1 и рис. 3.2 приведены схемы суммирующего, а на рис. 3.3 и рис. 3.4 вычитающего счетчиков с последовательным переносом, реализованных на триггерах D- и j-k-типов соответственно. Рис. 3.1 Схема суммирующего счетчика с последовательным переносом реализованного на D-триггерах 18 Рис. 3.2 Схема суммирующего счетчика с последовательным переносом реализованного на j-k-триггерах Рис. 3.3 Схема вычитающего счетчика с последовательным переносом реализованного на D-триггерах Рис. 3.4 Схема вычитающего счетчика с последовательным переносом реализованного на j-k-триггерах В счетчиках с параллельным переносом на информационный вход каждого разряда поступают сигналы с выходов всех предшествующих младших разрядов, а входной счетный сигнал одновременно поступает на синхровходы «С» триггеров во всех разрядах. Счетчики с параллельным переносом обычно строятся на базе j-k и Dтриггеров, синхронизируемых входом. На рис. 3.5 представлена схема суммирующего счетчика с параллельным переносом на триггерах типа j-k. 19 Рис. 3.5 Схема суммирующего счетчика с параллельным переносом реализованного на j-k-триггерах Суммирующие счетчики В суммирующем счетчике поступлении на вход очередного уровня логической 1 вызывает увеличение на одну единицу хранимого в счетчике числа. Таким образом, в счетчике устанавливается число, которое получается путем суммирования предыдущего значения с единицей. Это суммирование проводится по обычным правилам выполнения операций сложения в двоичной системе счисления. Например, В процессе такого суммирования имеют место следующие особенности: если цифра некоторого разряда остается неизменной либо изменяется с 0 на 1, то при этом цифры более старших разрядов не изменяются; если цифра некоторого разряда остается изменяется с 0 на 1, то происходит инвертирование цифры следующего за ним более старшего разряда. Этот принцип использован при построении схемы счетчика, представленной на рис. 3.6. Рис. 3.6 Схема суммирующего счётчика В построении схемы имеются следующие особенности: входы J и K в каждом триггере объединены и на эти входы подан уровень логической 1; таким образом, в каждом триггере синхронизирующий вход C является счетным входом триггера; сигнал с прямого выхода триггера каждого разряда поступает на счетный вход «С» триггера следующего более старшего разряда, а на счетный вход триггера первого разряда Тг1 подаются входные просчитываемые импульсы. 20 Если на счетном входе «С» триггера действует импульс, то его положительным фронтом переключается ведущая часть триггера, на отрицательном фронте – ведомая его часть. Итак, при каждом изменении сигнала на счетном входе с уровня логической 1 на уровень логического 0 изменяется на противоположное состояние выхода триггера. Таким образом, на отрицательном фронте сигнала на выходе триггера происходит переключение следующего за ним триггера более старшего разряда. На рис. 3.7 показана временная диаграмма работы суммирующего счётчика. Рис. 3.7 Временная диаграмма суммирующего счётчика Вычитающие счетчики В вычитающем счетчике поступление на вход очередной логической 1 вызывает уменьшение хранившегося в счетчике числа на единицу. Покажем примеры такого вычитания единицы: Из первого примера видно, что если в младшем разряде числа содержится 1, то получающееся в результате вычитания 1 число отличается от исходного лишь в младшем разряде. Если в младшем разряде числа содержится 0, то процесс вычитания сопровождается возникновением переносов. В отличие от операции суммирования, в которой перенос прибавляется в разряд, в который он поступает, в операции вычитания перенос имеет смысл заёма из следующего, более старшего разряда и вычитается из этого разряда. Последовательная передача таких заёмов из разряда в разряд продолжается до тех пор, пока в очередном разряде, в который передается заем, не обнаруживается 1. Так, во втором из приведенных выше примеров такая 1 обнаруживается в четвертом разряде. В результате заёма этой 1 в четвертом разряде образуется 0, а занятая из этого разряда 1 передается в третий разряд, где она имеет значение уже 2. Из этих двух единиц в третьем разряде остается одна, а другая передается во второй разряд, где она также приобретает значение 2 и т. д. Таким образом, в результате вычитания часть числа левее первого из разрядов, содержащих 1, остается неименной, цифры остальных разрядов инвертируются. На рис. 3.8 показана схема вычитающего счетчика с последовательной передачей переносов. 21 Рис. 3.8 Схема вычитающего счетчика Для повышения скорости работы счетчика могут быть использованы последовательно-параллельные цепи передачи переносов. Вычитающий счетчик, как и суммирующий, имеет период циклической работы, равный 2n импульсов. Реверсивный счетчик Реверсивный счетчик – счетчик, допускающий в процессе работы переключение из режима суммирования в режим вычитания, и наоборот. На рис. 3.9 приведена схема такого счетчика. В ней предусмотрены две цепи передачи переносов, одна из которых соответствует схеме суммирующего счетчика, другая – схеме вычитающего счетчика. Управляющие сигналы I1 и I2 включают в работу одну или другую цепь. При I1=1 и I2=0 оказывается закрытым элемент И2 и, следовательно, отключена цепь передачи переносов режима вычитания. Счетчик работает в режиме суммирования. При I1=0 и I2=1 закрыт элемент И1 и отключена, таким образом, цепь передачи переносов режима суммирования, счетчик работает в режиме вычитания. Рис. 3.9 Реверсивный счетчик Пример выполнения Суммирующий последовательный счетчик на D-триггерах изображён на рис. 3.10. 22 23 Рис. 3.10 Суммирующий последовательный счётчик Перечень элементов: схема содержит четыре триггера (D1, D2, D3, D4), генератор сигналов (ГС), генератор одиночных импульсов (ГОИ), логический анализатор (ЛА), ключ (П), кнопку (К). Счётчик устанавливается в исходное ( «0» ) состояние. На вход поступает уровень логической 1 (импульс), который вызывает увеличение на одну единицу хранимого в счетчике числа. Если на счётном входе «С» триггера действует импульс, то его положительным фронтом переключается ведущая часть триггера, на отрицательном фронте – ведомая его часть. Итак, при каждом изменении сигнала на счётном входе с уровня логической 1 на уровень логического 0 изменяется на противоположное состояние выхода триггера. С каждым входным импульсом число счётчика увеличивается на единицу. Такое нарастание числа происходит до тех пор, пока после пятнадцатого (в общем случае (2n1)) входного импульса (n – число разрядов в счётчике) не установится в счётчике двоичное число 1111. Далее с приходом шестнадцатого импульса в счётчике устанавливается исходное состояние 0000, после чего счёт ведётся сначала. Временная диаграмма суммирующего последовательного счётчика на «D» триггерах изображена на рис. 3.11. Рис. 3.11 Временная диаграмма работы суммирующего последовательного счётчика Контрольные вопросы 1. Определить понятие счетчика. 2. Принцип работы суммирующего счетчика. 3. Принцип работы вычитающего счетчика. 4. Сравнить быстродействие счётчиков. Варианты заданий Разработать схемы суммирующего, вычитающего и реверсивного счетчиков, используя D-триггеры, j-k-триггеры (табл. 3.1). Таблица 3.1 Счетчики Вариант Суммирующий Вычитающий Реверсивный n=4 n=4 n=4 1 Последовательный на j-k Параллельный на D На j-k 2 Параллельный на j-k Последовательный D На j-k 24 Продолжение табл. 3.1 3 Последовательный на D Параллельный на j-k На j-k 4 Параллельный на D Последовательный на j-k На j-k 5 Параллельный на j-k Последовательный D На j-k 6 Последовательный на j-k Параллельный на D На j-k 7 Параллельный на D Последовательный на j-k На j-k 8 Последовательный на D Параллельный на j-k На j-k 9 Последовательный на j-k Параллельный на D На j-k 10 Параллельный на j-k Последовательный D На j-k 11 Последовательный на D Параллельный на j-k На j-k 12 Параллельный на D Последовательный на j-k На j-k 13 Последовательный на j-k Параллельный на D На j-k 14 Параллельный на D Последовательный на j-k На j-k 15 Последовательный на D Параллельный на j-k На j-k Содержание отчета 18. Наименование работы. 19. Цель работы. 20. Краткие теоретические сведения. 21. Вариант задания. 22. Пример выполнения схем счетчиков. 23. Временная диаграмма работы. 24. Анализ полученных результатов и выводы. 25. Подпись исполнителя. Литература 1. Калабеков Б.А., Мамзелев И.А. «Цифровые устройства и микропроцессорные системы», М., «Горячая линия», 2007. 25 Лабораторная работа № 4 «Сумматоры» Цель работы: изучить схемы сумматоров и принципы их работы. Краткие теоретические сведения Сумматором называется функциональный блок аппаратных средств вычислительной техники, предназначенный для сложения двух n-разрядных слов (чисел). Операция вычитания в сумматоре выполняется сложением слов в обратном или дополнительном коде. Операции умножения и деления выполняются многократным сложением и сдвигом. Сумматор является частью арифметико-логического устройства, функция сумматора обозначается буквами SM или ∑. Сумматор, в общем случае, состоит из функциональных узлов – одноразрядных сумматоров, выполняющих все действия по сложению значений одноименных разрядов двух чисел (операндов). Сумматоры классифицируются по следующим признакам: способу сложения (параллельные, последовательные и параллельно-последовательные); числу входов(полусумматоры, одноразрядные и многоразрядные сумматоры);организации хранения результата сложения (комбинационные, накапливающие, комбинированные); организации переноса между разрядами — с последовательным, сквозным, параллельным или комбинированным переносом; системе счисления (позиционные , т.е. двоичные, двоично-десятичные, троичные) и непозиционные, например, в системе остаточных классов); разрядности (длине) операндов (от 4 до 64 и более); способу представления отрицательных чисел (в обратном или дополнительном кодах, а также в их модификациях); времени сложения (синхронные, асинхронные). В параллельных «n»-разрядных сумматорах значения всех разрядов операндов поступают одновременно на соответствующие входы одноразрядных суммирующих узлов. В последовательных сумматорах значения разрядов операндов и перенос, который запомнился в предыдущем такте, поступают последовательно в направлении от младших разрядов к старшим на входы одного одноразрядного сумматора. В параллельно-последовательных сумматорах числа разбиваются на части, например, байты, разряды байтов поступают на входы восьмиразрядного сумматора параллельно (одновременно), а сами байты — последовательно, в направлении от младших к старшим байтам с учетом запомненного переноса. В комбинационных сумматорах результат операции сложения запоминается в регистре результата. В накапливающих сумматорах процесс сложения объединяется с хранением результата. Организация переноса практически определяет время выполнения операции сложения. Последовательные переносы реализуются меньшим числом схемотехнических средств, однако уменьшают их быстродействие. Параллельные переносы – наоборот. Разрядность сумматоров находится в широких пределах: 4 до 64 и более. Сумматоры с постоянным интервалом времени для сложения называются синхронными. Сумматоры, в которых интервал времени для сложения определяется моментом фактического окончания операции, называются асинхронными. Сумматоры характеризуются следующими параметрами: быстродействием — временем выполнения операции сложения, которое отсчитывается от начала подачи 26 операндов до получения результата, часто быстродействие может характеризоваться количеством сложений в единицу времени, аппаратными затратами, потребляемой мощностью. Одноразрядным сумматором называется логическая схема, которая выполняет сложение значений i-х разрядов 𝑎𝑖 , и 𝑏𝑖 , двоичных чисел с учетом переноса 𝑃𝑖−1 из младшего соседнего разряда и вырабатывает на выходах функции результат 𝑆𝑖 и перенос Р𝑖 в старший соседний разряд. На основе одноразрядных схем сложения на три входа и два выхода строятся многоразрядные сумматоры любого типа. Алгоритм работы одноразрядного сумматора отображается таблицей истинности (табл. 4.1). Таблица 4.1 Pi ai bi Pi−1 Si 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 На основе таблицы 4.1 записывается система логических функций для результата 𝑆𝑖 и переноса 𝑃𝑖 . 𝑆𝑖 = 𝑎̅𝑖 𝑏̅𝑖 𝑝𝑖−1 ⋁ 𝑎̅𝑖 𝑏𝑖 𝑝̅𝑖−1 ⋁ 𝑎𝑖 𝑏̅𝑖 𝑝̅𝑖−1 ⋁ 𝑎𝑖 𝑏𝑖 𝑝𝑖−1 𝑃𝑖 = 𝑎̅𝑖 𝑏𝑖 𝑝𝑖−1 ⋁ 𝑎𝑖 𝑏̅𝑖 𝑝𝑖−1 ⋁ 𝑎𝑖 𝑏𝑖 𝑝̅𝑖−1 ⋁ 𝑎𝑖 𝑏𝑖 𝑝𝑖−1 ; (1) ; (2) После минимизации 𝑃𝑖 будет (функция 𝑆𝑖 не минимизируется) 𝑃𝑖 = 𝑎𝑖 𝑏𝑖 ⋁𝑎𝑖 𝑝𝑖−1 ⋁ 𝑏𝑖 𝑝𝑖−1 = 𝑎𝑖 𝑏𝑖 ⋁(𝑎𝑖 ⋁𝑏𝑖 )𝑝𝑖−1 ; (3) При проектировании комбинационных одноразрядных сумматоров учитывают следующие факторы: регулярность (одинаковость) структуры и минимальная стоимость, минимальное время получения переноса. Необходимость выработки как ̅𝑖 значений переноса – парафазная организация переносов. прямых 𝑃𝑖 , так и инверсных 𝑃 При реализации на элементах «И-НЕ» уравнения (1) и (2) преобразуются на основе теоремы де Моргана к следующему виду: ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅ 𝑆𝑖 = (𝑎 ̅𝑖 𝑏̅𝑖 𝑝𝑖−1 ) (𝑎 ̅𝑖 𝑏𝑖 𝑝̅𝑖−1 ) ̅̅̅̅̅̅̅̅̅̅̅̅̅ (𝑎𝑖 𝑏̅𝑖 𝑝̅𝑖−1 ) ̅̅̅̅̅̅̅̅̅̅̅̅̅ (𝑎𝑖 𝑏𝑖 𝑝𝑖−1 ) ; (4) ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅ 𝑃𝑖 = (𝑎 ; (5) 𝑖 𝑏𝑖 ) (𝑎𝑖 𝑝𝑖−1 ) (𝑏𝑖 𝑝𝑖−1 ) При реализации на элементах «Сложение по модулю два», уравнения (1) и (2) выразим через функцию «Сложение по модулю два» получим: ̅̅̅̅̅̅̅̅̅ 𝑆𝑖 = (𝑎𝑖 ⊕ 𝑏𝑖 )𝑝̅𝑖−1 ⋁(𝑎 𝑖 ⊕ 𝑏𝑖 )𝑝𝑖−1 = 𝑎𝑖 ⊕ 𝑏𝑖 ⊕ 𝑝𝑖−1 27 ; (6) 𝑃𝑖 = 𝑝𝑖−1 (𝑎̅𝑖 𝑏𝑖 ⋁𝑎𝑖 𝑏̅𝑖 )⋁𝑎𝑖 𝑏𝑖 (𝑝̅𝑖−1 ⋁𝑝𝑖−1 ) = 𝑎𝑖 𝑏𝑖 ⋁(𝑎̅𝑖 𝑏𝑖 ⋁𝑎𝑖 𝑏̅𝑖 )𝑝𝑖−1 = 𝑎𝑖 𝑏𝑖 ⋁(𝑎𝑖 ⊕ 𝑏𝑖 )𝑝𝑖−1 (7) ; При реализации на элементах «И-ИЛИ-НЕ» получим: ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ 𝑆𝑖 = 𝑎 ̅𝑖 𝑏𝑖 𝑝𝑖−1 ⋁𝑎̅𝑖 𝑏̅𝑖 𝑝̅𝑖−1 𝑖 𝑏𝑖 𝑝̅𝑖−1 ⋁𝑎𝑖 𝑏𝑖 𝑝𝑖−1 ⋁𝑎 𝑃𝑖 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 𝑎̅𝑖 𝑝̅𝑖−1 ⋁ 𝑏̅𝑖 𝑝̅𝑖−1 ⋁𝑎̅𝑖 𝑏̅𝑖 ; (8) ; (9) Схема сумматора на элементах «Сложение по модулю два» будет: Pис. 4.1 Схема одноразрядного двоичного сумматора Временная диаграмма работы одноразрядного двоичного сумматора приведена на рис. 4.2. Pис. 4.2 Временная диаграмма работы одноразрядного двоичного сумматора Пример выполнения 28 На рис. 4.3 изображена схема трехразрядного последовательного сумматора на элементах «сложение по модулю два». Она состоит из 3-х сдвигающих регистров, построенных на универсальных D-триггерах c прямыми установочными входами (DA1DA3 – для числа a, DB1-DB3 – для числа b, DS1-DS3 – для числа-результата суммирования), одноразрядного сумматора (элементы E1-E4, где E3 имеет инверсный выход, в связи с чем был установлен инвертор Е4) и триггер задержки переноса DP. Также используются лампы индикации (a1-a4, b1-b4, S1-S4, ai, bi, Pi-1, Pi , CLK, R) и шина 1 для коммутации выходов триггеров и сумматора. Для работы сумматора в автоматическом режиме регистры для хранения чисел были закольцованы, то есть выход младшего разряда был соединен со входом старшего. Работа схемы начинается с установки элементов в состояние лог. «0» нажатием переключателя K2. Затем с помощью переключателя К3 подается сигнал от генератора одиночных импульсов (ГОИ) на установочные входы триггеров DA1-DA3, DB1-DB3, DP для задания суммируемых чисел и переноса 𝑃𝑖−1 (схема на рис. 4.3 обеспечивает суммирование чисел 001 и 011 без установки переноса 𝑃𝑖−1, для реализации других вариантов необходимо будет перекоммутировать установочные входы (S) триггеров в соответствии с вариантом). При подаче синхроимпульсов на входы CLK происходит поразрядное суммирование чисел. Синхроимпульсы могут подаваться либо с помощью ГОИ и переключателя К4, либо с помощью функционального генератора (ФГ). Выбор между ФГ и ГОИ осуществляется с помощью переключателя К1. Временная диаграмма, демонстрирующая работу сумматора приведена на рис. 4.4 (для обеспечения наглядности временной диаграммы, регистры были предварительно раскольцованы). Сумматор также можно реализовать на регистрах. На рис. 4.5 приведена схема четырехразрядного последовательного сумматора на универсальных сдвигающих регистрах D-типа. Она содержит 2 универсальных четырехразрядных сдвигающих регистра D-типа (D1A, D2B), предназначенных для записи и переноса кодов складываемых чисел (логика работы управляющих переключателей S0, S1 представлена в таблице 2); регистр (D3S) для вывода результата суммирования (вход SR предназначен для сдвига поступившего сигнала вправо, SL- влево), одноразрядный двоичный сумматор на элементах E1-E2 XOR2 (где E3 AND_OR_I имеет инверсный выход, в связи с чем был установлен инвертор Е4 NOT), D-триггер задержки переноса с прямыми входами D4P (так как входы регистров CLR инверсные, то перед триггером стоит инвертор E5 NOT) и лампы индикации (a1-a4, b1-b4, S1-S4, ai, bi, Pi-1, Pi , CLK, R) и шина 1 для коммутации выходов триггеров и сумматора. Для работы сумматора в автоматическом режиме регистры для хранения чисел были закольцованы, то есть выход младшего разряда был соединен со входом старшего. Работа схемы начинается с установки элементов в состояние лог. «0» нажатием переключателя K2. Затем с помощью переключателя К2(замкнутое состояние) подается сигнал от генератора одиночных импульсов (ГОИ) на установочные входы триггера D4P и регистров (A, B, C, D, S0, S1 SHIFT_4BIDI) и 1 синхроимпульс (особенность регистра), для задания переноса 𝑃𝑖−1 и суммируемых чисел (схема на рис. 4.5 обеспечивает суммирование чисел 0011 и 0101 без установки переноса 𝑃𝑖−1, для реализации других вариантов необходимо будет перекоммутировать установочные входы (A, B, C, D) регистров и установочный вход S триггера D4P в соответствии с вариантом). Затем с помощью переключателя К3, регистры переходят в режим сдвига вправо. При подаче синхроимпульсов на входы CLK происходит поразрядное суммирование чисел. Синхроимпульсы могут подаваться либо с помощью ГОИ и переключателя К4, либо с помощью функционального генератора (ФГ). Выбор между ФГ и ГОИ осуществляется с помощью переключателя К1. Временная диаграмма, демонстрирующая работу сумматора приведена на рис. 4.6 (для обеспечения наглядности временной диаграммы, регистры были предварительно раскольцованы). 29 Pис. 4.3 Схема трехразрядного последовательного двоичного сумматора 30 Pис. 4.4 Временная диаграмма работы трехразрядного последовательного двоичного сумматора Таблица 2- Таблица истинности управляющих переключателей регистра S0 S1 Результат 31 0 0 Хранение информации 0 1 Сдвиг влево 1 0 Сдвиг вправо 1 1 Запись информации 32 Pис. 4.5 Схема четырехразрядного последовательного двоичного сумматора Pис. 4.6 Временная диаграмма работы четырехразрядного последовательного двоичного сумматора При выполнении работы следует установить элементы в состояние лог. «0». Затем установить начальные значения в соответствии с вариантом и изучить работу схемы в одиночном режиме (синхроимпульсы с помощью ГОИ). После этого изучить работу схемы в автоматическом режиме (синхроимпульсы с ФГ) и снять временную диаграмму. Контрольные вопросы 1. Дайте определение сумматора. 2. По каким признакам классифицируются сумматоры? 3. Дайте определение комбинационного сумматора. 4. Сравнить сумматоры с последовательной и параллельной организацией переноса. 5. Какими параметрами характеризуются сумматоры? 6. Сравнить объемы схемотехнического оборудования при реализации сумматоров на разных электроэлементах. 33 Варианты заданий № 1 1 2 3 4 5 6 7 8 9 10 11 12 𝑎𝑖 𝑏𝑖 𝑝𝑖−1 2 3 2 3 4 3 2 3 4 3 2 3 4 3 4 5 3 2 4 5 3 2 4 5 3 2 4 1 0 1 1 1 0 1 1 1 0 1 1 Тип Тг 5 Тип элем. 6 № 1 13 14 15 16 17 18 19 20 21 22 23 24 𝑎𝑖 𝑏𝑖 𝑝𝑖−1 2 3 2 3 4 3 2 3 4 3 2 3 4 3 4 5 3 2 4 5 3 2 4 5 3 2 4 1 0 1 1 1 0 1 1 1 0 1 1 Тип Тг 5 Тип элем. 6 D Сложение по модулю два И-НЕ И-ИЛИ-НЕ J-K И-НЕ Сложение по модулю два И-ИЛИ-НЕ Содержание отчета 2. 3. 4. 5. 6. 7. 8. 9. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы сумматора. Временная диаграмма работы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Бабич Н.П., Жуков И.А. “Компьютерная схемотехника”, К., “МК-Пресс”, 2012. 2. Шестеркин А.Н. “Система моделирования и исследования радиоэлектронных устройств Multisim 10”. Издательство “ДМК”. Москва 2012. 34 Лабораторная работа № 5 «Распределитель сигналов» Цель работы: изучить структуры и работу распределителей. Краткие теоретические сведения Распределитель сигналов – устройство, которое при поступлении на его вход переключающих сигналов формирует управляющий сигнал на одном из выходных каналов. В зависимости от назначения распределители различаются числом переключающих входов, каналов, а также длительностью, частотой и порядком следования формируемых сигналов. По виду формируемых сигналов распределители сигналов классифицируются: распределители сигналов (потенциалов); распределители импульсов; комбинированные распределители. Распределители сигналов являются частью системы дискретной обработки информации. Основное их назначение - формирование сигналов для управления другими устройствами цифровой системы. Схема распределителя показана на рис. 5.1. Выходы распределителя обычно называют каналами (И0-Иn, C0-Cn), а его входы, при подаче сигнала на которые происходит включение нового канала - переключающими входами. Рис. 5.1 Схема распределителя сигналов Распределителем импульсов называют устройство, с помощью которого временная последовательность импульсов, поступающая на его вход, распределяется по независимым выходным цепям, или, что- то же самое, каждому числу входных импульсов соответствует сигнал 1 на выходе одной определенной цепи из N возможных. Его иногда называют регистром сдвига единицы, так как при поочередном поступлении входных импульсов сигнал «1» последовательно «перемещается» с одного выхода на другой. Матричный распределитель (рис. 5.2) в общем случае состоит из многоразрядного счетчика и дешифратора (иногда матричный дешифратор называют диодной матрицей, или просто матрицей). Они могут быть выполнены на двоичных счетчиках, обеспечивают минимальную затрату оборудования на одну выходную цепь распределителя. 35 Рис. 5.2 Структурная схема матричного распределителя Распределители комбинированного типа имеют как потенциальные, так и импульсные выходы. Схема распределителя сигналов содержит устройство формирования параллельного кода и дешифратор. Дешифраторы - это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На одном выходе дешифратора появляется логическая единица, а на остальных — логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности. В качестве устройства формирования кода используются кольцевые сдвигающие регистры с прямыми и перекрестными связями и двоичные счетчики. Распределители сигналов на счетчиках. При построении схем распределителей наиболее распространены счетчики с параллельным переносом, обладающие высоким быстродействием и не вызывающие ложного включения каналов при переходе из одного состояния в другое. Распределители на регистрах. К достоинствам этих схем распределителей относятся высокое быстродействие, простота схем дешифрации, регулярность топологии разрядов; к недостатками — наличие запрещенных состояний. В общем случае как число каналов распределителя, так и последовательность их включения могут быть заданы достаточно произвольно. При этом определяющей величиной для построения схемы распределителя является не число каналов, а длина повторяющейся последовательности номеров включаемых каналов. Эта величина соответствует числу различных состояний схемы формирования кодов, и если она кратна степени 2, то в распределителе используется полный дешифратор. В противном случае применяется неполный дешифратор, функции которого минимизируются с учетом запрещенных состояний схемы формирования кодов. Выходы дешифратора с помощью логических схем объединяются согласно повторению номеров на выделенном участке. 36 Пример выполнения Рис. 5.3 Схема трехканального распределителя сигналов на счетчике Джонсона, реализованного на триггерах типа D На рис. 5.3 изображена схема трехканального распределителя сигналов, реализованного на счетчике Джонсона на D-триггерах. Последовательность включения каналов –1,1,3,1,2,3.. 37 ГИ – генератор импульсов. Он генерирует импульсы заданной частоты. ГОИ – генератор одиночных импульсов. При кратковременном сигнале на входе он формирует электрический импульс прямоугольной формы определенной длительности (она не зависит от длительности входного, т. е. запускающего, импульса), после чего переходит в ждущий режим и не работает до прихода следующего запускающего сигнала. S2 – элемент «ключ», который служит для замыкания и размыкания отдельного участка схемы. G1 - логический элемент «или», обозначающий дизъюнкцию. G2, G3, G4 и G5 - логический элемент «и», обозначающий конъюнкцию. G6 и G7 - логический элемент, обозначающий сложение по модулю два. Т1,Т2,Т3 - Dтриггер. ЛА – логический анализатор (для записи логических последовательностей). При работе с ЛА для отображения временной диаграммы, необходимо задать частоту равную 500 Гц. Далее необходимо указать отношение время/деление, оно должно быть равно 4. Входной сигнал задается с помощью функционального генератора. Сигнал поступает на синхронизирующие входы триггеров, осуществляя функционирование регистра (трехразрядный счетчик Джонсона), который служит основой для работы дешифратора. Значение на каждом триггере фиксируется индикатором. Дешифратор, в соответствии с поступающими значениями с триггеров формирует на выходах y1 - yN логические сигналы. Выходные сигналы фиксируются ЛА. Временная диаграмма работы схемы изображена на рис. 5.4. Ее работа иллюстрируется в соответствии с элементами идентификации. 38 39 Рис. 5.4 Временная диаграмма трехразрядного распределителя сигналов, реализованного на счетчике Джонсона и на триггерах типа D Варианты заданий Вариант Число каналов 1 5 2 4 3 3 4 3 5 4 6 3 7 4 8 5 9 3 10 5 11 5 12 3 13 3 14 15 Тип триггеров D j-k + Последовательно сть Схема формирования включения каналов Счетчик Джонсона 1,1,1,3,2,2,3,3,… Счетчик 3,1,2,3,3,2,1,1,… Счетчик 1,1,1,3,2,3,4,2… + Счетчик Джонсона 3,1,1,3,1,2,3,3,… + Счетчик 1,3,3,4,1,3,2,4,… Счетчик Джонсона 4,2,2,3,3,1,1,2,… Счетчик 1,1,2,2,3,3,3,1,… Счетчик Джонсона 3,4,3,1,2,2,3,1,… Счетчик 1,2,4,4,3,2,2,3,… Счетчик 1,2,3,3,2,2,1,1,… + Счетчик Джонсона 1,3,1,3,1,2,3,3,… + Счетчик 1,2,2,3,3,4,… + Счетчик Джонсона 1,2,1,3,3,4,4,4,… 4 + Счетчик 1,3,3,2,3,4,4,1,… 4 + Счетчик Джонсона 4,3,2,4,2,1,3,4,… + + + + + + + Контрольные вопросы 1. 2. 3. 4. 5. Каково назначение распределителя сигналов? Назовите типы распределителей сигналов. Какова структура распределителя, дешифраторов? Дайте сравнительные характеристики распределителя дешифраторов. В чем особенности построения схем дешифраторов на элементах И-НЕ? Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы распределителя. Временная диаграмма работы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10, Издательство «ДМК Пресс», 2012 г. 40 2. Майоров С.А. «Структура цифровых вычислительных машин», Л. Машиностроение. Ленингр. отделение, 1979 г. 41 Лабораторная работа № 6 «Компараторы» Цель работы: изучить структуры компараторов и исследовать их работу. Краткие теоретические сведения Цифровой компаратор предназначен для сравнения двух многоразрядных двоичных чисел. В простейшем случае требуется лишь установить факт равенства бинарных чисел А и В одинаковой разрядности. При п-разрядных числах компаратор состоит из п сумматоров по модулю 2, выходы которых подключены к элементу ИЛИ. Только при совпадении значений всех разрядов чисел А и В на выходах всех сумматоров будет 0. Если же числа отличаются хотя бы в одном разряде, то на выходе соответствующего сумматора и, следовательно, на общем выходе будет 1. Операция поразрядного сравнения заключается в выработке признака равенства (равнозначности) или неравенства (неравнозначности) двух сравниваемых двоичных чисел. Два числа равны при равенстве цифр в одноименных разрядах: аi = bi, где аi – цифра в i-м разряде одного числа, bi – цифра в i-м разряде другого числа. Равенство аi = bi имеет место при аi = 1, bi = 1 или при аi = 0, bi = 0. Поэтому логическая функция, выражающая это равенство, равна единице, если единице равно произведение этих цифр или произведение их инверсных значений, т. е. y aibi aibi , (1) а логическая функция, описывающая компаратор для п-разрядных чисел, имеет вид y (a1b1 a1b1 )(a2b2 a2b2 )...(anbn anbn ) . (2) Для построения компаратора только на элементах И-НЕ запишем её в другой форме, воспользовавшись формулой де Моргана, y ( a1b1 a1b1 )( a2b2 a2b2 )...( an bn an bn ). (3) Схема, реализующая это выражение, приведена на рис. 6.1а. Если необходимо, чтобы при равенстве кодов на выходе компаратора была логическая 1, то к выходу схемы (рис. 6.1а) следует присоединить инвертор. В некоторых компараторах находит применение узел сравнения чисел с определением знака неравенства, т. е. А > B или А < B. Устройство компаратора в этом случае получается более сложным. Число входов его равно 2п, а число выходов три: Y> при А > B, Y= при А = B, Y< при А < B. Компараторы выполняют в виде отдельных микросхем. Так, например, микросхема, изображённая на рис. 6.1б, позволяет сравнивать два четырёхразрядных числа. 42 а1 b1 & & & а0 у & b0 & & an & bn & у А>B Y= а2 & Y> а1 b1 A=B b2 & Y< а3 & & = = а б Рис. 6.1 Данный тип компаратора обладает свойством наращиваемости. Для сравнения, например, 8-разрядных чисел применяют два 4-разрядных компаратора. Для этой цели как в микросхеме на рис. 6.1б предусмотрены три дополнительных входа: А > B, А = B и А < B, к которым подводятся соответствующие выводы микросхемы, выполняющей сравнение младших разрядов. Устройства сравнения на равенство строятся на основе поразрядных операций над одноименным разрядами обоих слов. Признак r равенства разрядов имеет единичное значение, если в обоих разрядах содержатся либо единицы, либо нули, т.е.: ri ai bi ai bi ai bi ai bi ai bi . (4) В свою очередь признак неравенства разрядов: ri ai bi ai bi ai bi ai bi ai bi . (5) Признак неравенства слов R принимает единичное значение, если все разряды равны, т.е.: R rn1 rn2 ...r0 . (6) Устройства сравнения на «больше» («меньше»). Для одноразрядных слов функции FA B A B ( FA B AB ). Функцию FAB для сравнения двухразрядных слов можно получить исходя из следующих условий. Если в старшем разряде слова А – единица, а слова В – нуль, то независимо от младших разрядов A > B и FAB = 1. Если старшие разряды идентичны, то следует переходить к анализу младших, применив к ним то же условие, что и для старшего разряда ( FAB = 1 при A0 = 1 и B0 = 0). Таким образом, справедливо соотношение: FA B A1 B1 A0 B0 r1 , где r1 A1 B1 A1 B1 - признак равенства разрядов. (7) Легко видеть, что сравнение многоразрядных слов должно быть основано на тех же соображениях и поэтому можно записать: FAB A1 B1 A0 B0 B1 A0 A1 B0 A1 B1 A0 B0 ( A1 B1 ) , (8) Как и ранее, первый член формулы отражает результаты сравнения старших разрядов. Переход к анализу младших разрядов производится при условии, что состояние старших разрядов не противоречит этому переносу, но в данном случае это условие имеет вид Ai Bi . Введём обозначения Ci Ai Bi , d i Ai Bi , или d i ri . С помощью этих обозначений по индукции можно записать выражение FAB для сравнения многоразрядных слов: 43 FA B Cn1 Cn2 Dn1 Ci Dn1 ...Di 1 ... C0 Dn1 ...D1 . (9) Пример выполнения Построим схему компаратора по таблице истинности (табл. 6.1). Таблица 6.1 FA<B A B FA=B FA>B 0 1 0 0 1 1 0 0 1 0 1 1 1 0 0 На рис. 6.2 изображена схема реализации компаратора на базе двухразрядного счётчика Джонсона. Условные обозначения: ФГ – функциональный генератор. Он может вырабатывать сигналы прямоугольной, синусоидальной и треугольной формы. ГОИ – генератор одиночных импульсов. При кратковременном сигнале на входе он формирует электрический импульс прямоугольной формы вполне определённой длительности(она не зависит от длительности входного, т.е. запускающего импульса), после чего переходит в ждущий режим и не работает до прихода следующего запускающего сигнала. Р1, Р2 и Р3 – элемент «ключ», который служит для смыкания и размыкания отдельного участка схемы. G1 и G2 – логический элемент «и», обозначающий конъюнкцию. G3 – логический элемент «или», обозначающий дизъюнкцию. J-K – устройство, отражающее на схеме J-K триггер. ЛА – логический анализатор. Это устройство предназначенное для записи логических последовательностей. L1, L2 и L3 – индикаторы, фиксирующие сигналы с выходов различных логических элементов и триггеров. 44 45 Рис. 6.2 Схема реализации компаратора на базе двухразрядного счётчика Джонсона Первоначально оба триггера устанавливаются в «0» путём подачи сигнала с генератора одиночных импульсов (ГОИ) на входы Reset. Затем входной сигнал задаётся с функционального генератора (ФГ), он поступает на синхронизирующие входы триггеров (U1, U2), осуществляя функционирование счётчика (двухразрядного счётчика Джонсона), который служит основой для работы компаратора. Значение информации на каждом триггере фиксируется индикаторами (L1, L2, L3). Значение информации на элементе «или»(G3) также фиксируется индикатором. Компаратор, в соответствии с поступающими значениями информации с триггеров, формирует сигналы на выходах G1_1, G2_1 и G3_1, которые поступают с логических элементов «и»(G1 и G2) и исключающее «или»(G3). Эти сигналы фиксируются логическим анализатором (ЛА) и индикаторами (L1, L2, L3). Временная диаграмма работы компаратора изображена на рис. 6.3. Рис. 6.3 Временная диаграмма работы компаратора на базе двухразрядного счётчика Джонсона Варианты заданий Варианты Функции Количество разрядов Тип триггеров 1 А=В, А>В, А<В 1и2 D 2 А=В, А>В 2 J-K 3 А=В, А<В 2 D 4 А=В, А>В, А<В 1и2 J-K 5 А=В, А>В 2 D 6 А=В, А<В 2 J-K 7 А=В, А>В, А<В 1 J-K 8 А=В 4 D 9 А=В 4 J-K задания 46 10 А=В, А<В 4 D 11 А=В, А>В 4 J-K 12 А=В, А>В, А<В 4 D Контрольные вопросы 1. Дайте определение компаратора. 2. Какие микрооперации можно реализовать с помощью компаратора? 3. Объясните полученные при исследовании данные. Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы компаратора. Временная диаграмма и осциллограмма. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10. – М.: ДМК Пресс, 2012. – 360 с. 47 Лабораторная работа № 7 «Преобразователь параллельного кода в последовательный» Цель работы: понять и изучить структуру преобразователя параллельного кода в последовательный. Краткие теоретические сведения Параллельным называют код, все разряды которого передаются с устройства на устройство одновременно (параллельно). Последовательным называют код, разряды которого передаются с устройства на устройство один за другим (последовательно во времени). Для преобразования параллельного кода в последовательный можно использовать универсальный регистр – рис. 7.1. Рис. 7.1 Преобразователь параллельного кода в последовательный Он имеет параллельные и последовательные входы, а также параллельные выходы. Число разрядов сдвигающего регистра (параллельных входов для записи кода) на один разряд больше, чем разрядность входного кода. В этот разряд, сигнал которого при смещении кода появляется на выходе последним, записывается логический ноль, во все остальные разряды - входной код. Запись входной информации производится по фронту импульса, поступающего на вход С1. На последовательный вход регистра DSR постоянно подается логическая единица. После завершения записи информации в регистр каждым импульсом, поступающим на вход смещения С2, данные в регистре перемещаются на один разряд, то есть на n-ом выходе последовательно появляется информация, хранящаяся в регистре. В освобождающиеся разряды регистра вместо “выталкиваемых” данных записываются логические единицы. Схема такого преобразователя не громоздка и позволяет смоделировать процессы, про По окончанию преобразования сигнал на выходе элемента (n+1)И примет значение логической единицы, тем самым будет сформирован запрос на вызов очередного входного кода. 48 Пример выполнения Построим преобразователь параллельного кода в последовательный на основе универсального регистра (рис. 7.1). При его построении (рис. 7.2) использованы компоненты: резисторы R1-R5, логический анализатор ЛА, переключатели П1-П7, УП1, УП2, ключ К0, четырехразрядные двунаправленные универсальные сдвигающие регистры DD1 и DD2 (микросхема 74LS194N), 8И DD3, индикаторы 1-9 (PROBE), функциональный генератор ФГ, генератор одиночных импульсов ГОИ, а также шины № 1, № 2 и № 3. Входной код задается с помощью переключателей П1-П7, чьи выходы единены с соответствующими входами регистров DD1 и DD2. Шина 1 используется для коммутации управляющих цепей, шина 2 – входного кода, и шина 3 – выходных сигналов регистра. Режим работы регистра устанавливается сигналами 2 и 1, которые поступают с переключателей УП1 и УП2 в соответствии с таблицей истинности применяемой микросхемы (табл. 7.1). Замыкание ключа К0 обеспечивает установку регистра в нулевое состояние. Функциональный генератор отвечает за формирование фронта импульса Cin на входах синхронизации регистров CLK. Цепь UR при не замкнутом ключе К0 поддерживает уровень логической единицы на входах установки нуля регистров CLR. При заполнении регистра единицами на выходе DD3 формируется уровень логической единицы и загорается индикатор 9. Индикаторы 1-8 позволяют контролировать данные, записанные в регистр и процесс их сдвига. На рис. 7.2 они индицируют состояние регистра после записи в него входной последовательности 1010101. После окончания преобразования все индикаторы должны светиться. Перед началом работы необходимо произвести сброс значений регистра при помощи ключа К0. Записав входную последовательность, осуществить сдвиг информации, воспользовавшись УП1 и УП2 в соответствии с таблицей истинности управляющих переключателей (табл. 7.1). Результат работы преобразователя с входной последовательностью 1010101 и сдвигом вправо изображен на рис. 7.3, где Cin- синхронизирующий сигнал, 1-7 – разряды входной последовательности и 8-разряд в который путем сдвига последовательно поступает входная последовательность. Таблица 7.1- Таблица истинности управляющих переключателей 49 УП1 УП2 Результат 0 0 Хранение информации 0 1 Сдвиг вправо 1 0 Сдвиг влево 1 1 Запись информации 50 Рис. 7.2 Схема преобразователя параллельного кода в последовательный Рис. 7.3 Временная диаграмма режима работы преобразователя Варианты заданий Разработать схему преобразователя параллельного кода в последовательный и получить временную диаграмму режима работы преобразователя с входной последовательностью согласно вашему варианту (табл. 7.2). Таблица 7.2- Варианты заданий № Входная 51 № Входная варианта последовательность варианта Последовательность 1 1100111 16 1110001 2 1110011 17 1010100 3 1111001 18 1010110 4 1111100 19 1010111 5 1001111 20 1110101 6 0011111 21 1110100 7 1100011 22 1110110 8 1110001 23 1110111 9 1111000 24 1000001 10 1000111 25 0100001 11 0001111 26 0010001 Продолжение табл. 7.2 12 1100001 27 0001001 13 1110000 28 0000101 14 1000011 29 0000011 15 0000111 30 1111101 Контрольные вопросы 1. Что такое параллельный код двоичного числа? 2. Что такое последовательный код двоичного числа? 3. Пояснить основы работы с преобразователем параллельного кода двоичного числа в последовательный. Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы преобразователя. Временная диаграмма работы преобразователя. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10. Издательство “ДМК”. Москва 2012г. 52 Лабораторная работа № 8 «Преобразователь последовательного кода в параллельный» Цель работы: изучение структуры и исследование работы преобразователя последовательного кода в параллельный. Краткие теоретические сведения Любой символ информации в цифровых устройствах кодируют в двоичном коде, поэтому сигналы могут принимать только два значения: высокий или низкий уровень напряжения, наличие или отсутствие импульса напряжения и т. д. Значения уровней сигналов (Uc) элементами цифровых устройств воспринимаются не непрерывно, а в дискретные моменты времени, интервал между которыми называют рабочим тактом Т. Как правило, за один рабочий такт в цифровых устройствах осуществляется одно элементарное преобразование поступивших на вход кодовых слов. Дискретизация времени обеспечивается специальными устройствами управления, вырабатывающими синхронизирующие импульсы (СИ). В дискретных устройствах используют два способа представления информации: потенциальный и импульсный. При потенциальном способе значениям логического 0 и логической 1 соответствуют напряжения низкого и высокого уровня. Если логическому 0 соответствует напряжение низкого уровня, а логической 1 - высокого, то такую логику называют положительной, и наоборот, если за логический 0 принимают напряжение высокого уровня, а за логическую 1 - напряжение низкого уровня, то такую логику называют отрицательной или инверсной. Далее в основном используются термины "напряжение высокого и низкого уровня" (сигналы высокого и низкого уровня), соответствующие уровням логической 1 и логического 0. Информация в цифровых устройствах может быть представлена в последовательном и параллельном кодах. Параллельным называют код, все разряды которого передаются с устройства на устройство одновременно (параллельно). Последовательным называют код, разряды которого передаются с устройства на устройство один за другим (последовательно во времени). Примером последовательного устройства может быть счетчик импульсов, состояние выходов которого зависят от общего числа поступивших на его вход импульсов. При использовании последовательного кода каждый такт соответствует одному разряду двоичного кода. Номер разряда определяется номером такта, отсчитываемого от такта, совпадающего с началом представления кода. Графики, показанные на рис. 8.1, иллюстрируют последовательный код байтового двоичного числа 10011011 при потенциальном и импульсном способах представления информации. Для передачи всего числа требуется восемь тактов (рис. 8.1а). При потенциальном способе (рис. 8.1б) сигнал сохраняет низкий или высокий уровни в течение одного или нескольких тактов. В моменты перехода сигнала от одного уровня к другому его значение является неопределенным. При импульсном способе представления цифровой информации (рис. 8.1в) единичному и нулевому значению двоичной переменной соответствует наличие или отсутствие импульса конечной длительности. При последовательном коде числа все его разряды могут быть зафиксированы на одном элементе и переданы по одному каналу передачи информации. 53 Рис. 8.1 Последовательный код двоичного числа при импульсном и потенциальном способах представления информации Параллельный код позволяет существенно сократить время обработки и передачи информации. На рис. 8.2 изображен параллельный код семиразрядного числа 1101101. В этом случае, как при импульсном (рис. 8.2а), так и при потенциальном (рис. 8.2б) способах представления информации все разряды двоичного кода представлены в одном временном такте, могут фиксироваться отдельными элементами и передаваться по раздельным каналам (разрядным шинам). Рис. 8.2 Параллельный код двоичного числа при импульсном и потенциальном способах представления информации Последовательный код позволяет передавать любое число разрядов по простейшему каналу связи, имеющему одну единственную линию связи между устройствами. Скорость передачи кодов при этом будет уменьшаться с увеличением числа информационных разрядов в коде. Скорость передачи параллельных кодов напротив не связана с числом разрядов, однако для передачи n-разрядного кода здесь требуется канал связи, имеющий n-параллельных линий связи. В случае большего расстояния между цифровыми устройствами обычно используют последовательный 54 код. В цифровых устройствах иногда приходится выполнять преобразование параллельного кода в последовательный или наоборот. Преобразователем кодов называется цифровое устройство, осуществляющее преобразование слов входного алфавита (x1, х2,..., хn) в слова выходного алфавита (y1, y2, ..., yk). Соотношения между числами n,k могут быть любыми: n = к, n > к, n < к. Преобразователи кодов можно разделить на два типа: с весовым преобразователем кодов, с невесовым преобразователем кодов. Примером преобразователей первого типа являются преобразователи десятичных кодов в двоичные, двоично-десятичных кодов в двоичные, двоичных кодов в десятичные и двоично-десятичных в двоичные, и другие. Преобразователи второго типа используются для преобразования двоично-десятичного кода в код семисегментного индикатора десятичных цифр, двоичного кода в код Грея и другие. Эти задачи решаются разными путями. Одним из таких путей является применение комбинационных узлов, называемых преобразователями кодов. Пример выполнения Для построения схемы преобразователя последовательного кода в параллельный (рис. 8.3) используются следующие элементы: резисторы (R1, R2, R3, R4, R5), генератор напряжения (ГН), функциональный генератор (ФГ), кнопки (К1, К2, К3), переключатели (П1, П2, П3), элементы (DD1, DD2), шины (№ 1, № 2, № 3), осциллограф (Осц), элементы индикации (1,..8), логический анализатор (ЛА). В схеме преобразователя последовательного кода в параллельный для генерирования информационного сигнала используется переключатель П3. Для выбора режима работы регистра используются переключатели П1 и П2. Сдвиг данных в регистре вправо (от входа A к входу D) происходит при формировании фронта синхронизирующего импульса, если переключатель П1 в верхнем, а П2 в нижнем положении. Кнопка К2 служит для сброса регистра. Моделирование сдвигающих импульсов можно осуществлять с помощью кнопки К3. Для записи необходимой информации к моменту нажатия на кнопку К3 переключатель П3, определяющий текущее значение записываемого в регистр сигнала, необходимо установить в соответствующее положение («1» - вверх, подключить к резистору R1; «0» - вниз, к шине Гн). Процесс записи и сдвига информации в регистре (элементы DD1-DD2) с помощью переключателей просто контролировать с помощью элементов индикации (лампочек 1-8). Для автоматического формирования сдвигающих импульсов используется функциональный генератор. Так как выходное сопротивление генератора мало, то ключ K2 при подключенном генераторе не влияет на работу схемы. При формировании сдвигающих импульсов генератором процесс записи и сдвига данных контролируется с помощью осциллографа. При формировании сдвигающих импульсов генератором и изменении входного сигнала с помощью интерактивного переключателя П3 необходимо выбрать такую частоту импульсов генератора, при которой исследователь к моменту формирования очередного импульса генератора успевал бы устанавливать очередной необходимый уровень входного сигнала (около 10 Гц). Форма импульсов генератора – прямоугольная, коэффициент заполнения – 20%, амплитуда выходных импульсов и смещение – 2.4 В. 55 Рис. 8.3 Схема преобразователя последовательного кода в параллельный Осциллограмма, приведенная на рис. 8.4, иллюстрирует запись в регистр кода 01011000. Очевидно, правые позиции кода записываются раньше левых. В верхней части осциллограммы изображены импульсы синхронизации, в нижней части – уровни входного сигнала при каждом из этих импульсов, которые представляет собой последовательный код 01011000. Конечный результат преобразования – записанный в регистре код – отображают и элементы индикации1-8 (рис. 8.3). Рис. 8.4 Осциллограмма преобразования последовательного кода в параллельный 56 Временная диаграмма работы, приведенная на рис. 8.5, иллюстрирует конечный результат преобразования – записанный в регистре код. Сигнал высокого уровня n-го индикатора означает, что он включен, сигнал низкого уровня - выключен. Последовательность уровней входящего сигнала представлена в виде логических нулей и логических единиц под временной диаграммой. Каждое новое изменение уровня входящего сигнала соответствует изменению уровней сигналов индикаторов. Рис. 8.5 Временная диаграмма режима работы Варианты заданий Разработать схему преобразователя последовательного кода в параллельный. Получить осциллограмму преобразования последовательного кода двоичного числа в параллельный и временную диаграмму режима работы. Двоичное число выбрать согласно своему варианту (табл. 8.1). Таблица 8.1 № варианта Двоичное число № варианта Двоичное число 57 1 10100011 16 01000111 2 10001110 17 00111001 3 10100011 18 01100101 4 01100110 19 01110011 5 10001010 20 01100011 6 01101010 21 10001110 7 10011011 22 01011011 8 10101000 23 01011110 9 01000110 24 01001110 10 11110010 25 10110011 11 01110001 26 10011101 Продолжение табл. 8.1 12 01011110 27 10110011 13 00011011 28 01100111 14 00100011 29 00110110 15 01011100 30 00110100 Контрольные вопросы 1. 2. 3. 4. Что такое последовательный код двоичного числа? Что такое параллельный код двоичного числа? Что такое преобразователь кодов? Пояснить работу преобразователя последовательного кода в параллельный. Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы преобразователя. Временная диаграмма работы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10. – М.: ДМК Пресс, 2012. – 360 с. 58 Лабораторная работа № 9 «Делители частоты импульсной последовательности» Цель работы: изучение структуры делителей частоты, построение и исследование различных схем делителей. Краткие теоретические сведения Делитель частоты — устройство, которое при подаче на его вход периодической последовательности импульсов формирует на выходе такую же последовательность, но имеющую частоту повторения импульсов, в некоторое число раз меньшую, чем частота импульсов входной последовательности. Отличие делителей частоты от счетчиков состоит в следующем. В счетчике каждая комбинация состояний триггеров определяет в некоторой системе счисления число импульсов, поступивших к данному моменту времени. В делителе частоты последовательность состояний может быть выбрана произвольной, важно лишь обеспечить заданный период цикла T. Последовательность состояний выбирается из соображений обеспечения при заданном T наибольшей простоты межтриггерных связей. Эти связи должны выполняться непосредственным соединением выходов одних триггеров с входами других без логических элементов. Счетчик, имеющий то же значение T, может исполнять роль делителя частоты, однако следует иметь в виду, что такое решение будет неэкономичным. Делители частоты импульсной последовательности характеризуются коэффициентом деления N, который показывает, во сколько раз период импульсной последовательности на выходе делителя частоты Tвых больше периода импульсной последовательности на входе Tвх . Делитель частоты с коэффициентом деления N = 2 (рис. 9.1a). В моменты отрицательного фронта входных импульсов триггер переключается в новое состояние. Как видно из временной диаграммы на рис. 9.1б, период импульсной последовательности Tвых на выходе триггера оказывается вдвое больше периода следования импульсов на входе. a б Рис. 9.1 Делитель частоты с коэффициентом деления N = 2 Следовательно: 1 1 𝑓вх = = 𝑇вых 2𝑇вх 2 т.е. частота следования импульсов на выходе в два раза ниже, чем на входе. 𝑓вых = Делитель частоты с коэффициентом деления N = 2n. На рис. 9.2a показано последовательное соединение делителей частоты с коэффициентом деления, равным двум, при котором выход каждого из делителей подключен к входу следующего. На выходе каждого делителя частота следования импульсов вдвое ниже, чем на входе. 59 Так, если частота следования импульсов на входе первого делителя 𝑓вх , то на выходе 𝑓 𝑓 𝑓 первого делителя 𝑓вых1 = вх, на выходе второго 𝑓вых2 = вых1 = вх2 , 2 на выходе третьего 𝑓вых3 = 2 𝑓вых2 2 = 𝑓вх 23 2 и т.д. При «n» каскадах этого делителя, частота выходной последовательности окажется равной 𝑓вых = частоты в N = 2n раз. 𝑓вх 2𝑛 , т. е будет осуществляться деление Делитель частоты с коэффициентом деления N = 3 (рис. 9.3). Счетчик с периодом цикла N = 3 имеет простейшие меж триггерные связи без логических элементов. Этот счетчик может одновременно служить и делителем частоты с коэффициентом N = 3. Рис. 9.3 Делитель частоты с коэффициентом деления N=3 60 Делитель частоты с коэффициентом деления N = 5. Схема делителя частоты и временная диаграмма работы приведены на рис. 9.2, таблица состояний (табл. 9.1). Таблица 9.1 Состояние триггеров Номер входного импульса текущее следующее a3 a2 a1 a3 a2 a1 1 0 0 0 0 0 1 2 0 0 1 0 1 1 3 0 1 1 1 1 0 4 1 1 0 1 0 0 5 1 0 0 0 0 0 6 0 0 0 0 0 1 7 0 0 1 0 1 1 … … … … … … … Как видно из временной диаграммы, на выходах триггеров всегда образуется последовательность импульсов с частотой в пять раз более низкой, чем частота импульсов на входе делителя. Каскадные делители частоты. В тех случаях, когда коэффициент деления N не является простым числом и может быть представлен произведением вида 𝑁 = 𝑁1 ∙ 𝑁2 ∙ 𝑁3 ∙ . .. ∙ 𝑁𝑘 , схема делителя строится в виде каскадного соединения делителей, имеющих коэффициенты деления 𝑁1 , 𝑁2 , 𝑁3 , . . . , 𝑁𝑘 (рис. 9.4). Рис. 9.4 Каскадное соединение делителей частоты Примером такого каскадного построения делителей является рассмотренный ранее делитель с коэффициентом 2n (рис. 9.2). Делитель частоты с коэффициентом деления 𝑁 = 6. Этот коэффициент можно представить произведением 𝑁 = 3 ∙ 2. Таким образом, данный делитель может быть построен в виде каскадного соединения делителей, имеющих коэффициенты деления 𝑁1 = 3 и 𝑁2 = 2. (рис. 9.5). 61 Рис. 9.5 Делитель частоты с коэффициентом деления N=6 N=6Построим делитель с коэффициентом деления N=6 Делитель частоты с коэффициентом деления 𝑁 = 9. Представим этот коэффициент в форме 𝑁 = 3 ∙ 3 и реализуем каскадным соединением двух делителей с коэффициентами 𝑁1 = 𝑁2 = 3 (рис. 9.6). Рис. 9.6 Делитель частоты с коэффициентом деления N=9 Делитель частоты с коэффициентом деления 𝑁 = 10. Представим 𝑁 = 𝑁1 ∙ 𝑁2 = 5 ∙ 2, при этом схема делителя строится в виде каскадного соединения делителей с коэффициентами 𝑁1 = 5 и 𝑁2 = 2 (рис. 9.7). Рис. 9.7 Делитель частоты с коэффициентом деления N=10 Таким образом, имея набор схем, реализующих коэффициенты деления, которые представляют собой простые числа, можно их каскадным соединением получать делители с разнообразными коэффициентами деления. Примеры выполнения Пример 1. Построим делитель частоты с коэффициентом деления 𝑁 = 4 на D триггерах. Представим этот коэффициент в форме 𝑁 = 2 ∙ 2 и, соответственно, соединим последовательно два делителя с коэффициентами 𝑁1 = 𝑁2 = 2. Перед запуском схемы (рис. 9.8а) триггеры устанавливаются в исходное состояние подачей сигнала на вход Reset с помощью генератора одиночных импульсов (ГОИ). Генератор импульсов (ГИ) подает на входы CLK исходную импульсную последовательность, с заданной частотой. Импульсная последовательность, получившаяся в результате деления частоты, регистрируется на осциллографе (ОСЦ). 62 Рис. 9.8a. Делитель частоты с коэффициентом деления N=4 Из полученной схемы видно, что построив делитель с коэффициентом N=4 (ветвь 4), мы так же получаем делитель с коэффициентом N=2 (ветвь 2). На рис. 9.8б показана временная диаграмма делителя. Рис. 9.8б. Временная диаграмма работы делителя частоты с коэффициентом деления N=4 Пример 2. Построим делитель с коэффициентом деления 𝑁 = 9 на J-K триггерах. Представим этот коэффициент в форме 𝑁 = 3 ∙ 3 и реализуем каскадным соединением двух делителей с коэффициентами 𝑁1 = 𝑁2 = 3. Перед запуском схемы (рис. 9.9а) триггеры приводятся в исходное состояние подачей сигнала с ГОИ на вход Reset. Последовательность импульсов будет создаваться генератором импульсов (ГИ). На “K” входы схемы подается непрерывный сигнал “1”. Рис. 9.9а. Делитель частоты с коэффициентом деления N=9 Из полученной схемы видно, что построив делитель с коэффициентом N=9 (ветвь 9), мы так же получаем делитель с коэффициентом N=3 (ветвь 3). На рис. 9.9б показана временная диаграмма делителя. 63 Рис.9б. Временная диаграмма работы делителя частоты с коэффициентом деления N=9 Контрольные вопросы 1. 2. 3. 4. 5. Назначение делителя частот импульсной последовательности? В чем состоит отличие делителя частоты от счетчика? Как в схемах делителей частоты достигается простота меж триггерных связей? Как определяется период частоты последовательности импульсов? Объяснить работу схем. Варианты заданий Вариант Коэффициент деления D-триггер J-K-триггер 1 4 21 2 6 15 3 9 16 4 10 18 5 12 10 6 14 12 7 15 14 8 16 9 9 18 6 10 21 4 Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы преобразователя. Временные диаграммы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. – М.: “Высшая школа”, 2012 64 Лабораторная работа № 10 «Аналого-цифровые преобразователи (АЦП)» Цель работы: изучение аналого-цифровых преобразователей (АЦП). Краткие теоретические сведения Аналого-цифровые преобразователи (АЦП) являются устройствами, предназначенными для преобразования непрерывных сигналов в цифровую форму для последующей обработки цифровыми процессорами и отображения на цифровых индикаторах. Некоторые физические величины могут быть непосредственно преобразованы в цифровую форму, однако эту задачу удается решить лишь в редких случаях из-за сложности таких преобразователей. Поэтому в настоящее время наиболее рациональным признается способ преобразования различных по физической природе величин сначала в функционально связанные с ними электрические, а затем уже с помощью преобразователей напряжение-код – в цифровые. Именно эти преобразователи имеют обычно в виду, когда говорят об АЦП. Преобразование включает в себя дискретизацию измеряемой величины во времени, квантование ее по уровню и кодирование. Дискретизация - процесс получения значений сигнала, который преобразуется, с определенным временным шагом - шагом дискретизации. Чем меньше шаг дискретизации, тем выше частота дискретизации и тем более точное представление о сигнале нами будет получено. Квантование – процесс замены реальных значений амплитуды сигнала значениями, приближенными с некоторой точностью. Каждый из возможных уровней называется уровнем квантования, а расстояние между двумя ближайшими уровнями квантования называется шагом квантования. Операция квантования подобна операции округления чисел и поэтому приводит к появлению погрешности квантования. Кодирование позволяет представить квантованные отсчеты в виде некоторого набора дискретных сигналов – кода. Для кодирования используют унитарный код (счетную последовательность импульсов), двоичный код, код Грея и др. Наибольшее распространение получили три классических метода преобразования и основанные на них три типа АЦП. Метод последовательного преобразования – последовательные АЦП. Этот метод основан на уравновешивании значений входной аналоговой величины суммой одинаковых и минимальных эталонов, называемых квантами. Момент равенства суммы квантов и значения входной величины устанавливается одним сравнивающим устройством – компаратором. Результат представляется в последовательном единичном коде, который преобразуется в двоичный код счетчиком. При количестве разрядов выходного кода, равном n, для уравновешивания максимального значения входной величины необходимо подсчитать 2n квантов. По этой причине метод имеет низкое быстродействие. Метод параллельного преобразования – параллельные АЦП. В этом методе применяется 2n-1 эталонов. При этом старший эталон равен 2n-1 квантов, а младший равен одному кванту. Входная величина сравнивается со всеми эталонами одновременно, для чего необходимо 2n-1 компараторов. Результат фиксируется по числу компараторов, отметивших превышение входной величины каким-либо эталоном. Полученный параллельный единичный код преобразуется в параллельный двоичный код специальным преобразователем кодов. Основное достоинство - высокое быстродействие (частота преобразования достигает сотен мегагерц). Основной недостаток – для реализации преобразователя требуется большое число элементов, в основном компараторов. 65 Метод параллельно-последовательного преобразования (комбинированные) АЦП. Преобразование осуществляется в 2 этапа: вначале производится определение старших разрядов выходного кода с помощью малоразрядного параллельного АЦП. Затем с помощью цифроаналогового преобразования найденных старших разрядов и дополнительных узлов вырабатывается разностный сигнал, который используется для определения младших разрядов выходного кода другим АЦП. Такая структура позволяет уменьшить число элементов, необходимых для реализации устройства, однако при этом уменьшается и быстродействие. Классическим примером АЦП последовательного типа являются времяимпульсные преобразователи. В них аналоговая величина (входное напряжение) Ux с помощью линейно растущего напряжения (ЛРН) преобразуется в пропорциональный интервал времени Δt, который заполняется счетными импульсами с целью получения сначала унитарного кода, а затем позиционного двоичного кода. Преобразование напряжения Ux во временной интервал Δt происходят одновременно. Принцип построения такого АЦП иллюстрируется блок-схемой, показанной на рис. 10.1. Рис. 10.1. Блок-схема АЦП времяимпульсного типа При равенстве входного 𝑈вх и выходного напряжений генератора ГЛРН срабатывает схема сравнения Сх ср, ее выходным сигналом триггер Т возвращается в исходное состояние и прекращается поступление импульсов на счетчик СТ. Очевидно, чем больше входное напряжение, тем больше импульсов поступит на вход счетчика, т.е. тем больше будет выходной код. Диапазон изменения выходного напряжения ГЛРН должен совпадать с диапазоном изменения входного напряжения. Пример выполнения Построим преобразователь напряжение-код времяимпульсного типа. На рис. 10.1 показана возможная схема преобразователя напряжения в код. При построении схемы использованы компоненты: резистор (R1,R2), импульсный генератор (ИГ, группа Sources, подгруппа SIGNAL_VOLTAGE_SOURCES), схема сравнения (DA1,DA2, COMPARATOR_VIRTUAL, группа Analog, подгруппа ANALOG_VIRTUAL), триггер (DD3A), логическое И 74LS08N (DD1A, DD1B, DD1C), инвертор 74LS04D (DD2A, DD2B, DD2C, DD2D), двоично-десятичный счетчик 7490N (DD1, DD2, DD3), генератор тока (I1), конденсатор (С1, С2, С3), функциональный генератор (ФГ), источник постоянного напряжения (V1), знакосинтезирующий индикатор со схемой управления (Т1, Т2, Т3, DCD_HEX_DIG…, группа Indicators, подгруппа HEX_DISPLAY). 66 67 Рис. 10.2 Преобразователь напряжение-код Отметим особенности разработанной схемы. Частота и максимальная длительность преобразования входного напряжения определяются соответственно периодом и длительностью импульсного генератора ИГ. Фронт импульса генератора, продифференцированный элементами R1, C2, DD1A, DD2A, DD2B, обеспечивают установку в исходное состояние счетчика (элементы DD1, DD2, DD3) и триггера (DD3A). При единичном состоянии триггера импульсы генератора ФГ через элемент DD1C поступают на счетный вход трехдекадного счетчика, построенного на трех двоично-десятичных счетчиках. Для формирования линейно растущего напряжения используется генератор тока I1, от которого во время формирования импульса генератором ИГ заряжается конденсатор С1. Во время паузы импульса конденсатор С1 разряжается ключевым элементом DA1. При равенстве линейно растущего и входного напряжения на выходе схемы сравнения (DA1) формируется импульс, фронтом которого триггер (DD3A) возвращается в исходное состояние, и прекращается поступление импульсов на счетчик (DD1-DD3). Таким образом счетчик оказывается в состоянии, которое равно числу импульсов, поступивших на его счетный вход за время преобразования. На рис. 10.3 изображены временные диаграммы работы преобразователя (CLK CT – импульсы поступающие на счетчик, ln1-ln4 - входы индикатора Т1). Рис. 10.3 Временные диаграммы работы преобразователя напряжение-код Варианты заданий Разработать преобразователь напряжения с амплитудой в соответствие со своим вариантом и получить диаграммы его работы (табл. 10.1). 68 Таблица 10.1- Варианты заданий № варианта Входное напряжение (В) № варианта Входное напряжение (В) 1 1,5 13 3,0 2 1,6 14 3,1 3 1,7 15 3,2 4 1,8 16 3,3 5 1,9 17 3,4 6 2,0 18 3,5 7 2,1 19 3,6 8 2,2 20 3,7 9 2,3 21 3,8 10 2,4 22 3,9 11 2,5 23 4,0 12 2,6 24 4,1 13 2,7 26 4,2 14 2,8 28 4,3 15 2,9 30 4,4 Контрольные вопросы 1. 2. 3. 4. Как классифицируются АЦП по принципу действия? Какие этапы включает в себя аналого-цифровое преобразование? Какой из методов преобразования имеет самое высокое быстродействие? К АЦП какого типа относятся времяимпульсные преобразователи? Содержание отчета 1. 2. 3. 4. 5. 6. 7. 8. Наименование работы. Цель работы. Краткие теоретические сведения. Вариант задания. Пример выполнения схемы АЦП. Временные диаграммы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10. Издательство “ДМК”. Москва 2012г. 69 Лабораторная работа № 11 «Цифро-аналоговые преобразователи (ЦАП)» Цель работы: изучение цифро-аналоговых преобразователей (ЦАП) на основе взвешенных напряжений. Краткие теоритические сведения Основное применение ЦАП – получение аналогового сигнала из сигналов последовательности цифровых кодов. По принципу действия их можно разделить на накапливающие, времяимпульсные и весовые. В первых выходное напряжение формируют путем заряда конденсатора импульсами одной полярности образцовой амплитуды, число которых определяется двоичным кодом. В преобразователях времяимпульсного типа выходной сигнал представлен в виде импульсов одинаковой частоты и амплитуды, но разной длительности, т.е. выходной сигнал определяется значением последовательности импульсов. В весовых преобразователях необходимо сформировать ряд величин (эталонных значений), соответствующих разрядам кода. Затем в соответствии с входным кодом взять необходимые эталонные значения и сложить. Выходной сигнал ЦАП принимает одно из возможных сочетаний совокупности эталонных значений, т.е. является квантованным. Однако при большом числе разрядов шаг квантования становится малым и погрешностью квантования можно пренебречь. Основные параметры весовых преобразователей: шаг квантования (разрешающая способность) – приращение выходного сигнала при изменении входного кода на единицу младшего разряда. Он определяется числом разрядов, чем больше число разрядов, тем меньше шаг квантования; диапазон изменения выходного сигнала или максимальное выходное напряжение 𝑈𝑚𝑎𝑥 ; максимальная частота преобразования 𝑓𝑚𝑎𝑥 , при которой параметры преобразователя соответствуют заданным значениям. Эта характеристика определяет быстродействие преобразователя. Оно оценивается по времени изменения сигнала на выходе при изменении старшего разряда входного кода. Другими параметрами являются метрологические характеристики. Их получают, сравнивая идеальную характеристику преобразования с реальной. Характеристика преобразования (рис. 11.1) – это ступенчатая кривая напряжений U, получаемая на выходе преобразователя при последовательном изменении входного кода от минимального до максимального. Если аппаратных погрешностей нет, то средние токи ступенек характеристики располагаются на прямой линии. Рис. 11.1 Характеристика преобразования 70 Схемы весовых преобразователей могут быть с параллельным суммированием напряжений (рис. 11.2) и с последовательным (рис. 11.3). Для преобразователей с параллельным суммированием напряжений эталонные напряжения (𝑖 = 1,2, … , 𝑛) коммутируются ключевыми элементами 𝐾𝑖 в соответствии с входным кодом. Единица в некотором разряде преобразуемого кода соответствует замыканию соответствующего ключа. Выходное напряжение 𝑈вых соответствует кодовой комбинации, поступившей на вход. Оно изменяется при изменении входных кодов. Рис. 11.2 Параллельное суммирование Рис. 11.3 Последовательное суммирование При последовательном суммировании необходимо использовать переключаемые элементы 𝐾𝑖 , позволяющие соединять эталонные источники других разрядов, если источник текущего разряда не участвует в формировании выходного напряжения. Приведенные выше схемы имеют существенный недостаток: для реализации преобразователя требуется значительное число эталонных источников с различными напряжениями, причем параметры каждого из них должны поддерживаться с высокой точностью. При преобразовании двоичного кода в аналоговый сигнал, число эталонных источников равно числу разрядов 𝑛, а эталонные значения соседних разрядов отличаются в два раза. Таким образом, параметры эталонных источников старшего и младшего различаются в 2𝑛−1 раз. Технологически сформировать и коммутировать высокоточные эталонные источники, отличающиеся друг от друга в десятки, а тем более в сотни раз, достаточно сложно. Рассмотренный недостаток отсутствует в схемах преобразователей с использованием цепных делителей (матриц) 𝑅 − 2𝑅, в которых используются резисторы, отличающиеся друг от друга по сопротивлению лишь в два раза. Схема преобразователя кода в напряжение с матрицей 𝑅 − 2𝑅 показана на рис. 11. 4. 71 Рис. 11.4 Схема преобразователя кода в напряжение с матрицей 𝑅 − 2𝑅 Пример выполнения Схема преобразователя кода с параллельным суммированием напряжений с использованием модели ЦАП показана на рис. 11.5. При построении схемы использованы компоненты: генератор слов (ГС), осциллограф (Осц), вольтметр, источники опорного напряжения (VCC и VDD), 8-ми разрядный преобразователь (VDAC), а также индикаторы (LAMP и DCD_HEX). На входе схемы (в генераторе слов) задается последовательность двоичных кодов, которые нужно преобразовать в напряжение. Двоичные сигналы поступают на индикаторы и на входы преобразователя. Вход D0 преобразователя соответствует младшему разряду двоичного кода, а D7 – старшему. Ко входу Vref+ преобразователя подключено опорное напряжение, равное 32V. Преобразователь, в соответствии с принципами, описанными выше (см. Краткие теоритические сведения) формирует на выходе Output напряжение в зависимости от поданных сигналов. Выходное напряжение фиксируется с помощью осциллографа и вольтметра. 72 Рис. 11.5 Схема преобразователя кода в напряжение с использованием модели ЦАП Осциллограмма, отражающая работу преобразователя (рис. 11.5), показана на рис. 11.6. По оси X показывается время входного двоичного сигнала, по оси Y – величина выходного напряжения U. Рис. 11.6. Осциллограмма Представим результаты работы схемы в виде табл. 11.1, содержащей входные коды и соответствующие им выходные напряжения. Построим график зависимости выходного напряжения от входного кода (рис. 11.7). 73 Таблица 11.1- Результаты работы схемы Десятеричное число Двоичный код Напряжение, V 0 00000000 0,000 2 00000010 0,250 4 00000100 0,500 8 00001000 1,000 16 00010000 2,000 18 00010010 2,250 20 00010100 2,500 22 00010110 2,750 32 00100000 4,000 24 00011000 3,000 48 00110000 6,000 16 00010000 2,000 Напряжение, V 7 6 5 4 3 2 1 0 0 10 20 30 40 50 Код Рис 11.7 График зависимости выходного напряжения от входного кода Для оценки полученных экспериментальных данных нужно сравнить их с расчетными данными. Для этого нужно рассчитать эталонное напряжение по формуле: 𝑈 𝑈0 = 𝑟𝑒𝑓 , где 𝑈𝑟𝑒𝑓 – это опорное напряжение, а К – максимальное количество кодовых 𝐾 комбинаций, которые могут быть поданы на вход преобразователя. Например: для 8-ми разрядного преобразователя с опорным напряжением равным 32V эталонное 32𝑉 напряжение будет равно: 𝑈0 = 28 = 0,125𝑉. 74 Варианты заданий № варианта Опорное Двоичный код напряжение, V 1 174 30, 72, 5, 47, 126, 101, 6, 71, 21, 84 2 168 51, 97, 6, 39, 42, 98, 0, 55, 102, 9 3 160 103, 62, 14, 24, 29, 83, 80, 71, 38, 86 4 152 99, 96, 3, 28, 103, 74, 58, 3, 89, 67 5 144 119, 14, 95, 112, 82, 117, 110, 59, 96, 87 6 136 104, 106, 104, 74, 95, 94, 58, 107, 17, 43 7 128 20, 61, 32, 62, 111, 82, 94, 104, 63, 95 8 120 40, 123, 93, 34, 17, 89, 94, 29, 69, 39 9 112 100, 21, 102, 77, 109, 119, 118, 55, 59, 8 10 104 16, 77, 112, 46, 47, 57, 108, 32, 0, 5 11 96 22, 5, 122, 1, 47, 107, 13, 70, 57, 6 12 88 126, 28, 37, 105, 70, 126, 86, 82, 80, 118 13 80 90, 38, 45, 55, 78, 89, 10, 46, 114, 86 14 72 107, 61, 29, 69, 16, 95, 26, 101, 30, 1 15 64 105, 48, 125, 52, 8, 115, 40, 7, 103, 48 16 56 98, 26, 79, 8, 36, 111, 87, 67, 49, 84 17 48 96, 93, 82, 98, 25, 64, 126, 94, 88, 102 18 40 100, 112, 51, 78, 13, 42, 40, 119, 46, 90 19 32 48, 3, 70, 66, 115, 81, 109, 20, 33, 32 20 24 7, 85, 51, 72, 31, 11, 92, 26, 27, 70 21 16 87, 20, 31, 10, 85, 12, 15, 64, 13, 5 Контрольные вопросы 1. 2. 3. 4. 5. 6. Как классифицируются ЦАП по принципу действия? Оцените шаг квантования у весовых преобразователей. Какая характеристика определяет быстродействие преобразователя? Как получают метрологические характеристики преобразователя? Какой недостаток имеют схемы, изображенные на рис. 2, рис 3.? Как оценить точность преобразователя? Содержание отчета 1. Наименование работы. 2. Цель работы. 3. Краткие теоретические сведения. 75 4. 5. 6. 7. 8. Вариант задания. Пример выполнения схемы преобразователя. Диаграммы. Анализ полученных результатов и выводы. Подпись исполнителя. Литература 1. Шестеркин А.Н. Система моделирования и исследования радиоэлектронных устройств Multisim 10. Издательство “ДМК”. Москва 2012г 76