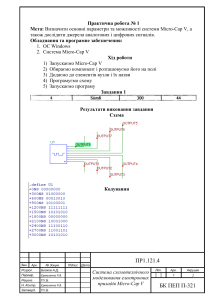

1. Електричні сигнали та їхнє представлення Для передачі інформації від джерела до приймача повідомлення перетворюють у сигнали. Відповідно до ДСТУ 2938-84 „ сигнал – це зміна фізичної величини, що використовується для пересилання даних”. Таким чином, сигнал утворюється на основі деякої фізичної величини (електромагнітні або акустичні коливання, електрична напруга та ін.), яку традиційно називають енергетичним носієм, і зміни одного або декількох її параметрів (амплітуди, частоти, фази та ін.) за законом переданої інформації. За допомогою сукупності сигналів можна подати будь-яке повідомлення. Зміна параметрів фізичної величини за законом переданого повідомлення називається модуляцією , а змінювані параметри – інформативними. Сигнали класифікують за такими ознаками: - ступенем визначеності очікуваних значень – випадкові і детерміновані; - структурою часової зміни – неперервні і дискретні; - роллю переданої інформації в комп’ютері – адреси, дані і керування; - способом перетворення - кодовані, декодовані, дискретизовані та ін.; - приналежністюдо виду зв’язку – телеграфні, телефонні, радіолокаційні, міжмашинні та внутрішньомашинні; - характером зміни кодованих сигналів у синхронізовані моменти часу – потенціальні та імпульсні. У процесі передачі сигналів від джерела до приймача фізичні величини і засоби їхньої модуляції можуть багаторазово змінюватися, але зміст повідомлення залишається незмінним, оскільки воно визначається тільки за законом модуляції. Найбільш поширеними способами представлення сигналів є часовий, спектральний, статистичний. У багатьох випадках інформація щодо протікання деякого фізичного процесу надходить від відповідних давачів у вигляді електричних сигналів, змінюються у часі. Розрізняють такі різновиди сигналів, що описуються часовою функцією f(t): - неперервна функція неперервного аргументу; - дискретна функція неперервного аргументу; - неперервна функція дискретного аргументу. Перетворення функції f(t) неперервного аргументу t в функцію f(t) дискретного аргументу t називається дискретизацією (квантуванням) у часі; - дискретна функція дискретного аргументу. Перший з розглянутих різновидів описує неперервні (аналогові) сигнали, другий і третій – дискретно-неперервні, а четвертий – чисто дискретні. 2. Види сигналів в комп’ютерній схемотехніці У комп'ютерній схемотехніці застосовуються два основних види двійкових сигналів: потенціальні й імпульсні (рисунок 1.2). Сигнал, який змінюється тільки в тактові моменти часу, називається потенціальним. Сигнал, що наростає в тактовий момент, а спадає в границях даного такту, називається імпульсним. Тривалість потенціального сигналу дорівнює або кратна тривалості машинного такту. Рисунок 1.2 - Діаграми потенціальних (ПС) та імпульсних (ІС) сигналів У логіці значення двійкового сигналу і відповідної змінної Х кодуються символами 0 (лог. 0) і 1 (лог. 1). Напругу, що відображає символ 1, позначимо через U1, а символ 0 – через U0. Розрізняють два способи кодування логічних сигналів Хі потенціальними сигналами – позитивний та негативний. При позитивному кодуванні (позитивна логіка чи угода) більший рівень напруги UН з урахуванням знака відображає лог. 1, а менший UL – лог.0, тобто Х = 1, якщо U1 = UH, та Х = 0 при U0=UL (рисунок 1.3, а). При негативному кодуванні (негативна логіка чи угода) більший рівень напруги UH з урахуванням знаку відображає лог. 0, а менший UL – лог. 1, тобто Х = 1, якщо U1 = UL, та Х = 0 при U0 = UH (рисунок 1.3, б). Рисунок 1.3 - Логічні угоди: а – позитивна X+; б – негативна X– Для імпульсних сигналів розрізняють два роди кодування: перший – наявність імпульсу відображає лог. 1, відсутність – лог. 0; другий – наявність імпульсу однієї полярності відображає лог. 1, а іншої полярності – лог. 0. Рисунок 1.4 - Імпульсне кодування: а – першого роду; б – другого роду 3. Електричні параметри сигналів цифрових мікросхем Логічні, схемотехнічні й експлуатаційні властивості логічних елементів визначаються сукупністю характеристик і параметрів, до яких відносяться: функції логічних елементів; логічні угоди; коефіцієнти об'єднання за входом і виходом; коефіцієнт розгалуження; швидкодія; потужність споживання; робота перемикання; вхідні й вихідні напруги і струми; статична і динамічна стійкість до завад; надійність елементів; допустимі розміри механічних впливів, діапазони тиску і температури навколишнього середовища, стійкість до радіаційних впливів; маса, вартість і конструктивне оформлення. У більшості випадків зазначені характеристики і параметри відносяться і до інтегрованих мікросхем, на яких реалізовані логічні елементи. Прийняті такі визначення і буквенні позначення електричних параметрів цифрових мікросхем (ДСТУ 2883-94): - вхідні UI і вихідні UO рівні напруг (індекси – від англійських слів Input і Output); - вхідні напруги низького UIL і високого UIH рівнів; для них установлюються максимальне значення низького рівня UIL max та мінімальне значення високого рівня UIH min (рисунок 1.5, а); - вихідні напруги низького UOL і високого UOH рівнів; для них установлені максимальне значення низького рівня UОL max та мінімальне значення високого рівня UОH min (рисунок 1.5, б); - вхідний II і вихідний IO струми; - вхідний струм IIL – при низькому рівні напруги на вході, IIH – при високому; - вихідний струм IOL – при низькому рівні напруги на виході, а IOH – при високому; - UCC – значення напруги джерела живлення; - IСС – струм, споживаний ІМС від джерела живлення; - PСС – потужність, споживана ІМС від джерела живлення; - вхідні граничні напруги, при яких відбувається перемикання елемента: UTIH – найменше значення для високого рівня і UTIL – найбільше значення для низького рівня. 4. Двійкові змінні і перемикальні функції Для формального опису вузлів комп’ютерів при їх аналізі і синтезі використовується апарат алгебри логіки (алгебри Буля, або булевої алгебри.). В булевій алгебрі розрізняють двійкові змінні і перемикальні функції. Двійкові змінні можуть приймати два значення: лог. 0 і лог.1. Вони називаються також логічними або булевими змінними і позначаються символами x1, x2, …, xn. Перемикальні функції (ПФ) залежать від від двійкових і вони як і аргументи можуть приймати лише два значення: лог. 0 і лог. 1. Перемикальні функції називають також логічними або булевими функціями. Позначаються, як правило, ПФ в вигляді f(x1, x2, …, xn), або у вигляді y1, y2, …, чи F1, F2, … , Fn . ПФ в свою чергу можуть слугувати аргументами ще більш складних логічних функцій. Відповідно, можна побудувати ПФ любої складності, використовуючи обмежене число логічних зв’язків. ПФ прийнято задавати таблицями істиності, в котрих для всіх наборів змінних вказуються відповідні їм значення ПФ, або у вигляді логічних формул. Формування значень ПФ в таблиці істиності виконується у відповідності з логікою роботи пристрою (суматора, шифратора чи дешифратора, перетворювача кодів та ін.). Набір змінних – це сукупність значень двійкових змінних, кожна з яких для всіх наборів, може бути рівною лог.0 або лог.1. Якщо число аргументів (незалежних змінних) ПФ рівне n (тобто x1, x2, … , xn), то існує 2n наборів. 5. Елементарні логічні функції Логічне заперечення (функція НЕ).Логічним запереченням змінної x називається така ПФ f1(x) , котра має значення 1, коли x = 0 і значення 0, коли x = 1. ПФ НЕ позначається у вигляді f1 = x‾‾ і читається « f1 є (еквівалентно) не x ». Функію НЕ виконує фізичний елемент ( електронна схема ), яка називається інвертором. Позначення інвертора на електричних принципових 1 схемах показано на рисунку Логічне множення (кон’юнкція).(І) Кон’юнкція двох (і більше) змінних x1 і x2 приймає значення 1 тільки на наборі, на котрому всі змінні мають значення 1. На інших наборах дана функція має значення 0. Таблиця істиності кон’юнкції двох змінних х1 і х2 . ПФ кон’юнкції поначається в вигляді f2 = x1x2 і читається: « f2 є (еквівалентно) х1 і х2 . x1 x x1 2 2 0 0 1 1 0 1 0 1 & f2 = x1x2 x2 Для позначення ^ або &. Логічне додавання ( диз’юнкція) (АБО.). Диз’юнкція двох (або іншого числа) змінних x1 і x2 має значення 0 тільки на наборі, в якому всі змінні мають значення 0. Якщо хоча одна із змінних рівна 1,то функція буде мати значення 1. ПФ диз’юнкція записується у вигляді x x f f3 = x1 V x2 і читається : « f3 є (еквівалентно) 1 2 3 х1 або х2 . Крім символа V застосовується 0 0 0 x f x x 1 x 0 1 1 символ + . 1 0 1 1 1 1 Електронні логічні функції НЕ, І, АБО є основними логічними функціями. Заперечення кон’юнкції (операція І-НЕ). Дана x x f функція утворюється шляхом заперечення результату , 1 2 4 отриманого при виконанні операції І. 0 0 1 ПФ І-НЕ записується у вигляді f4 = x1x2 .Число 0 1 1 входів елементу І-НЕ визначається числом 1 0 1 аргументів 1 1 0 1 3= 1V 2 2 x1 & f4 = x1x2 x2 функції І-НЕ. Заперечення диз’юнкції (операція АБО-НЕ). Ця операція утворюється шляхом заберечення результату, отриманого при виконанні операції АБО. ПФ АБО-НЕ записується у вигляді f5 = x1 V x2 . Число входів елементу АБО-НЕ x 1 x 2 0 0 1 1 f 5 0 1 0 1 f 1 0 0 0 0 0 0 1 x1 1 f5 = x1 V x2 x2 визначається числом аргументів функції АБО-НЕ. Виключаюче АБО (операція НЕРІВНОЗНАЧНІСТЬ або ДОДАВАННЯ ПО МОДУЛЮ ДВА). Дана функція має значення 1 на тих наборах змінних, на яких число одиниць непарне. f 6 = x1 x2 . Символ М2 в полі елементу означає « додавання x1 M2 x 1 x 2 0 0 1 1 f 6 0 1 0 1 0 1 1 0 f6 x2 по модулю два». _ _ f6 = x1x2 + x1x2 . Операція ВИКЛЮЧАЮЧЕ АБО-НЕ (РІВНОЗНАЧНІСТЬ). РІВНОЗНАЧНІСТЬ представляє собою заперечення x операції ВИКЛЮЧАЮЧЕ АБО. Дана операція 1 2 має 0 значення 1 на тих наборах змінних, які містять 0 парне 1 число одиниць. Для двох змінних операція 1 ВИКЛЮЧАЮЧЕ АБО-НЕ представлена таблицею істинності ______ f 7 = x1 x2 . _ _ f7 = x1x2 + x1x2 . x1 x2 M2 f7 Функція x f 7 0 1 0 1 1 0 0 1 6. Закони алгебри логіки У алгебрі логіки (булевій алгебрі) використовуються чотири основні закони: переміщувальний, сполучний, розподільний, інверсії. Дані закони дозволяють проводити еквівалентні перетворення ПФ, які записані за допомогою операцій І, АБО, НЕ, тобто приводити вирази ПФ до зручного вигляду. Переміщувальний закон аналогічний переміщувальному закону звичайної алгебри і записується у вигляді а) для диз’юнкції х1 + х2 = х2 + х1 ; б) для кон’юнкції х1х2 = х2х1 Таким чином, від зміни місць доданків (співмножників) їх логічна сума (логічний добуток) на змінюється. Сполучний закон також аналогічний сполучному закону звичайної алгебри і записується у вигляді: а) для диз’юнкції х1 + (х2 + х3) = (х1 + х2) + х3 б) для кон’юнкції х1(х2х3) = (х1х2)х Відповідно, можна групувати змінні, які об’єднані знаками диз’юнкції чи кон’юнкції. Розподільний закон записується у вигляді: а) для диз’юнкції х1 + х2 х3 = (х1 + х2) (х1 + х3тобто диз’юнкція змінної і кон’юнкція рівносильні кон’юнкції диз’юнкцій цієї змінної із співмножниками; б) для кон’юнкції х1 (х2 + х3) = х1 х2 + х1 х3 , тобто кон’юнкція змінної і диз’юнкція еквівалентна диз’юнкції кон’юнкцій даної змінної з доданками. Закон інверсії: а) для диз’юнкції _____ _ _ х1 + х2 = х1 х2 тобто заперечення диз’юнкції логічних змінних аквівалентно кон’юнкції заперечень цих змінних; б) для кон’юнкції ____ _ _ х1 х2 = х1 + х2 тобто, заперечення кон’юнкції змінних еквівалентно диз’юнкції заперечень даних змінних. Правила:1. Вирази, які завжди мають значення 1: х + 1 = 1; _ х + х = 1. 2. Вирази, які завжди мають значення 0: х & 0 = 0; _ x & x = 0. 3. Подвійне заперечення : x = х . 4. Повторення: х&x&…&x= x; х+х+…+х=х. 5. Склеювання : _ х1х2 + х1х2 = х1 . 6. Поглинання : х1 + х1х2 = х1 . 7. Мінімізація перемикальних функцій Перемикальні функції можуть бути виражені різними логічними формулами завдяки можливості проведення над ними еквівалентних перетворень. Однак на практиці найбільш зручними для представлення ПФ є диз’юнктивні і кон’юнктивні форми. Серед диз’юнктивних форм представлення ПФ розрізняють диз’юнктивну нормальну форму (ДНФ) і досконалу диз’юнктивну нормальну форму (ДДНФ). В основі представлення ПФ в диз’юнктивних формах лежить поняття елементарної кон’юнкції. Диз’юнктивною нормальною формою (ДНФ) перемикальної функції називається диз’юнкція (логічна сума) любого числа елементарних кон’юнкцій. Досконалою диз’юнктивною нормальною формою (ДДНФ) перемикальної функції, яка має n аргументів, називається така форма, в якій всі кон’юнкції мають ранг n . Мінімізація, або скорочення виразу, для ПФ необхідна з метою забезпечення мінімуму затрат обладнання при побудові функціональної схеми в заданому базисі (наборі) логічних елементів. Найчастіше використовується набір І, АБО, НЕ, а мінімізація ПФ ведеться в ДНФ. Мінімізацією ПФ (булевої функції) називається процес одержання її мінімімальної форми. Для мінімізації ПФ використовують два основних методи: а) метод Квайна; б) метод діаграм Вейча ( карт Карно ). Метод Квайна застосовується до ПФ, котрі задані в ДДНФ (можливе задання в КДНФ), і проводиться в два етапи. Метод грунтується на застосуванні співвідношень склеювання і поглинання. x1 x2 x1 x2 x1 x1 x1 x2 x1 ( x1 x2 )( x1 x2 ) x1 ( x1 x2 ) x1 x1 На першому етапі здійснюється перехід від ДДНФ до скороченої ДНФ шляхом проведення всіх можливих склеювань однієї з одною спочатку кон’юнкцій рангу n, потім рангу n-1, далі n-2 і т.д. Кожен раз в групі кон’юнкцій рангу r (1 r n) знаходяться пари кон’юнкцій виду Ax i A x , де А – спільна частина даних кон”юнкцій. Дані кон’юнкції склеюються між собою по змінній х . При цьому отримується кон’юнкція A рангу r-1, а кон’юнкції Ax i A x відмічаються і порівнюються також з всіма іншими кон’юнкціями рангу r з метою виконання операції склеювання. Результатом виконання послідовності попарного порівняння і склеювання кон’юнкцій рангу r є група кон’юнкцій рангу r-1 і невідмічені кон’юнкції рангу r. Невідмічені кон’юнкції рангу r не брали участі в склеюванні , значить є простими імплікантами і включаються в скорочену ДНФ. Кон’юнкції рангу r-1 знову попарно порівнюються і склеюються ; в результаті маємо групу кон’юнкцій рангу r-2 і невідмічені кон’юнкції рангу r-1, котрі є простими імплікантами, що включаються далі в скорочену ДНФ. Перший етап закінчується тоді, коли отримана група кон’юнкцій не містить членів, котрі склеюються, тобто містить тільки прості імпліканти. Після цього записується скорочена ДНФ ПФ, в яку включаються всі отримані прості імпліканти. Другий етап заключається в переході від скороченої ДНФ до тупікових ДНФ і виборі серед них МДНФ. Тупіковою називається така ДНФ, серед простих імплікант котрої немає ні однієї зайвої. При цьому під зайвою розуміється така проста імпліканта, видалення котрої не впливає на значення істиності даної функції. Для виявлення зайвих простих імплікант будується імплікантна матриця, котра називається також матрицею (таблицею) покриттів. Кожна стрічка імплікантної матриці відповідає одній простій імпліканті, а стовпці- конституентам одиниці, котрими вони і помічаються. Знаходження тупікових ДНФ за імплікантною матрицею починається з розмітки матриці. При цьому кожна імпліканта порівнюється з усіма конституентами одиниці. Якщо імпліканта є власною частиною деякої конституенти, то в пересіченні лінійки і стовпця ставиться умовний знак, наприклад *. Конституенти одиниці, котрі відмічені в лінійці з простою імплікантою, поглинаються (покриваються) цією простою імплікантою. Це значить, що на відповідних наборах дана імпліканта забезпечує одиничне значення ПФ. Виявлення лишніх (зайвих) простих імплікант виконується наступним чином. В імплікантній таблиці умовно викреслюється стрічка (лінійка) з простою імплікантою, що перевіряється, разом з відповідними помітками в стрічці (лінійці). Якщо при цьому виявиться, що в кожному стовпці імплікантної таблиці залишиться хоча б по одній помітці, то імпліканта, котра перевіряється, є зайвою, і її слід видалити. Прості імпліканти, котрі залишилися, покривають всі одиничні значення ПФ. Випробування кожної послідуючої простої імпліканти можливе лише після видалення вже виявлених лишніх простих імплікант. Метод діаграм Вейча (карт Карно) зручний для мінімізації ПФ, котрі, як правило, мають не більше чотирьох змінних. Діаграма Вейча має вигляд прямокутника (квадрата), який розбитий n на 2 кліток, де n – число аргументів ПФ . Кожній клітці діаграми ставиться у відповідність певна кон’юнкція, причому кон’юнкції розміщують таким чином, щоб в сусідніх клітках (стрічці чи стовпці) вони відрізнялися не більше ніж значенням однієї змінної. В результаті любі дві сусідні, в стрічці чи стовпці ,кон’юнкції склеюються по відповідній змінній. Сусідніми на діаграмі є також крайні (ліва і права) кон’юнкції в одній стрічці і (нижня і верхня) кон’юнкції в одному стовпці. Для мінімізації ПФ приводиться до ДДНФ, після чого заповнюється діаграма Вейча для n змінних. При цьому в відповідну клітинку діаграми вписується 1, якщо ПФ на даному наборі аргументів дорівнює одиниці. У всі інші клітинки вписуються нулі або вони залишаються пустими. 8. Характеристики і параметри інтегрованих систем елементів За видом сигналу залежно від способів кодування двійкових змінних цифрові ІМС поділяються на імпульсні, потенціальні і імпульсно-потенціальні. Зі всіх цифрових ІМС найбільш поширені потенціальні мікросхеми Основні параметри цифрових ІМС визначають допустимі поєднання схем в пристрої і в узагальненому виді характеризують працездатність даних схем в складних пристроях. Основні параметри, число котрих однакове для всіх типів мікросхем, визначають за виміряними електричними параметрами число яких залежить від типу мікросхеми. До основних параметрів відносяться: навантажувальна здатність - коефіцієнт розгалуження по виходу n; коефіцієнт обєднання по входу m; середній час затримки і передачі сигналу tз.ср ; статична завадостійкість Uз ; споживана потужність Pср ; гранична робоча частота fгр. Навантажувальна здатність характеризує максимальне число мікросхем, котрі можна котрі можна одночасно підключити до її виходу без спотворення передавання інформації. Часто навантажувальну здатність називають коефіцієнтом розгалуження по виходу і виражають цілим числом n. Коефіцієнт об’єднання по входу m характеризує максимальне число логічних входів функціонального елементу мікросхеми. Із збільшенням коефіцієнту m розширюються логічні можливості мікросхеми за рахунок виконання функцій з великим числом елементів на одному типовому елементі І-НЕ , АБО-НЕ і ін. Середній час затримки сигналу t з.ср є найбільш розповсюдженим параметром, який характеризує швидкодію логічних ІМС. Він визначає середній час проходження сигналу через одну мікросхему у пристрої. Якщо ланцюг проходження сигналу складається з N послідовно включених однотипних логічних ІМС (N-парне число),час проходження сигналу по ланцюгу TN=(N/2)tз++(N/2)tз-, де tз+ і tз-- часи затримки вкл.. і виключення. Статична завадостійкість характеризує максимально допустиму напругу статичної завади, яка діє на дану мікросхему з одного із зовнішніх джерел. При цьому зберігається роботоздатність мікросхеми в пристрої . Споживана потужність. Споживана схемою потужність в любий момент часу не є постійною, а залежить від логічного стану і типу логічного елементу схеми і змінюється при переключенні схеми. Тому в якості основного параметру використовують не миттєве, а середнє значення потужності, яку споживає мікросхема за достатньо великий проміжок часу: Pср = (P0 + P1)/2, де Р0 і Р1 – потужності, які споживає схема в стані “Вкл” і “Викл” відповідно. За споживаною потужністю цифрові ІМС поділяються на: потужні (25 < Pср < 250 мВт); середньої потужності (3 < Pср < 25 мВт); малопотужні (0,3 < Pср < 3 мВт); мікропотужні (1 < Pср < 300 мкВт); нановатні ( Pср < 1 мкВт). Цифрові ІМС, котрі споживають велику потужність, характеризуються найбільшою швидкодією і застосовуються при створенні обчислювальних пристроїв з високою швидкістю опрацювання інформації. Для обчислювальних пристроїв, в яких швидкодія не є визначальним параметром, використовують малопотужні і мікропотужні схеми. 9. Система умовних позначень інтегрованих мікросхем Згідно ГОСТ 2.743-82 умовне графічне позначення (УГП) елементу цифрової техніки має форму прямокутника, до котрого підводяться лінії виводів. Позначення елементу може вміщувати три поля: основне і два додаткових (при необхідності), котрі розміщені зліва і справа від основного поля. Додаткове поле може бути розділене на зони. У верхній стрічці основного поля розміщено позначення функції елементу , в додаткових полях 1- інформація про функціональне призначення виводів. Умовне позначення цифрової інтегральної схеми (ІС), яке наноситься на корпус мікросхеми складається із чотирьох елементів. Перший елемент - цифра, яка вказує на технологічні особливості виготовлення ІС. Напівпровідниковим ІС відповідають цифри 1,5,6,7 (без корпусна ІС). Гібридним ІС- цифри 2.4,8. Другий елемент- дві чи три цифри, котрі присвоєні даній серії ІС. Разом з першим другий елемент утворює номер серії. Третій елемент- дві букви, які визначають функціональне призначення і різновид ІС в даній функціональній підгрупі. Четвертий елемент- порядковий номер розробки ІС в даній серії. Букви К, КМ (керамічний, металокерамічний корпус), КР(пластмасовий корпус) перед умовним позначенням мікросхем характеризують умови прийоми на заводі-виробнику і особливості конструктивного виконання. Наприклад, запис КР1533ЛА3 означає, що маємо мікросхему широкого застосування (К), в пластмасовому корпусі (Р), напівпровідникову (1), серії 533. яка виконує функцію логічного елементу І-НЕ. 10. Базові логічні елементи Розробка кожної серії ІМС починається з базового логічного елемента (БЛЕ)-основи всіх її вузлів. Як правило, базовий логічний елемент реалізує логічні операції І-НЕ або АБО-НЕ , тому що вони володіють перевагами мінімального функціонально повного базису. Принцип будови, виконувана операція, спосіб керування, напруга живлення, споживана потужність, завадостійкість, швидкодія та інші параметри БЛЕ є визначальними для всіх ІМС даної серії. З БЛЕ можна спроектувати пристрої, які здатні для реалізації як завгодно складних логічних функцій. Існує велика кількість БЛЕ, які відрізняються типами схемотехнічних рішень, конструкцією і технологією виготовлення та іншими показниками. На сьогодні спостерігається найбільш інтенсивний розвиток серій ІМС, побудованих на основі БЛЕ діодно-транзисторної логіки, емітерно-зв’язної, інтегрально-інжекційної і МОН-транзисторної логіки. Схеми діоднотранзисторної логіки (ДТЛ) складаються з діодів і біполярних транзисторів. Він виконує операцію І-НЕ. +Eо +Eк Rк Rо VT VD1 Y= X1X2X3 X1 VD2 VDзм1 VDзм2 X2 R VD3 X3 Вхід розширювача Найпростіша схема ДТЛ-елемента Найбільш широко, на сьогоднішній день, застосовуються в цифровій техніці схеми ТТЛ. Це пояснюється тим, що мікросхеми ТТЛ володіють високою швидкодією і малою споживаною потужністю. Різновидністю схем ТТЛ є схеми ТТЛ з діодами Шоткі (ТТЛШ).В схемах ТТЛ у вхідних каскадах використовуються багатоемітерні транзистори. Uж R1 R2 R3 VT1 VT3 X1 VT2 X2 VD3 Вихід R4 VD1 VD2 VT4 За принципом побудови, а також за найважливішими параметрами вони близькі до схем ДТЛ. Емітерні переходи багатоемітерного транзистора виконують функцію, аналогічну функції діодів в схемах ДТЛ, а колекторний перехід відіграє роль діода зміщення. Багатоемітерний транзистор – специфічний інтегральний напівпровідниковий прилад, який представляє собою сукупність транзисторних структур, що мають загальний колектор і безпосередньо взаємодіють один з одним за рахунок руху основних носіїв заряду. Для підвищення завадостійкості і навантажувальної здатності використовуються ТТЛ - логічні схеми з складним інвертором. Логічні схеми, що працюють в активній зоні між областями насичення і відсічення, називаються схемами з емітерними зв'язками або ЕЗЛ-схемами. Вона складається з диференціального підсилювача, ланцюга зміщення і емітерного повторювача на виході. Така робота схеми відповідає операції АБО. Якщо на виході схеми стоїть додатковий емітерний повторювач і його база зв'язана з колектором VT2, то схема реалізує операцію АБО-НЕ. З цієї причини типовими схемами ЕЗЛ зазвичай вважають схеми АБО і АБО-НЕ. Диференціальний підсилювач Ланцюг зміщення Эмітерний повторювач Uk VT4 VT2 X2 X1 VT1 VT3 Вихід Ue Схеми комплементарної логіки — це KМОН-схеми, що характеризуються низькою споживаною потужністю і високою завадостійкістю. Логічні схеми цього типу виготовляють на базі n – і p-канальных МОН-транзисторів. МОН-транзистори мають структуру металдіелектрик-напівпровідник і в загальному випадку називаються МДНтранзисторами. Таким чином, дана схема працює як схема І-НЕ. Якщо в цій схемі поміняти місцями р - і n - канальні транзистори, то схема виконуватиме функцію АБО-НЕ. Отже, стандартна КМОН-схема – це або схема І-НЕ, або схема АБО-НЕ. Uc VT1 X1 X2 VT2 VT3 AB VT4 Інтегральні схеми виконані по КМОН-технології менш критичні до напруги живлення. Напруга живлення для деяких мікросхем може коливатися в діапазоні від 3 до 15 вольт. Промисловістю випускаються такі серії КМОН: К176, К564, К561, КР1561 і КР1554. Мікросхеми швидкодіючої серії КР1554 мають функціональну і технічну повноту і вміщують логічні елементи, тригери, регістри, лічильники, суматори, дешифратори, шифратори, мультиплексори, та ін. Характеристика і класифікація цифрових запам’ятовуючих елементів Тригером називають пристрій, побудований на логічних елементах, який має два стійкі стани. Тригерний пристрій (тригер) складається з бістабільної схеми, яку часто називають запамятовувальним елементом (ЗЕ) , та схеми керування. Зворотні звязки, показані пунктиром, можуть бути 11. відсутні. Стан тригера визначається сигналами на прямому Q та інверсному виходах. При позитивному кодуванні інформації високий рівень напруги на прямому виході відображає значення лог. 1 (стан Q=1), а низький рівень – значення лог. 0 (стан Q = 0). Тригери класифікують за такими ознаками: - логікою функціонування (RS, JK, D, T та ін.); - способом записування інформації (асинхронні й синхронні); - моментом реакції на тактовий сигнал (статичні, динамічні); - кількістю тактів синхронізації (одно-, дво- і тритактові); - кількістю ступенів (одно- або двоступеневі тригери); - складом логічних елементів (І-НЕ, АБО-НЕ ,І-АБО-НЕ та ін.). Відповідно до логіки функціонування розрізняють наступні тригери: - з роздільною установкою станів “0” і “1” (RS-тригери); - з одним інформаційним входом (D-тригери); - з лічильним входом (T-тригери); - універсальні з роздільною установкою станів “0” і “1” (JK-тригери); - комбіновані (RST-, RSJK-тригери); - із складною вхідною логікою. За способом записування (приймання) інформації розрізняють асинхронні й синхронні (тактовні) тригери. Тригери, які не мають С-входу, називаються асинхронними. В асинхронних тригерах записування інформації відбувається в будь-який момент часу при надходженні сигналів до інформаційних входів. Тригери, які мають С-вхід, називаються синхронними. У синхронному тригері записування інформації можливе при збігу сигналів на інформаційному й синхронному входах. Цим пояснюється вища стійкість до завад синхронних тригерів порівняно з асинхронними. Залежно від кількості тактових сигналів, необхідних для формування нового стану, розрізняють однотактові, двотактові та багатотактові тригери. За способом керування записуванням (моментом реакції на тактовий сигнал) виділяють синхронні тригери зі статичним (за рівнем), динамічним (за фронтами) та двоступеневим керуванням. 12. Асинхронні та синхронні RS-тригери RS-тригером називають запам'ятовуючий елемент з роздільними інформаційними входами для установлення його в стан “0” (Rвхід) і в стан “1” (S-вхід). Назва “RS-тригер” утворена від перших літер слів RЕSЕТ (скидання) і SЕТ (установлення) Асинхронний RS-тригер на елементах І-НЕ. Особливістю цього тригера є інверсне керування за інформаційними входами, що відображається в умовному графічному позначенні. Із аналізу діаграм роботи RS-тригера випливає, що елементи І-НЕ в схемі перемикаються послідовно. Є інтервал часу, коли на обох виходах встановлюються однакові сигнали Q = 1 і = 1. Тривалість перемикання тригера визначається сумою затримок: tп.т = 2tp. Тривалість вхідного сигналу визначається з умови ti ≥ tп.т. Асинхронний RS-тригер на елементах АБО-НЕ. Із аналізу діаграм роботи RS-тригера випливає, що елементи АБО-НЕ в схемі перемикаються послідовно. Є інтервал часу, коли на обох виходах установлюються однакові сигнали Q = 0 і =0, – явище “ризик. Синхронний RS-тригер на елементах І-НЕ. Схема синхронного RSтригера на чотирьох елементах І-НЕ з логічними зв’язками на основі виразу (4.5) показана на рисунку 5.7, а. Елементи D1 і D2 складають схему керування з прямими входами, а елементи D3 і D4 утворюють фіксатор (асинхронний RSтригер). Із часової діаграми випливає, що час перемикання тригера tп.т = 3tр, а тривалість синхросигналу (з урахуванням запасу на одну затримку) визначається з умови tС = 4tр. Максимальна і робоча частоти перемикання тригера відповідно дорівнюють: fmax = 1/3tp і fp = 1/4tp. Синхронний RS-тригер на елементах АБО-НЕ. При значенні сигналів = 0 і = 0 на виході елемента D2 встановлюється лог. 1 (тобто CS = 1) і тригер переключається в стан “1”. При значенні сигналів = 0 і = 0 на виході елемента D1 встановлюється лог. 1 (тобто CR = 1) і тригер переключається в стан “0”. Комбінація сигналів = = = 0 заборонена, тому що призводить до невизначеного стану тригера. 13.Тригери типу JK Тригером типу JK називається запам'ятовуючий елемент з двома стійкими станами та інформаційними входами J (аналог S) і К (аналог R), які забезпечують відповідно роздільну установку станів “1” і “0”. Він функціонує подібно до RS-тригера, але при збігу сигналів JK = 1 переключається в протилежний стан, тобто реалізує додавання сигналів за модулем два. Таким чином, JK-тригер не має заборонених комбінацій вхідних сигналів. Тригер типу JK є універсальним, оскільки може виконувати функції RS-тригера (при роздільному надходженні сигналів J і К), Т-тригера (при одночасній подачі сигналів J і К), D-тригера (при подачі сигналу від входу J через інвертор на вхід K). У схемотехніці потенціальних тригерів в основному застосовують двоступеневі синхронні JK-тригери на елементах І-НЕ. Нова інформація знімається з виходів Q основного М- ступеня, а стара – з виходів Q* допоміжного S-ступеня. Із часових діаграм слідує: при застосуванні JKтригера для зберігання інформації сигнали на входи J і K подаються почергово; при збігу сигналів на входах J і K реалізується лічильний тригер (на практиці ці входи часто монтажно об'єднуються). Час перемикання JK-тригера визначається сумою затримок першого і другого ступенів. На виході S-ступеня нова інформація з'являється після спаду сигналу C. 14.Тригери затримки (D-тригери) Тригером типу D називається синхронний запам'ятовуючий елемент з двома стійкими станами і одним інформаційним D-входом. Закон функціонування Dтригера описується логічним рівнянням: Qt+1 = CtDt. Дане рівняння показує, що після перемикання стан D - тригера повторює значення сигналу на D - вході в тактові моменти часу. Тому в літературі Dтригери часто називають тригерами затримки (від Delay – затримка). Схему D-тригера можна побудувати на основі синхронного RS-тригера, якщо сигнал по входу S одночасно подавати через інвертор на вхід R. Dтригер “слідкує” за зміною сигналу на D-вході під час дії синхросигналу С і зберігає ту інформацію, яка була в момент його закінчення. RS-тригери такої властивості не мають і тому вони менше завадостійкі порівняно з D-тригерами. Для затримки інформації в D-тригері на довільне число тактів використовується дозволяючий V-вхід. Якщо V = 1, то DV-тригер функціонує як звичайний тригер затримки; якщо V= 0, то робота схеми за входами блокується і DVтригер зберігає попередню інформацію. D-тригер з динамічним керуванням. В усіх синхронних тригерах із статичним керуванням (за рівнем) можливе фальшиве перемикання у випадку зміни сигналів на інформаційних входах під час дії сигналу С. Тому для надійної роботи D-тригера потрібний певний інтервал часу між фронтом синхроімпульсу С і спадом сигналу на D-вході (параметр tвідн). У тригерах з динамічним керуванням записуванням інформації синхроімпульс С активний лише на короткому інтервалі часу в області фронту чи спаду. Тому D-тригери з динамічним керуванням мають високу завадостійкість. На практиці широке розповсюдження отримали D-тригери з прямим динамічним керуванням за схемою “трьох тригерів”. 15.Дешифратори Дешифратором називається функціональний вузол комп’ютера, призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із своїх виходів. У загальному випадку дешифратор має n однофазних входів (іноді 2n парафазних) і m=2n виходів, де n – розрядність (довжина) коду, який дешифрується. Дешифратор з максимально можливим числом виходів m=2n називається повним дешифратором і реалізує 2n функцій. Кожному n – розрядному вхідному слову відповідає одиничний сигнал на одній із вихідних 2n шин і нулі на решті виходів. Система функцій є сукупністю всіх можливих конституент одиниці, які можна утворити від n змінних. Дешифратор являє собою КС з багатьма виходами. Дешифратор це перетворювач двійкового позиційного коду в 2n код. Бувають дешифратори і з інверсними виходами. На виході дешифратора завжди присутній тільки один сигнал, причому номер цього сигналу однозначно визначається вхідним кодом. Вихідний код дешифратора однозначно визначається номером вхідного сигналу. Дешифратори класифікують за такими ознаками: - способом структурної організації – одноступеневі і багатоступеневі - форматом вхідного коду – двійкові, двійково-десяткові; - розрядністю коду, який дешифрується – 2, 3, ..., n; - формою подачі вхідного коду – з однофазними і парафазними входами; - кількістю виходів – повні й неповні дешифратори; - видом вхідних стробуючих сигналів – в прямому або інверсному значеннях; - типом використовуваних логічних елементів – І, НЕ, АБО, І-НЕ , АБО-НЕ До основних характеристик дешифратора відносять: число ступенів (каскадів) дешифрації, кількість використаних логічних елементів або мікросхем, загальне число входів логічних елементів, час дешифрації і споживану потужність. У стандартні серії ІМС входять дешифратори на 4 виходи (2 розряди вхідного коду), на 8 виходів (3 розряди вхідного коду) і на 16 виходів (4 розряди вхідного коду). В комп’ютерах дешифратори використовують для виконання таких перацій: - дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір потрібної мікропрограми; - перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам’яті в процесі записування або читання інформації; - забезпечення візуалізації на зовнішніх пристроях; - реалізації логічних операцій та побудови мультиплексорів і демультиплексорів. Використання дешифраторів для дешифрації коду операції і адреси операнда, розташованих в регістрі команд процесора, показано на рисунку 5.3. Дешифрація коду операції в пристрої керування (ПК) визначає тип машинної команди. Дешифрація адреси операнда в оперативній пам’яті (ОП) забезпечує доступ до вказаної комірки пам’яті для записуван-ня або зчитування даних. 16.Шифратори Шифратором називається функціональний вузол комп’ютера, призначений для перетворення вхідного m-розрядного унітарного коду у вихідний n-розрядний двійковий позиційний код. Двійкові шифратори виконують функцію, обернену функції дешифратора. При активізації однієї з вхідних ліній дешифратора на його виходах формується код, який відображає номер активного входу. Повний двійковий шифратор має m=2n входів і n виходів. Умовні графічні позначення шифраторів на схемах показані на рисунку 5.9. Функція шифратора позначається буквами CD (coder). Входи шифратора нумеруються послідовними десятковими цифрами 0, 1, ..., m–1, а позначки виходів відображають ваги вихідних двійкових змінних 1, ..., 2 . Шифратори використовуються набагато рідше, ніж дешифратори. Наявність у шифраторів входів EI і EO дозволяє збільшувати кількість входів і розрядів шифратора, правда, за допомогою додаткових елементів на виході. На рисунку 5.11 показаний приклад побудови шифратора 16–4 на двох мікросхемах шифраторів ИВ1 і трьох елементах 2І-НЕ (ЛА3). Одночасна або майже одночасна зміна сигналів на вході шифратора приводить до появи періодів невизначеності на виходах. Вихідний код може на короткий час приймати значення, не відповідне жодному з вхідних сигналів. Тому в тих випадках, коли вхідні сигнали можуть приходити одночасно, необхідна синхронізація вихідного коду, наприклад, за допомогою вирішуючого сигналу EI, який повинен приходити тільки тоді, коли стан невизначеності вже закінчився. 17.Мультиплексори Мультиплексором називається функціональний вузол комп'ютера, призначений для почергової комутації (перемикання) інформації від одного з п входів на загальний вихід. Номер конкретної вхідної лінії, що підключається до виходу в кожний такт машинного часу, визначається адресним кодом А0, А1 ,... , Аm-1. Зв'язок між числом інформаційних n і адресних m входів визначається співвідношенням n = 2m. Таким чином, мультиплексор реалізує керовану передачу даних від кількох вхідних ліній в одну вихідну. Мультиплексори застосовують для таких операцій: комутації як окремих ліній, так і груп ліній (шин); перетворення паралельного коду в послідовний; реалізації логічних функцій; побудови схем порівняння, генераторів кодів. Мультиплексор символічно часто позначають: "n-1". При побудові схеми мультиплексорів з внутрішнім лінійним дешифратором потрібні логічні елементи з меншим числом входів, проте при цьому збільшується час встановлення вихідного сигналу. При виключенні дешифратора швидкодія підвищується, однак потрібні схеми збігу з більшим числом входів. В інтегральному виконанні мультиплексори випускають на чотири, вісім або шістнадцять входів. Каскадування дозволяє реалізувати комутацію довільного числа вхідних ліній на базі серійних мікросхем мультиплексорів меншої розрядності. За допомогою мультиплексорів реалізуються логічні функції з числом змінних т, що дорівнює розрядності адресного коду. Функція, що виконується, має бути представлена в ДДНФ. При цьому змінні поступають на адресні входи, а інформаційні входи використовуються як настроювальні — на них подаються константи нуля і одиниці залежно від функції, яка реалізується. Можливі й інші схемотехнічні застосування мультиплексорів. Мультиплексор може виконувати функції перетворювача n-розрядного двійкового паралельного коду в послідовний. Мультиплексування шин — це почергове перемикання шин (груп ліній) від кількох джерел інформації до одного приймача. Такі мікрооперації реалізуються схемами на основі мультиплексорів одиночних ліній. При виборі кількості й типу мультиплексорів враховують: • число комутованих шин дорівнює 2m, де m — довжина адресного коду; • i-й номер входу всіх мультиплексорів служить для підключення розрядів певної однієї шини. 18.Демультиплексори Демультиплексором називається функціональний вузол комп’ютера, призначений для комутації (перемикання) сигналу з одного інформаційного входу D на один з n інформаційних виходів. Номер виходу, на який в кожний такт машинного часу передається значення вхідного сигналу, визначається адресним кодом А0, А1, А2, ..., Аm-1. Адресні входи m та інформаційні виходи n пов’язані співвідношенням n=2m або m = log 2n. Демультиплексор виконує функцію, обернену функції мультиплексора. Стосовно мультиплексорів і демультиплексорів користуються також терміном “селектори” даних. Демультиплексори використовують для таких операцій: - комутації як окремих ліній, так і багаторозрядних шин; - перетворення послідовного коду в паралельний; - реалізації логічних функцій та інших. Схема демультиплексора з поєднанням адресних і вхідних змінних забезпечує високу швидкодію, проте вимагає застосування логічних елементів з більшим числом входів. Каскадування дозволяє реалізувати комутацію одного вхідного сигналу на довільне число вихідних ліній на базі серійних мікросхем меншої розрядності. Демультиплексори не випускають як самостійні вироби на інтегрованих мікросхемах. Функцію демультиплексора звичайно реалізують на дешифраторах, що мають входи стробування (дешифраторидемультиплексори). Під демультиплексуванням шин розуміється почергове перемикання груп ліній від одного джерела інформації до багатьох приймачів. 19.Суматори Суматором називається функціональний вузол комп’ютера, призначений для додавання двох n-розрядних слів (чисел). Операція віднімання заміняється додаванням слів в оберненому або доповняльному коді. Операції множення та ділення зводяться до реалізації багаторазового додавання та зсування. Тому суматор є важливою частиною арифметико-логічного пристрою. Функція суматора позначається буквами SM або Σ. Суматор складається з окремих схем, які називаються однорозрядними суматорами; вони виконують усі дії з додавання значень однойменних розрядів двох чисел (операндів). Суматори класифікуються за такими ознаками: - способом додавання – паралельні, послідовні та паралельно-послідовні; - числом входів – напівсуматори, однорозрядні та багаторозрядні суматори; - організацією зберігання результату додавання – комбінаційні, накопичувальні, комбіновані; - організацією перенесення між розрядами – з послідовним, наскрізним, паралельним або комбінованим перенесеннями (з груповою структурою); - системою числення – позиційні (двійкові, двійково-десяткові, трійкові) та непозиційні, наприклад, у системі залишкових класів; - розрядністю (довжиною) операндів – 8-, 16-, 32-, 64-розрядні; - способом представлення від’ємних чисел – в оберненому або доповняльному кодах, а також в їхніх модифікаціях; - часом додавання – синхронні, асинхронні. У паралельних n-розрядних суматорах значення всіх розрядів операндів поступають одночасно на відповідні входи однорозрядних підсумовуючих схем. У послідовних суматорах значення розрядів операндів та перенесення, що запам’ятовувалися в минулому такті, поступають послідовно в напрямку від молодших розрядів до старших на входи одного однорозрядного суматора. В паралельно-послідовних суматорах числа розбиваються на частини, наприклад, байти, розряди байтів поступають на входи восьмирозрядного суматора паралельно (одночасно), а самі байти – послідовно, в напрямку від молодших до старших байтів з урахуванням запам’ятованого перенесення. У комбінаційних суматорах результат операції додавання запам’ятовується в регістрі результату. В накопичувальних суматорах процес додавання поєднується із зберіганням результату. Це пояснюється використанням Ттригерів як однорозрядних схем додавання. Організація перенесення практично визначає час виконання операції додавання. Послідовні перенесення схемно створюються просто, але є повільнодіючими. Паралельні перенесення схемно організуються значно складніше, але дають високу швидкодію. 20. Перетворювачі кодів Перетворювачами кодів називаються дискретні пристрої, котрі здійснюють перетворення слів вхідного алфавіту x1,x2,...,xn у слова вихідного алфавіту y1,y2,…ym.В загальному випадку перетворювачі кодів мають n входів і m виходів. Обмеження на співвідношення величин n і m не накладаються. Відповідно до введеного визначення до перетворювачів кодів може бути віднесено множину дискретних пристроїв, які здійснюють перетворення одних простих кодів у інші, простих кодів – у коригуючи і навпаки. На практиці до перетворювачів кодів відносять більш вузький клас пристроїв комбінаційного типу, до яких відносяться пристрої, які перетворюють один конкретний код в інший (наприклад двійково-десятковий в двійковий і навпаки, двійково-десятковий у циклічний тощо). До подібних перетворювачів належать дешифратори і шифратори. Класифікація перетворювачів кодів може бути здійснена за призначенням, принципом дії, принципом побудови. За призначенням розрізняють перетворювачі прямого коду у зворотний, двійкового - в двійково-десятковий, двійкового – в код семи сегментного індикатора та багато інших. За принципом дії можуть бути виділені дві групи перетворювачів кодів: керовані (синхронні) та некеровані (асинхронні). Важливою ознакою класифікації є принцип побудови перетворювачів кодів, згідно з яким їх можна поділити на чотири групи. До першої групи відносяться перетворювачі кодів, котрі синтезуються як звичайні комбінаційні схеми на логічних елементах І, АБО, І-НЕ, І-АБО-НЕ та ін. Другу і третю групу складають перетворювачі кодів, побудовані на основі блокових схем: дешифратор-шифратор, дешифратор-матриця запам’ятовуючого пристрою. Четверту групу складають перетворювачі кодів, які реалізуються на основі програмованих логічних матриць. Візуальне відображення двійково-десяткових чисел часто виконується за допомогою семисегментних індикаторів на основі електролюмінісцентних приладів, рідких кристалів або світлодіодних матриць. Кількість семисегментних індикаторів визначається розрядністю чисел, що відображаються на світловому табло — звичайно шість і більше десяткових цифр. У комп'ютерах широко використовується двійково-десяткове кодування, в якому кожна десяткова цифра зображується чотирирозрядним двійковим кодом, тобто тетрадою двійкових символів. 21. Програмовані логічні матриці Програмовані логічні матриці (ПЛМ) відносяться до ВІС з регулярною структурою з великим ступенем універсальності матричного типу. За внутрішньою структурою ПЛМ поділяються на ПЛМ комбінаційної логіки і ПЛМ з пам’яттю. Основу ПЛМ комбінаційної логіки складають матриці М1 і М2 та вхідний і вихідний буфери Матриця М1 реалізує Н кон’юнкцій від L вхідних змінних І/АБО їх заперечень. Матриця М2 – реалізує N диз’юнкцій від Н термів, які отримані в матриці М1. Вхідний буфер Вх.Б призначений для формування прямих і інверсних значень вхідних змінних, а вихідний Вих.Б – при необхідності дозволяє інвертувати виходи матриці М2. Структуру ПЛМ зручно зображати у вигляді двох взаємодоповнюючих форм – в вигляді системи вертикальних і горизонтальних провідників. В залежності від способу фізичної організації міжз’єднань ПЛМ поділяються на ПЛМ, котрі програмуються в процесі виготовлення і ПЛМ, які програмуються користувачем. Причини використання ПМЛ: 1. Ускладнення програмного забезпечення. 2. Розширення можливостей інтегральної технології різко збільшило інформаційну ємність ПЛМ. 3. Поява ПЛМ, котрі програмуються користувачем , істотно розширила їх область застосування. Кожна ПЛМ характеризується кількістю входів - а, виходів – b і термів с. На даний час у вигляді ВІС випускаються ПЛМ з такими параметрами: число входів –12 ≤ а ≤ 24; число виходів - 12 ≤ b ≤ 24 ;число терм – 48 ≤ с ≤ 96 ; - число елементів пам’яті d ≤ 13. За допомогою ПЛМ можуть бути реалізовані дискретні пристрої будь-якої складності. Однак залежно від співвідношення параметрів а,b,c реальних ПЛМ і параметрів системи логічних функцій I , m, n можливе виникнення таких ситуацій, які визначають особливості методики побудови і особливо синтезу даних пристроїв на ПЛМ. 22. Класифікація регістрів Регістр- функціональний вузол комп'ютера, призначений для приймання, тимчасового зберігання, перетворення і видачі n-розрядного двійкового слова. Регістр містить регулярний набір однотипних тригерів, в кожному з яких зберігається значення одного двійкового розряду машинного слова. Найчастіше використовують тригери RS, JK і D Регістри, призначені тільки для приймання, зберігання і передачі інформації, називаються елементарними або фіксаторами. Регістри, в яких зберігання даних поєднується з мікроопераціями зсуву, називаються зсувовими. Логічна функція регістра позначається буквами RG (register). Регістри забезпечують зберігання команд, адреси пам'яті, результатів операцій, індексів та ін. Регістри класифікують за такими ознаками: способом керування записуванням – асинхронні та синхронні; способом записування і видачі двійкових слів – паралельні, послідовні й універсальні; у паралельних регістрах записування і видача слів виконується одночасно всіма розрядами, а в послідовних – розряд за розрядом в напрямку від молодших розрядів до старших або навпаки; універсальні регістри забезпечують як паралельний, так і послідовний обмін інформацією; числом ліній для представлення значення одного розряду слова – однофазні й парафазні; при однофазному поданні значення кожного розряду слова передається по одній лінії зв'язку, а при парафазному – по двох лініях; числом тактів для записування слова – одно-, дво- і багатотактні; складом мікрооперацій, які виконуються: установлювальні, записування, читання, порозрядні логічні й зсуву, а також перетворення послідовного коду в паралельний і навпаки; напрямом зсуву – односторонні (лівий або правий зсув) і двосторонні (реверсивні); типом тригерів, що використовуються; елементною структурою – потенціальні, імпульсні й потенціально-імпульсні. 23.Проектування регістрів на елементах пам’яті Установлювальні мікрооперації служать для переключення регістрів у певний стан. Наприклад, установлення регістра в стан "0" або "1"; установлення парних розрядів у стан "0", а непарних – у стан "1"; записування в регістр деякої константи або обнуління деяких байтів та ін. Установлювальні мікрооперації переважно використовують асинхронні входи регістра. У регістрах на RS- або JK- тригерах можливий однофазний або парафазний спосіб записування інформації. При однофазному записуванні значення кожного розряду слова А=Аn An-1…Аi …А1 надходить по одній лінії зв'язку на вхід S (або J) відповідних тригерів. Після зчитування записаної інформації регістр має обнулятися по спільному R входу. Таким чином, при однофазному записуванні частота обміну інформацією зменшується, оскільки процеси введення і скидання чергуються. При парафазному записуванні інформації значення кожного розряду слова А передається по двох лініях зв'язку. При цьому пряме значення Аі надходить на вхід S (або J) відповідних тригерів, а інверсне значення – на вхід R (або K). У цьому випадку не потрібне попереднє скидання регістра в стан "0", тому що таку функцію виконує сигнал У регістрах на D-тригерах, які мають один інформаційний вхід, можливий тільки однофазний спосіб записування інформації. З приходом чергового синхроімпульсу записується нова інформація або при відсутності даних на вхідній шині стан регістра автоматично обнуляється При необхідності збереження інформації на декілька тактів у регістрах на Dтригерах потрібно використати дозволяючий V-вхід, або блокувати проходження синхроімпульсу на С-вхід. 24. Схеми регістрів в інтегрованому виконанні Регістри в інтегральному виконанні входять до складу більшості мікросхем,які серійно випускаються , і відрізняються кількістю розрядів,функціональними можливостями,побудовою схеми. Особливості таких регістрів покажемо на прикладі регістра NP1. Мікросхема К155NP1 є чотирьох розрядним регістром зсуву з послідовним і паралельним прийманням та видачею інформації. Регістр має входи: V2 – вибору режиму роботи V1 – для приймання інформації в послідовному коді D1-D4 – для приймання інформації в паралельному коді та синхровходи: C1- для зсуву вправо C2- для керування прийманням інформації 25. Лічильники Лічильником називається типовий функціональний вузол комп'ютера, призначений для лiчби вхідних імпульсів. Лічильник являє собою зв’язаний ланцюг Т-тригерів, які утворюють пам’ять iз заданим числом сталих станів Розрядність лічильника n дорівнює числу T-тригерів. Кожний вхідний імпульс змінює стан лічильника, який зберігається до надходження наступного сигналу. Значення виходів тригерів лічильника Qn,Qn–1,...,Q1 відображають результат лічби в прийнятій системі числення. Логічна функція лічильника позначається буквами СТ (counter). Лічильник є одним з основних функціональних вузлів комп’ютера. Основне застосування лічильників: утворення послідовності адрес команд програми; підрахунок числа циклів при виконанні операцій ділення, множення, зсуву; Лічильник характеризується модулем і ємністю лічби. Модуль лічби КЛЧ визначає число станів лічильника. У лічильниках використовуються три режими роботи: керування, накопичення і ділення. У режимі керування зчитування інформації виконується після кожного вхідного лічильного імпульсу. У режимі накопичення головним є підрахунок заданого числа імпульсів. У режимі ділення основним є зменшення частоти надходження імпульсів в КЛЧ разів. Лічильники класифікують за такими ознаками: способом кодування – позиційні та непозиційні; модулем лічби – двійкові, десяткові, з довільним постійним або змінним модулем; напрямком лічби – прості (підсумовуючі, віднімальні) і реверсивні; способом організації міжрозрядних зв’язків – з послідовним, наскрізним, паралельним і комбінованим переносами (позикою); типом використовуваних тригерів – T, JK, D в лічильному режимі; За видом переходів прості лічильники (Лч) розподіляються на підсумовуючі (прямої лічби) і віднімальні (зворотної лічби). До часових характеристик лічильників відносяться роздільна здатність, швидкодія і час встановлення коду. У лічильниках з послідовними перенесеннями тригери перемикаються почергово після кожного вхідного імпульсу в напрямку від молодших розрядів до старших. Такі лічильники називаються послідовними або асинхронними. У лічильниках з паралельними перенесеннями тригери перемикаються одночасно після кожного вхідного імпульсу, такі лічильники називаються паралельними або синхронними. 26. Арифметико-логічні пристрої Арифметико-логічний пристрій (АЛП) — блок процесора, що служить для виконання арифметичних та логічних перетворень над даними, що іменуються операндами. Цей пристрій є фундаментальною частиною будь-якого обчислювача, навіть найпростіші мікроконтролери мають його в складі свого ядра. Центральний процесор та відеопроцесор можуть мати кілька АЛП, що відрізняються своїм функціональним призначенням або типом оброблюваних даних. Класифікація За структурою(з розподіленою логікою, з зосередженою логікою) За типом запису даних(послідовні;паралельні;послідовно-паралельні.) За архітектурними особливостями(з двоспрямованою шиною та одноадресним регістровим файлом; з односпрямованою шиною та одноадресним регістровим файлом; з односпрямованою шиною та двоадресним регістровим файлом.) Залежно від часу виконання операцій(синхронного типу;асинхронного типу;комбінованого типу.) Кожен АЛП може бути представлений як композиція пристрою управління, що керує та операційного пристрою, що безпосередньо виконує операції. Інколи окремо виділяють блок контролю, що слідкує за правильністю виконання операцій. Якщо пристрій має зосереджену логіку, то до цих компонент додаються ще й регістри. Однією з найважливіших характеристик будь-якого АЛП є набір операцій, що може виконуватися. Він має бути функціонально повним для того, щоб запрограмувати алгоритм, проте з метою підвищення швидкодії та спрощення програмування, вказаний набір має значну надлишковість. Кількість операцій може значно коливатися, наприклад від кількох десятків до кількох сотень, проте зазвичай це число є степінню двійки. 27. Операційні підсилювачі Операці́йний підси́лювач —підсилювач постійного струму з диференційним входом, що має високий коефіцієнт підсилення. Призначений для виконання різноманітних операцій над аналоговими сигналами, переважно, в схемах з від'ємним зворотним зв'язком (ВЗЗ). Операційні підсилювачі застосовуються в різноманітних схемах радіотехніки, автоматики, інформаційно-вимірювальної техніки, — там, де необхідно підсилювати сигнали, в яких є постійна складова. Класифікація ОП: За типом елементної бази(На біполярних транзисторах,на польових транзисторах) За галуззю застосування (Операційні підсилювачі, що випускаються промисловістю, постійно удосконалюються, параметри ОП наближаються до ідеальних. Проте, поліпшити всі параметри одночасно технічно неможливо, або недоцільно через дорожнечу отриманого чипа. Для того, щоб розширити область застосування ОП, випускаються різні їх типи, в кожному з яких один або декілька параметрів є видатними, а інші на звичайному рівні. Це виправдано, оскільки, залежно від сфери застосування, від ОП потрібне високе значення того або іншого параметра, а не всіх їх відразу. Звідси випливає класифікація ОП по областях застосування.) Індустріальний стандарт. Так називають широко вживані, дуже дешеві ОП загального застосування з середніми характеристиками. Приклад: Lm324 ОП з малим вхідним струмом. Високовольтні ОП Швидкодіючі ОП У загальному випадку, ОП використовує біполярне живлення, тобто джерело живлення, що має три виводи, з потенціалами: U+ (до нього підключається Vs+), 0, і U- (до нього підключається Vs-). Вивід джерела живлення з нульовим потенціалом, безпосередньо до ОП, зазвичай, не підключається, але, як правило, є загальною точкою схеми і використовується для створення зворотного зв'язку. Тому, часто, замість біполярного, використовується простіше, однополярне, джерело живлення, а загальна точка створюється штучно. 28. Аналогові перемножувачі Аналогові перемножувачі (АП) є найбільш поширеними після операційних підсилювачів аналоговими функціональними вузлами вимірювальної та обчислювальної техніки; з їх допомогою виконують модуляцію, демодуляцію, управління параметрами різних схем, обчислення й інше. Тому особливого значення набуває підвищення точності аналогових перемножувачів. Аналогові перемножувачі (АП ) призначені для операції перемноження двох аналогових величин - струмів або напруг. На їх основі можуть бути побудовані схеми подвійників частоти , балансних модуляторів , фазових детекторів , змішувачів , підсилювачів з електронним регулюванням посилення і багато інших радіотехнічні та електротехнічні схеми . У системах автоматичного регулювання вони можуть виконувати функції перемноження і зведення в квадрат , а спільно з операційними підсилювачами виконувати поділ , вилучення коренів і виділення тригонометричних функцій. За обсягами випуску універсальних пристроїв аналогові перемножувачі займають третє місце після операційних підсилювачів і стабілізаторів напруги , тому їх вдосконалення йде постійно , причому переслідується кілька цілей : підвищення лінійності перемноження , поліпшення частотних властивостей , зниження енергоспоживання , розширення діапазону вхідних величин при незмінному напрузі живлення , а також побудова аналогових перемножувачі з низьковольтним харчуванням без втрати основних якісних параметрів . Оскільки даний вид аналогових пристроїв є універсальним , то для більш повної сумісності та взаємозамінності морально застарілих схемотехнічних конфігурацій новішими необхідне дотримання такого параметра , як чотириквадрантний . Це означає , що обидві вхідні величини можуть приймати як позитивні , так і негативні значення . Таким чином , якщо одну вхідну величину відкласти по осі Х декартової системи координат , а другий - по осі У , то перемножувач повинен нормально функціонувати в усіх чотирьох квадрантах вийшла системи . 29. Аналогові комутатори і ключі Аналогові ключі (АК) являють собою одну з найпростіших різновидів аналогоцифрових схем . Управляються такі АК дискретними сигналами , а перемикають безперервні сигнали. Перевагами подібних АК є: а) у відкритому стані пропускають струм в обох напрямках; б) в каналі відсутні паразитні джерела напруги; в) в закритому стані опір каналу , яке визначається струмами витоку назад зміщених pn - переходів , дуже велике; г) час замикання - розмикання досить мало ; д) ланцюг управління електрично ізольована від сигнальної ланцюга. Аналогові комутатори (АК) зазвичай використовуються в системах збору інформації для обробки аналогових сигналів, що надходять по паралельних каналах для перетворення в цифрові сигнали. Число каналів у АК може досягати декількох сотень , але максимальне значення визначається необхідною частотою опитування датчиків. Взаємний вплив каналів спостерігається в АК не тільки в статичному режимі (за рахунок кінцевого опору розімкнутих ключів) , але і в динамічному , коли один з АК ще розімкнувся , а інший - вже замкнулося. Виникаючі при цьому великі наскрізні струми не тільки збільшують динамічну складову похибки , але також можуть вивести АК з ладу. Для усунення цього ефекту , АК проектуються таким чином , щоб час включення АК було більше часу виключення . 31. Компаратори Компаратори — це елементи порівняння, які широко використовуються в системах контролю та автоматичного керування й відносяться до елементів імпульсної техніки. Компаратор, виконаний на базі ОП (рис. 50, а), порівнює вимірювану напругу uвх, яка подається на один із входів (переважно на інвертувшіьніш), із опорною напругою (наперед заданою) Uon, яка подана на інший вхід. Опорна напруга є незмінною в часі, додатної чи від ємної полярності, а вхідна напруга — змінюється. Коли uBX = Uon вихідна напруга ОП змінює свій знак на протилежний (з U ВИХ . МАКС па U ВИХ . МАКС чи навпаки). Тому компаратор мас ще назву «нуль-орган», оскільки зміна полярності вихідної напруги (перемикання) відбувається за умови, що uвх — Uоn = 0, де Uоn — задана напруга. Якщо на інвертувальний вхід подається синусоїдний сигнал (u вх), а на неінвертувальний — постійна напруга (Uon) додатної полярності (рис. 42, б), то вхідна напруга ОП uвх.оп = uвх -U0П . До моменту часу від 0 до t1 , u BX .ОП 0 , тому uвих = U ВИХ до t1 до t 2 , u BX .ОП 0 , . МАКС . В проміжку часу від томуuвих= U ВИХ . МАКС . Компаратори для порівняння напруг однієї полярності випускають у вигляді мікросхеми, схемне зображення та передатну характеристику якого показано на рис. 51. 32. Інтервальні таймери Інтервальний таймер (Periodic Interval Timer - PIT) призначений для формування переривань з суворою періодичністю для нормального функціонування планувальника операційної системи. Інтервальний таймер розроблений з метою досягнення максимальної точності при формуванні інтервалів часу навіть для систем з великим часом відгуку. 33. Аналого-цифрові перетворювачі Аналого-цифрові перетворювачі (АЦП) призначені для перетворення аналогової інформації (звичайно у вигляді напруги) у цифровий код. Застосовують АЦП у мікропроцесорних системах, у цифрових вимірювальних приладах. Області застосування їх багато в чому аналогічні ЦАП, оскільки вони часто використовуються спільно, наприклад, в автоматизованих системах керування (АСК). Основними параметрами і характеристиками АЦП є: - число розрядів n вихідного коду; - роздільна здатність h - мінімальний квант вхідної напруги, за якої вихідний код змінюється на одиницю молодшого розряду; - нелінійність δл - максимальне відхилення вихідного коду від розрахункового значення у всьому діапазоні шкали; - абсолютна похибка δА найбільше відхилення вихідного коду від розрахункового в кінцевій точці шкали; - час перетворення tпр - інтервал від моменту початку перетворення до появи на виході сталого коду; часто замість tпр швидкодія АЦП характеризується частотою перетворення; - діапазон і полярність вхідної напруги, число джерел живлення, струм споживання, можливість спільної роботи з мікропроцесорами. У АЦП застосовуються такі методи перетворення: - послідовної лічби (з використанням ЦАП або з двотактним інтегруванням); - порозрядного кодування (послідовного двійкового наближення); - паралельної дії (зчитування); - паралельно-послідовні (комбіновані). У загальному випадку АЦП (мікросхему АЦП) можна представити у вигляді блоку, що має один аналоговий вхід, один або два входи для подачі опорної (зразкової) напруги, а також цифрові виходи для видачі коду, що відповідає поточному значенню аналогового сигналу. Часто мікросхема АЦП має також входи для подачі тактового сигналу CLK, сигналу дозволу роботи CS і сигналу готовності вихідного цифрового коду RDY. На мікросхему подається одна або дві напруги живлення і загальний дріт. Опорна напруга АЦП задає діапазон вхідної напруги, в якій виробляється перетворення. Вона може бути постійною або ж допускати зміну в деяких межах. Існує два основні принципи побудови АЦП: послідовний і паралельний. У послідовному АЦП вхідна напруга послідовно порівнюється одним єдиним компаратором з декількома еталонними рівнями напруги, і залежно від результатів цього порівняння формується вихідний код. Другий тип АЦП - АЦП паралельного типу - працює за простішим принципом. Всі розряди вихідного коду обчислюються в них одночасно (паралельно), тому вони набагато швидші, ніж послідовні АЦП. 35. Схеми затримування сигналів Інвертори широко застосовуються в тих випадках, коли необхідно отримати затримку сигналу, правда, незначну (від 5 до 100 нс). Для здобуття такої затримки послідовно включається потрібна кількість інверторів (рисунок 8.1,а). Рисунок 8.1 – Використання інверторів для затримки сигналу Сумарний час затримки, наприклад, для чотирьох інверторів, можна оцінити по формулі tз = 2tPHL + 2tPLH . Правда, треба враховувати, що зазвичай реальні затримки елементів виявляються істотно нижчими (інколи навіть удвічі), ніж табличні параметри tPHL і tPLH. Тобто про точне значення отримуваної затримки говорити не доводиться, її можна оцінити лише приблизно. Для затримки сигналу використовуються також конденсатори (рисунок 8.1, б). При цьому затримка виникає із-за повільного заряду і розряду конденсатора (напруга на конденсаторі - UC). Схема без резистора (зліва на рисунку) дає затримку близько 100 нс. У схемі з резистором (справа на рисунку) номінал резистора має бути порядка сотні Ом. Але при виборі таких схем з конденсаторами треба враховувати, що деякі серії мікросхем (наприклад, КР1533) погано працюють із затягнутими фронтами вхідних сигналів. Крім того, треба враховувати, що кількість задаючих час конденсаторів в схемі обернено пропорційно до рівня майстерності розробника схеми. 36. Формувачі В комп’ютерній схемотехніці бувають випадки, коли дуже корисною є особливість елементів І, І-НЕ, АБО, АБО-НЕ формувати короткі імпульси при зміні вхідних сигналів. . Наприклад, нам необхідно сформувати короткий імпульс по позитивному або негативному фронту наявного сигналу. Тоді цей сигнал інвертують, спеціально затримують за допомогою ланцюжка елементів або ємкості і подають вихідний сигнал і затриманий сигнал на входи елементу Імпульс по позитивному фронту вхідного сигналу формується на елементі 2І або 2І-НЕ (а), а імпульс по негативному фронту вхідного сигналу - на елементі 2АБО або 2АБО-НЕ (б). Якщо елемент з інверсією, то вихідний імпульс буде негативним, якщо без інверсії, то позитивним. При вказаній на схемах величині ємкості тривалість імпульсу виходить близько 50 нс. Для збільшення тривалості імпульсу треба збільшувати величину ємкості або ж кількість інверторів в ланцюзі затримки (при цьому кількість інверторів обов'язково має бути непарною). Для побудови формувачів сигналів шроко використовуються тригери Шмітта - це формувач сигналу початкового скидання по включенню живлення схеми. Необхідність такого сигналу скидання викликана тим, що при включенні живлення вихідні сигнали складних мікросхем, що мають внутрішню пам'ять (наприклад, регістрів, лічильників), можуть набувати довільних значень, що не завжди зручно. Привести їх в необхідний стан (найчастіше - встановити їх в нуль) якраз і покликаний сигнал початкового скидання. Для формування сигналу початкового скидання використовується простий RC-ланка, причому конденсатор береться з великою ємкістю. Напруга на конденсаторі при включенні живлення наростає повільно, внаслідок чого на виході тригера Шмітта формується позитивний імпульс 37. Генератори імпульсних сигналів Інвертор, як найбільш простий елемент, частіше за інші елементи використовується в нестандартних включеннях. Наприклад, інвертори зазвичай застосовуються в схемах генераторів прямокутних імпульсів (рисунок 8.4), вихідний сигнал яких періодично міняється з нульового рівня на одиничний і навпаки. Всі приведені схеми, окрім схеми д, виконані на елементах К155ЛН1, але можуть бути реалізовані і на інверторах інших серій при відповідній зміні номіналів резисторів. Наприклад, для серії К555 номінали резисторів збільшуються приблизно втричі. Схема д виконана на елементах КР531ЛН1, оскільки вона вимагає високої швидкодії інверторів. Схеми а, б і в є звичайними RC - генераторами, характеристики яких (вихідну частоту, тривалість імпульсу) можна розрахувати лише приблизно. Для схем а і б при вказаних номіналах резистора і конденсатора частота генерації складе порядка 100 кГц, для схеми в - близько 1 Мгц. Ці схеми рекомендується використовувати лише в тих випадках, коли частота не дуже важлива, а важливий сам факт генерації. Якщо ж точне значення частоти принципове, то рекомендується застосовувати схеми г і д, в яких частота вихідного сигналу визначається лише характеристиками кварцового резонатора. Схема г використовується для кварцового резонатора, що працює на першій (основний) гармоніці. Величину ємкості можна оцінити за формулою: C >1/(2RF) де F - частота генерації. Схема д застосовується для гармониковых кварцевих резонаторів, які працюють на частоті, більшій основної в 3, 5, 7 разів (це необхідно для частот генерації вище 20 Мгц). 38. Характеристика і функціональні схеми імпульсних блоків живлення Комп'ю́терний блок жи́влення —, призначений для забезпечення вузлів комп'ютера електричною енергією постійного струму. У його завдання входить перетворення мережевої напруги до заданих значень напруги живлення, її стабілізація і захист від незначних завад з боку електричних мереж живлення.. Основним параметром комп'ютерного блоку живлення є максимальна потужність, що споживається з мережі. В наш час існують блоки живлення із заявленої виробником потужністю від 50 (вбудовані платформи малих формфакторів) до 1600 Вт. Другим за важливістю параметром є напруга живлення від електричної мережі (100-127 В у Північній і Південній Америці, Японії і на Тайвані, 220-240 В в інших країнах світу). Деякі джерела живлення мають перемикач зміни вхідної напруги від 230 В до 115 В, інші можуть автоматично підлаштовуватися під будь-яку напругу в цьому діапазоні. Основне призначення блоку живлення - формування напруги живлення, яка необхідна для функціонування всіх блоків ПК. Основна напруга живлення компонентів це: +12В, +5В, +3,3В. Існуєь також додаткова напруга: -12В та -5В. Ще блок живлення здійснює гальванічну розв'язку між мережею 220В та компонентами комп'ютера. Це необхідно для усунення струмів витоків, наприклад на корпус ПК, а також перешкоджає виникненню паразитних струмів при сполученні пристроїв. 39. Блоки живлення АТХ Реальні схеми АТХ блоків живлення мають набагато більше елементів, у них присутні ще додаткові пристрої і є, відповідно, більш складними. На платі блоку живлення прийняті наступні позначення: 1. Конденсатори фільтра вихідних напруг. 2. Радіатор, що охолоджує діоди, які випрямляють вихідну напругу. 3. ШІМ-контролер АТ2005 (аналог WT7520), що здійснює стабілізацію напруг. 4. Основний трансформатор перетворювача. 5. Трансформатор, що формує керуючу напругу для вихідних транзисторів. 6. Трансформатор перетворювача чергової напруги. 7. Радіатор, що охолоджує вихідні транзистори перетворювачів. 8. Фільтр мережевої напруги від завад блоку живлення. 9. Діоди діодного мосту. 10. Конденсатори фільтра мережевої напруги. Нові блоки живлення мають вдосконалену сучасну схему, у ній з'явився ще один додатковий блок - коректор коефіцієнта потужності (ККП). Він здійснює підвищення коефіцієнта потужності, або інакше кажучи, забирає деякі недоліки мостового випрямляча мережевої напруги. Коефіцієнт потужності (КП) характеризує, скільки в повній потужності активної складової та скільки реактивної. Відповідно кампаніями були розроблені нові схеми блоків живлення, які мали ККП. Спочатку в якості ККП використовувався включений на вході дросель великої індуктивності, такий блок живлення називають блок живлення з PFC або пасивним ККП. Подібний блок живлення має підвищений КП. Для досягнення потрібного КП необхідно оснащувати блоки живлення більшим дроселем, тому що вхідний опір блоку живлення носить ємнісний характер через встановлені конденсатори на виході випрямляча. 40. Електричні параметри блоків живлення Блок живлення має безліч електричних параметрів, більшість з яких не відзначаються в паспорті. На бічній наклейці блоку живлення відзначається звичайно тільки декілька основних параметрів - робочі напруга та потужність. Потужність блоку живлення Потужність блоку живлення, характеризує, скільки він може віддати електричної енергії модулям, що підключають до нього, Допустимий максимальний струм лінії - При перевищенні допустимого струму в лінії блок живлення вимикається, тому що спрацьовує захист. Для її відключення необхідно виключити блок живлення від мережі і почекати деякий час, близько хвилини Діапазон робочих напруг - Під діапазоном робочих напруг передбачають інтервал значень мережевої напруги, при якому блок живлення зберігає працездатність і значення своїх паспортних параметрів. Пульсації вихідних напруг - Пульсації являють собою різку зміну напруги протягом короткого проміжку часу Стабільність напруг - Збільшення напруги викликає в першу чергу збільшення струмів спокою всіх схем, а також зміну параметрів схем. Зниження напруги навпаки зменшує струм спокою, і також погіршує характеристики схем. Коефіцієнт корисної дії - ККД показує скільки зі спожитої енергії перетворилося в корисну енергію. Чим вище ККД, тим менше треба платити за електроенергію споживану комп'ютером. Коефіцієнт потужності - При малому значенні коефіцієнта потужності буде і мале значення ККД. 41. Вибір блока живлення При покупці БЖ, в першу чергу необхідно подивитися на наявність сертифікатів і на відповідність його сучасним міжнародним стандартам. На блоках живлення найчастіше можна зустріти вказівку наступних стандартів: RoHS, UL, cUL, ISO, CB, FCC,TUV, ССС. Існують також комп'ютерні стандарти форм-фактору АТХ, у якому визначені розміри, конструкція та багато інших параметрів блоку живлення, включаючи допустимі відхилення напруг при навантаженні. Відмінність версій стандартів АТХ в основному стосується введення нових роз’ємів і нових вимог до ліній живлення блоку живлення. Коли виникає необхідність покупки нового блока живлення ATX, то спочатку необхідно визначитися з потужністю, яка необхідна для живлення комп'ютера, у який цей БЖ буде встановлений. Для її визначення достатньо просумувати потужності компонентів, використаних у системі, або скористатися правилом, що для середньостатистичного комп'ютера з однією ігровою відеокартою цілком вистачає блоку живлення потужністю 500-600 ват. Враховуючи те, що про більшість параметрів блоків живлення можна довідатися тільки протестувавши його, випливає наступне: настійно рекомендуємо ознайомитися з тестами та оглядами можливих претендентів - моделей блоків живлення, які доступні у вашому регіоні та задовольняють ваші потреби як мінімум щодо потужності, яку вони здатні забезпечити. Якщо ж такої можливості немає, то вибирати необхідно згідно відповідності блоку живлення сучасним стандартам (чим більшій кількості, тим краще), при цьому бажана наявність у блоці живлення схеми АККМ (APFC). Купуючи блок живлення, також важливо включити його, по можливості безпосередньо на місці покупки або одразу як прийшли додому, і простежити, як він працює, щоб блок живлення не видавав писків, гулу або іншого стороннього шуму. Взагалі, необхідно вибрати блок живлення, який був би потужним, якісно зробленим, з гарними заявленими та реальними електричними параметрами, а також щоб він був зручним в експлуатації та тихим під час роботи, навіть при високому навантаженні на нього. І в жодному разі при придбанні блока живлення не варто заощаджувати пару доларів. Пам'ятайте, що від роботи цього пристрою головним чином залежить стабільність, надійність і довговічність роботи всього комп'ютера. 42. Класична архітектура комп’ютера Класичну архітектуру сучасних комп’ютерів, що приведена на рисунку 10.1, часто називають « архітектурою фон Неймана ». Процесор АЛП Керування Керування ЦПК Адреса, результати Операнди Команди, дані Пристрій введення Пам’ять Пристрій виведення Результати Програма обчислень (обробки інформації) складається у вигляді послідовності команд і завантажується в пам’ять комп’ютера, в якій також зберігаються вихідні дані і проміжні результати. Пам’ять комп’ютера служить для зберігання вихідних даних, програм обробки інформації, проміжних і кінцевих результатів. В даній системі, як правило, виділяють рівні надоперативної, оперативної, буферної і завнішньої пам’яті. Кожний послідуючий рівень відрізняється від попереднього, в першу чергу найважливішими технічними характеристиками пам’яті - ємністю і швидкодією. В малих комп’ютерах, мікрокомп’ютерах структура пам’яті суттєво простіша і включає один, два рівні. В процесорі комп’ютера зосереджені всі процеси по обробці інформації. Процесор складається із арифметико-логічного (операційного) пристрою (АЛП) і центрального пристрою керування (ЦКП) . Арифметико-логічним пристроєм назавають ту частину процесора , котра призначена для виконання арифметичних і логічних операцій над словами, які поступають з пам’яті комп’ютера. Любий АЛП має в своєму складі декілька регістрів і функціональних (комбінаційних) схем. Регістри призначені для зберігання операндів в процесі виконання операцій. Всі операції реалізуються в АЛП як просторово - часові послідовності деяких елементарних операцій (мікро операцій) над словами. Центральний пристрій керування в складі процесора призначений для розшифрування команд і формування послідовностей керуючих сигналів. Дані сигнали включають в роботу окремі вузли процесора, що приводить до виконання дій, котрі вказані в команді. Для виконання однієї елементарної операції в АЛП необхідно подати один сигнал з пристрою керування по лініях керування. Відомо три основних типи ЦПК - мікропрограмні, апаратні і змішані. 43. Організація зв’язків між функціональними вузлами комп’ютера Для забезпечення роботи комп’ютера його функціональні вузли повинні бути відповідним чином з’єднані. Обмін інформацією між вузлами комп’ютера проводиться по шинах. Є три головних типи шин: шина даних, шина керування (або шина команд) та шина адрес, які використовуються відповідно для пересилання даних, команд та їх адрес. В двошинній структурі комп’ютера з обміном через процесор (рисунок 1) введення інформації з пристрою введення до основної пам’яті та виведення інформації з основної пам’яті до пристрою виведення здійснюється через процесор. Шина введення/виведення Пристрій введення Шина пам’яті Процесор Основна пам’ять Кеш пам’ять Пристрій виведення Рисунок 1. Недолік – процесор витрачає свій час на виконання операцій введення та виведення інформації, безпосередньо працюючи з пристроями введеннявиведення. В двошинній структурі комп’ютера з обміном через пам’ять (рисунок 2) процесор звільняється від операцій введення-виведення інформації. Процесор введення/виведення Пристрій введення Шина введення/виведення Шина пам’яті Основна пам’ять Кеш пам’ять Центральний процесор Пристрій виведення Рисунок 2 Для організації введення-виведення тут використовується спеціальний процесор введення-виведення. В одношинній структурі комп’ютера (рисунок 3) всі його функціональні вузли з’єднані через одну спільну шину. Шина розподіляється між ними в часі, тому одночасно посилати дані на шину може тільки один вузол. Пристрій введення Процесор Пам’ять Контролер Арбітр шини Рисунок 3 Пристрій виведення Контролер 44. Поняття архітектури комп’ютера Спеціалісти по архітектурі комп’ютерів називаються архітекторами комп’ютерів чи комп’ютерних систем. Задачею такого архітектора є розробка комп’ютера, який відповідав би конкретним вимогам його користувачів, чи загальним вимогам сьогоднішнього дня. Архітектура комп’ютера – це абстрактне представлення фізичної системи (апаратних засобів і мікропрограм) з точки зору програміста, який використовує машинно – орієнтовану мову. Архітектура визначає принципи організації комп’ютера (системи) і функції процесора і не відображає такі проблеми, як керування і передавання даних всередині процесора, особливості систем елементів і технологію виробництва. Архітектори комп’ютерів ставлять перед собою задачі удосконалення і оновлення парку комп’ютерів і побудованих на їх основі обчислювальних систем в кожному із перерахованих напрямків і в той же час намагаються створити систему з оптимальним співвідношенням вимог. Архітектура комп’ютера (комп’ютерної системи) передбачає багаторівневу організацію. Архітектуру комп’ютера (комп’ютерної системи) можна визначити шляхом виявлення її відмінностей від інших видів архітектури. Специфічною властивістю архітектури комп’ютера (комп’ютерної системи) є можливість виділення в ній набору рівнів абстракції (рисунок 1). 1 Прикладні програми користувачів 2 “Мовні” процесори 3 1 Керування ресурсами на логічному рівні 4 Керування ресурсами на фізичному рівні 5 5 5 Виконання 6 програми 7 A Процесори введення-виведення 6 9 10 Контролери 6 Контролери 10 Канали зв’язку і зовнішні пристрої B 6 Пам’ять 8 C 45. Архітектурні принципи Джона фон Неймана Великий вклад в розвиток обчислювальної техніки (побудови ЕОМ чи комп’ютерів) вніс відомий фізик і математик Джон фон Нейман Принципи фон Неймана 1. Принципи програмного керування (управління ) роботою комп’ютера. Програма складається з окремих кроків – команд. Послідовність команд є програмою. 2. Принцип умовного переходу. Можливість змінювати послідовність обчислення в залежності від отриманих проміжних результатів. 3. Принцип зберігання програми. Команди представляються в числовій формі і зберігаються в тому ж ОЗП, що і дані для обчислень. Таким чином, команди можна подавати в арифметичний пристрій і перетворювати як звичайні числа. Це дозволяє створювати програми, які здатні в процесі обчислень змінювати самі себе. 4. Використання двійкової системи числення для представлення інформації. 5. Принцип ієрархічності запам’ятовуючого пристрою. Дані, які найбільш часто використовуються, зберігаються в найбільш швидкодіючому ЗП порівняно малої ємкості, а дані, які використовуються досить рідко – в самому повільному, але набагато більшої ємкості. Більшість комп’ютерів першого покоління будувались на основі даних принципів, тому їх і називають машинами фон Нейманівського типу. Важливо відмітити, що архітектура персональних комп’ютерів повністю базується на принципах фон Неймана. 46. Типи сучасних комп’ютерів Основні засоби сучасної обчислювальної техніки можна класифікувати наступним чином: комп’ютерні системи (суперкомп’ютери), комп’ютери загального призначення, малі (міні–) комп’ютери, мікро– і персональні комп’ютери, мікропроцесори. Суперкомп’ютери До надпродуктивних комп’ютерів (суперкомп’ютерів) на даний час відносять комп’ютери (Cray, Cray 1,2, Cyber 205, Эльбрус, ПС–2000 і т.п.), які при виконані науково–технічних розрахунків досягають продуктивності від 10 до 103 Мфлоп/с (Мфлоп/с– мільйон операцій із плаваючою крапкою за секунду Комп’ютери загального призначення Комп’ютери вказаного типу відносяться до універсальних комп’ютерів і відрізняються показниками продуктивності. Такі машини мають високу швидкодію, пам’ять великого об’єму, гнучку систему команд, широкий вибір периферійних пристроїв і способів кодування інформації, що враховує потреби опрацювання даних. Мікрокомп’ютери і мікропроцесори Розвиток інтегральної технології привів до створення великих мікросхем (ВІС) різного призначення, що вміщують десятки й сотні тисяч простих елементів. Процесор комп’ютера, який реалізований на одній або декількох ВІС, отримав назву мікропроцесор (МП). МП за швидкодією й можливостями системи команд наближається до міні–комп’ютерів (малих комп’ютерів. Мікрокомп’ютери можуть бути виконані і на одній ВІС (наприклад, однокристальні мікрокомп’ютери К1816ВЕ48, К1816ВЕ51 і т.п.). Мінікомп’ютери Це широкий клас машин, що належать до стаціонарних. Мінікомп’ютери, в основному, відносяться до проблемно–орієнтованих обчислювальних машин. Основне призначення – керування технологічним обладнанням, первинне опрацювання інформації, організація обміну по лініях зв’язку і т. д. В той же час мінікомп’ютери достатньо універсальні, щоб вирішувати широке коло науково–технічних задач. На сучасному етапі можливості сучасних міні– машин, наприклад, суперміні–комп’ютери, перекривають можливості середніх і великих комп’ютерів. 47. Багаторівнева структура пам’яті ком’ютера В загальному випадку пам’ять комп’ютера (рисунок1) складається з надоперативної пам’яті (НОЗП) або місцевої пам’яті, оперативної пам’яті (ОП), пам’яті з прямим доступом на магнітних барабанах, магнітних і магнітооптичних дисках, пам’яті з послідовним доступом на магнітних стрічках і на оптичних дисках. Ієрархічна структура пам’яті дозволяє економічно ефективно поєднувати збереження великих об’ємів інформації з швидким доступом до інформації в процесі опрацювання. IІ рівень Ядро комп’ютера ІIІ рівень Пам’ять з прямим доступом НОЗП або місцева пам’ять Пам’ять каналу Оперативна пам’ять ЗП на МБ ЗП на дисках Пам’ять з послідовним доступом ЗП на МОД ЗП на МС Зовнішня пам’ять Керуюча пам’ть I рівень Внутрішня пам’ять До апаратури процесора Процесор Рисунок1 Ієрархія пам’яті сучасних комп’ютерів базується на декількох рівнях, причому більш високий рівень менший за об’ємом, швидший і має більшу вартість у перерахунку на байт, ніж більш низький рівень. Рівні ієрархії взаємно зв’язані: всі дані на одному рівні можуть бути знайдені на біль низькому рівні, а всі дані на даному більш низькому рівні можуть бути знайдені на наступному нижчому рівні і т.д., поки ми не досягнемо основи ієрархії. Ієрархія пам’яті складається з декількох рівнів, але в кожний момент часу маємо справу тільки з двома найближчими рівнями. Мінімальна одиниця інформації, котра або присутня, або відсутня у дворівневій ієрархії, називається блоком.В ієрархічній структурі підсистем пам’яті ПК можна виділити наступні рівні: – регістрова пам’ять (регістри мікропроцесора); – буферна або кеш–пам’ять; – оперативна пам’ять або ОЗП; – зовнішня пам’ять або ЗЗП. 48. Регістрова пам’ять Регістрова (надоперативна) пам’ять процесора це пам’ять (рисунок 1), яка сладається з регістрів з закріпленими операціями, та регістрів загального призначення. Тут РгА, РгК і РгД – відповідно регістри адреси, команд і даних. РгА РгД ПЛ Рг0 Рг1 . . . РгК Рг(n-1) РгССП n регістрів загального призначення Рисунок 11.2 – Регістрова пам’ять процесора РгА зберігає адресу даного або команди при звернені до основної пам’яті. РгД зберігає операнд при його запису або зчитуванні з основної пам’яті. В ролі операнда може бути дане, команда або адреса. РгК зберігає команду після її зчитування з основної пам’яті. ПЛ – програмний лічильник, який підраховує команди та зберігає адресу поточної команди. Регістри загального призначення (РЗП) є програмно доступними. Зазвичай їх називають регістровим файлом – це набір програмно-доступних регістрів, які знаходяться в регістровій пам’яті процесора. В сучасних процесорах регістровий файл займає одне з центрольних місць. Він використовується для локального збереження операндів, адрес команд та даних, індексів, а також дозволяє організовувати ефективний обмін даними між операційними пристроями процесора та основною пам’яттю. Для організації високопродуктивних обчислень важливо не тільки мати велику кількість регістрів, але і забезпечити швидкий доступ до даних, які в них зберігаються, за рахунок ефективної організації регістрового файлу. Типи регістрових файлів Інтегрований багатопортовий регістровий файл Розподілений регістровий файл Ієрархічний регістровий файл Кластерна організація Організація з керованою комутацією Регістрові вікна 49. Основна пам’ять.Оперативний запам’ятовуючий пристрій Основна пам’ять включає, як правило, два типи пристроїв: оперативні запам’ятовуючі пристрої (ОЗП) і постійні запам’ятовуючі пристрої (ПЗП). Структура основної пам’яті комп’ютера подана на рисунку 1. Шина адреси 0 РгА n-1 Основна пам’ять ПЗП Контролер основної пам’яті ОЗП 0 РгД n-1 Дозвіл роботи Запис/ читання Шина даних Рисунок 11.5 – Структура основної пам’яті комп’ютера До комірок основної пам’яті (ОП) центральний процесор може звертатися безпосередньо, як і до регістрів регістрового файла. Інформація, що зберігається у зовнішній пам’яті, стає доступною процесору тільки після того, коли буде переписана в основну пам’ять. Основну пам’ять будують як пам’ять з довільним доступом. В сучасних комп’ютерах основна пам’ять будується на напівпровідникових мікросхемах. Основну частину основної пам’яті утворює оперативний запам’ятовуючий пристрій (ОЗП), який дозволяє як запис, так і зчитування інформації, причому обидві операції виконуються подібним чином та практично за один час. Другу групу напівпровідникових пристроїв основної пам’яті складають мікросхеми постійного запам’ятовуючого пристрою (ПЗП), який працює тільки на зчитування інформації. 50. Постійний запам’ятовуючий пристрій Постійний запам’ятовуючий пристрій (ПЗП), як і оперативний, є складовою частиною основної пам’яті та призначений для збереження програм, констант, табличних функцій та іншої інформації, яка записується заздалегідь і не змінюється в процесі поточної роботи комп’ютера. ПЗП застосовується також у перетворювачах кодів, знакогенераторах, у мікропрограмних пристроях керування. Загальним для всіх мікросхем постійної пам’яті є енергонезалежність, словникова організація і використання режиму зчитування як основного. Як видно із рисунка 1, на якому показано інтерфейс ПЗП, в ньому відсутній сигнал запису-зчитування даних, і дані зчитуються з ПЗП в регістр Шина адрес РгА ПЗП РгД Шина даних Рисунок 1 Занесення інформації в ПЗП називають програмуванням або „прошивкою”, яке здійснюється на стідії виготовлення, або в лабораторних умовах на спеціальних пристроях, які називаються програматорами. 51. Зовнішня пам’ять Пам’ять комп’ютера разом з основною (оперативною) пам’яттю високої швидкодії, але порівняно невеликої ємкості, вміщує зовнішню пам’ять, яка є набагато повільнішою, але може зберігати практично скільки завгодно великий об’єм необхідної для комп’ютера чи системи інформації (дані, програми). Зовнішня пам’ять складається з декількох зовнішніх запам’ятовуючих пристроїв (ЗЗП), в якості яких в сучасних комп’ютерах використовуються ЗП з носієм інформації у вигляді рухомої поверхні. Зовнішні ЗП є пристроями з довільним зверненням, які допускають багатократне зчитування і запис нової інформації на місце записаної раніше. Звернення до ЗЗП в загальному випадку передбачає послідовне виконання двох процесів: – доступу до ЗЗП – зчитування і передача інформації із ЗЗП в ОП або із ОП в ЗЗП На носії, як правило, інформація розташовується впорядковано, тому доцільно, щоб при зверненні до ЗЗП проходив запис і зчитування послідовно розміщеного на носії блоку чи масиву даних. Зовнішні ЗЗП діляться на пристрої з прямим і послідовним доступом. Накопичувачі на магнітних стрічках. Накопичувачі на магнітних стрічках (НМС) відносяться до ЗЗП послідовного доступу з рухомим магнітним запам’ятовуючим елементом, в якості якого використовується магнітна стрічка. НМС широко використовуються для довгострокового зберігання великих масивів інформації Основний недолік НМС – великий час доступу. Накопичувачі на оптичних дисках. Однією з причин швидкого розповсюдження CD–ROM стало різке зростання об’єму програмних пакетів. Друга причина – поява дешевих комп’ютерів, які оснащені засобами multimedia. Звук, а особливо відео, вимагають досить великих об’ємів зовнішньої пам’яті, і найкраще для цього підходить CD–ROМ. Ще одна з причин базується на тому, що CD–ROM – пристрій, інформація на якому не лише надійно захищена, але і непідвладна випадковому знищенню чи перезапису при помилках користувача або “роботі” вірусів. Накопичувачі на магнітооптичних дисках. На сьогоднішній день існує декілька стандартних типів магнітооптичних дисководів, серед яких найбільше розповсюдження отримали два з них. Це 3,5– дюймові і 5,25–дюймові накопичувачі. Магнітооптичні накопичувачі випускаються в двох варіантах: вмонтовані і зовнішні. Перевага зовнішніх накопичувачів в тому, що нагрівання дисководу під час роботи лазера не підвищує температуру в корпусі самого комп’ютера. Вмонтовані накопичувачі можуть бути легко встановлені на місце звичайного флоппі–дисковода. 52. Узагальнена структура процесора комп’ютера Процесор – це центральний пристрій комп’ютера, який виконує задані програмою перетворення інформації та здійснює керування обчислювальним процесом і взаємодією складових частин комп’ютера чи комп’ютерної системи. Основною функцією процесора , як центрального пристрою комп’ютера, є виконання послідовності команд, які зберігаються в основній пам’яті. Послідовність операцій, необхідних для виконання однієї команди, називається командним циклом, який може бути поділений на дві основні фази: фазу вибірки та фазу виконання. Спочатку процесор вибирає команду з пам’яті (фаза вибірки). Фаза виконання включає декодування команди, вибірку з основної пам’яті вказаних в команді операндів, виконання операції, яка вказана в полі коду операції команди, а також запам’ятовування результатів. Робота процесора в рамках командного циклу задається послідовністю мікрооперацій, які формує пристрій керування. Крім виконання арифметичних і логічних операцій, процесор керує роботою інших вузлів комп’ютера. Зокрема. Здійснює керування введенням-виведенням інформації, наприклад обміном даних між пристроями введення-виведення та основною пам’яттю. Основними складовими процесора є арифметико-логічний пристрій(АЛП), пристрій керування і регістрова пам’ять або надоперативний запам’ятовуючий пристрій та блок інтерфейсу (БІФ) для з’єднання із зовнішнім середовищем – пам’яттю, периферійними пристроями. Обробка даних здійснюється в АЛП, який містить арифметико-логічний блок (АЛБ), блок РЗП, блок контролю БК і місцевий блок керування при децентралізованому керуванні. Арифметико-логічний блок має універсальний двійковий комбінаційний суматор, двійково-десятковий суматор або схему десяткової корекції, регістри для тимчасового зберігання двох операндів і результату операцій та регістр прапорців. Розрядність АЛП визначає розрядність всього процесора. В РЗП зберігаються початкові дані, проміжні та кінцеві результати, адреси даних, константи,які необхідні в процесі виконання команди.Всі операції в АЛП реалізуються як просторово-часові послідовності мікрооперацій над двійковими словами, кожна з яких є сукупністю булевих операцій над бітами слів. Пристрій керування ПК керує процесом оброблення даних, забезпечує основні режими роботи та взаємодію всіх пристроїв комп’ютера. До складу процесора можуть входити спеціальні системні засоби . Пристрій керування послідовно зчитує код команди з пам’яті і розміщує його в регістр команд (інструкцій). Блок керування дешифрує команду і формує послідовності керуючих сигналів. Для виконання однієї мікрооперації в АЛП необхідний один керуючий сигнал. В одному машинному такті реалізується сукупність мікрооперацій – мікрокоманда. Множина мікрокоманд створює мікропрограму команди. Кожна команда має свою мікропрограму, час виконання якої називається командним циклом. 53. Одношинна структура процесора Процесор – це центральний пристрій комп’ютера, який виконує задані програмою перетворення інформації та здійснює керування обчислювальним процесом і взаємодією складових частин комп’ютера чи комп’ютерної системи. Основною функцією процесора , як центрального пристрою комп’ютера, є виконання послідовності команд, які зберігаються в основній пам’яті. Залежно від зв’язків між функціональними вузлами процесора і організації їх взаємодії розрізняють кілька структур процесора. Однією з найпростіших структур процесора є одношинна структура. До складу процесора входять пристрій керування, арифметико-логічний пристрій АЛП з вхідним РгY та вихідним РгZ регістрами, і регістрова пам’ять, до складу якої входять регістр команд РгК, регістр даних РгД, регістри адреси РгА, програмний лічильник ПЛ , та регістровий файл – стек програмно-доступних регістрів Рг0, Рг1,..., Рг(n-1). Обмін інформацією між вказаними пристроями здійснюється через спільну внутрішню шину процесора. Зв’язок процесора з основною пам’яттю проводиться через регістри адрес та даних. Регістр адреси зберігає адресу операнда або команди при звернені до основної пам’яті. Регістр команд зберігає команду після її зчитування з основної пам’яті. Регістр даних збарігає операнд при його запису обо зчитуванні з основної пам’яті. Програмний лічильник ПЛ підраховує команди та зберігає адресу поточної команди. Регістри загального призначення Рг0 – Рг(n-1) регістрового файлу є програмно доступними. Вони можуть використовуватися програмістом в якості адресних регістрів, індексних регістрів при виконанні операцій модефікації адрес або в якості регістрів для зберігання проміжних результатів обчислень. Більшість комп’ютерів мають в складі процесора тригери для зберігання бітів стану процесора, або як їх ще називають прапорців. Кожен прапорець має спеціальне призначення. Частина прапорців вказує на результати арифметичних і логічних операцій: додатній результат (Р), від’ємний результат (N), нульовий результат (Z), перенос (С), арифметичне переповнення (V) тощо. Різні команди вказують процесору, коли встановити чи очистити ці тригери. Інша частина прапорців вказує режими захисту пам’яті. Існують також прапорці, які вказують пріоритети виконуваних програм. В деяких процесорах додаткові тригери слугують для зберігання кодів умов, формуючи регістр кодів умов. Разом взяті описані прапорці формують слово стану програми(ССП), а відповідні тригери – регістр ССП. 54. Багатошинна структура процесора Процесор – це центральний пристрій комп’ютера, який виконує задані програмою перетворення інформації та здійснює керування обчислювальним процесом і взаємодією складових частин комп’ютера чи комп’ютерної системи. Основною функцією процесора , як центрального пристрою комп’ютера, є виконання послідовності команд, які зберігаються в основній пам’яті. Одношинна структура процесора є достатньо простою. Тому вона широко використовується при проектуванні процесорів реальних комп’ютерів. За такою схемою побудовано більшість мікроконтроле-рів, від яких не вимагається висока швидкодія. Якщо ж така вимога існує, то застосовується багатошинна організація процесора, в якій завдяки наявності багатьох шин забезпечується можливість паралельного обміну інформацією між функціональними вузлами процесора. Входи та виходи регістрів процесора приєднані до різних шин, що дозволяє одночасно здійснювати обмін між двома парами регістрів, а не між однією, як це було в одношинній структурі процесора. Тим самим в два рази зростає кількість переданої одночасно інформаціх. Вузол зв’язку між шинами призначений для обміну інформацією між ними. Для виконання операції додавання потрібно лише два такти, тоді як в одношинній структурі процесора – три такти. Із збільшенням кількості шин швидкість обміну зростає. Так, в тришинній структурі процесора операція додавання двох чисел буде виконана за один такт. Збільшення кількості шин ускладнює структуру процесора та збільшує кількість необхідного обладнання на його побудову. Однак потреба підвищення продуктивності змушує розробників застосовувати саме багатошинну структуру процесора. Більшість процесорів сучасних високопродуктивних комп’ютерів є багатошинними. 55. Суперковеєрні та суперскалярні процесори Процесори сучасних комп’ютерів використовують особливу технологію – конвеєри, котрі дозволяють обробляти більше однієї команди одночасно. Обробка команди може бути розділена на декілька основних етапів, чи мікрокоманд. Основними з них є п’ять мікрокоманд: вибірка команди; розшифрування команди; вибірка необхідних операндів; виконання команди; збереження результатів. Всі етапи команди задіюються тільки один раз і завжди в одному і тому ж порядку: одна за другою. Це означає, що якщо перша мікрокоманда виконала свою роботу і передала результати другій , то для виконання текучої команди вона більше не знадобиться , і можна приступити до виконання наступної коман. Можлива така організація виконання деякої послідовності команд в процесорі, коли всі однойменні фази виконання цих команд здійснюються послідовно, тобто спочатку проводиться вибірка всіх команд, далі їх декодування і т.д., для послідовності із двох команд. Такий підхід не прискорює роботу процесора, але при конвеєрному опрацюванні команд може виявитися доцільним, оскільки в ярусах конвеєра знаходяться результати виконання декількох фаз різних команд, що при наявності конфліктів дозволяє ефективніше їх використовувати, ніж у звичайному конвеєрі команд. Процесор з конвеєром команд, в якому послідовно виконуються декілька фаз над різними командами, називається суперконвеєрним. Внутрішня частота роботи ярусів конвеєра суперконвеєрного процесора є в k разів вищою їх зовнішньої частоти, з якою відбувається обмін інформацією між ярусами. Для організації суперконвеєрного опрацювання команд необхідне деяке додаткове обладнання, зокрема, регістри для зберігання проміжних результатів послідовно виконуваних фаз різних команд. Суперскалярні процесори. Щоб підвищити продуктивність конвеєрного процесора потрібно далі спрощувати операції його ярусів та поглиблювати глибину конвеєра. Це і робиться в сучасних процесорах, в яких глибина конвеєра досягає двадцяти і більше ярусів.Однак процес спрощення операцій ярусів конвеєра має межу, коли операції не піддаються поділу. Тоді для підвищення продуктивності процесора необхідно використовувати паралельне включення декількох конвеєрів команд. Такі процесори з декількома конвеєрами команд дозволяють одночасно використовувати кілька скалярних команд, а тому дістали назву суперскалярних. Тут одночасно вибирається та декодується декілька команд,а блок виконання команд включає кілька функціональних блоків.Для забезпечення одночасного зчитування та запису кількох операндів кеш-пам’ять будується за модульним принципом. Підвищення продуктивності такого процесора досягається шляхом його конвеєризації. 56. Матричні процесори Процесор – це центральний пристрій комп’ютера, який виконує задані програмою перетворення інформації та здійснює керування обчислювальним процесом і взаємодією складових частин комп’ютера чи комп’ютерної системи. Основною функцією процесора , як центрального пристрою комп’ютера, є виконання послідовності команд, які зберігаються в основній пам’яті. Найбільш розповсюдженими із систем класу один потік команд – множина потоків даних (ОКМД - SIMD) є матричні системи , які найкраще пристосовані для рішення задач, що характеризуються паралелізмом незалежних об’єктів чи даних. Організація систем подібного типу на перший погляд є достатньо простою. Вони мають спільний керуючий пристрій, який генерує потік команд і велике число процесорних елементів, що працюють паралельно і кожен обробляє свій потік даних. Таким чином, продуктивність системи буде рівною сумі продуктивностей всіх процесорних елементів. Однак на практиці, щоб забезпечити достатню ефективність системи при рішенні широкого кола задач необхідно організувати зв’язки між процесорними елементами для найбільш повного завантаження їх роботою. Одним з перших процесорів був SOLOMON. Система SOLOMON вміщує 1024 процесорних елементи, які з’єднані у вигляді матриці 32×32. Кожний процесорний елемент матриці включає в себе процесор, який забезпечує виконання послідовних порозрядних арифметичних і логічних операцій, а також ОЗП ємкістю 16 Кбайт. Довжина слова – змінна від 1 до 128 розрядів. Розрядність слова встановлюється програмно. По каналах зв’язку від пристрою керування передаються команди і спільні константи. В процесорному елементі використовується, так звана, багатомодальна логіка, котра дозволяє кожному процесорному елементу виконувати або не виконувати спільну операцію в залежності від значень даних, що обробляються. Ідея багатомодальності заключається в тому, що в кожному процесорному елементі є спеціальний регістр на 4 стани – регістр моди. Мода (модальність) заноситься в даний регістр з пристрою керування. При виконанні послідовності команд модальність передається в коді операції і порівнюється з вмістимим регістра моди. Якщо є співпадіння, то операція виконується. В інших випадках процесорний елемент не виконує операцію, але може, в залежності від коду, пересилати свої операнди сусідньому процесорному елементу. Такий механізм дозволяє виділити стрічку чи стовбець процесорних елементів, що є корисним при операціях над матрицями. Взаємодіють процесорні елементи з периферійним обладнанням через зовнішній процесор. Подальшим розвитком матрічних процесорів стала система ILLIAS-4 фірми BARROYS з реальною швидкодією 200 млн. операцій за секунду і включала в себе 256 процесорних елементів, система ПС-2000, основою якої був мультипроцесор ПС – 2000, що включав 64 процесорних елементи. 57.Поняття про суперком’ютери та їх організацію З початку ери комп’ютерної техніки проблема зменшення пропасті між продуктивністю, необхідною для рішення конкретної прикладної задачі, і продуктивністю, яка забезпечується комп’ютером , створила множину альтернативних моделей комп’ютерів. Деякі з них доказали свою ефективність на практиці. Однак на сучасному етапі інформаційного вибуху з порядку денного не сходить питання постійного подальшого підвищення продуктивності. Наприклад, сучасні проекти потребують продуктивності порядка 109 операцій за секунду і більше ( тобто команда повинна виконуватися за 1 нс), що наближається до граничних можливостей тих різновидів техніки, для яких границею є швидкість розповсюдження світла. Термін „суперкомп’ютер” підрозуміває комп’ютер з деякими додатковими властивостями, в котрому на основі досягнень сучасної науки і техніки при певних умовах може досягатися максимально можлива продуктивність, і в більшій чи меншій мірі відноситься до комп’ютерів з супер-продуктивністю, яка необхідна для рішення великих числових задач. В першу чергу до них відносяться задачі моделювання складних систем і явищ , що потребують великого об’єму матричних обчислень (прогнозування погоди, ядерні дослідження і т.п.). До класу суперкомп’ютерів належать комп’ютери що мають максимальну в даний час продуктивність, а також максимальну ємність основної та зовнішньої пам’яті. Вони асоціюються з великими розмірами, великими завданнями, гранично високими технічними характеристиками і експлуатаційними параметрами. Швидкий розвиток комп’ютерної індустрії призводить до відносності або певного нівелювання даного поняття. Найпотужнішим на сьогодні комп’ютером є суперкомп’ютер фірми IBM Blue Gene/1, який має 131 072 процесорних вузли та продуктивність 280.6 TFLOPS (1012 FLOPS). Кожен вузол містить процесор PowerPC 440 і 512 МБ локальної пам’яті. 58. Класифікація суперкомп’ютерів Паралельні комп’ютери часто поділяють згідно класифікації Флінна на комп’ютери типу ОКМД і типу МКМД. Однак така класифікація не є досконалою: існують суперкомп’ютери , які не входять в дану класифікацію, присутні важливі ознаки, котрі в даній класифікації не враховані. Архітектура сучасних суперкомп’ютерів може бути класифікована по п’яти групах в залежності від способу організації між процесорних зв’язків і прийнятою структурою схеми. 1.Багатоковеєрні однопроцесорні системи. Більшість векторних суперкомп’ютерів у найпростішому випадку представляє собою конвеєрні одно процесорні системи, які вміщують декілька функціональних пристроїв. Архітектура типу „пам’ять-пам’ять” потребує великої пропускної здатності від пам’яті і команд великої довжини, що дає виграш лише при обробці довгих векторів. Для коротких векторів чи скалярних величин продуктивність такої системи може бути надто низькою. І навпаки, архітектура типу „регістр-регістр” є більш продуктивною при обробці суміші скалярних і векторних даних. 2.Процесорні матриці з архітектурою типу ОКМД. Дані матриці є процесорами паралельного типу, які працюють синхронно під керуванням спільного пристрою керування. Фізично процесорні елементи утворюють процесору матрицю.Так як комп’ютери даного типу часто використовуються для обробки масивів даних великої розмірності, вони також називаються матричними процесорами. 3. Багатопроцесорні системи з спільною пам’яттю. Дані системи представляють собою сильнозв’язані комп’ютери з архітектурою МКМД, в котрих декілька процесорів спільно використовують одну пам’ять. Архітектура в даних системах ділиться на два основних класи: зв’язок через шину і безпосередній зв’язок. Подібну архітектуру зв’язку має більшість дорогих моделей суперкомп’ютерів. 4. Багатомашинні системи з розподіленою пам’яттю. Даний клас суперкомп’ютерів включає в себе слабо зв’язані системи з архітектурою МКМД і з розподіленими локальними ЗП, які підключені до множини процесорних вузлів. Основний спосіб зв’язку між обчислювальними вузлами в багатокомп’ютерній системі – це передача повідомлень. Ефективність зв’язку і зв’язність апаратних засобів представляє собою основні фактори, які враховуються при виборі архітектури системи за критерієм економічної ефективності. 5. Ієрархічні та реконфігуруємі суперкомп’ютери. Дані комп’ютери мають комбіновану архітектуру, яка включає пам’ять, що використовується спільно, і засоби передачі повідомлень для міжпроцесорного зв’язку.Прийнятий підхід заключається в використанні макропотоку даних на рівні груп процесорів і власного керуючого потоку в кожному процесорі. Таким чином, паралелізм має місце на декількох рівнях, в тому числі і з різними обчислювальними моделями. 59. Архітектура суперкомп’ютерів з спільною пам’яттю Архітектура комп’ютерів з спільною пам’яттю передбачає організацію доступу до одних і тих же даних спільної пам’яті з боку декількох процесорів (рисунок 1). Перевага такого підходу в тому, що він дає кожному процесору можливість бачити задачу, яка вирішується, в цілому, а не тільки ті її частини, над котрими він безпосередньо працює. Оскільки існує тільки одна шина, яка зв’язує процесори з пам’яттю, виникає серйозна проблема пропускної здатності даного каналу обміну з пам’яттю. Процесор Процесор . . . Процесор Процесор Шина Пам’ять Рисунок 1. – Архітектура суперкомп’ютера з спільною пам’яттю Просте застосування більш швидкодіючої пам’яті не вирішує проблеми. При цьому проблема залишається, а вартість системи збільшується. Одним із способів вирішити подібну проблему – використання архітектури з кеш-пам’яттю (рисунок 2.). При наявності багатьох кеш-пам’ятей і центральної ( основної ) пам’яті виникає проблема когерентності , тобто відповідності вмістимого кеш-пам’ятей і основної пам’яті. Любі зміни вмістимого своїх кеш-пам’ятей іншими процесорами повинні знаходити відображення в кожній кеш-пам’яті і в основній пам’яті. Процесор Процесор ... Процесор Процесор Кешпам’ять Кешпам’ять . . . Кешпам’ять Кешпам’ять Шина Пам’ять Рисунок 2. – Архітектура суперкомп’ютерів з використанням кеш-пам’яті 60. Архітектура суперкомп’ютерів з розподіленою пам’яттю і слабопов’язаними зв’язками Як спосіб вирішиння проблеми ширини смуги пропускання каналу обміну з пам’яттю – взагалі відмовитися від центральної основної пам’яті. В паралельних системах класу так званих багатомашинних обчислювальних комплексів кожен процесор має власну пам’ять. Процесори взаємодіють різними способами за допомогою шини або по каналах зв’язку з усіма іншими процесорами чи тільки з деякими з інших процесорів. Зв’язки через шину (рисунок 1) Пам’ять Пам’ять . . . Пам’ять Пам’ять Процесор Процесор . . . Процесор Процесор Шина Рисунок 1. В ідеалі було б добре, якби кожен процесор мав прямі канали зв’язку з кожним іншим процесором, однак це практично нездійсненно (по крайній мірі у найближчий час), завдяки великій вартості такого рішення, оскільки для створення мережі з N процесорів необхідно N-1 каналів зв’язку. Певний компроміс представляє мережа з фіксованою топологією, в котрій кожен процесор з’єднується з деякою підмножиною своїх сусідів-процесорв. Якщо двом процесорам, які не мають прямого каналу зв’язку, необхідно взаємодіяти, вони передають повідомлення через поміжні процесори. Такий підхід має ту перевагу, що не накладає явного обмеження на число додаткових процесорів, які можна підключити до системи. А його недолік в тому, що він потребує оптимізації коду прикладних програм, щоб забезпечити виконання процесів, які потребують активних взаємодій, на сусідніх процесорах. Одиним із можливих методів побудови таких комбінованих архітектур є конфігурація з комутацією, коли кожен процесор має свою локальну пам’ять, а з’єднуються процесори за допомогою комутатора. 61. Характеристика і класифікація мікропроцесорів Мікропроцесор (МП) – програмно–керований пристрій, який проводить процес обробки інформації і керування ним, побудований як правило, на одній або декількох ВІС. МП характеризуються за такими ознаками: формат команд і даних, що обробляються, кількість, тип і гнучкість команд, методи адресації даних, число внутрішніх регістрів загального призначення і регістрів результату, можливості організації і адресації стеку, параметри віртуальної пам’яті і інформаційну ємкість пам’яті, що адресується безпосередньо (прямо). МП класифікуються: За призначанням розрізняють універсальні і спеціалізовані МП. Універсальні МП використовуються для рішення широкого кола різноманітних задач. При ньому їх ефективна продуктивність слабо залежить від проблемної специфіки задач. Серед спеціалізованих МП можна виділити різні мікроконтролери, орієнтовані на виконання складних послідовностей логічних операцій; математичні МП, які призначені для підвищення продуктивності при виконанні арифметичних операцій. За видом вхідних сигналів, що обробляються, розрізняють цифрові і аналогові мікропроцесори. Самі мікропроцесори – цифрові пристрої, однак можуть мати вбудовані аналого–цифрові і цифро–аналогові перетворювачі. Тому вхідні аналогові сигнали передаються і МП через перетворювач в цифровій формі, обробляються і після зворотного перетворення в аналогову форму поступають на вихід. З архітектурної точки зору такі мікропроцесори представляють собою аналогові функціональні перетворювачі сигналів і називаються аналоговими мікропроцесорами. За характером часової організації роботи мікропроцесори поділяють на синхронні і асинхронні. Синхронні мікропроцесори – мікропроцесори, в яких початок і кінець виконання операцій задаються пристроєм керування. Асинхронні мікропроцесори – дозволяють початок виконання кожної наступної операції визначити за сигналом фактичного закінчення виконання попередньої операції. За кількістю програм, що виконуються, розрізняють одно – і багатопрограмні мікропроцесори. В однопрограмних мікропроцесорах виконується тільки одна програма. Перехід до виконання другої програми відбувається після завершення текучої програми. В багато – або мультипрограмних мікропроцесорах одночасно виконується декілька програм. 62. Архітектура мікропроцесорів Архітектуру мікропроцесора характеризують: список команд та їхні формати; способи адресації; розрядність і ємність адресованої пам’яті; структура регістрів та їхні функції та ін. Історично першими склалися такі основні архітектури мікропроцесорів: з акумулятором, з РЗП, зі стековою організацією та комбіновані. Структура всіх мікропроцесорів містить такі однакові пристрої, вузли і блоки, об’єднані спільною внутрішньою шиною даних: АЛБ; ПК; IR – регістр команд (інструкцій); FL – регістр ознак (прапорців); EAR – регістр виконавчої адреси; БІФ – блок інтерфейсу з вихідними шинами адреси, даних і керування. В архітектурі мікропроцесора з акумуляторами додатково використовують індексний регістр X і покажчик стека SP; регістр R виконує функції акумулятора А. При виконанні арифметико-логічних операцій перший операнд попередньо розміщується в акумуляторі, а другий – з ОП безпосередньо поступає на вхід АЛБ. Результат операції розміщується в акумуляторі, а в регістр FL автоматично записуються ознаки операції. В архітектурі мікропроцесора з РЗП звичайно використовують від восьми до 16 регістрів, кожний з яких може виконувати функції акумулятора. Збільшення числа РЗП значно зменшує кількість звернень до ОП, що підвищує продуктивність комп’ютера. Але збільшення числа регістрів призводить до втрат машинного часу у випадках переривання програм: при цьому необхідно зберегти зміст РЗП в пам’яті (звичайно у стеку), а потім відновити його після обробки переривання. Тому при виборі кількості РЗП враховують цей фактор.У мікропроцесорі зі стековою архітектурою відсутні акумулятор і РЗП, а R виконує функції регістра тимчасового зберігання даних ОП на час виконання операції. Читання даних і їхнє записування у стекову пам’ять здійснюють за допомогою покажчика стека SP. Усі операції з даними виконують відповідно до польського запису: операнди розміщують у стеку в послідовності виконання над ними дій. Сукупність обчислювальних засобів, куди входять один або декілька мікропроцесорів та напівпровідникова пам’ять і засоби інтерфейса, називається мікропроцесорною системою (МПС). 63. Структура мікропроцесора Структура мікропроцесора (К1810ВМ86), складається з наступних основних пристроїв: обробки інформації (ПО), зв'язку з каналом (ПЗК), керування та синхронізації (ПКС). Пристрій обробки інформації (ПО) призначений для обробки даних та формування виконавчих адрес. До його складу входять: шістнадцятирозрядний арифметико-логічний пристрій (АЛП), мікропрограмний пристрій керування та блок регістрів. АЛП виконує арифметичні та логічні операції з восьми- та шістнадцятирозрядними операндами. За результатами формуються ознаки, котрі записуються в регістр F. Блок регістрів містить програмно-доступні регістри трьох типів: регістри загального призначення AH, AL, BH, BL, CH, CL, DH, DL, SF, BP, DI, SI, регістр ознак F, сегментні регістри CS, DS, SS, ES. Мікропрограмний пристрій керування - це сукупність мікропрограмного пристрою керування та апаратно-реалізованих засобів керування. Пристрій керування та синхронізації керує роботою мікропроцесора. Пристрій дешифрує команди, а також сприймає та обробляє необхідні керуючі сигнали. До його складу входить блок мікропрограмного керування, в якому реалізовано програмування на мікрокомандному рівні. Пристрій зв'язку з каналом виконує операції обміну з зовнішньою пам'яттю, вибірки команд та завантаження їх у чергу. Черга команд являє собою набір байтових регістрів і виконує роль регістра команд. Довжина черги становить 6 байт, що відповідає формату максимально довгої команди. Наявність черги команд, а також здатність ПО та ПЗК працювати паралельно дозволяють сумістити у часі фази вибірки команди та виконання заданої операції; поки одна команда виконується у пристрої обробки, ПЗК здійснює вибірку наступної команди. Таким чином досягається висока щільність завантаження шини та збільшення швидкості виконання програми. Для збереження команд, які пересилаються, а також адрес у складі ПЗК є два буферних регістри (БР). 64. Система команд До системи команд МП К1810ВМ86 входять 113 базових команди, багато з яких дозволяють різноманітні режими адресації. За функціональним призначенням команди можна згрупувати у п’ять функціональних груп: Команди передачі даних: Мікропроцесор має велику групу команд призначених для пересилань між регістрами та між регістрами і пам'яттю: Команда MOV (move - переносити) (формат: MOV dst,src (dst) <--(src)) може пересилати байт чи слово між регістром і коміркою пам'яті чи між двома регістрами. Вона може також пересилати безпосередні дані в регістр чи комірку пам'яті; Команда XCHG (exchange обміняти) (XCHG dst,src (dst)<->(src) ) дозволяє обміняти вміст двох регістрів чи регістра та комірку пам'яті. Команда XLAT (має формат: XLAT таблиця_джерело), де таблиця_джерело ім'я таблиці, що розглядається. Команди LEA (load effective addres завантажити виконавчу адресу), LDS (load pointer using DS - завантажити вказівник з використанням регістра DS) та LES (load pointer using ES завантажити вказівник з використанням регістра ES). При виконанні цих команд до вказаних регістрів передаються не дані, а адреси. Арифметичні команди: Арифметичні операції виконуються над цілими числами в чотирьох форматах: беззнакові подвійні, знакові двійкові, упаковані двійково-десяткові та неупаковані двійково-десяткові. Додавання та віднімання знакових та беззнакових чисел виконують однакові команди, а для множення та ділення передбачені окремі команди. Команди додаванн: Мікропроцесор має команду ADD (add - додати), власне додавання та команди ADC додавання з переносом. ADD dst,src ; (dst)<-(dst) + (src). Команди віднімання: До команд віднімання (subtract - відняти, decrement - зменшити) належать: SUB dst,src; (dst) <-- (dst) - (src). До команд віднімання традиційно відносять команду NEG зміни знака, так як її дія еквівалентна відніманню операнда від 0. NEG dst; dst <-- 0 - (dst) Команди множення: Мікропроцесор К1810ВМ86 має дві команди множення: MUL (multiply помножити) помножує числа без знака, IMUL (integer multiply - помножити цілі числа) - числа зі знаком. Обидві команди можуть множити як байти, так і слова. Команди ділення: Мікропроцесор має дві команди ділення. Команда DIV (division ділення) виконує ділення чисел без знака, а команда IDIV (integer division ділення цілих чисел) - ділення чисел зі знаком. Ці команди мають формат: DIV src; IDIV src, де src (джерело) - дільник (розміром у байт чи слово). 65. Способи адресації Існують 4 основних способи адресації: 1 . Реєстрова адресація - у команді в якості джерел операндів вказані регістри загального призначення. Гідність - однобайтное команда , і , як наслідок , малий час виконання команди , а недолік - обмежена кількість РОНов . Приклад реєстрової адресації - MOV B , L. ; переслати байт з регістра (L) в регістр (B). 2 . Безпосередня адресація - в команді вказується сам операнд у вигляді константи . Команди двобайтні . Приклад безпосередньої адресації - MVI H , 35h ; записати в регістр ( H) число 35h . 3 . Пряма адресація - в команді вказується адреса комірки пам'яті , в якій знаходиться операнд . Команди трехбайтние . Вони забезпечують довільних доступ до будь-якій комірці пам'яті в межах адресного простору , але мають максимальний час виконання . Приклад прямої адресації - LDA F8E4h ; переслати в акумулятор байт з комірки пам'яті з адресою F8E4h . 4 . Непряма адресація - у команді вказуються регістри , в яких зберігається адреса комірки пам'яті , в якій знаходиться операнд . Команди з непрямою адресацією однобайтние . Для реалізації непрямої адресації в структурі мікропроцесора необхідно мати регістри з розрядністю ША і можливістю використання їх як джерело адреси. Такими регістрами в МП КР1821ВМ85 є пара регістрів загального призначення ( HL ) . Команди з цими регістрами у випадку непрямої адресації мають позначення (M). MOV M , E; - переслати з регістра ( E) дані в комірку пам'яті з адресою, що зберігається в парі регістрів ( HL ) ; MOV D , M ; - переслати дані з комірки пам'яті з адресою, що зберігається в парі регістрів ( HL ) , в регістр ( D). 5 . Введення-виведення даних. Команди використовуються для звернення до УВВ . Розрізняють 2 способи звернення до зовнішніх пристроїв :a ) звернення до УВВ , що не входять в адресний простір МП , при цьому використовуються команди IN N8 ; P [ N8 ] -> (A ) , введення байта в акумулятор з УВВ , де N8 - 8 - розрядний номер зовнішнього пристрою; OUT N8 ; (A ) -> P [ N8 ] , висновок байта. Для цього способу введення- виведення даних при виконанні команд номер N8 встановлюється на молодшому байті ША і дублюється на старшому байті ША; б) звернення до УВВ як до комірок пам'яті , при цьому УВВ входять в адресний простір МП : LDA A16 ; P [ A16 ] -> (A ) , STA A16 ; (A ) -> P [ A16 ] . 66. Структура МПС Мікропроцесор - центральна частина будь мікропроцесорної системи (МПС. МП може функціонувати тільки в складі МПС, що включає в себе, крім МП, пам'ять, пристрої введення / виводу, допоміжні схеми (тактовий генератор, контролери переривань, шинні формувачі, регістри-засувки та ін.) У будь-якому МПС можна виділити наступні основні частини (підсистеми): процесорний модуль; пам'ять; зовнішні пристрої (пристрої введення / виводу,..); підсистему переривань; підсистему прямого доступу в пам'ять. Зв'язок між процесором та іншими пристроями МПС може здійснюватися за принципами радіальних зв'язків, загальної шини або комбінованим способом. У однопроцесорних МПС, особливо 8 - і 16-розрядних, найбільшого поширення набув принцип зв'язку "Загальна шина", при якому всі пристрої підключаються до інтерфейсу однаковим чином. Обмін інформацією по інтерфейсу виробляється між двома пристроями, один з яких є активним , а інше - пасивним. Активний пристрій формує адреси пасивних пристроїв і керуючі сигнали. Активним пристроєм виступає , як правило , процесор , а пасивним - завжди пам'ять і деякі ВУ . Однак, іноді швидкодіючі ВУ можуть виступати в якості задатчика (активного пристрою) на інтерфейсі , керуючи обміном з пам'яттю (т.зв. режим прямого доступу в пам'ять - див. розділ 8 ) . Концепція "Загальної шини " припускає, що звернення до всіх пристроїв МПС виробляється в єдиному адресному просторі , проте , з метою розширення числа адресованих об'єктів , в деяких системах штучно розділяють адресні простори пам'яті і ВУ , а іноді навіть і пам'яті програм і пам'яті даних. 67. Тришинна структура МПС МПС з трьома шинами : шина адреси ША . По ній передається інформація про адресу комірки пам'яті або УВВ , з яким зараз відбувається обмін даними. Розрядність ША m визначає число елементів пам'яті і (або) УВВ , які можуть бути безпосередньо адресовані мікропроцесором. N = 2 m ; шина даних ШД . По ній передається оброблювана інформація та результати обчислень. Ця шина двунаправленная . Розрядність ШД n визначає ту порцію інформації , яка може бути прочитана , оброблена чи записана за одну операцію. Розрядність ШД визначає розрядність машинного слова . Зазвичай розрядність n = 8 , 16 , 32 ... . Чим вище розрядність , тим більша порція інформації обробляється однією командою. Зазвичай при інших рівних умовах МП з більшою розрядністю ШД має і велику продуктивність ; - шина управління ШУ . По цій шині передаються сигнали управління , які визначають напрями обміну інформацією по ШД , наприклад ЧИТАННЯ (ЧТ ) і ЗАПИС ( ЗП) , а також інші сигнали управління ( переривання , підтвердження закінчення поточної операції при асинхронному обміні , запити прямого доступу в пам'ять ( ПДП) ) , налаштовуючи пристрої , що беруть участь в обміні , на потрібний режим. При реалізації обміну даними між МП і іншими пристроями (ЗУ і УВВ) може виникнути плутанина щодо напрямку обміну. Так, при передачі інформації з комірки пам'яті в МП для МП це операція введення, а для ЗУ операція виводу. Щоб уникнути подібної плутанини напрямок обміну завжди визначається відносно МП! Центральний процесорний елемент ( ЦПЕ ) складається з власне МП , генератора тактових сигналів і буферних підсилювачів , що забезпечують формування шин. Підсилювачі необхідні у зв'язку з обмеженою здатністю навантаження виходів МП і широкої розгалуженістю шин. Для шини даних підсилювач повинен бути двонаправленим . Генератор тактових сигналів формує тактові імпульси , що задають ритм роботи МП і всієї МПС. Генератори бувають однофазні f =1 і багатофазні - f > 1 . 68. Двошинна структура МПС Розвиток обчислювальних можливостей МП призводить до збільшення розрядностей як шини адреси, так і шини даних . При цьому відповідно зростає число " ніжок " МП , а для зв'язку між окремими елементами МПС по друкованій платі необхідно розводити все більша кількість провідників. Для зменшення кількості зв'язків і " ніжок " МП використовується 2 шинна структура МПС. При використанні цієї структури поєднуються шини адреси і даних і замість просторового розділення сигналів цих шин використовується тимчасове. Об'єднана шина Ш А / Д в кожній операції введення і виведення даних спочатку передає адресу , а потім дані ( рис. 13). Про те , що в поточний момент часу на Ш А / Д виставлений адресу , свідчить сигнал ALE =1. Розглянемо використання 2 - шинної структури на прикладі системи пам'яті. При реалізації 2 - шинної структури МПС в реальності все одно необхідно сформувати шину адреси , на якій на весь період обміну значення коду адреси буде фіксованим. Для цього використовується окремий буферний регістр для фіксації адреси. На вхід цього регістра підключається шина ^ Ш А / Д і сигнал ALE . Відповідно до тимчасової діаграмою руху інформації (рис. 13 ) на початку кожного циклу обміну сигнал ALE супроводжує адресу на шині Ш А / Д. Він і управляє записом адреси в буферний регістр адреси. Інформація в регістрі зберігається до наступного циклу обміну , в ході якого зміниться адреса комірки пам'яті і його запис буде здійснена новим сигналом ALE = 1 . Між двома сигналами ALE значення адреси буде зафіксовано на виході регістра . В іншому 2 - шинна структура МПС аналогічна 3 - шинної . 69. Однопроцесорні мікропроцесорні системи Історично першими з'явилися однопроцесорні архітектури. Класичним прикладом однопроцессорной архітектури є архітектура фон Неймана зі строго послідовним виконанням команд : процесор по черзі вибирає команди програми і також по черзі обробляє дані (програма і дані зберігаються в єдиній послідовно адресується пам'яті ) . У міру розвитку обчислювальної техніки архітектура фон Неймана збагатилася спочатку конвеєром команд , а потім багатофункціональної обробкою , і з таксономії * М.Фліна отримала узагальнену назву комп'ютера з одним потоком команд і одним потоком даних. Потік команд - це послідовність команд , виконуваних ЕОМ ( системою ) , а потік даних - послідовність даних ( початкова інформація і проміжні результати вирішення задачі) , оброблюваних під управлінням потоку команд. Точно також, як однопроцесорні комп'ютери, представлені архитектурами з одним потоком даних SISD і безліччю потоків даних SIMD, так і багатопроцесорні системи можуть бути представлені двома базовими типами архітектур залежно від паралелізму даних 70. Зосереджені мікропроцесорні системи Мікропроце́сорна систе́ма (МП-система) - спеціалізована інформаційна або керуюча система, побудована на основі мікропроцесорних засобів, тобто набору мікропроцесорних схем. За своєю будовою електронні системи поділяють на системи на “жорсткій логіці” та мікропроцесорні системи. Характерною особливістю традиційної цифрової системи на відміну від мікропроцесорної є те, що алгоритми обробки й зберігання інформації в ній жорстко зв'язані зі схемотехнікою системи. Тобто, зміна цих алгоритмів можлива тільки шляхом зміни структури системи, заміни електронних вузлів, що входять у систему, і/або зв'язків між ними. Саме тому традиційна цифрова система часто називається системою на "жорсткій логіці". Зменшення вартості, споживаної потужності й габаритних розмірів, підвищення надійності й продуктивності мікропроцесорів сприяли значному розширенню сфери їхнього використання. Поряд із традиційними обчислювальними системами вони все частіше стали використовуватися в задачах керування та обробки. При цьому перед мікропроцесором ставилася задача програмного управління різними периферійними об'єктами в реальному масштабі часу. Широке використання мікропроцесорної техніки саме для завдань керування привело до появи на ринку спеціалізованих мікропроцесорних пристроїв, орієнтованих на подібного роду застосування. Особливістю цих мікросхем є те, що крім власне процесора, на цьому ж кристалі розташована й система введення-виведення, що дозволяє знизити функціональну складність і габаритні розміри мікропроцесорної системи керування. Подібні пристрої називаються мікроконтролерами. З'явився ряд мікроконтролерів, спеціалізованих для завдань керування напівпровідниковими перетворювачами. Їхнє обчислювальне ядро, побудоване, як правило, на базі так званих "процесорів цифрової обробки сигналів", адаптовано на виконання рекурентних поліноміальних алгоритмів цифрового регулювання. Вбудовані периферійні пристрої містять у собі багатоканальні генератори ШІМ-сигналів, аналого-цифрові перетворювачі, блоки векторних перетворень координат, таймери-лічильники тощо. 72. Основні властивості процесорів з RISC-архітектурою Мікропроцесори з архітектурою RISC (Reduced Instruction Computers) використовують порівняно невеликий (скорочений) набір команд, який визначається в результаті статистичного аналізу великого числа програм для основних областей застосування CISC– процесорів. Всі команди працюють з операндами, які розміщені в регістрах процесора, і мають однаковий формат. Звернення до пам’яті виконується за допомогою спеціальних команд завантаження регістру і запису. Простота структури і невеликий набір команд дозволяє реалізувати повністю їх апаратне виконання і ефективний конвеєр при порівняно невеликому об’ємі обладнання. Тому RISC– процесори в 2–4 рази швидкодіючі в порівнянні з CISC– процесорами при однаковій тактовій частоті. Основними особливостями RISC – систем є необхідність великого числа регістрів (більше 100), максимальне використання цих регістрів і мінімальне число звернень до оперативної пам’яті, оптимізація конвеєрного режиму виконання команд. Існуючим типам систем з архітектурною RISC спеціалісти приписують вісім основних ознак: – відносно невелике число команд (бажано < 100, але допускається 150 і більше); – невелике число режимів адресації (бажано один–два, допускається 4); – невелике число форматів команд (один–два, допускається 4); – виконання всіх команд за один машинний цикл; – доступ до ЗП тільки по команді завантаження/зберігання; – відносно великий регістровий файл ЦП (>32 регістрів), виконання всіх операцій по типу регістр–регістр; – жорстко комутований блок керування; програмне керування з використанням операцій на мові високого рівня. 73. Переваги і недоліки RISC-архітектури Переваги RISC-архітектури: порівняна простота апаратної реалізації; швидке дешифрування команд; коротка тривалість такту і відповідно швидке киконання команд; можливість створення ефективного конвеєра команд. Недоліки RISC-архітектури: порівняно мала швидкість обміну операндами з оперативною пам’яттю; додаткові вимоги до програмного забезпечення. Одним з факторів, які вплинули на розробку архітектури, був розвиток технології НВІС і можливість, завдяки цьому, значно спростити блок керування. Починаючи з 1987 року і по сьогоднішній час на ринку RISC–МП з’явилася велика кількість моделей МП різних фірм виробників МП – техніки. Серед відомих виробників фірми ІВМ, Intel (МП 80860), Motorola (МП 88000) та ряд інших фірм. 74. Структура RISC-процесора Арифметику RISC - процесорів вирізняє високий ступінь дроблення конвеєра. Цей прийом дозволяє збільшити тактову частоту (отже, і продуктивність) комп'ютера; чим елементарніші дії виконуються в кожній фазі роботи конвеєра, - тим вищою є частота його роботи. RISC - процесори із самого початку були орієнтовані на реалізацію всіх можливостей прискорення арифметичних операцій, тому їхні конвеєри мають значно вищу швидкодію, ніж CISC-процесори. Тому RISC - процесори в 2—4 рази швидші, ніж CISCпроцесори зі звичайною системою команд, що мають таку ж саму тактову частоту, і більш високопродуктивні, незважаючи на більший розмір програм. RISCархітектура побудована на 4 основних принципах: 1. Будь-яка операція повинна виконуватися за один такт, незалежно від її типу. 2. Система команд повинна містити мінімальну кількість найчастіше використовуваних найпростіших інструкцій однакової довжини.* 3. Операції обробки даних реалізуються тільки у форматі «регістр — регістр» (операнди вибираються з оперативних регістрів процесора, і результат операції записується також у регістр; а обмін між оперативними регістрами й пам'яттю виконується тільки за допомогою команд завантаження/запису). 4. Склад системи команд повинен бути «зручним» для компіляції операторів мов високого рівня. Ускладнення RISC- процесорів фактично наближає їхню архітектуру до CISCархітектури. 75. RISC-мікропроцесори RISC - архітектура процесора , в якій швидкодія збільшується за рахунок спрощення інструкцій , щоб їх декодування було більш простим , а час виконання - меншим . Перші RISC - процесори навіть не мали інструкцій множення і ділення . Це також полегшує підвищення тактової частоти і робить ефективнішою суперскалярність ( розпаралелювання інструкцій між кількома виконавчими блоками) . Набір інструкцій у більш ранніх архітектурах , для полегшення ручного написання програм мовами ассемблер або прямо в машинних кодах , а також для спрощення реалізації компіляторів , виконування якнайбільше роботи . Нерідко в набори включалися інструкції для прямої підтримки конструкцій мов високого рівня. Інша особливість цих наборів - більшість інструкцій , як правило , допускали всі можливі методи адресації наприклад : операнди , і результат в арифметичних операціях доступні не тільки в регістрах , але і через безпосередню адресацію , і прямо в пам'яті. Пізніше такі архітектури були названі CISC (англ. Complex instruction set computer ) . Однак багато компіляторів не задіяли всі можливості таких наборів інструкцій , а на складні методи адресації йде багато часу через додаткових звернень до повільної пам'яті. Було показано , що такі функції краще виконувати послідовністю більш простих інструкцій , якщо при цьому процесор спрощується і в ньому залишається місце для більшого числа регістрів , за рахунок яких можна скоротити кількість звернень до пам'яті. У перших архітектурах , що зараховуються до RISC , більшість інструкцій для спрощення декодування мають однакову довжину і схожу структуру , арифметичні операції працюють тільки з регістрами , а робота з пам'яттю йде через окремі інструкції завантаження ( load ) і збереження ( store ) . Ці властивості і дозволили краще збалансувати етапи конвейеризации , зробивши конвеєри в RISC значно ефективнішими і дозволивши підняти тактову частоту. 76. Паралелізм архітектури комп’ютера Для розвитку архітектури сучасних суперкомп’ютерів характерною є тенденція до збільшення апаратних і програмних функцій, які вбудовуються в комп’ютер чи систему. В основу більшості сучасних суперкомп’ютерів покладені методи попереднього перегляду, функціональний паралелізм, конвеєрна обробка на різних рівнях, векторна і паралельна обробка в режимах ОКМД (SIMD) ( один потік команд і множина потоків даних) і МКМД (MIMD) (множина потоків команд і множина потоків даних). В більшості суперкомп’ютерів паралельна скалярна і векторна обробка здійснюється завдяки використанню великого числа функціональних пристроїв, котрі входять в одно процесорну чи багатопроцесорну системи. Під паралелізмом розуміється одночасна обробка завдань, кроків завдань, програм, підпрограм, циклів чи операторів (рисунок 13.2.1). Чим нижче рівень, тим мілкіше дроблення програмних процесів. В загальному випадку паралельна обробка заключається в реалізації паралелізму на любому із даних рівнів або в їх поєднанні. Векторна обробка заключається в паралельній обробці ітерацій циклів на рівні 2. В багатьох комп’ютерах , в основу яких покладений метод попереднього перегляду і які включають велике число функціональних пристроїв, здійснюється паралельне виконання незалежних скалярних операторів на рівні 1. Більшість сучасних комп’ютерів допускають мультипрограмування, яке передбачає розділення ресурсів процесора між декількома незалежними процесорами. Подібна процедура має місце і в одно процесорних системах, де використовується суміщення роботи ЦП і пристроїв введення-виведення. Багатопроцесорна обробка представляє собою спосіб паралельної обробки, при якому забезпечується мультипрограмний режим роботи двох і більше взаємодіючих між собою процесорів П’ять рівнів паралелізму при виконанні програм Рівень 5 - Незалежні завдання і програми Рівень 4 - Кроки завдань і зв’язані частини програм Рівень 3 - Програми і підпрограми Рівень 2 - Цикли інтеграції Рівень 1 - Оператори і команди При незалежній одно процесорній обробці знаходить застосування паралелізм на рівні 1, який реалізується шляхом використання декількох режимів типу ОКОД (одн потік команд один потік даних). 77. Класифікація паралельних комп’ютерних систем Класифікація Шора Одна з перших класифікацій комп'ютерних систем була запропонована Д. Шорам на початку 70-х років. Вона цікава тим, що є спробою виділення типових способів компонування комп'ютерних систем на основі фіксованого числа базових блоків: пристрою керування, арифметико-логічного пристрою, пам'яті команд і пам'яті даних. Додатково передбачається, що вибірка з пам'яті даних може здійснюватися словами, тобто вибираються всі розряди одного слова, і/або бітовим шаром - по одному розряду з однієї і тієї ж позиції кожного слова (іноді ці два способи називають горизонтальною і вертикальною вибірками відповідно). Звичайно ж, при аналізі даної класифікації треба робити знижку на час і появи, оскільки передбачити велику різноманітність паралельних систем теперішнього часу тоді було у принципі неможливо. Отже, згідно з класифікацією Д. Шора, всі комп ютери розбиваються на шість класів, перший з яких дістав назву машини І, другий - машини II, і т.д. Зчитування даних здійснюється вибіркою всіх розрядів деякого слова для їх паралельної обробки в арифметико-логічному пристрої. Склад АЛП спеціально не вказується, що допускає наявність декількох функціональних пристроїв, в тому числі конвеєрного типу. За цими міркуваннями до даного класу потрапляють як класичні послідовні машини (ІВМ 701, PDP-11, VAX 11/780), так і конвеєрні скалярні (CDC 7600) і векторно-конвеєрні (CRAY-1). Класифікація Фліна Одну з перших практично значимих класифікацій паралельних комп'ютерних систем подав у 1966 році співробітник фірми ІВМ Майкл Флін, який зараз є професором Стенфордського університету (США). Його класифікація базується на оцінці потоку інформації, який поділено на потоки даних між основною пам'яттю та процесором, та потік команд, які виконує процесор. При цьому потік даних та команд може бути як одиничним, так і множинним. Згідно з М. Фліном, усі комп'ютерні системи поділяють так: ОКОД - комп'ютерні системи з одиничним потоком команд та одиничним потоком даних (SISD - Single Instruction Single Data stream). МКОД - комп'ютерні системи з множинним потоком команд та одиничним потоком даних (MISD - Multiply Instruction Single Data stream). ОКМД - комп'ютерні системи з одиничним потоком команд та множинним потоком даних (SIMD - Single Instruction Multiply Data stream). МКМД - комп'ютерні системи з множинним потоком команд та множинним потоком даних (MIMD - Multiply Instruction Multiply Data stream). 78. Архітектури типу ОКМД До комп’ютерних систем класу ОКМД слід віднести векторні та матричні комп’ютерні системи. Призначення даних систем в основному схоже це – обробка великих масивів інформації. В основі матричних комп’ютерних систем лежить матричний процесор, який складається з регулярного масиву процесорних елементів (ПЕ). Системи типу ОКМД мають пристрій керування, що генерує потік команд і велике число ПЕ, які працюють паралельно і обробляють кожен свій потік даних. Проте на практиці, щоб забезпечити велику ефективність системи при вирішенні широкого кола задач, необхідно організувати зв’язки між ПЕ так, щоб по максимуму завантажити їх роботою. Саме характер зв’язків між ПЕ і визначає різницю у властивостях системи. Між матричними і векторними комп’ютерними системами є істотна різниця. В складі системи команд векторного процесора є команди обробки векторів даних, що дозволяє ефективно завантажити конвеєри його операційних блоків. Векторні процесори простіше використовувати, тому що команди для обробки векторів – це зручніша модель програмування, ніж команди для паралельно включених ПЕ. Матричний процесор інтегрує безліч ідентичних процесорних елементів, які об’єднані у матрицю і працюють в стилі ОКМД. Є дві голвні конфігурації, які були використанів матричних комп’ютерних системах типу ОКМД. Процесори зв’язуються один з одним через комунікаційну мережу. Якщо комунікаційна мережа не забезпечує прямого зв’язку між заданою парою процесорів, то ця пара може обмінюватися даними через проміжний процесор. У другій схемі процесори і модулі пам’яті зв’язуються між собою через комунікаційну мережу. Два процесори можуть передати дані один одному через проміжний модуль пам’яті або, можливо, через проміжний процесор. 79. Архітектури типу МКМД Комп’ютерні системи типу МКМД складаються з багатьох процесорів та багатьох модулів пам’яті, з’єднаних за допомогою комунікаційної мережі. Вони можуть бути поділені на дві великі групи: із спільною пам’яттю та з передачею повідомлень. В першій групі процесори обмінюються через спільну пам’ять, причому кожний процесор має рівні можливості зчитувати та ззаписувати дані до пам’яті, а також однакову швидкість доступу до пам’яті, тому їх часто називають симетричними багатопроцесорними системами. У другій групі процесори обмінюються інформацією через комунікаційну мережу. В КС з передачею повідомлень (системи з розподіленою пам’яттю) зазвичай наявна локальна пам’ть і процесор у кожному вузлі комунікаційної мережі. Спільна пам’ять тут відсутня і тому необхідно переміщувати дані з однієї локальної пам’яті до іншої за допомогою механізму передачі повідомлень. 80. Шина процесора і пам’яті Комп'ютерна шина (англ. computer bus) служить для передачі даних між окремими функціональними блоками комп'ютера і є сукупністю сигнальних ліній, які мають певні електричні характеристики і протоколи передачі інформації. Шини можуть розрізнятися розрядністю, способом передачі сигналу (послідовні або паралельні, синхронні або асинхронні), пропускною здатністю, кількістю і типами підтримуваних пристроїв, протоколом роботи, призначенням (внутрішня або інтерфейсна). Шиною звався інформаційний канал, до якого приєднувалася низка пристроїв, які могли читати та передавати дані. Існують і спеціалізовані шини, такі як внутрішні шини процесорів або шина для підключення відеоадаптерів — AGP. Усі стандарти розрізняються як за кількістю й використанням сигналів, так і за протоколами їхнього обслуговування. Шина входить до складу материнської плати, на якій розташовуються її провідники і роз'єми (слоти) для підключення плат адаптерів пристроїв (відеокарти, звукові карти, внутрішні модеми, накопичувачі інформації, пристрої введення/виведення і т. д.) і розширень базової конфігурації (додаткові пусті роз'єми). Існують 16- і 32-розрядні, високопродуктивні (VESA, VLB, AGP і РСІ із тактовою частотою більше 16 МГц) і низькопродуктивні (ISA і EISA із тактовою частотою 8 і 16 МГц) системні шини. Також шини, розроблені за сучасними стандартами (VESA, VLB і РСІ), допускають підключення декількох однакових пристроїв, наприклад декілька жорстких дисків, а шина РСІ забезпечує самостійну конфігурацію периферійного (додаткового) устаткування — підтримку стандарту Plug and Play, що виключає ручну конфігурацію апаратних параметрів периферійного устаткування при його зміні або нарощуванні. Операційна система, яка підтримує цей стандарт, сама налаштовує устаткування, підключене через шину РСІ, без втручання користувача. Існують як 64-розрядні розширення шини РСІ, так і 32-розрядні, що працюють на частоті 66 МГц.