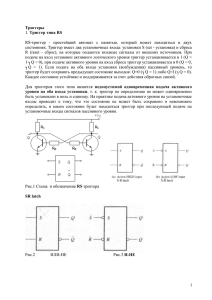

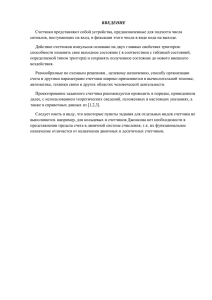

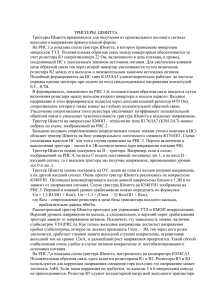

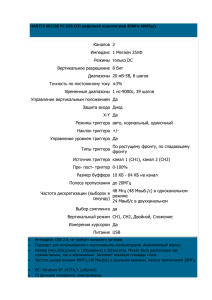

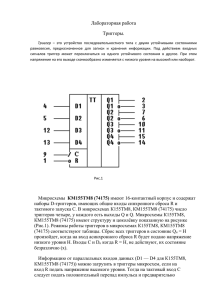

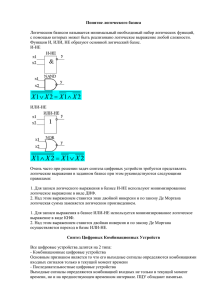

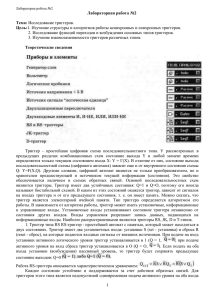

Микропроцессорные устройства в системах мобильной связи конспект лекций СПИСОК ПРИНЯТЫХ СОКРАЩЕНИЙ А АШ АЦП БВВ (IOB) БИС БМК БЯ ВУ ДНФ ДОЗУ(DRAM) ЗУ ЗЭ ИС КЛБ КМОП КПДП (DMA) КЦ ЛБ ЛЗС ЛИЗМОП ЛФ ЛЭ МК МНОП МОП МПК МПС МЦ МЭТ ОЗУ ОК ПБЯ ПДП (DMA) ПЗУ (ROM) ПЗУМ ПКП (PIC) ПЛМ (PLA) ПМЛ (PAL) ППА (PPI) ППВМ (FPGA) ППЗУ (PROM) ПСА (PCI) адрес адресная шина аналого-цифровой преобразователь блок ввода/вывода большая интегральная схема базовый матричный кристалл базовая ячейка ЗУ внешнее устройство дизъюнктивная нормальная форма динамическое ОЗУ запоминающее устройство запоминающий элемент интегральная схема конфигурируемый логический блок комплементарная МОП – структура контроллер прямого доступа к памяти командный цикл логический блок линия записи – считывания МОП – структура с лавинной инжекцией заряда логическая функция логический элемент микроконтроллер структура «металл–нитрид–оксид-полупроводник металл – окисел – полупроводник микропроцессорный комплект микропроцессорная система машинный цикл многоэмиттерный транзистор оперативное ЗУ открытый коллектор периферийная базовая ячейка прямой доступ к памяти постоянное ЗУ масочное ПЗУ программируемый контроллер прерываний программируемая логическая матрица программируемая матричная логика программируемый параллельный адаптер программируемая пользователем вентильная матрица программируемое постоянное ЗУ программируемый связной адаптер РОН РПЗУ-УФ (EPROM) РПЗУ-ЭС (EEPROM) СБИС СДНФ СОЗУ (SRAM) ТС ТТЛ ТТЛШ УВВ УС ЦАП ЦУ ША (AB) ШД (DB) ШУ (CB) ШФ ЭСЛ регистр общего назначения репрограммируемое ПЗУ со стиранием данных ультрафиолетовыми лучами репрограммируемое ПЗУ c электрическим стиранием данных сверхбольшая интегральная схема совершенная дизъюнктивная нормальная форма статическое ОЗУ третье состояние ЛЭ транзисторно-транзисторная логика ТТЛ с диодами Шотки устройство ввода/вывода управляющее слово цифроаналоговый преобразователь цифровое устройство (узел) шина адреса шина данных шина управления шинный формирователь эмиттерно-связанная логика ГЛАВА I. ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ 1.1. Понятие об алгебре логики Математический аппарат, описывающий теорию и работу цифровых устройств, базируется на алгебре логики или булевой алгебре по имени автора – английского математика Джорджа Буля (1815 – 1864). Джордж Буль – отец писательницы Этель Буль, широко известной в нашей стране под псевдонимом Э. Войнич как автор романа "Овод". В 1847 г. Джордж Буль опубликовал работу "Математический анализ логики", а в 1854 г. – "Исследование законов мышления", в которых изложил основы алгебры логики. В дальнейшем идеи алгебры логики, получившей наименование булевой алгебры, развивались рядом ученых. Значительный вклад в развитие булевой алгебры в ХХ веке внесли преподаватель Казанского университета П.С. Порецкий и профессор Московского университета И.И. Жегалкин. Впервые на возможность использования алгебры логики для решения технических задач указал в 1910 году П. Эренфест в рецензии на русский перевод книги Л. Кутюра "Алгебра логики". В дальнейшем, однако, идея Эренфеста оказалась забытой. Лишь в 1938 году были выполнены первые исследования по приложениям булевой алгебры к потребностям релейной техники. Их авторами были в нашей стране – В.И. Шестаков (диссертация "Некоторые математические методы конструирования и упрощения двухполюсных электрических схем класса А"), а в США – Клод Шеннон (статья "Символический анализ электрических цепей с контактными выключателями"). Внедрение булевой алгебры в практику проектирования релейных устройств на начальном этапе (40-е годы) обязано усилиям М.А. Гаврилова. Разработка методов приложения булевой алгебры к задачам телемеханики и иллюстрации этих приложений конкретными примерами нашли отражение в его монографии "Теория релейно-контактных схем", опубликованной в 1950г. В 50-х годах основным источником новых задач теории логического проектирования переключательных устройств стали потребности рационального построения электронных вычислительных машин. Благодаря привлечению крупных сил математиков и специалистов электронной техники были разработаны методы, ставшие классической основой теории логического проектирования. Современное состояние теории цифровых автоматов отражено в работах Д.Хоффмана, В.Квайна, Е.Вейча, М.Карно, В.М.Глушкова и др. Алгебра Буля имеет своей целью исследование различного рода ситуаций, которые задаются высказываниями. Высказыванием называется любое утверждение, о котором можно сказать, истинно оно или ложно. При этом полагается, что каждое выска- зывание в данный момент времени может быть либо только истинным, либо только должным и не может быть одновременно и тем, и другим. Значение истинности высказывания может рассматриваться как двоичная (логическая) переменная, принимающая в каждой конкретной ситуации одно из двух значений: 1 – если высказывание истинно, 0 – если высказывание ложно. Высказывания могут быть простыми и сложными. Простым высказыванием называется такое высказывание, значение истинности которого нее зависит от значений истинности двух высказываний. Сложным высказыванием называется высказывание, значение истинности которого зависит от значений истинности составляющих его простых высказываний. Таким образом, значение истинности сложного высказывания является двоичной (булевой) функцией значений истинности простых высказываний, играющих роль аргументов. Высказывания различной сложности могут образовываться из простых высказываний с помощью определенных логических связей (операций). В булевой алгебре рассматриваются не сами словесные высказывания и взаимосвязи между ними, а двоичные логические переменные (аргументы), отображающие ложность или истинность этих высказываний, и логические операции над ними. Так как значение истинности каждого высказывания является двоичной переменной, то это дает возможность применить методы алгебры логики для исследования схем, использующих двоичные сигналы. В этом случае алгебра логики оперирует не с высказываниями, а с сигналами, которые обозначаются как двоичные переменные X n 1 , X n 2 , … X 1 , X 0 . Нумерацию переменных целесообразно осуществлять в соответствии со значениями разрядов двоичного числа, образуемого этими переменными при их позиционной записи. Значения этих переменных отождествляются со значениями входных сигналов, поступающих на схему. Связи между входными и выходными сигналами в цифровых схемах аналитически описываются логическими (булевыми) функциями. Таким образом, значение булевой функции f X n 1 , X n 2 ,..., X 1 , X 0 будет соответствовать значению выходного сигнала цифровой схемы, на которую поступают входные сигналы X n 1 , X n 2 ,..., X 1 , X 0 . 1.2. Основные операции алгебры логики Действия над двоичными переменными производятся по правилам логических операций. Между обычной, привычной алгеброй и алгеброй логики имеются существенные различия в отношении количества и характера операций, а также законов, которыми они подчиняются. Простейшими логическими операциями являются: отрицание (инверсия, операция НЕ); логическое умножение (конъюнкция, операция И); логическое сложение (дизъюнкция, операция ИЛИ). Более сложные логические преобразования всегда можно свести к указанным простейшим операциям. Операция отрицания (операция НЕ, инверсия) выполняется над одной переменной и характеризуется следующими свойствами: функци Y = 1 при аргументе Х = 0 и Y = 0, если Х = 1. обозначается отрицание чертой над переменной, с которой производится операция: Y X . Соответственно, Y X . Следовательно: определение любой логической операции дополняется конкретной таблицей, которая называется таблицей истинности. Для операции НЕ таблица истинности приведена на рис. 2.1,а. X НЕ 0 1 Y 1 0 а) X2 0 0 1 1 И X1 0 1 0 1 б) Y 0 0 0 1 X2 0 0 1 1 ИЛИ X1 0 1 0 1 в) Y 0 1 1 1 Рис. 1.1 Операция логического умножения (операция И, конъюнкция) для двух переменных определяется таблицей истинности (рис. 1.1,б) и обозначается логической формулой: или Y X2 X1. (1.1) Y X 2 X1 Как следует из таблицы, нулевое значение хотя бы одного из аргументов обеспечивает нулевой результат операции. В дальнейшем будем пользоваться первым обозначением операции логического умножения, а именно Y X 2 X1 . Операция логического сложения (операция ИЛИ, дизъюнкция) определяется таблицей истинности (рис. 1.1,в) и обозначается логической формулой Y X2 X1 или Y X 2 X1 . (1.2) Из таблицы следует, что равенство хотя бы одного аргумента логической единице определяет единичное значение всей функции. В дальнейшем будем пользоваться первым способом обозначения операции ИЛИ, т.е. Y X2 X1 . Операции дизъюнкции и конъюнкции могут осуществляться и с большим числом аргументов. Операция ИЛИ – НЕ (логическая операция стрелка Пирса) представляет собой отрицание логической суммы и может быть обозначена с помощью знаков логического сложения и отрицания или знаком "". Y X 2 X1 X2 X1 . (1.3) Операция И – НЕ (логическая операция штрих Шеффера) представляет собой отрицание логического произведения и обозначается с помощью знаков логического произведения и отрицания или знаком "". Y X 2 X1 X 2 X1 . (1.4) Операция ЗАПРЕТ. В результате операции запрет по X 1 функция Y 1 только когда X 1 0 , а X 2 1 , т.е. выражение для операции в данном случае имеет вид Y X 2 X1 . (1.5) При запрете по X 2 выражение принимает вид Y X 2 X1 . Операция РАВНОЗНАЧНОСТЬ. В результате операции Y 1 в том случае, если значения переменных совпадают, т.е. X 2 и X 1 равны 0 или 1. Если же значения переменных не совпадают, то Y 0 . Операция РАВНОЗНАЧНОСТЬ записывается в виде выражения Y X 2 X1 X2 X1 (1.6) или обозначаются знаком Y X 2 ~ X1 . Операция НЕРАВНОЗНАЧНОСТЬ (исключающее ИЛИ, сумма по модулю 2). В результате операции Y 0 в том случае, когда значения переменных X 1 и X 2 совпадают, и Y 1 в случае несовпадения значений переменных. Операция НЕРАВНОЗНАЧНОСТЬ записывается в виде выражения Y X 2 X 1 X 2 .X 1 (1.7) и обозначается знаком Y X 2 X1 . Данная операция является отрицанием (инверсией) операции РАВНОЗНАЧНОСТЬ Y X 2 X1 X 2 X1 X 2 X1 X 2 X1 X2 X1 . (1.8) Обозначение логических элементов, реализующих рассмотренные выше операции, на функциональных схемах приведено на рис. 1.2. Рис. 1.2. 1.3. Законы алгебры логики Алгебра логики базируется на нескольких аксиомах, из которых выводят основные законы для преобразования выражений с двоичными переменными. Обоснованность выбора этих аксиом подтверждается таблицами истинности для рассмотренных операций. Каждая аксиома представлена в двух видах, что вытекает из принципа дуальности 9двойственности) логических операций, согласно которому операции конъюнкции и дизъюнкции допускают взаимную замену, если одновременно поменять логическую 1 на 0, 0 на 1, знак "+" на "" на "+". Алгебра логики определяется следующей системой аксиом: X 0 , если X 1; X 1 , если X 0. 1 1 1; 0 0 0. 0 0 0; 1 1 1. 1 0 0 1 0; 0 1 1 0 1. 0 1; 1 0. . (1.9) (1.10) (1.11) (1.12) (1.13) Аксиома (1.9) утверждает, что в алгебре логики рассматриваются только двоичные переменные, аксиомы (1.10) – (1.12) определяют операции дизъюнкции и конъюнкции, а аксиомы (1.13) – операцию отрицания. Аксиома (2.10) для операции дизъюнкции 1 + 1 = 1 не имеет аналога в двоичной арифметике, где сумма (а не операция ИЛИ) 1 + 1 = 10. Законы булевой алгебры вытекают из аксиом и также имеют две формы выражения: для конъюнкции и дизъюнкции. Законы для одной переменной 1. Закон первого множества а) X 0 0 ; б) X 0 X . 2. Закон универсального множества а) X 1 X ; б) X 1 1 . 3. Закон повторения (тавтологии) а) X X X ; б) X X X . 4. Закон дополнительности а) X X 0 ; б) X X 1 . 5. Закон двойной инверсии (двойного отрицания) ХX. (1.14) (1.15) (1.16) (1.17) (1.18) Законы для двух и более переменных 1. Переместительный (коммутативный) закон а) X 1 X 2 X 2 X 1 ; (1.19) б) X 1 X 2 X 2 X 1 Этот закон имеет такой же смысл, как и в обычной алгебре. В применении к логическим схемам переместительный закон означает, что выходной сигнал элементов ИЛИ и И не зависит от того, к каким клеммам подводится тот или иной входной сигнал. 2. Сочетательный (ассоциативный) закон (1.20) а) X 1 X 2 X 3 X 1 X 2 X 3 X 1 X 2 X 3 б) X 1 X 2 X 3 X 1 X 2 X 3 X 1 X 2 X 3 Сочетательный закон аналогичен соответствующему закону обычной алгебры. 3. Распределительный (дистрибутивный) закон а) X 1 X 2 X 3 X 2 X 1 X 3 X 1 ; б) X 1 X 2 X 3 X 2 X 1 X 3 X 1 . (1.21) Если выражение (а) аналогично известному закону обычной алгебры, то выражение (б) получается из (а) применением принципа двойственности. Если в (а) заменить двоичные X 1 , X 2 и X 3 на их отрицания, получим X 1 X 3 X 2 X 3 X 1 X 2 X 1 . Применив операцию дизъюнкции на конъюнкцию и наоборот и отрицания переменных на сами переменные, получим X 1 X 3 X 2 X 3 X 1 X 2 X 1 , что и требовалось доказать. 4. Закон обращения Если X 1 X 2 , то X 1 X 2 . (1.22) 5. Закон поглощения а) X 1 X 2 X 1 X 1 ... ; б) X 1 X 2 X 1 X 1 ... (1.23) Для доказательства равенства (а) вынесем переменную Х за скобки. Получим X 1 X 2 X 1 X 1 1 X 2 . Но 1 X 2 1 в соответствии с (1.15), что и доказывает справедливость закона поглощения. Для доказательства равенства (б) воспользуемся законом (1.20,а), т.е. X 1 X 2 X 1 X 2 X 1 X 1 X 1 X 1 X 2 X 1 X 1 1 X 2 X 1 . 6. Закон склеивания а) X 2 X 1 X 2 X 1 X 2 ...; б) X 2 X 1 X 2 X 1 X 2 . (1.24) Для доказательства выражения (а) применим распределительный закон X 2 X 1 X 2 X 1 X 2 X 2 X 2 X 1 X 2 X 1 X 1 X 1 X 2 1 X 1 X 2 X 1 X 2 1 X 1 X 2 . Для доказательства вынесем X 2 за скобки. Получим: X 2 X 2 X 2 X 2 . 1 7. Закон инверсии (закон де Моргана) а) X 2 X 1 X 2 X 1 ; б) X 2 X 1 X 2 X 1 . (1.25) Справедливость этого закона вытекает непосредственно из принципа двойственности. Пусть Y X 2 X 1 . Тогда в соответствии с принципом двойственности Y X 2 X 1 , так как при замене переменных их отрицаниями и операции умножения операцией сложения получается отрицание результата. Это доказывает справедливость выражения а). Таким же образом доказывается и справедливость выражения б). 1.4. Логические функции и способы их задания 1.4.1. Логические функции и их суперпозиция Логической (двоичной, переключательной) функцией Y f X n 1 , X n 2 ,...X i , X 0 называется двоичная переменная Y, значения которой зависят от значений других двоичных переменных X n 1 , X n 2 ,...X 1 , X 0 , называемых аргументами. Таким образом, логическая функция так же, как и ее аргументы, может применить только два значения 0 или 1. Задание логической функции Y означает, что каждому из возможных сочетаний (наборов) ее аргументов X n 1 , X n 2 ,… X 1 , X 0 поставлено в соответствие определенное значение Yi . Функции считаются различными, если значения функции Y отличаются, по крайней мере, для одного набора аргументов. Пусть логическая функция Y зависит от n аргументов. Тогда полное число возможных двоичных наборов аргументов. p 2n . (1.26) Поскольку каждому из наборов могут соответствовать два значения функции 0 или 1, то общее число N различных функций Yi n – аргументов равно N 2p (1.27) Набор аргументов принято нумеровать. Если считать, что номера наборов совпадают со значениями двоичных чисел, разрядами которых являются аргументы X n 1 , X n 2 ,...X 1 , X 0 , то номера наборов будут меняться от 0 до ( 2 n 1 ). Если логическая функция определена на всех наборах, то она называется полностью определенной. Если же на некоторых наборах значение функции не задано, то она называется частично определенной или недоопределенной. Наборы входных переменных (аргументов), на которых логическая функция не задана называются запрещенными. На этих наборах значения функции определяются как факультативные (необязательные). Их можно устанавливать по своему усмотрению, т.е. частично определенную функцию можно доопределять. Алгебра логики предполагает возможность образования сложных логических функций, аргументы которых являются функциями других двоичных переменных. Например, если Y f X 3 , X 2 , X1 , X0 , а Z 2 f 2 X 3 , X 2 , то Y Z 2 , Z 1 . Z1 f1 X 1 , X 0 и Операция замены аргументов одной логической функции другими логическими функциями называется суперпозицией логических функций. Эта операция позволяет с помощью функций меньшого числа двоичных аргументов получить логические функции большего их числа. Многократное применение операции суперпозиции позволяет получить функции лю- бого требуемого числа аргументов. В частности, такую возможность обеспечивает суперпозиция двух аргументов. 1.4.2. Совершенные нормальные (канонические) формы логических функций Нормальными или каноническими называют логические функции, полученные посредством суперпозиции специально вводимых вспомогательных функций – конститутент единиц (минтермов) и конституент нулей (макстермов). Минтермом называют логическую функцию, которая принимает единичное значение на одном из всех возможных наборов аргументов и нулевое на всех прочих наборах. Макстермом называют логическую функцию, которая принимает нулевое значение на одном из всех возможных наборов аргументов и единичное на всех других. Количество минтермов и макстермов заданного числа аргументов n совпадает с числом различных наборов аргументов p 2 n (как это и следует из определения макстермов и минтермов). В таблице 1.1 представлены минтермы и макстермы двух аргументов X1 и X0 . Из определения конституент и таблицы 1.1 следует, что для одного и того же набора аргументов макстерм является инверсией минтерма и наборов. Алгебраически минтерм, соответствующий какому-либо набору, представляется в виде конъюнкции прямых и инверсных значений аргументов (в прямой форме в конъюнкцию входят аргументы, имеющие в рассматриваемом наборе единичное значение, а в инверсной – нулевое значение). Таблица 1.1 Аргументы Минтермы Макстермы X1 X0 C01 C11 C21 C31 C00 C10 C20 C30 0 0 1 0 0 0 0 1 1 1 0 1 0 1 0 0 1 0 1 1 1 0 0 0 1 0 1 1 0 1 1 1 0 0 0 1 1 1 1 0 В соответствии с таблицей 1.1 минтермы двух аргументов выражаются формулами C 01 X 1 X 0 ; C 11 X 1 X 0 ; C 21 X 1 X 0 ; C 31 X 1 X 0 . (1.28) Макстермы алгебраически представляются дизъюнкцией прямых и инверсных значений аргументов (в прямой форме в дизъюнкцию входят аргументы, имеющие в рассматриваемом наборе нулевое значение, а в инверсной – единичное значение). Макстермы двух аргументов имеют вид C 00 X 1 X 0 ; C 10 X 1 X 0 ; C 20 X 1 X 0 ; C 30 X 1 X 0 . (1.29) Формы представления функций посредством суперпозиции их минтермов и макстермов получили наименование, соответственно, совершенных дизъюнктивных (СДНФ) и совершенных конъюнктивных (СКНФ) нормальных норм функций. СДНФ (или первая стандартная форма) функции представляет собой дизъюнкцию минтермов, соответствующих наборам аргументов, на которых рассматриваемая функция имеет единичное значение. В общем виде алгебраическая запись СДНФ имеет вид m 1 Y X n 1 , X n 2 ,...X 1 , X 0 C i1 . i 0 (1.30) где m – число наборов, на которых Y 1 . СКНФ (или вторая стандартная форма) функции представляет собой конъюнкцию макстермов, соответствующих наборам аргументов, на которых рассматриваемая функция имеет нулевое значение. Алгебраическая запись СКНФ в общем случае имеет вид Y X n 1 , X n 2 ,...X 1 , X 0 k 1 C i0 , i 0 (1.31) где k – число наборов, на которых Y 0 . 1.4.3. Способы задания логических функций Логическая функция может быть задана следующими способами: словесно; таблицей, называемой таблицей истинности; алгебраическим выражением; картой Карно; числовым способом. Словесный способ. В качестве примера рассмотрим задание логической функции мажоритарных подсчетов, при которых функция трех аргументов принимает значение 1, если два любые аргумента равны 1. Табличный способ. Логическая функция, заданная словесно, может быть представлена в виде таблицы истинности (таблица 1.2). Как следует из таблицы, функция Y принимает значение 1 на 3, 5, 6 и 7 наборах. Алгебраический способ. От таблицы истинности можно перейти к алгебраической форме представления функции Y или к структурной формуле. Структурная формула может быть записана по единицам и нулям. При записи структурной формулы по единицам логическая функция представляется в СДНФ. Для перехода от таблицы 1.2 к СДНФ для каждого набора, на котором функция равна единице, записывается элементарное произведение всех аргументов. При этом, если аргумент в этом наборе принимает значение 0, то записывается его отрицание. Затем производится логическое сложение этих элементарных произведений (минтермов) Yсднф X 2 X 1 X 0 X 2 X 1 X 0 X 2 X 1 X 0 X 2 X 1 X 0 . (1.32) Таблица 1.2 Переменные Номер набора X2 X1 X0 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 1 6 1 1 0 1 7 1 1 1 1 Y При записи структурной формулы по нулям логическая функция представляется с СКНФ. Для этого составляются элементарные суммы аргументов наборов, на которых функция равна нулю. В том случае, если ар- гумент в наборе принимает значение 1, то он записывается в элементарную сумму со знаком отрицания, затем производится логическое перемножение элементарных сумм (макстермов). Yсднф X 2 X 1 X 0 X 2 X 1 X 0 X 2 X 1 X 0 X 2 X 1 X 0 . (1.33) Представление функций картой Карно. Карта Карно представляет собой прямоугольник, разбитый на квадраты (ячейки), число которых равно общему числу наборов для данной функции nпеременных, т.е. Рис. 1.3. p 2n (рис. 1.3). Для рассматриваемой функции n 3 и число ячеек равно 8. Каждая ячейка. Следовательно, соответствует определенному набору, причем, если на этом наборе функция равна 1, то в ячейке проставляется 1, а если – 0, то проставляется 0. Значения входных переменных размещаются по горизонтали и вертикали карты поровну при четном их количестве и асимметрично при нечетном. Переменные должны располагаться таким образом, чтобы при переходе от одной ячейки к другой изменялась только одна переменная (00, 01, 11, 10). Числовой способ. Для числового представления логической функции в СДНФ под знаком суммы перечисляются в возрастающем порядке номера наборов, на которых функция равна 1. Для рассматриваемой логической функции Yсднф 3 ,5 ,6 ,7 . (1.34) При числовом представлении логической функции в СКНФ под знаком произведения перечисляются номера наборов, на которых функция равна 0. Yскнф ( 0 ,1 ,2 ,4 ) (1.35) 1.5. Переход от структурной формулы к логической схеме На основе полученной структурной формулы можно построить логическую схему, состоящую из логических элементов, реализующих базовые булевы функции (операции) НЕ, ИЛИ, И. Логические элементы располагаются на схеме, начиная от входов, в порядке, соответствующем выполняемым логическим операциям. Так, для двоичной функции (1.32) сначала необходимо получить отрицания переменных X 2 , X 1 , X 0 , затем логические произведения переменных для каждого набора, а после этого провести операцию ИЛИ с полученными произведениями. Логическая схема, реализующая структурную формулу 1.32, приведена на рис. 1.4. Рис. 1.4. Полученная логическая схема состоит из трех логических элементов НЕ, четырех трехвходовых элементов И и одного элемента ИЛИ, имеющего четыре входа. 1.6. Функционально-полные наборы логических элементов Любая логическая функция, как показано в п.1.5, может быть представлена в виде структурной формулы, над аргументами в которой производятся только три базисные булевы операции: НЕ, ИЛИ, И. Набор логических функций, который обеспечивает представление любой другой функции посредством суперпозиции функций этого набора, называется функционально полным набором (ФПН). Учитывая, что операции НЕ, ИЛИ, И выполняются с помощью трех видов логических элементов, то и система базисных элементов НЕ, ИЛИ, И, позволяющая построить на их базе логическую схему любой сложности, называется функционально полным набором логических элементов (ФПН ЛЭ). Существует, однако, и другие ФПН ЛЭ, включающие в себя меньшее число ЛЭ. Кроме того, на практике широко применяются ЛЭ. Выполняющие операции ИЛИ-НЕ (стрелка Пирса) и И-НЕ (штрих Шеффера). Рассмотрим некоторые функционально полные наборы логических элементов. 1. Наборы, состоящие только из элементов НЕ и ИЛИ (НЕ и И). При этом операция И и, соответственно, ИЛИ реализуется применением известных законов двойного отрицания (1.18) и де Моргана (1.25) X1 X0 X1 X0 X1 X0 , X1 X0 X 1 X0 X 1 X0 . (1.36) После преобразований (1.36) логическая функция будет содержать только операции ИЛИ и НЕ или только операции И и НЕ. Соответствующая этой функции логическая схема будет состоять только из набора элементов НЕ, ИЛИ или НЕ, И. Следовательно, эти наборы являются ФПН ЛЭ. При этом операцию И в первом наборе реализует логическая схема (рис. 2.5, а), а операцию ИЛИ во втором наборе – логическая схема (рис. 1.5,б). Рис. 1.5. 2. Набор, состоящий только из логических элементов ИЛИ-НЕ (стрелка Пирса). Базисные операции алгебры логики НЕ, ИЛИ, И через операцию ИЛИ-НЕ могут быть реализованы на основе законов (2.16), (1.18) и (1.25). XXX; X1 X0 X1 X0 ; X1 X0 X 1 X0 X1 X0 . . (1.37) На рис. 1.6 приведены логические схемы реализации базисных операций булевой алгебры с помощью ЛЭ ИЛИ-НЕ на основе выражений (1.37). Рис. 1.6. 3. набор, состоящий только из логических элементов И-НЕ (штрих Шеффера). Базисные операции алгебры логики через операцию И-НЕ также реализуется на основе законов (1.16), (1.18) и (2.25). X XX; X1 X0 X1 X0 ; (1.38) X1 X0 X1 X0 X1 X0 . На рис. 1.7 приведены логические схемы реализации базисных операций булевой алгебры с помощью ЛЭ И-НЕ на основе выражений (1.38). Рис. 1.7. ФПН логических элементов на основе ЛЭ ИЛИ-НЕ (И-НЕ) иногда называют истинно полным. 3.3. Шифраторы и дешифраторы 3.3.1. Шифраторы Шифратором называется КЦУ с m входами и n выходами, преобразующий сигнал I на одном из входов в n-элементный параллельный код на выходах. Максимальное число входов m max определяется числом возможных кодовых комбинаций и составляет 2 n . Условное графическое обозначение шифратора показано на рис.3.10. Входные шины нумеруются от 0 до m 1 , а на выходных шинах обозначается вес двоичного разряда 0 1 2 3 n1 2 ,2 ,2 ,2 ,...2 . Как следует из определения шифратора, только небольшая часть Рис. 3.10 наборов входных переменных таблицы истинности соответствует кодовым комбинаn циям на выходе, остальные 2 m наборов с числом единиц больше одной являются запрещенными. Поэтому оператор, выполняемый шифратором, удобно задавать сокращенной таблицей истинности, содержащей только m строк. В качестве примера в таблице 3.5 задан шифратор с семью входами и тремя выходами. Таблица 3.5 X1 X2 X3 X4 X5 X6 X7 Y3 Y2 Y1 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 0 1 Как видно из таблицы, выходной код в этом примере представляет собой совокупность двоичных чисел от I до 7 (старший разряд Y3 ), соответствующих номеру входной переменной X i , которая равна I. Булевы функции для трех выходных переменных составляются на основании отображаемых таблицей очевидных связей входных и выходных переменных. Так, переменная Y3 равна I, если или X 6 1 , или X 7 1 . Таким образом Y3 X 4 X 5 X 6 X 7 ; X 4 1 , или X 5 1 , или Y2 X 2 X 3 X 6 X 7 ; (3.9) Y1 X 1 X 3 X 5 X 7 . Разумеется, если составить таблицу со всеми возможными наборами входных переменных, то после минимизации функций для Y1 , Y2 , Y3 с учетом факультативных условий были бы получены более сложным путем те же выражения (3.9). Схема шифратора (рис.3.11) состоит из трех четырехвходовых элементов "ИЛИ". Если необходимо синтезировать шифратор на элементах "И-НЕ", то выражения (1.9) необходимо преобразовать с использованием теоремы де-Моргана Y3 X 4 X 5 X 6 X 7 ; Y2 X 2 X 3 X 6 X 7 ; (3.10) Y1 X 1 X 3 X 5 X 7 . Рис. 3.11 К ИМС шифраторов ТТЛ относятся КМ555ИВ1 и К555ИВ3. Микросхема КМ555ИВ1 (рис. 3.12,а) представляет собой приоритетный шифратор, на входы I 1 I 8 которого подаются напряжения низкого уровня. На выходах Q0 , Q1 , Q2 появляется двоичный код, соответствующий номеру входа, оказавшегося активным. Приоритет в том случае, если на несколько входов подаются активные уровни, имеет старший по номеру. Высший приоритет у входа I 8 . ИМС имеет два дополнительных выхода GS (групповой сигнал) и E0 (разрешение от выхода), а также девятый разрешающий вход E 1 . На выходе GS появится напряжение низкого уровня, если хотя бы на одном из сигнальных выходов Q0 - Q2 присутствует напряжение низкого уровня. На выходе E0 появится напряжение низкого уровня, если на всех входах - высокие уровни. Совместное использование выхода E0 и входа E 1 позволяет построить многоразрядные приоритетные шифраторы. а Рис.3.12 б Микросхема К555ИВЗ (рис. 3.12,б) преобразует уровни логической единицы на одном из девяти входов I1 I9 в выходной двоичнодесятичный код на выходах Q0 Q3 . К ИМС шифраторов ЭСЛ относится микросхема К500ИВ165, которая преобразует сигнал логической единицы, поданный на один из 8 входов, в двоичный трехразрядный эквивалент десятичного номера входа. Шифратор может работать синхронно, так как на выходах комбинационной схемы включены синхронные D-триггеры. 3.3.2. Дешифраторы Дешифратором (декодером) называется КЦУ с m входами и n выходами, преобразующий m-элементный параллельный код, поступающий на входы, в сигнал 1 на одном из выходов. Каждому выходу соответствует своя кодовая комбинация на входах. Условное обозначение дешифратора показано на рис. 3.13. Входы обозначаются весами двоичных разрядов от 1 до 2 m 1 , а выходы нумеруются от 0 до (n-1). Так как на m входах может быть 2 m наборов входных переменных, то максимальное число выходов равно Рис.3.13 nmax 2 m . (3.11) Если используются все выходы, дешифратор называется полным, если же число выходов меньше 2 m - неполным. Линейные (одноступенчатые) дешифраторы В ряде случаев в дешифраторах номер выхода, на котором появляется сигнал 1, равен двоичному числу, представленному набором входных переменных. Такой дешифратор с тремя входами работает в соответствии с таблицей 3.6. На основании таблицы 3.6 можно записать следующую систему из восьми функций Y0 X 3 X 2 X 1 ; Y4 X 3 X 2 X 1 ; Y1 X 3 X 2 X 1 ; Y5 X 3 X 2 X 1 ; (3.12) Y2 X 3 X 2 X 1 ; Y6 X 3 X 2 X 1 ; Y3 X 3 X 2 X 1 ; Y7 X 3 X 2 X 1 . Таблица 3.6 Номер X3 X2 X1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 0 0 0 0 2 0 1 0 0 0 1 0 0 0 0 0 3 0 1 1 0 0 0 1 0 0 0 0 4 1 0 0 0 0 0 0 1 0 0 0 5 1 0 1 0 0 0 0 0 1 0 0 6 1 1 0 0 0 0 0 0 0 1 0 7 1 1 1 0 0 0 0 0 0 0 1 набора Как видно из выражений (3.12), каждый выход дешифратора реализует один из минтермов всех входных переменных. По функциям (3.12) строится схема дешифратора, который называется одноступенчатым или линейным (рис. 3.14,а). Рис. 3.14 Он определяет собой совокупность из n элементов "И", причем, на входы их подаются все переменные X i либо в прямом, либо в инверсном виде. Следовательно, дешифратор имеет 2m парафазных входов (в данном случае 6 входов, если входные переменные снимаются, например, с триггеров). В ИМС выполняется расширение фазы с помощью двух инверторов (рис. 3.14,б). Этим создается также одинаковая для всех входов единичная нагрузка, что облегчает непосредственное соединение дешифратора с выходами источников входных сигналов. Подобную схему имеет, например, дешифратор с четырьмя входами и десятью выходами в ИМС К555ИД6 (ИД10). Дешифраторы часто выполняются синхронизуемыми. При этом число входов элементов должно быть увеличено на 1. Линейный дешифратор может быть построен и на элементах "ИЛИНЕ", лежащих в основе, например, всех серий ИМС ЭСЛ типа. Для этого с помощью теоремы де-Моргана функции (3.12) преобразуются к виду: Y0 X 3 X 2 X 1 ; Y1 X 3 X 2 X 1 ; (3.13) Y7 X 3 X 2 X 1 . По этому принципу построены ИМС дешифраторов К500ИД161 и К500ИД162. Они преобразуют поступающее на 3 входа трехразрядное двоичное число в сигнал логическая единица (ИД162) или логический нуль (ИД161) на одном из семи выходов. Многоступенчатые дешифраторы При большом числе входных переменных m с целью сокращения необходимого числа логических элементов применяются многоступенчатые схемы, к которым относятся прямоугольные и пирамидальные дешифраторы. В основу построения схемы прямоугольного дешифратора положены следующие операции: 1. Все m входов дешифратора разбиваются на 2 группы (при четном m – на две одинаковые группы). Для каждой группы образуются частичные минтермы, в которые входят переменные только данной группы. 2. Производится парное логическое перемножение всех частичных минтермов первой группы со второй. При этом получается n полных минтермов. Эти две операции выполняются двумя ступенями схемы. Пусть необходимо построить дешифратор для m 4 . Если разбить входные переменные на две группы X 1 , X 2 и X 3 , X 4 и обозначить частичные минтермы первой и второй групп соответственно pi и q j , получим: p0 X 2 X 1 ; q0 X 4 X 3 ; p1 X 2 X 1 ; q1 X 4 X 3 ; p2 X 2 X 1 ; q2 X 4 X 3 ; p3 X 2 X 1 ; (3.14) q3 X 4 X 3 . Очевидно, что система булевых функций для выходов может быть записана в виде: Y0 q0 p0 ; Y4 q1 p0 ; Y8 q 2 p0 ; Y12 q3 p0 ; Y1 q0 p1 ; Y5 q1 p1 ; Y9 q 2 p1 ; Y13 q 3 p1 ; Y2 q0 p2 ; Y6 q1 p2 ; Y10 q 2 p2 ; Y14 q 3 p2 ; Y3 q0 p3 ; Y7 q1 p3 ; Y11 q2 p3 ; Y15 q 3 p3 . (3.15) Переменные pi и q j получаются на выходах двух линейных дешифраторов (рис. 3.15), составляющих первую ступень. Вторая ступень представляет собой матричную схему из 16 двухвходовых элементов "И". Она обеспечивает получение конъюнкций q j pi и для всех индексов j и i от 0 до 3. Рис.3.15 Число ступеней дешифратора может быть и больше двух. При большом числе переменных в группе она может быть, в свою очередь, разбита на две подгруппы, которые объединяются собственной матричной ступенью. Выходные переменные дешифратора образуются при этом третьей матричной ступенью. Эта третья ступень может иметь большое число элементов, но, в принципе, возможно составление ее из отдельных частей, которые содержат группы двухвходовых элементов "И", не связанных друг с другом. Вообще прямоугольный дешифратор обладает свойством наращиваемости с целью увеличения входов и выходов. Дешифраторы с большим числом выходов находят широкое применение в адресной части запоминающих устройств. В этих случаях они практически всегда строятся по прямоугольной схеме, причем последняя матричная ступень совмещается с запоминающей матрицей. Пирамидальная схема дешифратора (рис.3.16) строится следующим образом. В первой ступени получаются четыре переменные, соответствующие всем возможным наборам входных переменных Х 1 и Х 2 . Во второй ступени происходит логическое умножение на Х 3 и Х 3 , так что число выходов удваивается, в третьей ступени – на Х 4 и Х 4 и т.д. При m входных переменных последняя ступень имеет 2 m выходов, а число ступеней m 1 , причем в каждой ступени применяются только двухвходовые элементы "И" либо "ИЛИ-НЕ". На рис.3.16 приведена схема пирамидального дешифратора для m 6 . Рис.3.16 Прямоугольные и пирамидальные дешифраторы уступают линейным по быстродействию, так как временная задержка пропорциональна числу ступеней. Однако линейные схемы при одинаковом числе входов требуют применения более сложных логических элементов, а если m превышает максимальное число входов данного типа интегральных логических элементов, то реализация одноступенчатой схемы невозможна. 3.4. Мультиплексоры 3.4.1.Определения и функциональная схема мультиплексора Мультиплексор (от англ. multiplex – многократный) – это ЦУ, предназначенный для коммутации в желаемом порядке информации, поступающей с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор подобен бесконтактному многопозиционному переключателю. Мультиплексоры обладают двумя группами входов: информационными и управляющими и одним, реже двумя – взаимодополняющими (парафазными) выходами. К информационным входам подводятся информа- ционные каналы. К управляющим входам относятся адресные и разрешающие (стробирующие) входы. На адресные входы подается кодовая комбинация, в соответствии с которой тот или иной информационный вход подключается к выходу. Если мультиплексор имеет n адресных входов, то число информационных входов равно 2 n . Таким образом, кодовая комбинация на адресных входах определяет конкретный информационный вход, который будет соединен с выходом мультиплексора. Разрешающий (стробирующий) вход управляет одновременно всеми информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действия всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Разрешающий вход также используется для наращивания разрядности мультиплексора. На рис.3.17 приведена функциональная схема и условное графическое обозначение простейшего мультиплексора вида "две линии в одну" (2:1). Для переключения входных информационных каналов используется один адресный сигнал А. Когда А=0, F=X0; при А=1, F=X1, то есть узел реализует логическую функцию F A X 0 AX 1 (3.16) Рис.3.17 Эти же принципы положены в основу построения и более сложных схем мультиплексоров. На рис.3.18,а приведена функциональная схема реального мультиплексора "четыре линии в одну" (4:1) – половина микросхемы К155 КП2. Она содержит четыре информационных входа D0 – D3, два адресных входа А и В и разрешающий вход V. Вход А принадлежит младшему разряду, В – старшему разряду адресной комбинации. Когда разрешающий вход находится под высоким потенциалом V=1, один из входов логических элементов "И" будет под низким V 0 , так как сигнал подается через инвертор и, следовательно, на их выходах также будут ну- левые уровни независимо от состояния остальных входов. Выходной сигнал в этом случае также будет F=0. Схема управления выполнена таким образом, что при поступлении на вход разрешающего сигнала V=0 любые комбинации сигналов на адресных входах А и В (00, 01, 10, 11) создают условия, при которых на выходе обеспечивается селекция одного их информационных входов (D0, D1, D2, D3). Так, например, двоичное число 10 на адресных входах обеспечивает селекцию шины D2. а) б) Рис.3.18 Это следует из таблицы истинности рассматриваемого мультиплексора (таблица 3.8) и его логической формулы (3.17). F V B A D0 B AD1 BA D2 BAD3 (3.17) В мультиплексорах ТТЛ входные информационные сигналы проходят через несколько логических элементов. Поэтому такие приборы могут обрабатывать только цифровые сигналы, логические уровни которых находятся в пределах, допустимых для ИМС ТТЛ. Таблица 3.8 В х о д ы Выход F V B A 0 0 0 D0 0 0 1 D1 0 1 0 D2 0 1 1 D3 1 X X 0 Мультиплексоры КМОП строятся на основе дешифраторов и двунаправленных вентильных ключей. Поэтому такие мультиплексоры с равным успехом могут быть использованы и в обращенном режиме в качестве демультиплексоров – узлов, коммутирующих сигналы от одной шины к нескольким. Такие мультиплексоры могут обрабатывать и аналоговые сигналы. Условное графическое обозначение мультиплексора К155 КП2 представлено на рис.3.18,б. Микросхема К155 КП2 содержит в одном корпусе два мультиплексора вида 4:1. Каждая секция имеет четыре информационных входа D0 D3 , разрешающий вход V, а также прямой по отношению к информационным входам выход F. Два адресных входа А и В – общие для обоих мультиплексоров, причем вход А – младший разряд. 3.4.2. Способы наращивания числа информационных входов В мультиплексорах, выпускаемых в виде самостоятельных ИМС, число информационных входов не превышает 16. Большее число входов обеспечивается путем наращивания. Наращивание можно выполнять двумя способами: объединением нескольких мультиплексоров в пирамидальную схему; последовательным соединением разрешающих входов мультиплексоров. На практике применяются оба способа соединения: пирамидальное и последовательное. Пирамидальные мультиплексоры строятся по ступенчатому принципу, причем обычно применяются две-три ступени. Пирамидальный характер схемы состоит в том, что каждая ступень, начиная с первой, имеет больше входов, чем последующая. Младшие разряды кода адреса подаются на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды адресного кода. На рис.3.19 показан вариант мультиплексора 32:1 на основе приборов 8:1 и 4:1. Чередование сигналов на адресных входах СВА (000, 001, 010, 011, 100, 101, 110, 111), микросхем DD1-DD4 одновременно коммути- рует входы Х 0 Х 7 на шину У 0 , входы Х 8 Х 15 на шину У 1 , Х 15 Х 23 на шину У 2 и Х 24 Х 31 на шину У 3 . Адресу СВА=100, например, соответствует поступление сигналов с X 4 на У 0 ; с X 12 на У 1 ; с X 20 на У 2 и с X 28 на У 3 . Мультиплексирование шин У 0 У 3 происходит при смене сигналов на адресных входах высших разрядов ЕD (микросхема DD5) от 00 до 11. Если требуется, чтобы выход F был соединен с входом X 24 , то ЕD должно быть равно 11 (код шины У 3 ), а код шины X 24 - CВА=000.Следовательно, информационному входу X 24 соответствует адрес ЕDCВА=11000. Рис.3.19 Общее число информационных входов при однотипных мультиплексорах младшей ступени равно произведению числа входов отдельных мультиплексоров и числа мультиплексоров: N вх . общ . N вх . MX P , (3.18) где N вх .MX -число входов отдельного мультиплексора; Р- число мультиплексоров. Для очень больших N вх .общ . может понадобиться третий ряд (ступень) мультиплексора. Недостатками пирамидального наращивания следует считать повышенный расход микросхем, а также сравнительно невысокое быстродействие из-за суммирования задержек при последовательном прохождении сигналов по ступеням пирамиды. Рис.3.20 Способ последовательного соединения разрешающих входов на примере получения мультиплексора 32:1 из двух 16:1 (К155 КП1) с использованием разрешающих входов микросхем в качестве адресных входов высшего разряда показан на рис.3.20. Адресными входами низших разрядов служат входы АВСD. Разрешающие входы V в данном случае используются для подачи высшего(пятого) разряда Е: на первую схему в прямом виде, на вторую - в инверсном. Первая микросхема работает при нулевом сигнале высшего разряда (Е=0), а вторая – при единичном (Е=1). Благодаря логическому элементу "И-НЕ", фазы сигналов на выходе будут идентичны входным. 3.4.3. Мультиплексоры как универсальные логические элементы По функциональным возможностям мультиплексоры являются очень гибкими устройствами и помимо прямого назначения могут выполнять и другие функции. Мультиплексоры, в частности, используются для преобразования параллельного двоичного кода в последовательный. Если управляющие сигналы на адресных входах мультиплексора циклически менять в двоичной последовательности 00; 01; 10; 11 (эта операция легко выполняется с помощью двоичного счетчика), то на выходе мультиплексора будут появляться один за другим сигналы, существующие на информационных входах, в порядке номеров этих входов. Разрядность преобразуемого слова определяется числом информационных входов. Если при этом время от времени чередовать сигналы на разрешающем входе, информация на выходе мультиплексора будет характеризоваться псевдослучайной последовательностью. Мультиплексор также может работать в качестве универсального логического элемента, реализующую любую логическую функцию, содержащую до m 1 переменной, где m - число адресных входов мультиплексора. Применение мультиплексоров для реализации логических функций наиболее приемлемо, когда число переменных достаточно велико, 4-5 и более. Один мультиплексор в этом случае может заменить несколько корпусов с логическими элементами вида "И", "ИЛИ", "НЕ" и др. Синтез таких схем довольно прост и осуществляется на основе словесного описания функции или по таблице истинности. Использование мультиплексора в качестве универсального логического элемента основано на общем свойстве логических функции: независимо от числа аргументов всегда ровняться логической единице или нулю. 1 f X n 1 ,..., X 1 , X 0 0 Если на адресные входы мультиплексора подать входные переменные, зная, какой выходной уровень должен отвечать каждому сочетанию этих сигналов, то, предварительно установив на информационных входах потенциалы нуля и единицы согласно программе, получим устройство, реализующее требуемую функцию. Так для логической функции "исключающее ИЛИ" сочетаниям X 1 X 0 00 и X 1 X 0 11 соответствует значение логического нуля, а двум другим X 1 X 0 01 и X 1 X 0 10 - логической единицы. Для выполнения этих условий достаточно подключить к адресным входам мультиплексора А и В сигналы X 0 и X 1 соответственно, на информационные входы D0 и D3 подать потенциал логического нуля, а на D1 и D2 - логической единицы. На разрешающий вход V при этом должен подаваться сигнал логического нуля (рис.3.21,а). Если число аргументов равно n 1 , то есть превышает число адресных входов, то мультиплексор следует включать несколько иначе. Пусть на основе мультиплексора 4:1 требуется составить схему, реализующую функцию трех переменных, заданную таблицей истинности (таблица 3.9). Расчленим мысленно таблицу истинности на группы по две строки в каждой. В каждой группе X 2 и X 1 неизменны, а X 0 (аргумент младшего разряда) имеет два состояния. Выходной сигнал может иметь одно из четырех значений: F 1 , F 0 , F X 0 , F X 0 . Таблица 3.9 Рис.3.21 Если переменные сигналы X 2 и X 1 подключить к адресным входам мультиплексора В и А, а на информационные входы D0 D3 подать согласно таблице истинности постоянные сигналы U 1 ,U 0 и переменные сигналы X 0 , то такая схема (рис.3.21,б) будет удовлетворять заданным условиям. Описанный метод приемлем также для составления схем с большим числом переменных. 3.4.4. Демультиплексоры Демультиплексором называется ЦУ, в котором сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам. Выбор нужной выходной шины, как и в мультиплексоре, обеспечивается кодом на адресных входах. При K адресных входах демультиплексор может иметь в зависимости от конструкции до 2 k выходов. Таблица истинности демультиплексора 1:4 приведена в таблице 3.10. Таблица 3.10 В А V X F0 F1 F2 F3 0 0 0 0/1 0/1 1 1 1 0 1 0 0/1 1 0/1 1 1 1 0 0 0/1 1 1 0/1 1 1 1 0 0/1 1 1 1 0/1 0 0 1 Ф 0 1 1 1 0 1 1 Ф 1 0 1 1 1 0 1 Ф 1 1 0 1 1 1 1 Ф 1 1 1 0 Структурная логическая схема демультиплексора, синтезированого согласно таблице истинности приведена на рис.3.22. Рис.3.22 ции: Работу демультиплексора описывают следующие логические функ- F0 X V B А ; F1 X V B A ; (3.19) F2 X V BA ; F3 X V BA . Как следует из определения, демультиплексор отличается от дешифратора тем, что у дешифратора имеется m входов и n выходов, а у демультиплексора 1 вход и n выходов, причем n 2k , (3.20) где k -количество адресных входов. В ряде случаев одни и те же микросхемы выполняют функции и демультиплексора и дешифратора. Так, например, микросхема К155 ИД3, условное изображение которой приведено на рис.3.23, работает как дешифратор, если на обоих разрешающих входах поддерживать уровень логического нуля и служит для преобразования четырехразрядного двоичного кода в сигнал "1" на одном из 16 выходов. Для создания режима демультиплексора 1:16 на один из разрешающих входов , например, V0 , подают уровень логического нуля, а другой ( U 1 ) используют в качестве информационного. Кодовая комбинация на входах D0 , D1 , D2 , D3 переводит один из 16 выходов в активное состояние. Сигналы на активном выходе повторяют в прямом виде сигналы, поступающие на раз Рис.3.23 решающий вход (V1 ). 3.5. Сумматоры 3.5.1. Общие сведения об арифметических цифровых уздах. Рассмотренные ранее комбинационные узлы выполняли логические функции. Для описания их поведения используется аппарат алгебры логики. Входные и выходные сигналы высокого и низкого уровней оценивались соответственно как логическая единица и логический нуль. Дискретная техника оперирует и другим классом комбинационных узлов, назначение которых состоит в выполнении арифметических действий с двоичными числами: сложения, вычитания, умножения и деления. Такие цифровые узлы называют арифметическими. К арифметическим узлам относятся также ЦУ, выполняющие специальные арифметические операции, такие, как выявление четности или нечетности заданных чисел и их срав- нение. Особенность арифметических узлов состоит в том, что сигналам приписываются не логические, а арифметические значения 1 и 0 и действие над ними подчиняется законам двоичной арифметики. Хотя арифметические узлы оперируют с численными величинами, для описания их работы также удобно пользоваться таблицами истинности. Арифметические узлы широко используются в ЭВМ и достаточно часто в аппаратуре информационно-измерительной техники. Арифметические узлы выпускаются в виде готовых изделий в составе многих серий цифровых микросхем. Важнейшая из арифметических операций - сложение (суммирование). Помимо прямого назначения она используется и при других операциях: вычитание - это сложение, в котором вычитаемое вводится в обратном или дополнительном коде, а умножение и деление - это последовательное сложение и вычитание. Сумматорами называются цифровые узлы, выполняющие операцию сложения двоичных чисел. В устройствах дискретной техники суммирование осуществляется в двоичном или двоично-десятичном кодах. По характеру действия сумматоры подразделяются на 2 категории: а) комбинационные - как и все рассмотренные ранее узлы, не имеющие элементов памяти; б) накопительные - сохраняющие результаты вычислений. В свою очередь, каждый сумматор, оперирующий с многоразрядными слагаемыми, в зависимости от способа обработки чисел, может быть отнесен к последовательному или параллельному типу. Сумматоры, выполненные в виде самостоятельных микросхем,комбинационные, и в дальнейшем только они и будут рассматриваться. Как последовательные, так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Сложение чисел в последовательных сумматорах осуществляется поразрядно, последовательно во времени. В сумматорах параллельного действия сложение всех разрядов многоразрядных чисел происходит одновременно. 3.5.2. Полусумматоры Полусумматором называется комбинационный цифровой узел, обеспечивающий выполнение операции арифметического сложения двух одноразрядных чисел А и В. Условное графическое обозначение полусумматора показано на рис. 3.24. Полусумматор имеет два входа А и В для двух слагаемых и два выхода S (сумма) и Р (перенос). Обозначением полусумматора служат буквы HS (halfsum полусумма). Работу устройства отражает таблица истинности 3.11. Рис.3.24 Таблица 3 11 А 0 0 I I В S 0 1 0 1 0 I I 0 P 0 0 0 1 При сложении в двоичной системе счисления двух одноразрядных чисел получаются результаты, приведенные на рис.3.25. Рис.3.25 Логическая структура полусумматора такова, что состояние выхода S отображает бит суммы, а выхода P - бит переноса. Это следует из таблицы истинности полусумматора, работа которого описывается следующими уравнениями: (3.24) S AB A B A B P A B (3.25) Выражение 3.24 для выхода S как и столбец S таблицы истинности, полностью совпадает с уравнением для логического элемента "Исключающее ИЛИ". Это обстоятельство объясняет, почему операцию "Исключающее ИЛИ" иногда называют сумматором по модулю 2 и обозначают в соответствии с рис. 3.26,а. Рис.3.26 Логическая структура полусумматора в общем виде приведена на рис. 3.26,б. Для реализации структуры в развернутом виде на логических элементах "И-НЕ" преобразуем выражение (3.24) с использованием теоремы де-Моргана (3.26) S AB A B AB A B Реализация структурной схемы полусумматора, в соответствии с выражением (3.26), приведена на рис. 3.26,в. Решение некоторых вопросов преобразования цифровой информации требует применения многовходовых сумматоров по модулю 2, называемых также узлами проверки на четность для кодов с проверкой на четность. Сигнал единица на выходе такого узла появляется только в случаях, когда набор входных переменных содержит четное число единиц. Многовходные узлы контроля четности выполняются в виде ИМС повышенного уровня интеграции. Так, ИМС 155 ИП2 имеет 8 информационных входов и два выхода четности и нечетности. Структура таких ИМС представлена на рис.3.27. Рис.3.27 На выходе S такой ИМС логическая "I" появится только в случае, когда количество единиц на входах А В С D ... N четно, а на выходе S нечетно. 3.5.3.Полные сумматоры Полным сумматором называется комбинационный цифровой узел, предназначенный для сложения двух n-разрядных двоичных чисел. Процедуру сложения двух n разрядных двоичных чисел можно представить в виде, показанном на рис. 3.28. Сложение цифр А1 и B1 младшего разряда дает бит суммы S1 и бит переноса Р1. В следующем (втором) разряде происходит сложение цифр Р1 A2 и B2, которое формирует сумму S2 и перенос Р2. Операция поразрядного сложения длится до тех пор, пока не будет сложена каждая пара цифр во всех разрядах. Результатом сложения будет число S= Рn Sn .....S2S1, где Рn. и SI отображают I и 0, полученные в результате поразрядного сложения. Полусумматор имеет два входа и пригоден, поэтому для использования только в младшем разряде. Устройство для суммирования двух многоразрядных чисел должно иметь, начиная со второго разряда, три входа. два для слагаемых Аi и Вi и один для сигнала переноса Рi-1 с предыдущего разряда. Рис.3.28 Проведем синтез полного сумматора. Исходя из таблицы истинности (таблица 3.12), можно записать следующие логические функции в СДНФ для сигналов суммы и переноса. S i Ai B i Pi 1 Ai B i Pi 1 Ai Bi Pi 1 + Ai Bi Pi 1 ; (3.27). Pi Ai Bi Pi 1 Ai B i Pi 1 Ai B i Pi 1 Ai Bi Pi 1 (3.28) Таблица 3.12 Номер строки 0 1 2 3 4 5 6 7 Ai 0 0 0 0 1 1 1 1 Входы Bi 0 0 1 1 0 0 1 1 Pi-1 0 1 0 1 0 1 0 1 Выходы Pi Si 0 0 0 1 0 1 1 0 1 0 1 0 1 0 1 1 Преобразуем выражения 3.27 и 3.28 к виду, удобному для реализации на полусумматорах. Si ( Ai Bi Ai Bi )Pi 1 ( Ai Bi Ai Bi )Pi 1 ( Ai Bi ) Pi Pi ( Ai Bi Ai Bi )Pi 1 Ai Bi ( Pi1 Pi 1 ) ( Ai Bi )Pi 1 Ai Bi (3.29) (3.30) Из выражений (3.29) и (3.30) следует, что полный сумматор можно представить как объединение двух полусумматоров( рис. 3.29). Рис. 3.29 Первый полусумматор служит для сложения двух чисел, принадлежащих одному разряду, и обеспечивает выход промежуточной суммы S i и переноса Pi . Второй полусумматор складывает перенос предыдущего разряда Pi 1 с промежуточной суммой S i . Таким образом, на выходе S второго полусумматора получается сумма S i для данного разряда с учетом переноса Pi 1 предыдущего. Перенос Pi для данного разряда получается как логическая сумма переносов для первого и второго полусумматоров, что реализует логику работы полного сумматора, так как перенос PI =1 в том случае, если на двух и более входах будет логическая единица. Как уже отмечалось, суммирование многоразрядных чисел может быть последовательное или параллельное. При последовательном суммирований используется один, общий для всех разрядов полный сумматор с дополнительной цепью задержки (рис.3.30). Оба слагаемых кодируются последовательностями импульсов, которые синхронно вводятся в сумматор через входы А и В, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса PI на время одного Рис. 3.30 такта, то есть до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку обеспечивает D-триггер (триггер задержки). Для хранения и ввода слагаемых А и В, а также для преобразования последовательного кода выходных импульсов в параллельный применяют регистры сдвига. Работа регистров сдвига и триггера задержки синхронизируется общим генератором тактовых импульсов. Достоинство последовательных сумматоров - малые аппаратурные затраты. К недостаткам их следует отнести сравнительно невысокое быстродействие, поскольку одновременно суммируется лишь один разряд и время выполнения операции пропорционально числу разрядов слагаемых. На рис. 3.31 приведена схема, поясняющая принцип действия n -разрядного параллельного сумматора с последовательным переносом. Число сумматоров в схеме равно числу разрядов. Выход переноса каждого сумматора соединен со входом переноса сумматора более старшего разряда. На входе переноса сумматора первого разряда установлен потенциал U0, поскольку сигнал переноса сюда не поступает. Слагаемые Ai и Bi складываются во всех разрядах одновременно, а перенос поступает с окончанием операции сложения в предыдущем разряде. Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как появление сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространяется последовательно по всей системе. При большом числе разрядов сумматора применяется групповой перенос. ОбраРис. 3.31 зование суммы в каждом разряде внутри группы происходит при последовательном переносе, а перенос в следующую группу снимается не с сумматора старшего разряда, а с выхода схемы параллельного переноса. Этот сигнал переноса P4 подается на один из входов такой же схемы следующей группы, а также на вход сумматора младшего разряда в этой группе. Рис. 3.32 В микросхеме К555 ИМ6 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора (рис.3.32). Сигнал пе- реноса последовательно передается с выхода предыдущего разряда сумматора на вход переноса следующего разряда. Время выполнения операции в данном сумматоре намного больше времени сложения в одноразрядном сумматоре, т.к. в каждый следующий разряд единица переноса попадает, проходя все более длинную цепочку логических элементов. Чтобы уменьшить время выполнения операции сложения многоразрядных чисел используют схемы параллельного переноса. При этом сигналы переноса во всех разрядах одновременно вычисляются по значениям входных переменных в данном разряде. Для сигнала переноса из любого i-го разряда справедливо соотношение p i Аi В i Аi Вi pi 1 q i С i p i 1 (3.31) где q i -функция генерации переноса С i -функция распространения переноса Пользуясь рекуррентным соотношением 3.31 можно вывести следующие формулы для вычисления сигналов переноса в четырехразрядном сумматоре: p1 q1 p0 C 1 p2 q 2 p1C 2 q 2 C 2 q1 p0 C 1C 2 p3 q 3 p2 C 3 q 3 C 3 q 2 C 3 C 2 q1 p0 C 3 C 2 C 1 p4 q 4 p 3 C 4 q4 C 4 q 3 C 4 C 3 q 2 C 4 C 3 C 2 q1 p0 C 4 C 3 C 2 C 1 Q C Реализацию этих функций выполняет схема ускоренного переноса, приведенная на рис. 3.33 Рис. 3.33 Хотя полученные логические выражения достаточно сложны, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций определяется временем задержки распространения сигнала в двух элементах. Для построения 16-разрядного сумматора используется эта же схема ускоренного переноса, на которую подаются сигналы Q и C от рассмотренного четырехразрядного сумматора. Особенно необходимо использование ускоренного переноса в сумматорах на МОП транзисторах, отличающихся невысоким быстродействием. Вследствие этого в ИМC 164 ИМ I кроме четырехразрядного сумматора с последовательным переносом содержится и схема параллельного группового переноса (164 ИП4). Эта ИМС предназначена для совместного применения с ИМС арифметико-логического устройства. Она может быть использована для формирования ус Рис.3.34 коренного переноса при построении многоразрядного сумматора из групп по четыре одноразрядных сумматора в каждой. Условное графическое обозначение этой микросхемы приведено на рис.3.34. 3.6. Цифровые компараторы Цифровыми компараторами называются цифровые узлы, предназначенные для сравнения двух чисел, заданных в двоичном коде. Цифровые компараторы также как и сумматоры относятся к арифметическим устройствам. Цифровые компараторы, предназначенные для сравнения двух n-разрядных чисел А и В, имеют 2n входов и 3 выхода F A B , F A B и F A B . Условное графическое изображение компаратора представлено на рис, 3.36,а. Рис. 3.35 Схема компаратора для сравнения одноразрядных чисел А и В представлена на рис. 3.35,б. Она представляет собой развернутую логическую структуру элемента "Исключающее ИЛИ-НЕ" с тремя выходами. Из определения операции "Исключающее ИЛИ (неравнозначность) вытекает, что функции F А В , F А B , F A B равны: 1 при А В F A B AB A B ; 0 при А В 1 при А В А 1 , В 0 А 0,В 1 ; F A B AB 0 при А В А 0 , В 0 А 1, В 1 F А В (3.32) 1 при А В А 0 , В 1 А 1, В 0 АВ . 0 при А В А 1 , В 1 А 0,В 0 Синтезируем компаратор для сравнения двух двухразрядных чисел В b1b0 . Очевидно, и A B , если а 1 b0 . или А а 1 а0 а0 b0 при а 1 b1 . Аналогично, A B , если а 1 b1 или а0 b0 при а 1 b1 . Если же а 1 b1 и а 0 b0 , то А В . На основании этих правил составим таблицу истинности ( таблица 3.13). Таблица 3.13 Номер набора 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 а1 а0 b1 b0 F A B F A B F A B 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 На рис. 3.36 приведены карты Карно для функции F А В , F А B , F A B Рис. 3.36 Проведя минимизацию функций, получим: F A B а 1а 0 b1b0 а 1а0 b1 b0 а 1 а0 b1 b0 а 1 а0 b1 b0 а 1b1 а0 b0 а0 b0 а 1 b1 а0 b0 а0 b0 а1b1 а1b1 а0 b0 а0 b0 а1 b1 а0 b0 (3.33) F A B а1 b1 а0 b1 b0 а1а0 b0 а1 b1 а0 b1 b0 а1 а0 b0 (3.34) F A B а 1 b1 а 0 а 1b0 а0 b1 b0 а 1 b1 а0 а 1 b0 а0 b0 b1 (3.35) Схема, соответствующая выражениям (3.33), (3.34) и ( 3.35 ), приведена на рис. 3.37.Следует отметить, что один из выходов коммутатора может быть получен как функция двух других. Например, F A B F A B F A B , так как F A B 1 только при условии, что F A B 0 и F A B 0 . При этом сокращается общее число логических элементов в схеме компаратора (на рис. 3.37 показано пунктиром). Рис. 3.37 Однако общая глубина схемы и общая временная задержка увеличиваются. С повышением разрядности сравниваемых чисел сложность схемы резко возрастает. Потребуется большое количество логических элементов и с большим числом входов. Неизбежно возрастает и глубина схемы. Цифровые компараторы выполняются в виде отдельных ИМС. Так, например, ИМС K56I ИП2 сравнивает два четырехразрядных двоичных числа и имеет F A B , F A B , F A B , три выхода отображающих неравенство или равенство двоичных чисел. Условное графическое изображение ИМС K56I ИП2 приведено на рис.3.38. Рис. 3.38 Восемь входов микросхемы используются для приема входных слов АО-АЗ и ВО-ВЗ. Три входа А > В, А < В, и А = В (каскадирующие входы) используются при наращивании числа разрядов устройства сравнения. Если применяется только один корпус K56IИП2 на входы А = В и А > В, следует подать напряжение, соответствующее логической единице, а на вход А < В - логического нуля. Логические состояния цифрового компаратора приведены в таблице 3.14. Таблица 3.14 Входы сравнения A3,B3 A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A2,B2 A1,B1 A0,B0 A2>B2 A2<B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A1>B1 A1<B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 A0>B0 A0<B0 A0=B0 A0=B0 A0=B0 A0=B0 A0=B0 A0=B0 A0=B0 A0=B0 Входы каскадирования A>B A<B A=B 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 0 0 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 0 0 Выходы QA>B 1 0 1 0 1 0 1 0 0 1 0 0 0 0 0 0 QA<B 0 1 0 1 0 1 0 1 0 0 1 0 1 1 1 0 QA=B 0 0 0 0 0 0 0 0 1 0 0 1 1 0 1 0 Расширяющие (каскадирующие) входы компараторов позволяют наращивать разрядность сравниваемых чисел без дополнительных логических элементов. Рис. 3. 39 При этом компараторы соединяют последовательно (каскадно) или параллельно (пирамидально). На вход I A B подается сигнал логической единицы. На входы I A B I A B компаратора и младших разрядов (D1) подается сигнал логической единицы, а на вход I A B - логического нуля. В этом случае обеспечивается функционирование компараторов согласно таблице 3.14. Схема каскадного соединения двух компараторов K56I ИП2 обеспечивает сравнение восьмиразрядных слов. На рис.3.40 приведена схема сравнения 20разрядных чисел при параллельном (пирамидальном) соединении компараторов. В этой схеме выходы Q A B и Q A B компараторов D5 , D4 , D3 , D2 первой ступени соединяются со входами, соответственно Ai и Bi компаратора D6 второй ступени, а выходы Q A B и Q A B компаратора D1 со входами I A B и I A B компаратора D6 . На расширяющие входы компараторов первой ступени для обеспечения их нормального (согласно таблицы 3.14) функционирования подаются сигналы I A B = I A B =1 и I A B =0. При параллельном способе соединения компараторов быстродействие схемы сравнения значительно выше, чем при каскадном соединении, так как задержки в случае каскадного соединения суммируются. ГЛАВА 4. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УЗЛЫ 4.1. Основная модель последовательностного цифрового узла В состав последовательностного цифрового узла, кроме комбинационных ЛЭ, входят элементы памяти. Поэтому для определения совокупности значений выходных сигналов необходимо знать начальное состояние узла и совокупность сигналов на входе. Математической моделью устройств, обладающих рассмотренным типом зависимости между входными и выходными сигналами, является конечный автомат. Конечный автомат, как абстрактная математическая модель устройства, применим для изучения функциональных свойств цифровых устройств. Конечным автоматом называется устройство, для которого определены: дискретное время t, принимающее целые положительные значения (t=0,1,2,….); конечное множество ( Xn-1, Xn-2,... X1, Xo ) возможных значений входного сигнала Х(t), называемое входным алфавитом автомата; конечное множество внутренних состояний Qi(t) = ( qk-1, qk-2, … q1, q0 ); функция переходов ( возбуждения ) Fп, определяющая состояние, в которое перейдет автомат в момент t+1 , если известно его состояние и значение входного сигнала в момент t; функция выходов Fвых , выражающая зависимость значения выходного сигнала автомата от его внутреннего состояния и значения входного сигнала в момент t. Обозначая текущее состояние автомата через Q( t ), функции Q( t+1 ) и Y( t+1 ) можно записать в следующем виде: Q ( t 1 ) F n ( Q i( t ) , X ( t ) ) , ( 4.1 Y ( t 1 ) F вых ( Q i ( t ) , X ( t ) ) ) Зная конкретный вид функций Fn и Fвых для любого начального состояния Q( 0 ) и входного сигнала X( t ), можно найти последовательность состояний Qi( t ) и выходной сигнал Y( t ). Автоматы, используемые в цифровой технике, обычно имеют двоичные входы и выходы. Такие автоматы называются цифровыми автоматами (ЦА). Функциональная схема асинхронного цифрового автомата приведена на рис.3.1. Она состоит из комбинационного цифрового узла и элементов памяти D0, D1, …, Dk-1. В синхронных ЦА элементы задержки синхронные, т.е. значения qk изменяются только в дискретные моменты времени t = 1, 2, 3 … , а в промежутках между этими моментами сигналы qk ( t+1 ) не изме- няют состояние элементов памяти. Для выполнения этого условия на элементы памяти подаются тактовые (синхронизирующие) импульсы С. Фундаментальным результатом теории конечных автоматов, определяющим методы синтеза последовательностных цифровых устройств, является возможность разложения произвольного конечного автомата на совокупность взаимодействующих автоматов простейшего типа, обладающих одним или двумя внутренними состояниями. Рис.4.1 П р и м и т и в н ы м или автоматом без памяти называется ЦА с одним внутренним состоянием. Его функция переходов вырождается в тождественную функцию, а функция выходов – в систему переключательных функций входных двоичных переменных, т.е. Y0 = Fвых 0 ( xm-1, xm-2, . . . , x1, x0 ) Y1 = Fвых 1 ( xm-1, xm-2, . . . , x1, x0 ) Y2 = Fвых 2 ( xm-1, xm-2, . . . , x1, x0 ) ( 4.2 ) . . . Yn-1 = Fвых n-1 ( xm-1, xm-2, . . . , x1, x0 ), где m и n – число входов и выходов двоичных переменных. Примитивный автомат реализуется в виде комбинационной логической схемы (КЦУ), представляющей собой соединение логических элементов без цепей обратной связи. Элементарным называется ЦА с двумя внутренними состояниями. Эти состояния кодируются двоичной переменной Q, совпадающей со значением выходной переменной, т.е. функция выходов элементарного ЦА вырождается в равенство Y( t 1) Q(t 1) , т .е . Fвых 1. ( 4.3 ) Схемной реализацией элементарного ЦА является триггер. Элементарные автоматы отличаются друг от друга числом входов и видом функции переходов. При синтезе цифровых устройств обычно используют относительно небольшое число элементарных автоматов. В принципе для построения произвольного автомата достаточно иметь всего один элементарный автомат, функция переходов которого удовлетворяет условию полноты. Это условие состоит в том, что для любого состояния существует входной сигнал, переключающий автомат в новое состояние, и сигнал, оставляющий это состояние неизменным. Реальные ЦА в отличие от абстрактных конечных автоматов работают в непрерывном времени. Переход от дискретного времени абстрактного автомата к непрерывному времени реального составляет важный раздел теории автоматов. По способу задания дискретного времени цифровые автоматы делятся на асинхронные и синхронные. В асинхронных ЦА после каждого изменения входного сигнала имеет место переходный процесс, состоящий в последовательном переключении связанных между собой ЛЭ, и этот процесс заканчивается переходом ЦА в новое стационарное состояние. В этом состоянии ЦА будет находиться до следующего переключения входного сигнала. а) б) Рис. 4.2 Время, в течение которого ЦА будет оставаться в стационарном состоянии, не влияет на характер процессов при следующих переключениях, т.к. в потенциальных ЛЭ отсутствуют динамические элементы памяти. Поэтому можно принять временной интервал между двумя соседними переключениями на входе равным единице. Тогда к началу каждого очередного переключения условное (дискретное) время принимает целочисленное значение, для которого состояние ЦА известно, поскольку к моменту нового переключения, как предполагалось, переходный процесс предыдущего переключения уже завершен. На рис.4.2 приведен порядок определения дискретного времени для асинхронного устройства с тремя двоичными входными переменными х0 , х1 и х 2 , временные диаграммы которых приведены на рис.4.2,а. Моменты времени, в которые происходит переключение, пронумерованы цифрами 1 - 5. Полагая временные интервалы между соседними переключениями равными единице, перейдем к условному времени t I при котором переключение входных переменных происходит при целочисленных значениях t I (рис.4.2,б). В синхронных ЦА переключение происходит в момент подачи специального сигнала синхронизации (синхроимпульса), определяющего дискретное время, причем состояние в которое перейдет ЦА определяется сигналами на других входах. Входы ЦА называются статическими, если на процессы его переключения влияет только значение входной переменной. Статический вход ЦА называется управляющим, если изменение значения переменной х на этом входе не может вызвать переключения ЦА, а лишь управляет характером воздействия на процессы переключения со стороны других входов. Входы ЦА называются динамическими, если на процессы его переключения влияет только изменение значения входной переменной. Статические и динамические входы могут быть прямыми и инверсными. Условные обозначения прямого и инверсного статического и динамического входов приведено на рис.4.3. Статический вход называется прямым, если переключение ЦА осуществляется сигналом логической единицы, и инверсным, если переключение ЦА осуществляется сигналом логического нуля (рис.4.3,а). x xX x а Рис.4.3 б Динамический вход называется прямым, если переключение ЦА осуществляется положительным фронтом входного сигнала, и инверсным, если переключение ЦА осуществляется спадом входного сигнала (рис.4.3,б). Совокупность входов называется совокупностью установочных входов, если допустимые комбинации значений переменных xm-1, xm-2, . . . , x1, x0 на этих входах можно отнести к одному из трех видов: пассивные, установки 0 и 1, запрещенные. 4.2. Особенности синтеза последовательностных цифровых узлов Последовательностный ЦУ (ЦА) может быть задан: 1.Словесным описанием; 2.Табицей истинности; 3.Аналитическим способом, в виде аналитических выражений для Fn и Fвых; 4.Графически, в виде графа внутренних состояний, переходов и выходов; 5.Временными диаграммами. Синтез ПЦУ включает в себя следующие этапы: - формулировка за уточнение технических требований к работе синтезируемого ПЦУ; - построение графа ПЦУ (таблицы истинности); - определение требуемого количества внутренних состояний Q и количества элементов памяти р на основании соотношения p log 2 Q , (4.4) где скобки означают округление до большего целого; - кодирование внутренних состояний ПЦУ; - выбор типа логических элементов и элементов памяти, на которых будет выполняться синтезируемый ПЦУ; - построение таблицы переходов, выходов и возбуждающих функций, управляющих состоянием элементов памяти; - получение аналитических выражений для функций возбуждения и выходов, их минимизация и запись минимизированных функций в сооветствии с выбранным базисом; - составление по полученным выражениям функциональной схемы синтезируемого узла; - выбор промышленной серии интегральных микросхем; - составление принципиальной схемы ПЦУ на выбранных ИМС. К основным последовательностным цифровым узлам относятся триггеры, регистры и счетчики. Выходные переменные ПЦУ, как было указано выше, определяются как значениями входных переменных в данном такте работы узла, так и состояниями элементов памяти. При N элементах памяти макси- мальное число внутренних состояний равно 2N. В некоторых случаях часть возможных состояний исключается и ЦУ имеет число внутренних состояний меньшее, чем 2N . Как правило, в последовательностных ЦУ в качестве элементов памяти используются статические триггеры, которые являются элементарными ЦА. 4.3. Триггер как элементарный цифровой автомат Потенциальный триггер представляет собой два инвертирующих усилителя, замкнутых в кольцо положительной обратной связи и имеет два состояния устойчивого равновесия. В качестве инвертирующих усилителей могут быть использованы усилители (ключи) на транзисторах или интегральные логические элементы И-НЕ или ИЛИ-НЕ. Переключение триггера осуществляется подачей внешних сигналов управления, которые определяются типом триггера. Выходные сигналы триггера будем обозначать Q (прямой выход) и Q (инверсный выход). Состояние триггера характеризуется значениями сигналов на прямом Q и инверсном Q выходах. Такие выходы называют парафазными. Будем считать, что триггер находится в единичном состоянии, если Q 1 и Q 0 и в нулевом,если Q 0 и Q 1 . Триггер может сохранять одно из двух устойчивых состояний, в котором он находится, бесконечно долгое время, поэтому он сам является элементом памяти. Наличие двух устойчивых состояний позволяет считать триггер элементарым ЦА. Триггеры могут быть асинхронными и синхронными (тактируемыми). Асинхронными называются триггеры, опрокидывание которых происходит в момент поступления на входы определенной комбинации входных информационных сигналов. Синхронными называются триггеры, опрокидывание которых происходит в момент поступления на тактовый (синхронизирующий) вход тактового импульса С при определенной для данного триггера комбинации входных информационных сигналов. В синхронных триггерах, наряду с информационными входами, имеется один или несколько синхронизирующих входов С, на которые подаются периодические последовательности тактовых импульсов. Синхронизирующие сигналы (импульсы) поступают на вход С только в дискретные моменты времени: t 1 , t 2 ,..., t n1 , t n , t n1 ,.... Сигналы запуска триггера на информационных входах могут изменяться не только в эти моменты времени, но и в промежутках между ними. Главное, чтобы к моменту прихода сигнала синхронизации на информационные входы подавалась заданная комбинация запускающих сигналов. Условимся символами X n , C n , Q n обозначать соответственно значения входных, тактовых (синхронизирующих) и выходных сигналов триггера, действующих в интервале t n t t n 1 , т.е. в n-м такте. Тогда Q n 1 - значение сигнала на выходе Q триггера в (n-1)-м такте. Правило работы триггера задается в виде таблицы переходов (истинности) или в виде логической функции набора входных сигналов и предшествующего состояния триггера: Q n f Q n1 , X 1n , X 2n ,..., C n . Для реализации подобных логических функций в схему включают наряду с собственно триггером и логическую схему управления. При рассмотрении триггера на дискретных элементах мы различаем собственно триггер и схему запуска, от которой зависят функции, выполняемые триггером. 4.4.Потенциальные триггеры на ИЛЭ В различных сериях интегральных узлов, выпускаемых промышленностью представлено несколько типов триггеров, отличающихся друг от друга как по схеме, так и по назначению. Обычно собственно триггер и логическая схема, управляющая его входами, создаются на одной кремниевой пластине и составляют конструктивно один модуль. Рассмотрим таблицу переходов триггера с раздельным запуском по входам S “включено” или R “выключено” (таблица 4.1) В таблице за исполнительное значение входного сигнала принята 1, а за нейтральное – 0. На последних двух наборах значение выходного сигнала Q n триггера неопределенное, т.к. на оба его входа поступают одновременно исполнительные значения сигналов. Неопределенность перехода отображаются в таблице знаком факультатива Ф. Составим на основании таблицы 4.1 карту Карно для функции Q n (рис. 4.4,а). Столбец карты Карно при комбинации входных сигналов n n S R 11 называется столбцом неопределенности. Доопределение функции на факультативных наборах позволяет получить 4 возможных состояния столбца неопределенности (рис. 4.4,б). При синтезе триггера на ИЛЭ в соответствии с картой Карно (рис. 4.4,а) и первым состоянием столбца неопределенности получим схему RS-триггера с инверсными входами, вторым состоянием – RS-триггера с прямыми входами, третьим – Е-триггера, четвертым – JK-триггера. Таблица 4.1 Номер набора 0 1 2 3 4 5 6 Sn Rn Qn1 Qn Реакция триггера 0 0 0 0 1 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 0 1 0 0 1 1 Ф 7 1 1 1 Ф Хранение 0 Хранение 1 Подтверждение 0 Сброс в 0 Установка 1 Подтверждение 1 Неопределенность Неопределенность Рис. 4.4 Эти типы триггеров на ИЛЭ являются основными, имеющими два информационных входа. Е-триггеры широкого применения не получили и не реализуются промышленностью в интегральном исполнении ни в одной из серий ИМС. Однако для устранения запрещенной комбинации S R 1 для RS-триггера с прямыми входами может быть использована управляющая схема, применяемая в Е-триггере. По одному информационному входу имеют Т-триггер (триггер со счетным входом) и D-триггер (триггер задержки). Перечисленные типы триггеров могут быть как асинхронными, так и синхронными. 4.4.1. RS-триггеры Простейшим триггером является RS-триггер. На основе RSтриггера с использованием различных схем управления строятся другие, более сложные типы триггеров. Асинхронный RS-триггер с инверсными входами. Для синтеза этого триггера доопределим искомую функцию, полагая ее равной единице на факультативных наборах. Карта Карно этой функции представлена на рис. 4.5. Проведя минимизацию по методу карт Карно, получим: Q n S n R n Q n 1 . Для реализации триггера на ИЛЭ И-НЕ преобразуем выражение (4.5), используя теорему де Моргана. Получим Рис.4.5 n n1 Qn S n R nQ n1 S n R Q (4.5) Q n 1 Обозначая R n Q n 1 через Qn , получим функциональную схему триггера (рис. 4.6,а), соответствующую выражению 4.5. УГО этого триггера приведено на рис. 4.6,б. Рис. 4.6 Из функциональной схемы триггера можно получить выражение для Qn , которое можно записать в следующем виде Q n R n S n Q n1 (4.6) Порядок опрокидывания RS-триггера на ИЛЭ И-НЕ приведен в таблице 4.2. Как видно из таблицы, переключение триггера в состояние Q n 1 происходит при S n 0 и R n 1 , а в состояние Q n 0 - при S n 1 и R n 0 в силу того, что информационные входы являются инверсными. При S n R n 1 триггер сохраняет свое состояние ( Q n Q n1 ). Комбинация входных сигналов S n 0 и R n 0 является запрещенной для данного триггера. Таблица 4.2 Sn 0 Rn 0 Qn запр. 0 1 1 1 0 0 1 1 Qn1 Рассмотренный триггер на ИЛЭ И-НЕ называют RS-триггером с инверсными входами ( S , R ), т.к. он управляется сигналами, соответствующими логическому 0. Для нормального функционирования триггера должно выполняться условие S n R n 0 . Асинхронный RS-триггер с прямыми входами. Доопределим искомую функцию Q n , полагая ее равной 0 на факультативных наборах. Карта Карно полученной функции представлена на рис.3.7. Проведя минимизацию, получим: Qn SnRn RnQn1 Rn Sn Qn1 . (4.7) Для реализации триггера на ИЛЭ ИЛИНЕ преобразуем выражение (4.7), используя теорему де Моргана. Рис.4.7 Получим: Qn Rn SQ. n n 1 (4.8) Qn Рис. 4.8 Функциональная схема триггера, соответствующая выражению (4.8), приведена на рис. 4.8,а, а УГО этого триггера – на рис. 4.8,б. Порядок переключения RS-триггера на ИЛЭ ИЛИ-НЕ приведен в таблице 4.3. Таблица 4.3 n n S R Qn 0 0 Qn1 0 1 0 1 0 1 1 1 запр. Переключение данного триггера в состояние Q n 1 осуществляется при S n 1 и R n 0 , а в состояние Q n 0 - при S n 0 и R n 1 . Триггер сохраняет исходное состояние при S n R n 0 . Комбинация входных сигналов S n R n 1 является запрещенной. Рассмотренный триггер на ИЛЭ ИЛИ-НЕ называют RS-триггером с прямыми входами S и R в силу того, что он управляется силами, соответствующими логической 1. Для нормального функционирования триггера, так же, как и в RS-триггере с инверсными входами, должно выполняться условие S n R n 0 . В рассмотренных асинхронных RS-триггерах управляющие сигналы воздействуют на триггер непосредственно с началом своего появления на входах. В современных цифровых устройствах срабатывание всех триггеров должно происходить строго одновременно по тактовым (синхронизирующим) импульсам. Такие RS-триггеры называются синхронными. Синхронные RS-триггеры На рис. 4.9 представлены схемы синхронных RS-триггеров на ИЛЭ ИЛИ-НЕ (рис.4.9,а) и И-НЕ (4.9,б). В этих схемах управляющие сигналы поступают на входы S и R собственно триггера не непосредственно, а через схему управления, состоящую из двух ИЛЭ. Синхронные RS-триггеры имеют три входа: сигнальные входы S, R и синхронизирующий вход С. Кроме того, такие триггеры могут иметь еще установочные входы S' и R'. Они являются входами собственно триггера и предназначены для приоритетной установки триггера в исходное состояние (1 или 0), независимо от комбинации сигналов на входах S, R и С. При наличии на входе С триггера разрешающего значения синхросигнала ИЛЭ схемы управления обеспечивают передачу информационных входных сигналов на входы S' и R' собственно триггера. Если синхросигнал имеет запрещающее значение, то ИЛЭ схемы управления обеспечивают на входах S' и R' собственно триггера нейтральные сигналы, благодаря чему триггер сохраняет предыдущее состояние. Рис. 4.9 Особенностью синхронных RS-триггеров, представленных на рис. 4.9, является применение в схеме управления инвертирующих ИЛЭ (ИЛИ-НЕ, И-НЕ), приводящее к изменению исполнительных значений управляющих сигналов по сравнению с асинхронными RS-триггерами, собранными на аналогичных ИЛЭ. Порядок переключения синхронных RS-триггеров, приведенных на рис. 4.9,а и рис. 4.9,б приведен, соответственно, в таблицах 4.4 и 4.5. С n n Таблица 4.4 Qn 0 S 0 0 0 1 1 0 1 0 0 0 1 1 Qn1 1 0 0 Qn1 1 0 1 Qn1 1 1 0 Qn1 1 1 1 Qn1 R 0 запр. Таблица 4.5 С Sn Rn Qn 0 0 0 Qn1 0 0 1 Qn1 1 0 Qn1 0 1 1 Qn1 1 0 0 Qn1 1 0 1 0 1 1 0 1 1 1 1 запр. Рассмотренные RS-триггеры реагируют на исполнительное значение входных информационных сигналов сразу же после их подачи, т.е. по переднему фронту сигналов (в синхронных триггерах – с появлением синхроимпульсов). Такие триггеры называются одноступенчатыми и имеют на УГО в основном поле одну букву Т. Одноступенчатые триггеры не могут быть использованы для построения нашедших широкое применение в цифровой технике однотактных регистров и счетчиков, в которых триггеры соединяются последовательно друг с другом. При распространении сигналов по этой цепочке происходит передача информации от триггера к триггеру. Так, например, в регистрах с приходом синхроимпульса каждый триггер Ti цепочки принимает состояние предыдущего триггера Ti 1 и должен сохранить это состояние до прихода синхроимпульса следующего такта. С помощью одноступенчатых триггеров осуществить такую передачу сигналов невозможно. Для решения этой задачи применяются двухступенчатые триггеры. Двухступенчатые триггеры состоят из двух триггеров первой и второй степени. Триггер первой ступени предназначен для приема (записи) информации и передачи ее в триггер второй ступени в промежутке между тактовыми импульсами. Внутренние связи между триггерами первой и второй ступени обеспечивают следующий порядок работы в каждом такте: - запись входной информации в запоминающий триггер первой ступени с одновременным блокированием входов триггера второй ступени и сохранением его исходного состояния Q n 1 ; - блокирование входов триггера первой ступени с одновременной перезаписью информации из нее в разблокированную вторую ступень. Проще всего это достигается разделением такта на две части и применением в каждой ступени синхронных триггеров. При этом осуществляется двухтактное управление двухступенчатой схемой триггера (рис. 4.10,а). В этой схеме периодическая последовательность синхроимпульсов С1 первого полутакта разблокирует вход синхронного триггера первой ступени, обеспечивая запись информации в него, а периодическая последовательность синхроимпульсов С 2 второго такта – перезапись информации в триггер второй ступени. Недостатком этой схемы является необходимость формирования двух последовательностей полутактовых импульсов. Рис. 4.10 Осуществлять управление двухступенчатым триггером одной тактовой последовательностью синхроимпульсов можно, если между синхроимпульсов первой и второй ступеней включить инвертор (рис. 4.10,б). В этой схеме при поступлении синхроимпульса С 1 первая ступень будет разблокирована, а вторая заблокирована, т.к. на ее входе действует синхросигнал С 0 . После окончания синхроимпульса вторая ступень окажется разблокированной и информация, записанная в первой ступени, перепишется в нее. Так как информация в двухступенчатом триггере снимается с выхода триггера второй ступени, то, в отличие от одноступенчатых, двуступенчатые триггеры срабатывают после спада синхроимпульса, т.е. в них осуществляется задержка опрокидывания на время, равное длительности синхроимпульса. Широкое применение получил другой способ построения схем двухступенчатых триггеров, в которых отсутствует дополнительный инвертирующий элемент (рис. 4.11,а). В этой схеме триггер первой ступени блокируется и разблокируется синхроимпульсом С, а управление триггером второй ступени осуществляется сигналами, снимаемыми с выходов схем управления первой ступенью. Таким образом, первая ступень полностью управляет работой второй, что привело к появлению в иностран- ной литературе названия данного триггера "хозяин – раб" (англ. master slave) или MS-триггер. Такие триггеры называют также двухступенчатыми триггерами с запрещающими связями. Рис. 4.11 Блокирование второй ступени триггера осуществляется сигналами запрещающих связей ЗАПР.S и ЗАПР.R. При значениях синхросигнала С 1 и входных сигналов S 0 и R 1 или S 1 и R 0 один из запрещающих сигналов равен 0. В этом случае первая ступень разблокирована и примет входную информацию, вторая же ступень заблокирована нулевым значением одного из запрещающих сигналов и сохраняет свое предыдущее состояние. Если значение синхросигнала С 0 , то произойдет блокирование триггера первой ступени. Сигналы же запрещающих связей будут единичными (ЗАПР.S = ЗАПР.R = 1), что приведет к разблокированию второй ступени и перезаписи в нее информации, записанной ранее в первую ступень. И, наконец, если значение синхросигнала С 1 , а входные сигналы имеют нейтральные значения S 0 и R 0 , то обе ступени будут разблокированы. Но изменения состояний первой и второй ступеней не произойдет, т.е. триггер сохранит исходное состояние, соответствующее состоянию в предыдущем такте. Условное графическое обозначение двухступенчатого RS-триггера приведено на рис. 4.11,б. Оно отличается от УГО одноступенчатого триггера наличием двух Т в основном поле. Можно показать, что среднее время задержки опрокидывания одноступенчатого асинхронного RS-триггера (разрешающее время) определяется соотношением: (4.9) t зд тр ср 2 t зд рас ср , а для синхронного одноступенчатого триггера t зд тр ср 3 t зд рас ср . (4.10) Поэтому максимальная частота следования синхроимпульсов FC max с учетом (4.10) определяется соотношением: FC max 1 . (4.11) 3 t зд рас ср Для двухступенчатых синхронных RS-триггеров максимальная частота FC max следования синхроимпульсов должна быть в 2 раза меньше. FC max 1 . (4.12) 6 t зд рас ср Для устойчивого срабатывания асинхронного RS-триггера длительность информационных сигналов на входах S и R должна быть не меньше суммарной задержки переключения триггера, т.е. (4.13) t n t зд тр ср 2 t зд рас ср . В виде самостоятельных ИМС RS-триггеры выпускаются промышленностью в ряде серий. Например, ИМС К555ТР2 и К561ТР2. Каждая из ИМС содержит по 4 RS-триггера. 4.4.2. JK-триггеры Подставив в столбец неопределенности значения Q n , соответствующие JK-триггеру, получим карту Карно переходов триггера (рис. 4.12,а). Рис. 4.12 Проведя минимизацию по единицам (рис. 4.12,б) и нулям (рис. 4.12,в), получим выражения для Q n и Q n : Q n S n Q n1 R n Q n1 , Q n R n Q n 1 S n Q n 1 . (4.14) Преобразуя выражения (4.14) для реализации схемы триггера на ИЛЭ И-НЕ, получим: Q n S n Q n 1 R n Q n 1 , Q RQ n n n1 S Q n n1 . (4.15) Сравнивая выражения (4.15), с (4.5) и (4.6), можно отметить, что эти выражения идентичны при обозначениях S n S n Q n 1 и R n R n Q n 1 . Если реализовать выражения для S n и R n на ИЛЭ И-НЕ, то получим триггер с прямыми входами S n и R n . Чтобы отличить входные сиг налы JK-триггера от входных сигналов S n и R n внутреннего RSтриггера, их обозначают, соответственно, S n через J (от англ. jump – переброс) и R n через К (от англ. keep – сохранять). Таким образом, вход J имеет то же назначение, что и вход S, а вход K – что и вход R. Функциональная схема JK-триггера, соответствующая выражениям (4.15), приведена на рис. 4.13,а. Рис. 4.13 Элементы временной задержки, введенные дополнительно в схеме на рис. 4.13, предназначены для стабилизации состояний триггера и непосредственно на его функциональные свойства не влияют. Они предназначены для создания временного сдвига между моментом ввода входной информации J n и K n и началом формирования выходной Q n и Q n . Без элементов задержки во время действия входной комбинации J n K n 1 при t и вх t зд тр ср началась бы генерация, т.к. с каждой сменой выходных сигналов на входах оставалась бы комбинация, вызывающая новое опрокидывание триггера, что отражает таблица переключений JK-триггера (таблица 4.6). Исключение запрещенной для RS-триггера комбинации входных сигналов S n R n 1 обеспечивается в JK-триггере наличием обратных связей с выхода Q на вход К и с выхода Q на выход J. Таблица 4.6 Jn 0 Kn 0 0 1 1 1 0 1 Qn Qn1 0 1 Qn Схема синхронного одноступенчатого JK-триггера приведена на рис. 4.13,б. Эффективное устранение генерации осуществляется в двухступенчатом JK-триггере. В этом триггере элементы задержки не применяются. Устойчивая работа обеспечивается последовательным опрокидыванием первой и второй ступеней. Двухступенчатые JK-триггеры строятся так же, как и двухступенчатые RS-триггеры. Функциональная схема синхронного двухступенчатого JK-триггера с установочными входами S , R и его УГО приведены на рис. 4.14,а,б. Рис. 4.14 Установка триггера в единичное или нулевое состояние производит по инверсным установочным входам S и R сигналами нулевого уровня независимо от сигналов, подаваемых на входы J, K и С. Триггеры JK –типа производятся во многих сериях ИМС (133, 155, 533, 555, 1533, 561, 564, 1561, и др.) и обозначаются условно буквами ТВ на корпусе ИМС. Например: К155ТВ1, К555ТВ6, К564ТВ1. JK-триггер является универсальным триггером. Кроме того, что он полностью выполняет функции RS-триггера, из него, как будет показано, можно получить и другие типы триггеров, например, Т- и D-триггеры. 4.4.3. D-триггеры Триггер D-типа, или триггер задержки (от английского слова delay – задержка), представляет собой синхронный триггер (ИМС асинхронных D – триггеров не производятся) с одним информационным входом D и входом синхронизации С. Помимо входа С у D-триггера может быть дополнительный вход V, равнозначный со входом С и разрешающий (при V 1 ) запись информации. Такой триггер называют DV-триггером. Возможные состояния D-триггера приведены в таблице 4.7. Как следует из таблицы 4.7, сигнал на выходе Q триггера в n-м такте при С n =1 соответствует сигналу на входе D в этом же такте. Qn Dn . (4.16) Таблица 4.7 Сn 0 0 0 0 1 1 1 1 Dn 0 0 1 1 0 0 1 1 Qn1 0 1 0 1 0 1 0 1 Qn 0 1 0 1 0 0 1 1 Поэтому D-триггер в ряде случаев называется триггером данных (data – данные) и применяется для записи и хранения двоичной информации. Синтезируем синхронный D-триггер, исходя из таблицы его состояний. Карта Карно переходов триггера представлена на рис. 4.15. Проводя минимизацию по методу карт Карно с учетом введения третьего Рис. 4.15 контура для устранения опасных состязаний в синтезируемой схеме триггера, получим: n n Q C D n C nQ n1 D nQ n1 . (4.17) C n D n C n D n Q n 1 Для реализации D-триггера на ИЛЭ И-НЕ преобразуем выражение (4.17), используя теорему де Моргана. Тогда Q n C n D n C n D nQ n1 . (4.18) Сравнивая полученное выражение (4.18) с (4.6), можно отметить, что эти выражения идентичны при (4.19) S n C n Dn и R n C nD n . n n n Преобразуем выражение R C D для того, чтобы использовать реализацию S n C n D n (4.20) R n C n D n C n D n С nC n C n C n D n C n Dn C n . Функциональная схема синхронного D-триггера на основе RSтриггера с инверсными входами с учетом выражений (4.19) и (4.20) представлена на рис. 4.16,а. Рис. 4.16 УГО синхронного одноступенчатого D-триггера приведено на рис. 4.16,б. Пунктиром на схеме показан разрешающий вход V, характерный для синхронного DVтриггера. В D-триггере задержка изменения информации на выходе Q осуществляется от момента подачи сигнала на вход D до момента прихода синхроимпульса (С=1). Примером реализации такого Dтриггера может служить микросхема Рис.4.17 К555ТМ7, УГО которой приведено на рис. 4.17. ИМС содержит четыре синхронных Dтриггера, функциональная схема которых приведена на рис. 4.16,а. Для построения счетчиков и делителей частоты применяются Dтриггеры, у которых процессы во входных и выходных цепях разделены во времени. Для этой цепи применяют двухступенчатые D-триггеры и Dтриггеры с прямым динамическим входом. На рис. 4.18,а представлена функциональная схема двухступенчатого D-триггера на основе двух RS-триггеров с инверсными входами. При С=1 информация со входа D записывается в первую ступень, вторая же ступень закрыта сигналом логического нуля, снимаемого с выхода одного из логических элементов схемы управления DD1 первой ступени. При перепаде 1 0 сигнала на входе С информация переписывается во вторую ступень и появляется на ее выходах. На УГО этого триггера рассмотренная особенность отражена указанием инверсного динамического характера входа С (рис. 4.18,б). На триггерах, приведенных на схеме (рис. 4.18,а) построены многие микросхемы регистров сдвига с однотактным управлением. Рис. 4.18 D-триггеры с прямым динамическим входом построены по принципу самоблокировки (автоблокировки) от воздействия сигнала на входе D после установления состояния триггера, осуществляемого положительным перепадом синхронизирующего сигнала (рис. 4.19,а). По такому принципу построены ИМС триггеров, обозначаемых ТМ в различных сериях. Например: К155ТМ2, К555ТМ2, К561ТМ2 и т.д. УГО такого триггера приведено на рис. 4.19,б. Процесс перехода триггера (рис. 4.19,а) в новое состояние состоит из двух этапов. На первом этапе (подготовки) при С=0 логические элементы D2.2 и D3.2 заблокированы и сигналы на их выходах, соответственно, равны: S 1 и R 1 . При этом RS-триггер с инверсными входами на логических элем6ентах D1.1 и D1.2 сохраняет свое состояние неизменным. Состояние логических элементов D3.1 и D2.1 на этапе подготовки определяется значением сигнала на входе D. Так, на выходе D3.1 сигнал равен логической единице, а на выходе D2.1 – логическому нулю при D=0. Второй этап (установки) начинается в момент изменения сигнала С из 0 в 1. При этом, если D=0, на выходе D3.1 имеет место логическая единица, а на выходе D3.2 – логический ноль, т.е. R 0 . Так как на входах логического элемента D2/1 действуют сигналы, соответствующие логической единице, то на его выходе – логический ноль, а, следовательно, на выходе элемента D2.2 – логическая единица, т.е. S 1 . При таком сочетании входных сигналов RS-триггер с инверсными входами установится в состояние Q=0, Q 1 , т.е. Q n D n 1 . При D=1 триггер устанавливается в состояние Q=1, Q 0 . Рис. 4.19 Важным моментом в работе данного триггера является блокировка цепей передачи сигнала D на вход триггера (D1.1 – D1.2) сразу после переключения логических элементов D2.2 и D3.2. При установке триггера в состояние Q=0 блокируется элемент D3.1, т.е. на его входе постоянно действует сигнал "0", а при Q=1 – блокируется D2.1. В результате блокировки автоматически фиксируются значения сигналов на входе триггера S и R , возникающие в момент подачи положительного перепада синхроимпульса, т.е. фактически имеет место автоблокировка. Для правильной работы триггера необходимо, чтобы входная переменная D оставалась постоянной в течение коротких интервалов времени до и после подачи положительного перепада синхроимпульса. Первый интервал определяется задержками в логических элементах D3.1 и D2.1, т.к. сигналы на их выходах должны при заданном сигнале на входе D установиться, второй интервал - задержками в элементах D3.2 и D2.2. В остальное время тактового интервала переменная D может изменяться произвольно, т.е. данный триггер является триггером с прямым динамическим тактовым входом, что и показано на УГО (рис. 4.19,б). Рис. 4.20 Синхронный D-триггер можно получить (рис. 4.20) из синхронного JK-триггера (или RS-триггера), если между входами J и К (S и R) включить инвертор, а сигнал D подавать на вход J (S). 4.4.4. Т-триггеры Счетный Т-триггер (от англ. toggle – переключатель) имеет один вход Т и может иметь еще установочные входы S и R. Т-триггер изменяет свое состояние с приходом каждого счетного импульса. Таким образом, коэффициент счета триггера К сч 2 , так как триггер возвращается в исходное состояние с приходом второго импульса. Основная область применения Т-триггеров – счетчики импульсов и делители частоты их следования. Счетные триггеры обычно получают из JK и D-триггеров (рис. 4.21). Как следует из таблицы 1.6, JK-триггер опрокидывается в новое состояние, если на входы J и K подать сигнал, соответствующий логической единице. Поэтому для получения Т –триггера необходимо входы J и K соединить (рис. 4.21,а). Если не требуется синхронизация Т-триггера, то и вход С соединяют со входами J и K. Для преобразования синхронного D-триггера в Ттриггер необходимо соединить выход Q со входом D. При этом счетные импульсы подаются на вход С (рис. 4.21,б). Рис. 4.21 На практике получил распространение Т-триггер, построенный на трех асинхронных RS-триггерах с инверсными входами (рис. 4.22,а). Рис. 4.22 Основной триггер содержит ИЛЭ, D1.1, D1.2, а два коммутирующих - D2.1, D2.2 и D3.1, D3.2. Пусть в исходном состоянии на выходах основного триггера Q n 0 и Q n 1 . При подаче на вход Т логического нуля (отсутствие счетного импульса) на выходах ИЛЭ D2.2 и D3.1 будет логическая единица, что приводит к тому, что состояние основного триггера не изменится. На выходах элементов памяти D2.1 и D3.2 установятся, соответственно логические сигналы единица и ноль. При изменении сигнала Т от 0 до 1 (наличие перепада от 0 до 1) на выходе D2.2 сигнал изменяется от 1 к 0, а на выходе D3.1 остается единичным, так как на выходе D3.2 до прихода перепада сигнал равнялся 0. При этом Q n 1 1 и Q n 1 0 , а сигналы на выходах элементов памяти D2.1 D3.2 изменяются на обратные. После окончания входного импульса на выходах элементов D2.2 и D3.1 будут единичные сигналы и основной триггер не изменит своего состояния. С приходом следующего счетного импульса, с учетом состояния элементов памяти, основной триггер изменит свое состояние на обратное, то есть Q = 0. Рассмотренная схема Т-триггера реагирует на перепады из 0 в 1, то есть данный триггер является триггером с прямым динамическим входом (рис. 4.22, б). Рис. 4.23 Примером реализации Т-триггера в виде интегральной микросхемы может служить TR-триггер К6500ТТ1, способный переключаться с частотой свыше 1 ГГц (рис. 4.23). 4.4.5. Триггер Шмитта на ИЛЭ Триггер Шмитта существенно отличается от рассмотренных видов триггеров прежде всего тем, что он не выполняет функцию хранения информации. Его характеристика передачи имеет гистерезис с двумя пороговыми значениями напряжений U пор1 и U пор2 на входе, при которых происходит опрокидывание триггера из одного состояния в другое. Благодаря этому свойству, триггер Шмитта формирует прямоугольные импульсы из колебаний произвольной формы. Триггер-формирователь, аналогичный триггеру Шмитта, можно построить на ИЛЭ. Схема такого триггера на ИЛЭ И-НЕ и графики напряжений на входе и выходе приведены на рис. 4.24,а,б. Рис. 4.24 Для создания регенеративного процесса переключения необходимо обеспечить определенное отношение R0 R . Ширина петли гистерезиса определяется разностью U пор1 U пор 2 . Значения U пор1 и U пор 2 зависят от уровней выходного напряжения U 1 и U 0 , изменяющихся при смене логических элементов и увеличении (уменьшении) нагрузки на триггер. Это является существенным недостатком данного типа триггера. 4.5. Регистры 4.5.1. Назначение и классификация регистров Регистром называется последовательностный ЦУ, предназначенный для записи, кратковременного хранения и последующего считывания информации, представленной в виде n - разрядной кодовой комбинации (двоичного числа, слова). Регистры могут также использоваться в качестве счетчиков и делителей частоты, узлов временной задержки импульсов. В соответствии с выполняемыми функциями регистры делятся на два класса: регистры хранения (памяти) и регистры сдвига (сдвигающие регистры). Регистры сдвига могут быть двунаправленными, т.е. записанное в них слово можно сдвигать как вправо, так и влево. Для подачи сигнала включения режима сдвига влево или вправо имеется специальный вход. Разновидностью сдвигающих регистров являются кольцевые и рекуррентные регистры. Занесение информации в регистр называется операцией ввода или записи. Выдача информации на внешние устройства называется операцией вывода или считывания. По способу вывода информации различают регистры с последовательным и параллельным выводом. Основными характеристиками регистров являются разрядность и быстродействие. Разрядность регистра определяет количество разрядов записываемого слова. Быстродействие регистра определяется максимально возможной тактовой частотой, с которой производится запись, сдвиг и считывание информации. 4.5.2. Регистры хранения Регистры хранения предназначены для записи, хранения и считывания информации. Принцип построения регистра хранения на RS – триггерах приведен на рис.4.25,а. Основу регистра составляют одноступенчатые RS – триггеры. Каждый триггер служит для записи и хранения одного двоичного разряда слова Аа n 1 , a n 2 ,...a1 , a 0 , то есть для записи n – разрядного слова необходимо n триггеров. Перед записью информации все триггеры устанавливаются в нулевое состояние подачей положительного единичного импульса по шине УСТ. "0". Разряды слова А подводятся к S – входам триггеров через схемы совпадения (ЛЭ "И"), управляемые по шине "ЗАПИСЬ" единичными импульсами Е. При сигнале Е=0 обеспечивается режим хранения записанной информации, то есть новая информация на установочные входы S не подается. Вывод информации из регистра может осуществляться в прямом и обратном коде через схемы совпадения, управляемые сигналами Е Z1 и Е Z 2 . Для считывания информации в требуемом коде необходимо на соот- ветствующую шину подать единичный импульс. По окончании считывания на RS – триггеры регистра подается сигнал сброса в "0", после чего регистр готов принимать и хранить следующее слово. Рис.4.25 Таким образом, для записи, хранения и считывания одного разряда слова необходимы элемент памяти (триггер) и ЛЭ на входе и выходе. Эта элементарная часть схемы регистра иногда называется его разрядом. Условное графическое обозначение регистра хранения приведено на рис.4.25,б. Упрощенная схема регистра хранения на синхронных одноступенчатых D -триггерах с динамическим управлением по входу синхронизации приведена на рис.4.26. Достоинством регистра на синхронных D -триггерах является существенное уменьшение числа соединений в узле, отсутствие шины сброса разрядов регистра в нулевое состояние, так как D -триггеры при нулевом сигнале на входе самостоятельно устанавливаются в нулевое состояние. При использовании D -триггеров с динамическим управлением по входу синхронизации повышается устойчивость регистра к помехам, поскольку воздействие помех возможно только в течение короткого интервала времени, равного длительности переключения триггера после перепада сигнала C . Рис.4.26 Примером регистра хранения является ИМС К155 ИР15. В этом регистре, УГО которого приведено на рис.4.27, в отличие от приведенной на рис.4.26, имеется два равноценных инверсных разрешающих входа (запись) Е1 и Е2, а также два инверсных входа Е Z1 и Е Z 2 для вывода информации в инверсном виде. Рис.4.27 4.5.3. Регистры сдвига Регистры сдвига, кроме функций, выполняемых регистрами памяти, позволяют осуществлять сдвиг информации вправо и влево под воздействием тактовых импульсов. Если в регистры хранения двоичное слово записывается параллельным кодом, то в регистры сдвига – последовательным. По направлению сдвига информации, записанной в регистре, различают регистры прямого сдвига или сдвига вправо, т.е. в сторону младшего разряда, регистры обратного сдвига или сдвига влево в сторону старшего разряда и реверсивные регистры, допускающие сдвиг в обоих направлениях. Регистры сдвига реализуются, как правило, на синхронных D и JK - триггерах со статическим или динамическим управлением. Такие регистры имеют информационный вход, вход тактовых импульсов и установочный вход. Выходы в регистре сдвига могут быть с триггера каждого разряда для считывания информации параллельным кодом или только с последнего младшего разряда для считывания информации последовательным кодом. Схема четырехразрядного регистра сдвига вправо на синхронных D -триггерах с прямым динамическим входом С приведена на рис.4.28,а.. Регистр обеспечивает запись информации по входу D последовательным кодом и ее считывания как в последовательном, так и параллельном коде Условное графическое обозначение регистра приведено на рис.4.28,б. Стрелка под обозначением регистра RG в основном поле показывает направление сдвига информации. В схеме прямой выход Q каждого предыдущего (левого) триггера соединен со входом D последующего триггера. Перед записью информации регистр устанавливается в нулевое состояние подачей положительного импульса по шине «СБРОС». Рис.4.28 Двоичное число в последовательном коде, начиная с младшего разряда, подается на вход D триггера старшего разряда T3 . По фронту каждого тактового импульса кодовая комбинация будет продвигаться от разряда к разряду вправо и после окончания четвертого тактового импульса запишется в регистр. Таким образом, для записи n-разрядного слова необходимо подать n импульсов сдвига. Считывание информации последовательным кодом осуществляется, как и запись, путем поразрядного сдвига записанной информации к выходу Q0 . При этом на вход D триггера T3 подается напряжение логического нуля, что приводит к последовательному обнулению всех триггеров последовательностью тактовых импульсов. Для считывания информации последовательным кодом потребуется такое же число импульсов сдвига, как и при записи. Считывание информации параллельным кодом осуществляется в паузе между последним n -ым импульсом сдвига одного цикла записи и первым импульсом сдвига другого цикла записи или считывания последовательным кодом. Таким образом, с помощью регистра сдвига можно осуществлять преобразование двоичного кода из последовательной формы представления в параллельную. Если в триггерах, на которых собран регистр, кроме входа D , имеются установочные входы S , то можно осуществить запись в регистр информации параллельным кодом и преобразовать ее из параллельной формы представления в последовательную. Рис.4.29 Сброс (установка в нулевое состояние триггеров) регистра перед записью нового двоичного слова в последовательном коде может и не производиться, так как при подаче новой кодовой комбинации все триггеры регистра опрокинутся в соответствующие состояния. На рис.4.29 приведены временные диаграммы состояний триггеров регистра при записи и считывании последовательным кодом числа 11(10)=1011(2). Приведенный на рис.4.28 регистр осуществляет сдвиг информации вправо (в сторону младших разрядов). В регистре со сдвигом влево (рис.4.30) двоичное слово, начиная со старшего разряда, подается на вход триггера младшего разряда. Выход этого триггера соединен со входом более старшего разряда и т.д. Рис.4.30 Рассмотренные регистры сдвига на D -триггерах (рис.4.28 и 4.30) имеют однопроводную связь между разрядами. При построении регистров на RS и JK -триггерах должна осуществляться двухпроводная (парафазная) связь. Причем для записи информации в последовательном коде необходимо, чтобы триггер, на который подается информация, работал как D -триггер. Схема регистра сдвига на двухступенчатых JK триггерах с установочными входами и ее условное графическое обозначение приведены на рис.4.31. а Рис.4.31 б JK -триггер преобразован в D -триггер соединением входов J и K через инвертор. Для триггеров TT2 , TT1 и TT0 такого преобразования не требуется, так как соединения входов J и K с выходами предыдущего триггера парафазные. Установочные входы S 0 , S1 , S 2 , S 3 используются для записи информации в регистр параллельным кодом. Регистры сдвига могут быть построены и на одноступенчатых триггерах. В этом случае в каждом разряде регистра необходимо использовать два триггера, которые управляются двумя сдвинутыми во времени тактовыми импульсами. Наличие двух триггеров в одном разряде обеспечивает поразрядное продвижение информации в регистре от входа к выходу. Применение одноступенчатых триггеров по одному на разряд привело бы к нарушению правила работы регистра сдвига – при первом же импульсе сдвига информация, записанная в первый разряд, перешла бы последовательно во второй, третий и т.д. разряды. Номенклатура микросхем регистров довольно большая. Регистры имеются и ТТЛ (ТТЛШ), ЭСЛ и КМОП сериях. Как правило, ИМС регистров комбинированные, то есть выполняют функции как регистров хранения, так и регистров сдвига. Они работают в различных режимах, например, сдвиг вправо, влево, прием параллельного и последовательного кода, вывод параллельного и последовательного кода. Для реализации указанных режимов в ИМС применяются соответствующие логические схемы управления. Микросхемы регистров обозначаются двумя буквами ИР. Перед буквой стоит обозначение серии, а после них номер микросхемы. Например, К155 ИР1 (четырехразрядный сдвиговый регистр с последовательным и параллельным вводом данных, ТТЛ серии), К561 ИР6 (восьмиразрядный с параллельными и последовательными входами и выходами, КМОП серии), К500 ИР141 (четырехразрядный регистр, работающий в четырех режимах: хранение, сдвиг вправо, сдвиг влево, параллельный прием, ЭСЛ серии). Особую группу регистров составляют специализированные регистры последовательного приближения для построения аналого-цифровых преобразователей (К155 ИР17, К564 ИР13). 4.5.4. Кольцевые регистры Кольцевые регистры строятся на основе сдвигающих регистров путем соединения выхода триггера младшего разряда со входом триггера старшего. Такие регистры (рис.4.32,а) находят применение в счетчикахделителях и распределителях импульсов. Распределитель импульсов предназначен для формирования поочередно следующих друг за другом импульсных сигналов в различных целях. Как следует из временных диаграмм (рис.4.32,б), число цепей равно разрядности регистра. В исходном состоянии триггер ТТ 3 находится в единичном состоянии, так как на установочный вход S подан единичный сигнал. При подаче синхроимпульсов 1 в каждом такте переписывается в последую- щий триггер. На входах триггеров длительность импульсов определяется периодом тактовых импульсов t и Т с . а б Рис.4.32 После опрокидывания из 0 в 1 триггера младшего разряда ТТ 0 за счет обратной связи на входы J и K триггера старшего разряда происходит его опрокидывание в единичное состояние в следующем такте. Сигналы, снимаемые с выходов Q триггеров кольцевого регистра, могут быть использованы для поочередного управления различными устройствами. 4.5.5.Рекуррентные регистры Рекуррентные регистры представляют собой сдвигающие регистры, охваченные цепью логической обратной связи. Обычно в качестве элемента логической обратной связи используется сумматор по модулю 2. На рис.4.33. представлена схема четырехразрядного рекуррентного регистра, в котором на вход сумматора по модулю два подаются сигналы с выходов Q0 и Q1 триггеров, а выход сумматора соединен со входом J- триггера ТТ3. Рис.4.33 Порядок сдвига информации в регистре при подаче тактовых импульсов приведен в таблице 4.8. В исходном состоянии триггер ТТ3. устанавливается в состояние 1 подачей на установочный вход S единичного сигнала. Все остальные триггеры регистра - в нулевом состоянии. Сигналы сдвига "С" продвигают записанную в ТТ3 единицу сначала в триггер ТТ2, а затем в TT1. При опрокидывании триггера TT1 в единичное состояние на вход сумматора по модулю два подается комбинация Q1Q 0 10 . При этом на его выходе имеет место сигнал F Q 1 Q 0 1 0 1 , что приводит в третьем такте к записи 1 в триггере Q 3 . Учитывая, что в третьем такте триггер ТТ0 опрокидывается в 1, а TT1 - в 0, на входе сумматора по модулю два имеет место комбинация 01, что приводит в четвертом такте к тому, что триггер ТТ3 остается в единичном состоянии. В соответствии с таблицей 2.1. в течение 14 тактов комбинации состояний триггеров регистра будут различными. Комбинация 15 такта повторяет исходную, и цикл затем повторяется. Таким образом, данный четырехразрядный регистр с логической обратной связью формирует периодическую рекуррентную последовательность вида 1000010000101001, длиной М 2 4 1 периодов сдвигающих импульсов. Такие рекуррентные последовательности называются Мпоследовательностями. В этих последовательностях в течение полного цикла М max 2 n 1 (n - количество триггеров в регистре) чередование нулей и единиц осуществляется по случайному закону, однако в следующем цикле закон следования повторяется. Поэтому такую последовательность называют псевдослучайной. Таблица 4.8. Номер такта Исходное состояние I 2 3 4 5 6 7 8 9 10 II 12 13 14 15 Q3 Q Q2 Q1 Q0 1 0 0 0 0 0 I I 0 I 0 I I I I 0 0 0 I 0 0 I I 0 I 0 I I I I 0 0 0 I 0 0 I I 0 I 0 I I I I 0 0 0 I 0 0 I I 0 I 0 I I I I I 0 0 0 Рекуррентная последовательность полного цикла, длиной М max 2 n 1 получается при подключении одного из входов сумматора по модулю два только строго к определенному выходу триггера. Так, в приведенной схеме - к выходу Q1. При других подключениях этого входа получаются частичные рекуррентные циклы. Рекуррентные регистры находят применение для получения длинных кодовых комбинаций, приближающихся по своим статистическим характеристикам к флюктуационному (белому) шуму, в схемах кодирующих и декодирующих устройств широкополосных систем связи, при формировании сигналов синхронизации (фазирования) в системах передачи данных и т.п. Широкое применение получили рекуррентные регистры в генераторах псевдослучайных последовательностей, используемых при формировании изменяющихся временных интервалов (циклов). 4.6. Счетчики 4.6.1. Назначение и классификация счетчиков Счетчиком называется последовательностный цифровой узел (ПЦУ), осуществляющий счет числа входных импульсов и фиксирующий их число в каком-либо коде. Элементами счетчика являются Т-триггеры. Счетчик, состоящий из n триггеров, позволяет подсчитать 2 n входных импульсов, причем код числа подсчитанных импульсов определяется состоянием триггеров, входящих в счетчик. С приходом очередного счетного импульса происходит изменение состояния триггеров, что и отражает в заданном коде результат счета. Основными параметрами счетчиков являются модуль (коэффициент) пересчета Ксч и быстродействие. Модуль пересчета определяется числом возможных устойчивых состояний счетчика. Для двоичных счетчиков, т.е. счетчиков, работающих в двоичной системе счисления, модуль пересчета равен K сч 2 n , (4.21) где n – число триггеров (разрядов) счетчика. Применяя обратные связи, можно получить любой целый коэффициент пересчета от K min 2k 1 1 до K max 2n при 2 K n . Быстродействие счетчика определяется разрешающим временем t разр . Разрешающим временем называется минимальный отрезок времени между двумя счетными импульсами, при котором обеспечивается нормальное функционирование счетчика. При подаче на вход счетчика периодической последовательности счетных импульсов быстродействие счетчика оценивается минимальным периодом t разр Tmin или максимальной частотой поступающих импульсов Fmax 1 . Tmin Счетчики можно классифицировать по способу кодирования, направлению счета и способу межразрядного переноса сигналов. По способу кодирования состояний разрядов различают счетчики с позиционным кодированием "вес" каждого разрда постоянен и состояние счетчика после поступления i го импульса определяется выражением (4.22) Аi а n1 2 n1 а n 2 2 n 2 ...а j 2 j ... а 0 2 0 ; го где а j -состояние; j -разряда счетчика после воздействия i го входного j го импульса; n -число разрядов счетчика; 2 -вес j разряда счетчика. Счетчики с непозиционным кодированием не имеют постоянных весов разрядов, что может привести к некоторому усложнению их схем. По направлению счета счетчики подразделяются на суммирующие, показания которых возрастают на единицу с приходом каждого входного сигнала; вычитающие, показания которых уменьшаются на единицу с приходом каждого входного сигнала; и реверсивные, которые могут работать как суммирующие и вычитающие в зависимости от сигналов управления. По способу межразрядного переноса сигналов различают счетчики с последовательным, параллельным, сквозным и комбинированным переносом единицы от разряда к разряду. Счетчики, построенные на основе асинхронных триггеров, называются асинхронными, а счетчики синхронных триггеров – синхронными. Конструктивно цифровой счетчик может быть выполнен как в виде совокупности ИМС триггеров, соединенных по печатной плате, так и в виде одной ИМС повышенного уровня интеграции, содержащей сформированную на одной подложке схему многоразрядного счетчика. 4.6.2. Суммирующие счетчики с последовательным переносом Схема двоичного трехразрядного суммирующего счетчика на двухступенчатых Т-триггерах приведена на рис.4.34,а, а его условное графическое обозначение на рис.4.34,б. В исходном состоянии триггеры счетчика установлены в состояние "0" подачей импульса сброса на вход "УСТ.0". При подаче первого счетного импульса U сч триггер младшего разряда опрокидывается в единичное состояние, причем на выходе Q0 единичный перепад появится только после окончания импульса счета, так как двухступенчатый триггер опрокидывается по отрицательному перепаду входного напряжения. Задержка опрокидывания триггера ТТ 0 относительно отрицательного перепада импульса счета составляет t зд.тр.ср. . Вторым счетным импульсом триггер ТТ 0 опрокидывается в исходное состояние (нулевое). При этом отрицательным перепадом напряжения на выходе Q0 первого триггера опрокидывается в единичное со- стояние триггер TT1 . Третьим счетным импульсом триггер ТТ 0 опрокидывается в единичное состояние, а TT1 остается в единичном состоянии, так как отрицательный перепад напряжения на входе T -триггера отсутствует. Из временных диаграмм (рис.4.34,в) следует, что в промежутках между счетными импульсами совокупное состояние выходов Q 2 , Q1 , Q0 триггеров счетчика представляет собой двоичный код числа поступающих на вход счетных импульсов. Этот двоичный код и считы- вается с выходов Q 2 , Q1 , Q0 для определения числа поступивших на вход счетчика импульсов. Рис.4.34 В суммирующем счетчике запуск каждого последующего триггера осуществляется только после опрокидывания предыдущего, то есть с задержкой, показанной на временных диаграммах. При последовательном опрокидывании разрядных триггеров задержка распространения накапливается, что снижает быстродействие счетчика. Так, разрешающее время для n -разрядного счетчика: (4.23) t разр. nt зд.тр.ср. 4.6.3. Вычитающие счетчики с последовательным переносом В вычитающем счетчике при каждом входном счетном импульсе двоичный код записанного числа должен уменьшаться на единицу. Схема такого счетчика (рис.4.35,а) отличается от схемы суммирующего счетчика тем, что счетный вход каждого последующего триггера соеди- няется не с прямым, а с инверсным выходом предыдущего. Условное графическое обозначение вычитающего двоичного счетчика приведено на рис.4.35,б. Пусть в исходном состоянии подачей единичного сигнала на установочные входы S триггеров в счетчик записано десятичное число 7, то есть Q2 1, Q1 1, Q0 1 . Тогда при подаче первого импульса счета первый триггер опрокидывается в нулевое состояние, то есть в счетчике уже будет записано число 6 ( Q 2 1, Q1 1, Q0 0 ). При подаче второго импульса счета триггер ТТ 0 опрокидывается в единичное состояние, а триггер TT1 -в нулевое, так как напряжение на выходе Q 0 изменяется из 1 в 0 и на счетном входе триггера TT1 действует отрицательный перепад. На рис.2.11,в приведены временные диаграммы счетчика, показывающие, что код записанного числа с приходом восьми импульсов счета изменяется последовательно от 7 до 0. Рис4.35 ЛИТЕРАТУРА 1. Бродин В.Б., Шагурин И.И. Микроконтроллеры: Справочник. – М.: ЭКОМ, 1999. – 395с. 2. Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.Н. Микросхемы и их применение: Справ. Пособие. – 3-е изд., перераб. и доп. – М.: Радио и связь,1989. – 240с. 3. Гилмор Ч. Введение в микропроцессорную технику: Пер. с англ. _ М.: Мир, 1984. 334 с. 4. Гусев В. В.,Зеличенко Л.Г., Конев К.В. и др. Основы импульсной и цифровой техники. Уч. Пос. для вузов. – М.: Сов. Радио, 1975. – 440с. 5. Зельдин Е.А. Цифровые интегральные микросхемы в информационной измерительной аппаратуре. – Л.: Энергоатомиздат, 1986. – 280с. 6. Каган Б.М., Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. – М.: Энергоатомиздат, 1983. - 304 с. 7. Клочков Г.Л. Импульсные и цифровые узлы радиоэлектронных средств. В 4 - х частях. – Воронеж: ВИРЭ, 1995. – 560 с. 5. Лебедев О.Н., Мирошниченко А.В., Телец В.А. Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. Микросхемы ЦАП и АЦП: Справочник – М.: Радио и связь, 1994. - 248 с. 6. Микросхемы памяти, ЦАП и АЦП: Справочник – 2-е изд. /О.Н. Лебедев, А-Й. К. Марцинкявичус, Э-А. К. Багданскис и др. – М.: КУбК-а, 1996. - 384 с. 7. Макаров Г.В., Плутес Д.В., Тюрин С.В. Элементы проектирования микропроцессорных устройств и систем: Учебное пособие. Воронеж: Издво ВГТУ, 1998. - 128 с. 8. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. – М.: Радио и связь, 1990. – 304с. 9. Память на любой вкус.Компьютер пресс, декабрь 2002г. 10. Сташин В.В., Урусов А.В., Мологонцева О.Ф. Проектирование цифровых устройств на однокристальных микроконтроллерах. – М.: Энергоатомиздат, 1990. – 224 с. 11. Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ – Санкт-Петербург, 2000. 528 с. 12. Фрике К. Вводный курс цифровой электроники. – М: Техносфера, 2003. 432с. 13. Хоровиц П., Хилл У. Искусство схемотехники: В трех томах: Т.2. Пер. с англ. – 4-е изд., перер. и доп. – М.: Мир, 1993. – 371 с. 14. Шило В.Л. Популярные цифровые микросхемы: Справочник / 2-е изд. – Челябинск: Металлургия, 1989. – 352 с.