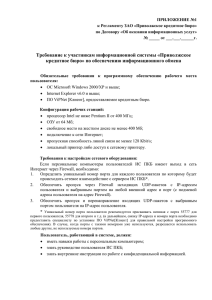

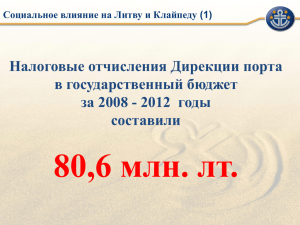

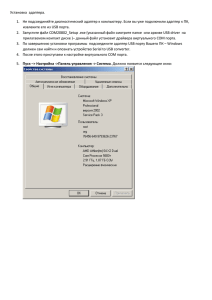

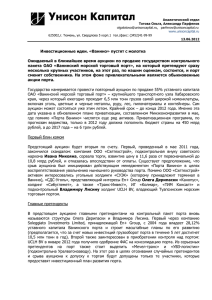

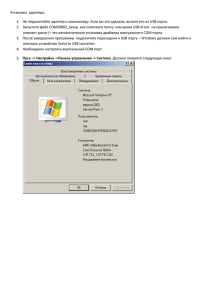

Министерство науки и образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования «Магнитогорский государственный технический университет им. Г.И. Носова» Институт энергетики и автоматизированных систем Кафедра электроники и микроэлектроники ЛАБОРАТОРНАЯ РАБОТА №2 по дисциплине «Микропроцессоры» Выполнение арифметических и логических операций с двоичными многобайтными числами Выполнил: Рахмангулов А.Д студент 5 курса, группы зЭАНб-13 Проверил, к.т.н., Усатый Д.Ю. Магнитогорск, 2018 Цель работы Исследовать работу микроконтроллера при работе арифметических, логических команд, команд сдвига и команд битового процессора. Задание №1. Установить в «1» биты 0-3 порта 1. Таблица 1 – Программа 1 на Ассемблере. Метка MAIN Ассемблер Комментарии $MOD812 Ссылка на файл с предопределёнными символиками CSEG Директива для указания начала сегмента памяти ORG 0000h Начальный адрес, где размещаются команды AJMP MAIN Перейти на адрес начала программы ORG 0100h Начальный адрес основной программы SETB P1.0 установка бита 0 порта 1 в 1 SETB P1.1 установка бита 1 порта 1 в 1 SETB P1.2 установка бита 2 порта 1 в 1 SETB P1.3 установка бита 3 порта 1 в 1 Рисунок 1 – действие программы установки в «1» биты 0-3 порта 1. 2 Задание №2. Сбросить в «0» биты 0, 2 и 6 порта 2. Таблица 2 – Программа 1 на Ассемблере. Метка MAIN Ассемблер Комментарии $MOD812 Ссылка на файл с предопределёнными символиками CSEG Директива для указания начала сегмента памяти ORG 0000h Начальный адрес, где размещаются команды AJMP MAIN Перейти на адрес начала программы ORG 0100h Начальный адрес основной программы CLR P2.0 Сброс бита 0 порта 2 в 0 CLR P2.2 Сброс бита 2 порта 2 в 0 CLR P2.6 Сброс бита 6 порта 2 в 0 Рисунок 2 – действие программы сброса в «0» биты 0,2 и 6 порта 2. Задание №3. Выбрать нулевой банк регистров. Таблица 3 – Программа 3 на Ассемблере. Метка Ассемблер Комментарии $MOD812 Ссылка на файл с предопределёнными символиками CSEG Директива для указания начала сегмента памяти ORG 0000h Начальный адрес, где размещаются команды AJMP MAIN Перейти на адрес начала программы 3 MAIN ORG 0100h Начальный адрес основной программы CLR RS0 Выбор нулевого банка регистров CLR RS1 Выбор нулевого банка регистров Рисунок 3 – действие программы выбора нулевого банка регистров. Задание №4. Проинвертировать биты 7,6,5 порта 0. Таблица 4 – Программа 4 на Ассемблере. Метка MAIN Ассемблер Комментарии $MOD812 Ссылка на файл с предопределёнными символиками CSEG Директива для указания начала сегмента памяти ORG 0000h Начальный адрес, где размещаются команды AJMP MAIN Перейти на адрес начала программы ORG 0100h Начальный адрес основной программы CPL P0.7 инвертирование бита 7 порта 0 CPL P0.6 инвертирование бита 6 порта 0 CPL P0.5 инвертирование бита 5 порта 0 4 Рисунок 4 – действие программы проинвертировать биты 7,6,5 порта 0. Задание №5. Вычислить булеву функцию трех переменных: 𝑌 = 𝑋 × 𝑉 + 𝑊 × (𝑋 + 𝑉) Переменные X, V, W поступают на линии 2, 1, 0 порта P0 соответственно. Результат Y выводится на линию 3 порта P1. Таблица 5 – Программа 5 на Ассемблере. Метка Ассемблер Комментарии $MOD812 Ссылка на файл с предопределёнными символиками Q1 EQU P2.0 Замена порта ввода-вывода P2.0 на символическое имя Q1 X EQU P0.2 Замена порта ввода-вывода P0.2на символическое имя X V EQU P0.1 Замена порта ввода-вывода P0.1 на символическое имя V W EQU P0.0 Замена порта ввода-вывода P0.0 на символическое имя W 5 MAIN Y EQU P1.3 Замена порта ввода-вывода P1.3 на символическое имя Y CSEG Директива для указания начала сегмента памяти ORG 0000h Начальный адрес, где размещаются команды AJMP MAIN Перейти на адрес начала программы ORG 0100h Начальный адрес основной программы CLR C Сброс бита C MOV C, X Загрузка бита X в бит C ANL C, V Логическое умножение битов C и V MOV Q1, C Загрузка бита C в бит q1 MOV C, X Загрузка бита X в бит C ORL C, V Логическое сложение битов C и V ANL C, W Логическое умножение битов C и W ORL C, Q1 Логическое сложение битов C и Q1 MOV Y, C Выгрузка бита C в бит Y Рисунок 5 – действие программы вычисление булевой функции трех переменных 6 Задание №6. Сложить два двоичных многобайтных числа. Оба слагаемых расположены в Памяти Данных последовательно, начиная с младшего байта. Начальные адреса слагаемых хранятся в регистрах R0=00 и R1=02. Формат слагаемых задан в R2=02 (количество байт в слагаемых). Результат поместить на место 1 слагаемого. Написать и загрузить в ADSim812 программу приведенную выше. Разобрать ее работу и дать комментарии к программе. Составить алгоритм работы программы. Определить время ее выполнения. Таблица 6 – Программа на Ассемблере. Метка MAIN M1 Ассемблер Комментарии $MOD812 Ссылка на файл с определением мнемокодов адресов CSEG Директива для указания начала сегмента памяти программ ORG 0000h Адрес нулевого вектора прерывания(вектора системного сброса) AJMP MAIN Переход на начальный адрес программы ORG 0100h Указываем компилятору на адрес начала программы MOV R0, #00 Загрузка числа 00h в регистр R0 MOV R1, #02 Загрузка числа 02h в регистр R1 MOV R2, #02 Загрузка числа 02h в регистр R2 CLR C Сброс бита C для следующего сложения с переносом MOV A, @R0 Помещаем в аккумулятор слагаемое, адрес слагаемого в рег. 0 ADDC A, @R1 Складываем аккумулятор с слагаемым по адресу в рег. 1 MOV @R0, A Перемещаем результат из аккумулятора по адресу в рег.1 INC R0 Увеличиваем на единицу R0 INC R1 Увеличиваем на единицу R1 DJNZ R2, M1 Декрементируем R2 и если не результат не ноль переходим на М1 END Директива, указывающая компилятору на завершение программы 7 Рисунок 6 – программа в ADSim812 Алгоритм работы программы представлен комментариями к программе. Программа складывает нулевую ячейку ОЗУ со второй, размещает результат в нулевой ячейке. Так же складывает первую ячейку с третьей, результат размещает в первой. Полностью программа состоит из выполнения 17 инструкций, что составило 20 циклов тактового генератора, при частоте тактирования 12 МГц время выполнения программы эмулятором составило 20 микросекунд, мне не удалось понять, откуда есть такое несоответствие, ведь при частоте 12МГц один такт составит примерно 0,083мкс. По-видимому, ядро подключено через предделитель. Один цикл сложения составляет 6 инструкций, выполняемых за 7 тактов, в два такта выполняется инструкция DJNZ, также как и инструкция в начале программы – AJMP. Мне стало интересно, и я попробовал применить инструкцию SJMP, она так же выполнилась за два такта, что позволяет утверждать – команды переходов выполняются дольше других команд и для быстродействия программы необходимо стремиться их снизить. 8

![Вопросы на экзамен [27 Kb, doc]](http://s1.studylib.ru/store/data/003661877_1-87d61786810e1856df8e7abc314ad5bc-300x300.png)