Н. М. Закарлюк

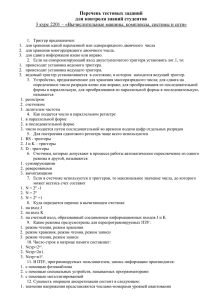

ЦИФРОВЫЕ УСТРОЙСТВА

АВТОМАТИКИ И ТЕЛЕМЕХАНИКИ

Оглавление

1. ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ ..............................6

1.1. Основные теоретические сведения ....................................................6

1.1.1. Функции алгебры логики...........................................................6

1.1.2. Законы булевой алгебры ............................................................9

1.1.3. Взаимное соответствие булевых функций и логических схем ..14

1.1.4. Полные системы функций алгебры логики ............................ 15

1.1.5. Булевский базис ....................................................................... 16

1.1.6. Базис И-НЕ .............................................................................. 19

1.1.7. Базис ИЛИ-НЕ ......................................................................... 20

1.1.8. Сумма по модулю 2 .................................................................. 22

1.1.9. ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ ................................................. 23

1.2. Лабораторная работа № 1. Исследование логических элементов .. 25

1.2.1. Задания для самостоятельной подготовки .............................. 25

1.2.2. Методические рекомендации .................................................. 25

1.2.3. Порядок выполнения работы .................................................. 29

1.2.4. Содержание отчета ................................................................... 29

1.3. Контрольные вопросы ...................................................................... 29

2. СХЕМЫ КОНТРОЛЯ ЧЕТНОСТИ, ЦИФРОВЫЕ КОМПАРАТОРЫ,

СУММАТОРЫ .......................................................................................... 35

2.1. Основные теоретические сведения .................................................. 35

2.1.1. Контроль четности ................................................................... 35

2.1.2. Устройства сравнения .............................................................. 41

2.1.3. Сумматоры................................................................................ 45

2.2. Лабораторная работа № 2. Исследование схем контроля

четности, сравнения и сумматоров .................................................. 51

2.2.1. Задания для самостоятельной подготовки .............................. 51

2.2.2. Порядок выполнения работы .................................................. 52

2.2.3. Содержание отчета ................................................................... 58

2.3. Контрольные вопросы ...................................................................... 58

3

3. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ ............................................................... 60

3.1. Основные теоретические сведения .................................................. 60

3.1.1. Триггерные системы ................................................................ 60

3.1.2. Асинхронные и синхронные триггеры .................................... 62

3.1.3. Способы управления триггерами ............................................ 64

3.1.4. Активные и пассивные логические уровни элементов........... 66

3.1.5. Асинхронный RS-триггер с прямыми входами ....................... 67

3.1.6. Асинхронный RS-триггер с инверсными входами ................. 70

3.1.7. Статический синхронный D-триггер ...................................... 71

3.1.8. Динамический синхронный D-триггер ................................... 73

3.1.9. Счетный Т-триггер ................................................................... 76

3.1.10. JK-триггеры ............................................................................ 78

3.1.11. Триггеры Шмитта ................................................................... 79

3.2. Лабораторная работа № 3

Исследование основных типов интегральных триггеров ................ 81

3.2.1. Задания для самостоятельной подготовки .............................. 81

3.2.2. Порядок выполнения работы .................................................. 81

3.2.3. Содержание отчета ................................................................... 87

3.3. Контрольные вопросы ...................................................................... 87

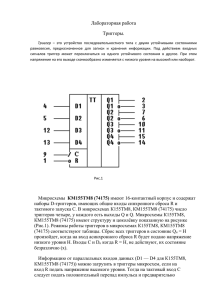

4. РЕГИСТРЫ ............................................................................................... 90

4.1. Основные теоретические сведения .................................................. 90

4.1.1. Параллельный регистр ............................................................. 91

4.1.2. Последовательный регистр (регистр сдвига) .......................... 92

4.1.3. Универсальный регистр ........................................................... 95

4.2. Лабораторная работа № 4. Исследование работы регистров .......... 97

4.2.1. Задания для самостоятельной подготовки .............................. 97

4.2.2. Порядок выполнения работы .................................................. 97

4.2.3. Содержание отчета ................................................................. 102

4.3. Контрольные вопросы .................................................................... 102

5. СЧЕТЧИКИ ИМПУЛЬСОВ................................................................... 104

5.1. Основные теоретические сведения ................................................ 104

5.1.1. Характеристики и классификация счетчиков ....................... 104

5.1.2. Условное графическое обозначение счетчиков .................... 109

5.1.3. Способы построения и принцип действия простейших

счетчиков ................................................................................110

5.2. Лабораторная работа № 5

Исследование счетчиков электрических импульсов .....................124

5.2.1. Задания для самостоятельной подготовки ............................ 124

4

5.2.2. Порядок выполнения работы ................................................ 124

5.2.3. Содержание отчета ................................................................. 128

5.3. Контрольные вопросы .................................................................... 128

6. КОДИРУЮЩИЕ УСТРОЙСТВА ЦИФРОВОЙ ТЕХНИКИ .............. 131

6.1. Основные теоретические сведения ................................................ 131

6.1.1. Мультиплексоры .................................................................... 131

6.1.2. Демультиплексоры ................................................................. 137

6.1.3. Дешифраторы ......................................................................... 140

6.1.4. Преобразователи произвольных кодов ................................. 144

6.2. Лабораторная работа № 6. Исследование дешифратора,

демультиплексора и мультиплексора ............................................155

6.2.1. Задания для самостоятельной подготовки ............................ 155

6.2.2. Порядок выполнения работы ................................................ 155

6.2.3. Содержание отчета ................................................................. 164

6.3. Контрольные вопросы .................................................................... 165

7. КОНТРОЛЬ РАБОТЫ ЦИФРОВЫХ УСТРОЙСТВ ............................. 167

7.1. Основные теоретические сведения ................................................ 167

7.1.1. Основные понятия о системах контроля .............................. 167

7.1.2. Основные понятия теории кодирования .............................. 169

7.1.3. Контроль по методу Хэмминга .............................................. 171

7.1.4. Контроль с использованием структурной избыточности..... 178

7.2. Лабораторная работа № 7

Исследование методов контроля работы цифровых устройств .... 184

7.2.1. Задания для самостоятельной подготовки ............................ 184

7.2.2. Порядок выполнения работы ................................................ 185

7.2.3. Содержание отчета ................................................................. 190

7.3. Контрольные вопросы .................................................................... 190

БИБЛИОГРАФИЧЕСКИЙ СПИСОК ...................................................... 191

Приложение 1.1. Функциональный набор ЛЭ ..................................... 192

Приложение 1.2. Наличие ЛЭ в сериях ТТЛ, ТТЛШ, КМДП ............. 194

Приложение 1.3. Основные характеристики серий логических ИМС..... 196

5

1. ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ

1.1. Основные теоретические сведения

1.1.1. Функции алгебры логики

Математический аппарат, описывающий действие цифровых

устройств, базируется на алгебре логики, или, как ее еще называют по

имени автора – английского математика Джорджа Буля (1815–1864),

булевой алгебре. Алгебра логики имеет дело с высказываниями. Под

высказыванием понимают любое утверждение, в отношении которого можно утверждать, истинно оно или ложно. Высказывания могут

быть простыми или сложными: первые не зависят от других высказываний, а вторые образуются от двух или более простых высказываний. Простые высказывания называют логическими переменными,

а сложные – логическими функциями этих переменных. Логические

переменные, в отличие от переменных обычной алгебры, могут принимать только два значения, называемые различными авторами ИСТИНА и ЛОЖЬ, TRUE и FALSE, ДА и НЕТ, 1 и 0. Наиболее распространено последнее обозначение. При этом 1 и 0 нельзя трактовать

как числа и производить над ними арифметические операции. Это

просто короткая форма обозначения понятий ДА и НЕТ, точно так

же, как номер трамвая – это краткое наименование его маршрута:

если друг за другом идут трамваи № 2 и 1, то это не значит, что они

вместе пойдут по маршруту № 3 или 21.

Логические переменные хорошо описывают состояния таких объектов, как реле, тумблеры, кнопки и т. п., т. е. объектов, которые

могут находиться в двух четко различимых состояниях: включено –

выключено. К таким объектам относятся и полупроводниковые логические элементы, на выходе которых может быть лишь один из двух

6

четко различимых уровней напряжения. Чаще более высокий, или

просто ВЫСОКИЙ, уровень принимается за логическую единицу,

а более низкий, или просто НИЗКИЙ, – за логический нуль.

В основе булевой алгебры лежит понятие логической (двоичной,

переключательной, булевой) функции вида Y = f (1, 2, …, n) относительно аргументов 1, 2, …, n, которая, как и ее аргументы, может принимать только два значения – 0 и 1. Аргументы логической функции иногда называют двоичными (булевыми) переменными. Как

частный случай, двоичные переменные могут постоянно сохранять

одно из значений – 0 либо 1. Логическая функция может быть задана словесно, алгебраическим выражением и таблицей истинности,

в левой части которой выписываются все наборы значений двоичных переменных, а в правой – соответствующие им значения функций. Таблица истинности – наиболее наглядная форма задания логических функций.

Упражнение 1. В выражении «я выполню работу, если подготовлюсь к ней и приду на занятие» предполагается, что выполнение работы Y есть функция двух аргументов: подготовки X1 и присутствия

на занятии X2. Требуется описать функцию Y с помощью таблицы

истинности.

Решение. Необходимо перебрать все возможные комбинации аргументов и для каждой комбинации четко определить, исходя из смысла ситуации, значение функции Y:

при X1 = 0,

при X1 = 0,

при X1 = 1,

при X1 = 1,

X2 = 0 → Y = 0;

X2 = 1 → Y = 0;

X2 = 0 → Y = 0;

X2 = 1 → Y = 1.

Результат принято записывать в виде таблицы истинности (табл. 1.1),

которая полностью строго задает логическую функцию.

Таблица 1.1

Аргументы

Функция

X1

X2

Y

0

0

1

1

0

1

0

1

0

0

0

1

7

Позже будет показано, что такую функцию называют «функция И».

Для двух аргументов число комбинаций значений аргументов (набор аргументов) равно 22 = 4, и таблица содержит 4 строки. Если

число аргументов увеличить на единицу, то число строк таблицы

удвоится и станет равным 23 = 8. Действительно, для перебора всех

комбинаций придется перечислить четыре возможные комбинации

X1 и X2 при третьем аргументе, равном 0, а потом те же четыре комбинации 1 и 2 при третьем аргументе, равном 1. В общем случае, для

n аргументов число строк таблицы m = 2n. При n = 4 получим m = 16,

при n = 6 – m = 64. Чтобы не ошибиться при перечислении комбинаций аргументов, нужно приучиться перечислять их единообразно,

в виде последовательностей чисел, представленных в двоичной системе счисления. Например, комбинации трех переменных нужно

перечислять в следующем порядке: 000, 001, 010, 011, 100, 101, 110,

111, итого восемь двоичных чисел от 0 до 7.

Практическим препятствием для повсеместного использования табличной формы задания функций при построении цифровых

устройств является быстрый рост числа строк таблицы. Так, при пяти

входных переменных столбик таблицы займет всю страницу. При большом числе переменных удобнее использовать аналитическую форму представления логических функций в виде алгебраических выражений. Булева функция принимает только два значения (0 или 1),

n

поэтому общее число булевых функций n аргументов равно 2m = 22 .

Для анализа и синтеза цифровых схем широко используются

функции одной и двух переменных. Существуют всего четыре функции одного аргумента. Таблица истинности для логических функций

одного аргумента X1 приведена в табл. 1.2.

Таблица 1.2

X1

0

1

f1(X1)

1

1

f2(X1)

0

0

f3(X1)

0

1

f4(X1)

1

0

Функция f1(X1), принимающая значение 1 при любом значении переменной, является абсолютно истинной («константа единицы»), а функция f2(X1) – абсолютно ложной функцией («константа

нуля»). Функция f3(X1), повторяющая значения логической переменной (f3(X1) ≡ X1), называется «тождественная функция» (эквивалентность, функция равнозначности). Функция f4(X1), принимающая

8

значения, обратные значениям X1, называется «логическое отрицание» (инверсия, функция НЕ) и обозначается чертой над аргументом:

Х 1 (другие обозначения:⎤X1, NOT X1, НЕ X1), т. е. f4(X1) = Х 1.

Устройства, реализующие функции f1(1), f2(1), f3(1), тривиальны

и приведены на рис. 1.1.

f1(X1)

X1

ллог

ог.1 1

X1

f2(X1)

X1

f3(X1)

ллог

ог. 00

Рис. 1.1. Устройства, реализующие функции f1(X1), f2(X1), f3(X1)

Как видно из рисунка, формирование функции f3 требует соединения входа устройства с выходом, формирование f2 требует разрыва между входом и выходом, формирование f1 – подключения выхода к источнику сигнала логической 1. Из всех функций одного

аргумента практический интерес представляет лишь функция НЕ –

f4(X1) = Х 1 .

Полный набор логических функций от двух переменных представлен в табл. 1.3.

Функции одной и двух двоичных переменных называют элементарными логическими функциями. Используя принцип подстановки булевых функций вместо аргументов в другую функцию, можно

построить любую сложную булеву функцию из элементарных.

1.1.2. Законы булевой алгебры

Действия над двоичными переменными производятся по правилам логических операций. Между обычной, привычной для нас алгеброй и алгеброй логики имеются существенные различия в отношении количества и характера операций, а также законов, которым

они подчиняются.

Законы и аксиомы булевой алгебры используют для минимизации сложных логических функций с целью снижения затрат при их

аппаратурной реализации.

9

10

Y = X1· X 2

f5 Переменная X2 Y = X2

f4 Запрет по X1

Y = Х 1 ·X2

f3 Переменная X1 Y = X1

f2 Запрет по Х2

f1

Y=0

Основное

X 1 /\ X2

X2 Δ X1;

X1 /\ X 2

X1 Δ X2;

X1·X2;

X1 /\ X2;

X1 & X2;

Дополнительное

Обозначение функции

Конъюнкция; Y = X1·X2

операция И; логическое произведение; AND

f0 Константа 0

№

Название

функции

X2 но не X1

X1 но не X2

Константа

нуль

X1 и X2

Как читается

И; конъюнктор

Название

логического

элемента

X2

X1

X2

X1

X2

X1

&

&

&

Y = X1 · X 2

Y = X1 · X 2

Y = X1 · X 2

Условное графическое

обозначение элемента

Y

Y

Y

Y

Y

Y

X1

X2

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

0

1

1

0

0

1

0

Таблица

истинности

1

0

1

0

1

0

1

1

Таблица 1.3

11

f10

f9

f8

f7

f6

№

Основное

Инверсия X2;

NOT

Y=X2

Дизъюнкция; Y = X1 \/ X2

операция ИЛИ;

логическая сумма; OR

Функция (стрелка) Пирса; операция ИЛИ-НЕ;

Y = X1↓ X2

функция Вебба;

отрицание дизъюнкции; NOR

Эквивалентность;

равнозначY = X1~ X2

ность;

EQV

⎤X2

X1·X2∨ Х 1 · X 2 ;

X1X2

X1 ~ X2;

X1 ≡ X2;

X 1· X 2

X1∨ X 2 ;

X1 + X2

X1· X 2 + X 1 ·X 2

X1 ∀ X 2;

Дополнительное

Обозначение функции

Исключающее Y=X1 ⊕ X2

ИЛИ; сумма по

модулю 2; функция неравнозначности; XOR

Название

функции

ИЛИ

Не Х2

Х1 эквивалентно Х2;

Х1 равнозначно Х2

НЕ, инвертор

ИСКЛЮЧАЮЩЕЕ ИЛИНЕ

Ни Х1, ни Х2 ИЛИ-НЕ

X1 или X2

Либо X1 либо ИСКЛЮЧАX2; X1 не эк- ЮЩЕЕ ИЛИ

вивалентно

X2; X1 не равно X2

Как читается

Название

логического

элемента

=1

=1

1

1

Y

Y = X 1 ∨X 2

Y = X1 ∨ X 2

X 1· X 2

Y

1

Y= X2

Y = X 1 · X 2 ∨ X 1 ·X 2

X2

X2

X1

X2

X1

X2

X1

Y = X1 · X 2

X2

X1

Условное графическое

обозначение элемента

Y

Y

Y

Y

Y

X1

X2

1

1

1

0

0

0

0

0

0

0

1

1

0

1

1

0

0

1

1

1

0

Таблица

истинности

0

1

0

1

0

1

1

Продолжение табл. 1.3

12

f14

f15 Константа 1

X1 ∨ X 2;

X1 / X2

Функция

(штрих) Шеффера; отрицание конъюнкции; NAND

Y=1

Y = X1⏐ X2

X 1 ∨ X2;

X1 ⊃ X2

Y = X1

⎤ X1

X1 ∨ X 2

X2 ⊃ X1

Дополнительное

Импликация

Y = X1→ X2

от X1 к X2; IMP

Инверсия X1;

NOT

Импликация от

X2 к X1; IMP

Y =X2 → X1

Основное

Обозначение функции

f13

f12

f11

№

Название

функции

Константа 1

Не Х1 или

не Х2; Х1

и Х2 не совместимы

Если Х1

то Х2; Х1

влечет Х2

Не Х1

Если Х2

то Х1; Х2

влечет Х1;

Х2 имплицирует Х1

Как читается

И-НЕ

НЕ, инвертор

Название

логического

элемента

X2

X1

X2

X1

X1

X2

X1

&

1

1

1

Y = X 1 ·X 2

Y = X1 ∨ X 2

Y = X1

Y = X1 ∨ X 2

Условное графическое

обозначение элемента

Y

Y

Y

Y

Y

X1

X2

1

1

1

1

1

0

0

1

1

1

1

0

0

1

1

1

0

0

1

1

0

Таблица

истинности

1

0

1

0

1

1

1

Окончание табл. 1.3

Булева алгебра базируется на нескольких аксиомах, из которых

выводят основные законы для преобразований с двоичными переменными. Каждая аксиома представлена в двух видах, что вытекает

из принципа дуальности, согласно которому операции конъюнкции

(логическое произведение) и дизъюнкции (логическая сумма) допускают взаимную замену, если одновременно поменять логическую

1 на 0, 0 на 1, знак логической суммы «+» на знак логического произведения «·», а знак «·» на знак «+».

Аксиомы операции отрицания: 0 = 1 , 1 = 0 .

Аксиомы операций конъюнкции (а) и дизъюнкции (б):

1a) 0 · 1 = 0;

1б) 1 + 1 = 1;

2a) 1 · 0 = 0 · 1 = 0;

2б) 0 + 1 = 1 + 0 = 1;

3a) 1 · 1 = 1;

3б) 0 + 0 = 0.

Законы булевой алгебры вытекают из аксиом и также имеют две

формы выражения: для конъюнкции и дизъюнкции. Их правильность легко проверяется по таблицам истинности.

1. Переместительный закон:

а) X1 · X2 = X2 · X1;

б) X1 + X2 = X2 + X1.

2. Сочетательный закон:

а) X1 · (X2 · X3) = (X1 · X2) · X3 = X1 · X2 · X3;

б) X1 + (X2 + X3) = (X1 + X2) + X3 = X1 +X2 + X3.

3. Распределительный закон:

а) X1 · (X2 + X3) = X1 · X2 + X1 · X3;

б) X1 + X2 · X3 = (X1 + X2) · (X1 + X3).

4. Закон повторения:

а) X · X = X;

б) X + X = X.

5. Закон обращения: если X1 = X2, то X 1 = X 2 .

6. Закон двойной инверсии: X = X.

7. Закон нулевого множества:

а) X · 0 = 0;

б) X + 0 = X.

8. Закон универсального множества:

а) X · 1 = X;

б) X + 1 = 1.

9. Закон дополнительности:

а) X · X = 0;

10. Закон поглощения:

а) X1 + X1 · X2 = X1;

11. Закон склеивания:

б) X + X = 1.

б) X1 · (X1 + X2) = X1.

а) (X1 + X2) · (X1 + X 2 ) = X1;

б) X1 · X2 + X1 · X 2 = X1.

13

12. Закон исключения:

б) X1 + X 1 ·X2 = X1 + X2.

а) X1 · ( X 1 + X2) = X1 · X2;

13. Закон де Моргана (закон инверсии):

а) X 1·X 2 = X 1 + X 2 , ( X 1·X 2 = X 1 + X 2 );

б) X 1 + X 2 = X 1·X 2 , ( X 1 + X 2 = X 1·X 2 .

1.1.3. Взаимное соответствие булевых функций

и логических схем

Двоичные переменные, входящие в логические уравнения, можно

представить двумя различными электрическими сигналами. Путем преобразования этих сигналов получают другие, тоже двоичные сигналы,

которые соответствуют результатам определенных логических операций. Имея запись булевой функции Y = f(X1, X2, …, Xn), можно по ней

составить развернутую электрическую схему, которая будет преобразовывать логические сигналы X1, X2, …, Xn согласно указанной функции.

Устройства, выполняющие в аппаратуре логические операции,

называются логическими элементами. Логические элементы различаются между собой характером реализуемой функции, числом входов (по числу одновременно действующих переменных), числом выходов и другими признаками. Работа их оценивается только с точки

зрения логики, без учета практического воплощения (технической

базы, способа питания и т. п.).

Входы и выходы логических элементов в зависимости от уровня сигналов, при котором вырабатывается определенное значение

двоичной переменной, подразделяются на прямые и инверсные.

На прямом входе (выходе) двоичная переменная имеет значение логической 1, когда сигнал на этом входе (выходе) имеет значение, принятое за 1. На инверсном входе (выходе) двоичная переменная имеет

значение 1, когда уровень сигнала на этом входе (выходе) соответствует состоянию, принятому за 0.

На логические входы можно подавать постоянные логические

уровни 1 и 0 (константа 1 и константа 0). Входы, равноценные в логическом отношении (которые можно менять местами без ущерба

для выполняемой функции), допускают объединение по закону повторения; при этом они действуют как один вход.

На принципиальных схемах логические элементы цифровой

техники изображают прямоугольником, в верхней части которого

указывают символ функции: например, & для элемента И, 1 для

14

элемента ИЛИ. Входы показывают с левой стороны прямоугольника, выходы – с правой. Инверсные входы и выходы выделяются небольшим кружком у вывода.

Различные логические элементы производятся в виде самостоятельных изделий, а также как составная часть более сложных

устройств. Широко используются логические элементы, совмещающие несколько операций, например И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ,

И-ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ и др.

1.1.4. Полные системы функций алгебры логики

Очевидно, могут быть построены простейшие логические элементы, выполняющие элементарные логические функции двух переменных f0, …, f15 (табл. 1.3). На элементах, осуществляющих элементарные функции, можно выполнить любую сложную логическую

операцию. Такую систему функций называют функционально полной системой или базисом. Наличие 16 различных типов логических

элементов является достаточным условием для синтеза логического устройства любой сложности, но не является необходимым, т. e.

при синтезе можно ограничиться меньшим набором элементарных

функций, взятых из f0, …, f15. Известно, что функционально полными

системами являются, например, базисы: И, ИЛИ, НЕ; И, НЕ; ИЛИ,

НЕ; И-НЕ; ИЛИ-НЕ; И-ИЛИ-НЕ.

Выбор того или иного базиса для синтеза логических устройств

связан с тем, насколько просто, удобно и экономично технически

выполнить логические элементы базиса.

Базисы могут быть избыточными и минимальными. Базис И,

ИЛИ, НЕ, который принято называть основным (булевским), является избыточным, так как возможно исключение из него некоторых

функций. Например, можно исключить функцию И, выразив ее через оставшиеся функции ИЛИ и НЕ. Чтобы показать это, дважды инвертируем конъюнкцию и применим затем закон де Моргана:

X 1 ⋅ X 2 = ( X 1 ⋅ X 2) = X 1 + X 2 .

Отсюда видно, что такая логически тождественная замена технически нерациональна, так как потребовала бы реализации трех операций инверсии и одной операции ИЛИ. Поэтому на практике при

начальной стадии проектирования устройств для построения функциональной схемы используется неминимальный базис, включающий в себя все три функции И, ИЛИ, НЕ.

15

Для реализации цифровых устройств обычно используют базисы

И-НЕ либо ИЛИ-НЕ, элементы которых широко выпускаются промышленностью в интегральном исполнении.

1.1.5. Булевский базис

Содержит набор трех логических функций НЕ, И, ИЛИ, с помощью которых можно выразить любую сложную логическую функцию.

Функция НЕ – это функция одного аргумента (другие названия:

отрицание, инверсия, операция НЕ, NOT). Обычно обозначается

чертой над аргументом:

Y =X ,

где Y – логическая функция, X – аргумент (читается: Y равен не X).

Встречается и другое обозначение – Y = gX. Функция отрицания равна 1, когда ее аргумент равен 0, и наоборот:

ПОГАШЕН = ГОРИТ.

Если утверждение ГОРИТ истинно, то утверждение ПОГАШЕН

будет ложно, и наоборот. Отрицание отрицания аргумента равно самому аргументу: НЕ (НЕ ВКЛЮЧЕН) = ВКЛЮЧЕН, или если Y = X ,

то Y = X = X .

Электронный логический элемент, реализующий функцию НЕ

в виде различных уровней напряжения, называют инвертором (от

англ. inversion – переворачивание). Инвертор на функциональных

схемах изображается, как показано на рис. 1.2: вход – слева, выход –

справа, кружок – символ инверсии.

a

X

0

1

Y

1

0

б

1

X

Вход

Y =X

Выход

в

X

1

Y =X

Выход

Вход

г

E

SA1

HL1

X

Y =X

X

Y =X

X

Y =X

X

Y =X

Рис. 1.2. Инвертор:

а – предпочтительное изображение; б – допустимое изображение;

в – реализация на контакте; г – обозначения в зарубежной литературе

16

Функция И – это функция двух и большего числа аргументов (другие названия: конъюнкция, логическое умножение, совпадение, операция И). Обозначения: Y = X1·X2; Y = X1&X2; Y = X1/\X2 (читается «X1 и X2»). Функция И равна 1 тогда и только тогда, когда все ее

аргументы равны 1. Союз «и» естественного языка, как правило, выражает именно это отношение, например: лифт пойдет, если дверь

закрыта и кнопка нажата, или в аналитической записи: Y = X1 · X2,

где Y – выходной сигнал на двигатель лифта; X1 – сигнал закрытия

двери; X2 – сигнал нажатой кнопки.

Значения функции И для всех комбинаций значений аргументов

X1 и X2 приведены на рис. 1.3, а.

a

X1 X2

Y

0

0

0

0

1

0

1

0

0

1

1

1

б

X1

&

Y

X2

X1

X2

X3

X4

в

&

Y

E

г

SA1

SA2

X1

X2

HL1

Y

X1

X2

X1

X2

X1

X2

Y

Y

Y

Рис. 1.3. Элемент И:

а – предпочтительное изображение (Y = X1 · X2);

б – допустимое изображение (Y = X1 · X2 · X3 · X4);

в – реализация на контактах (Y = X1 · X2);

г – обозначения в зарубежной литературе (Y = X1 · X2)

Элемент, реализующий функцию И, называют «элемент И», или

«конъюктор». Элемент И часто используется для управления потоком информации. При этом на один его вход поступают логические

сигналы, несущие информацию, а на другой – управляющий сигнал:

пропускать – 1, не пропускать – 0. Элемент И, используемый таким

образом, называют вентилем.

Условное обозначение элемента И на схемах показано на рис. 1.3.

Функцию И можно построить от любого числа аргументов (рис. 1.3, б).

В цифровой технике с помощью элемента И реализуются следующие законы булевой алгебры (рис. 1.4).

Функция ИЛИ – это функция двух или большего числа аргументов. Функция ИЛИ равна 1, если хотя бы один из ее аргументов равен 1 (другие названия: дизъюнкция, операция ИЛИ, логическая сумма, OR). Обозначение: Y = X1+X 2 (читается «X1 или X 2»). В русском

языке функция дизъюнкции выражается союзом «или» во фразах

17

типа: «Мы попадем на тот берег, если речка мелкая или мост цел».

Значение функции ИЛИ от двух аргументов и условное обозначение

на схемах элемента, реализующего функцию ИЛИ – дизъюнктора,

показаны на рис. 1.5.

a

б

в

X

&

г

Y = X ·1 = X

Y = X · 0 =0

X

X

&

Y =0

Y = X · X =X

&

Y =X

Y= X · X = 0

X

Y =X

&

1

1

0

Y =0

X

Рис. 1.4. Законы булевой алгебры, реализуемые с помощью элемента И:

а – закон 7 а, б – закон 8 а, в – закон 4 а, г – закон 9 а

a

X1

X2

Y

0

0

0

0

1

1

1

0

1

1

1

1

б

X1

1

г

X1

X2

Y = X1 + X 2 +X3

Y = X1 + X 2

X1

в

X2

X3

Y

f1(X1)

1

SA1

X2

Y

Y

X1

HL1

X1

X2

Y

X1

X2

SA2

E

Y

Y

Рис. 1.5. Элемент ИЛИ: а – предпочтительное изображение (Y = X1 + X2);

б – допустимое изображение (Y = X1 + X2 + X3); в – реализация на контактах (Y = X1+X2); г – обозначения в зарубежной литературе (Y = X1+X2)

В цифровой технике с помощью элемента ИЛИ реализуются следующие законы булевой алгебры (рис. 1.6).

a

б

Y=X+0=X

X

0

1

в

г

Y=X+1=1

X

Y =X

1

Y = X + X =X

X

Y =1

1

Y =X

X

Y=X+X=1

1

1

Y =1

1

X

Рис. 1.6. Законы булевой алгебры, реализуемые с помощью элемента ИЛИ:

а – закон 7 б, б – закон 8 б, в – закон 4 б, г – закон 9 б

18

1.1.6. Базис И9НЕ

Функция И-НЕ – это функция двух и более аргументов (другие

названия: штрих Шеффера, функция Шеффера, отрицание конъюкции, NAND). Значения функции приведены на рис. 1.7, а. Легко заметить, что это инверсия функции И, т. е. отрицание конъюнкции

Y = X 1 ⋅ X 2 : любой 0 на входе дает 1 на выходе, все единицы на входе дают 0 на выходе. В качестве основного знака этой функции используется символ «|» (штрих Шеффера). Условное обозначение функции

Шеффера Y = X1|X2 читают так: неверно, что функция Y есть X1 и X2

(не X1 или не X2). Обозначение элемента на схемах показано на рис. 1.7.

a

X1 X2

0

0

0

1

1

0

1

1

Y

1

1

1

0

б

X1

&

в

X1

X2

X3

X4

Y

X2

&

г

SA1

SA 2

X1

X2

X1

Y

X2

Y

Y

HL1

X1

X2

E

Y

Рис. 1.7. Элемент И-НЕ:

а – предпочтительное изображение; б – допустимое изображение;

в – реализация на контактах; г – обозначения в зарубежной литературе

Используя только элементы И-НЕ, можно получить элементы

НЕ, И, ИЛИ, как показано на рис. 1.8. Правомерность такого представления можно доказать с помощью таблиц истинности.

а

б

в

X1

X 1· X 2

X

&

X1

Y =X

&

&

& Y1 = X 1

& Y = X1 +X 2

Y = X1 · X 2

X2

X2

&

Y2 = X 2

г

X1

&

X 1· X 2

X1

&

X2

& Y1= X 1· X 2 = X 1+X 2

&

X2

Рис. 1.8. Возможности элемента И-НЕ:

а – НЕ; б – И; в – ИЛИ; г – ИЛИ-НЕ

19

Упражнение 2. Доказать, что схема на рис. 1.8, в выполняет функцию ИЛИ.

Решение. Типичная ошибка начинающих: при анализе схем пытаются все промежуточные результаты держать в уме, что приводит

к ошибкам. Для их исключения рекомендуется записывать промежуточные результаты в табличной форме (табл. 1.4).

Таблица 1.4

1

X1

X2

0

0

1

1

0

1

0

1

2

Элемент 1

3

Элемент 2

4

5

Элемент 3

6

Y1 = X 1

Y2 = X 2

Y1 · Y2

Y 1 ⋅Y 2 = X 1 ⋅ X 2

ИЛИ

Y = X1+X2

1

1

0

0

1

0

1

0

1

0

0

0

0

1

1

1

0

1

1

1

В таблице для каждого элемента схемы выделены столбцы, в которых записываются значения выхода элемента для всех комбинаций

входных сигналов. Для элементов, выполняющих сложные или просто непривычные функции, можно выделить два или больше столбцов, как это сделано для элемента 3. Полученный итоговый результат (столбец 5) сравнивается с ожидаемым результатом, в данном

случае с таблицей значений функции ИЛИ, для удобства записанных в столбец 6.

Способность функции И-НЕ выражать только через себя все

функции булева базиса доказывает, что эта функция обладает логической полнотой. С помощью одной лишь функции И-НЕ можно

построить любую сколь угодно сложную логическую функцию. Вторым ценным свойством функции оказалось то, что именно ее удалось эффективно реализовать средствами интегральной технологии.

Поэтому элементы И-НЕ в виде отдельных микросхем наиболее распространены в цифровой технике. На их основе создано также множество схем средней и большой степени интеграции. Аналога в русском языке функция не имеет, поэтому мышление в базисе И-НЕ

непривычно и требует тренировки.

1.1.7. Базис ИЛИ9НЕ

Функция ИЛИ-НЕ – это функция двух и более аргументов (другие названия: функция Вебба (Пирса), стрелка Пирса, операция

20

ИЛИ-НЕ, отрицание дизъюнкции, NOR). Значения функции представлены на рис. 1.9.

a

X1

X2

б

в

г

X1

Y

0

0

1

0

1

0

1

0

0

1

1

0

X1 1

X1

X2

X3

X4

Y

X2

1

HL1

SA1

SA2

E Y

X1

X2

Y

X2

Y

X1

X2

Y

Рис. 1.9. Элемент ИЛИ-НЕ: а – двухвходовой ( Y = X 1 + X 2 = X 1 ↓ X 2 );

б – многоходовой ( Y = X 1 + X 2 + X 3 + X 4 ); в – реализация

на контактах; г – обозначения в зарубежной литературе

Функция истинна только тогда, когда значения ее переменных

ложны. В качестве основного знака этой функции в булевой алгебре используется символ «↓» (стрелка Пирса). Условное обозначение функции Y = X1↓X2 читают так: функция Y есть ни X1, ни X2.

Данная функция, являясь инверсией функции ИЛИ, может быть

приведена к виду Y = X 1 + X 2 , т. е. результат операции Пирса есть

отрицание дизъюнкции переменных. Отсюда еще одно название –

операция ИЛИ-НЕ. Русский язык немного умеет оперировать с этой

функцией, называя ее «ни – ни». Функция ИЛИ-НЕ, как и функция И-НЕ, обладает полнотой и тоже удобна для интегрального исполнения. Это вторая по распространенности после И-НЕ функция

в цифровой технике.

Используя только элементы ИЛИ-НЕ, можно получить элементы НЕ, И, ИЛИ (рис. 1.10).

а

б

в

X1

X

1

1

X1

Y =X

1

Y = X1 · X2

X1 1

X 1+ X 2

1

X2

X2 1

X2

Рис. 1.10. Возможности элемента ИЛИ-НЕ:

а – НЕ; б – И; в – ИЛИ

21

Y = X1 + X2

Упражнение 3. Доказать правильность схем на рис. 1.10, последовательно заполняя таблицу по примеру табл. 1.4.

1.1.8. Сумма по модулю 2

Функцию «сумма по модулю 2» (М2) в случае двух аргументов

называют также функцией неравнозначности, ИСКЛЮЧАЮЩЕЕ

ИЛИ, OR. Обозначение в формулах: Y = X1⊕X2 (знак ⊕ – псевдоплюс); читается: либо X1, либо X2 (X1 не равно X2). Таблица истинности функции и обозначения на схемах приведены на рис. 1.11.

а

б

X1

X2

Y

0

0

0

0

1

1

1

0

1

1

1

0

X1

в

=1

X1

Y = X1 ⊕ X 2

Y

X2

X2

Рис. 1.11. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ: а – таблица истинности;

б, в – условные обозначения в отечественной и зарубежной литературе

Название функции связано с тем, что X1⊕X2 есть арифметическая сумма двоичных чисел X1 и X2 в пределах одного разряда: 02 +

+ 02 = 02; 02 + 12 = 12; 12 + + 02 = 12; 12 + 12 = 102. В последнем случае

возникает единица переноса в старший разряд, а в разряде самих слагаемых получается нуль. В связи с этим элемент широко применяется при построении сумматоров. Как видно из таблицы истинности,

элемент может служить также для сравнения двоичных разрядов (выявления их неравенства).

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ выпускается промышленностью в виде интегральных схем, но может быть также реализован на

элементах И-НЕ, И, НЕ, ИЛИ (рис. 1.12).

а

б

X1

&

& Y

&

X2

&

X1

X2

&

в

&

X1

1

X2

1

& Y

&

&

&

1 Y

&

Рис. 1.12. Варианты реализаций элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

(Y = X1⊕X2)

22

в различных базисах: а) Y = X 1 ⋅ X 1 ⋅ X 2 ⋅ X 2 ⋅ X 1 ⋅ X 2 ;

б) Y = X 1 ⋅ X 2 ⋅ X 1 ⋅ X 2 ;

в) Y = X 1 ⋅ X 2 + X 1 ⋅ X 2

Упражнение 4. Доказать правильность схем на рис. 1.12, последовательно заполняя таблицу по примеру табл. 1.4.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ обладает интересной особенностью. Если на одном из его входов, например X1, поддерживать

уровень логической 1, то Y = 0·X2 + 1· X 2 = X 2 и элемент работает

как инвертор X2. При логическом 0 на одном входе Y = 1·X2 + 0· X 2 = X2

и элемент работает как повторитель сигнала X2.

Иногда требуется многовходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

Такой элемент можно собрать по схемам, приведенным на рис. 1.13.

а

б

в

X1

=1

X2

X1

X2

X3

X3

=1

=1

X2

=1

X5

=1

=1

Y

X7

Y

Y

=1

=1

=1

X8

X8

Y = X 1 ⊕X 2 ⊕ X 3

=1

X6

=1

X3

=1

X4

X4

X1

=1

Y =X 1⊕ X 2⊕ X 3 ⊕ X 4⊕ X 5 ⊕X 6 ⊕ X 7 ⊕X 8

Y =X 1 ⊕X 2 ⊕X 3 ⊕X 4 ⊕ X 5 ⊕ X 6 ⊕ X 7 ⊕X 8

Рис. 1.13. Варианты многовходовых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ:

а, б – линейная схема; в – пирамидальная схема

Структура, показанная на рис. 1.13, в, является основой микросхем, предназначенных для проверки на четность многоразрядных

цифровых слов.

1.1.9. Исключающее ИЛИ9НЕ

Функция М2 обладает интересным свойством: при инвертировании одного из аргументов вся функция инвертируется, т.е.

X1⊕ X 2 = X1⊕ X 2 = X1⊕ X 2 .

Инверсия суммы по модулю 2 (другое название – ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ) имеет и собственный смысл: это функция равнознач23

ности (эквивалентности). Она равна единице, если X1 = X2. Обозначение

элемента равнозначности и таблица истинности показаны на рис. 1.14.

а

б

X1

X2

Y

0

0

1

0

1

0

1

0

0

1

1

1

в

X1

=1

X1

Y = X1 ⊕ X2

Y

X2

X2

Рис. 1.14. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ:

а – таблица истинности; б, в – условное обозначение в отечественной

и зарубежной литературе

Промышленностью не выпускаются элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, поэтому их собирают из отдельных логических элементов. На рис. 1.15 даны примеры схем таких устройств.

а

в

б

1

X1

X1

&

=1

Y

X2

&

X2

&

1

1

X2

X1

Y

Y

&

1

&

&

г

д

X1

&

X1

&

X2

&

1

Y

&

&

&

Y

&

&

X2

е

ж

X1

&

X1

X2

1

1

Y

1

&

X2

1

Y

&

&

1

1

Рис. 1.15. Варианты реализации элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

(Y = X 1 ⊕ X 2 )

24

Упражнение 5. Доказать правильность схем на рис. 1.15, последовательно заполняя таблицу по примеру табл. 1.4.

1.2. Лабораторная работа № 1

Исследование логических элементов

Цель работы: изучение принципа действия логических элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и экспериментальное подтверждение их

таблиц истинности.

1.2.1. Задания для самостоятельной подготовки

1. Изучить основы алгебры логики. Выполнить упражнения из теоретической части.

2. Выписать основные логические функции одной и двух переменных и основные законы алгебры логики.

3. Зарисовать условные графические обозначения изучаемых логических элементов, их таблицы истинности.

4. Продумать и зарисовать схемотехническую реализацию всех логических функций (НЕ, И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИЛИНЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ) на элементах И-НЕ.

5. Письменно ответить на контрольные вопросы.

1.2.2. Методические рекомендации

Работа выполняется с использованием среды моделирования

Electronics WorkBench (EWB 5.12). Окно программы EWB имеет вид

(рис. 1.16):

Рис. 1.16. Окно программы EWB

25

Принципы работы и возможности программы EWB рассмотрим

на примере «ручного» исследования логического элемента (ЛЭ) И.

Для этого соберем схему по рис. 1.17:

1 k Ohm /5 V

+v

[A]

[B]

Рис. 1.17. Моделирование логического элемента И

Элементы, необходимые для сборки схемы, можно найти на панели инструментов. Из каталога Sources выбираем заземление (рис. 1.18).

Рис. 1.18. Каталог Sources

Из каталога Basic выбираем соединительный контакт 1, ключ 2

и источник напряжения 3 (рис. 1.19).

Рис. 1.19. Каталог Basic

26

На схеме над ключом в квадратных скобках указывается клавиша

клавиатуры, переключающая этот ключ (по умолчанию – пробел).

Чтобы изменить это значение, нужно двойным щелчком мыши по

элементу вызвать окно свойств, выбрать закладку Value и изменить

значение Key. Параметры источника питания (1 kOhm/5 V) задаются

по умолчанию. Если нужны другие параметры, то по аналогии с ключом выставляют соответствующие значения. Чтобы развернуть элемент в нужном направлении, нужно щелчком правой кнопки мыши

по элементу вызвать контекстное меню и выбрать Rotate либо Flip

Vertical или Flip Horizontal. Логические элементы находятся в каталоге

Logic Gates. Для данной схемы требуется элемент И (рис. 1.20).

Рис. 1.20. Каталог Logic Gates

Светодиоды для визуального определения уровня сигнала (горящий светодиод соответствует логической 1) находятся в каталоге

Indicators (рис. 1.21).

Рис. 1.21. Каталог Indicators

После сборки схемы включаем ее с помощью управляющей кнопки (см. рис. 1.16). На рис. 1.17 ключи разомкнуты (светодиоды не горят), на ЛЭ подаются сигналы низкого уровня, на выходе получаем

сигнал низкого уровня. Изменяя состояние ключей, составляем таблицу истинности данного ЛЭ.

27

Для автоматического снятия таблицы истинности соберем схему по рис. 1.22.

Рис. 1.22. Использование логического преобразователя

Логический преобразователь находится в каталоге Instruments

(рис. 1.23).

Рис. 1.23. Каталог Instruments

Двойной щелчок мыши по логическому преобразователю открывает его рабочее окно (рис. 1.24).

Рис. 1.24. Рабочее окно логического преобразователя

28

При нажатии кнопки 1 генерируется таблица истинности. При

нажатии кнопки 2 в окне 3 выводится соответствующее ей логическое выражение.

1.2.3. Порядок выполнения работы

Используя ручной способ и логический преобразователь, исследовать работу изучаемых логических элементов по приведенной выше

методике. По результатам исследования составить их таблицы истинности.

1.2.4. Содержание отчета

1. Название и цель работы.

2. Краткие теоретические сведения.

3. Выполненные упражнения из теоретической части.

4. Схемы экспериментов и снятые таблицы истинности.

5. Ответы на контрольные вопросы.

1.3. Контрольные вопросы

1.

– это условное обозначение элемента:

а) И

б) ИЛИ

в) НЕ

г) И-НЕ

2. Булево выражение для логического элемента И с двумя входами имеет вид:

а) X1 + X2

б) X1 · X2

в) X 1 ⋅ X 2

г) X 1 + X 2

3. Если на оба входа схемы И поданы сигналы высокого уровня,

то на выходе появится сигнал ... уровня:

а) низкого

б) высокого

29

4.

– это условное обозначение элемента:

а) И

б) ИЛИ

в) НЕ

г) И-НЕ

5. Булево выражение для логического элемента ИЛИ с двумя входами имеет вид:

а) X1 + X2

б) X1·X2

в) X 1 ⋅ X 2

г) X 1 + X 2

6. Если на оба входа схемы ИЛИ поданы сигналы низкого уровня, то на выходе появится сигнал ... уровня:

а) низкого

б) высокого

7.

– это условное обозначение элемента:

а) И

б) ИЛИ

в) НЕ

г) И-НЕ

8. Булево выражение для элемента И-НЕ с двумя входами имеет вид:

а) X1 + X2

б) X1 · X2

в) X 1 ⋅ X 2

г) X 1 + X 2

9. Если на оба входа схемы И-НЕ поданы сигналы высокого уровня, то на выходе появится сигнал ... уровня:

а) низкого

б) высокого

10. Логический элемент И-НЕ может выполнять логическую

функцию инвертирования, если его входы:

а) соединены

б) разъединены

11. Для реализации логической функции ИЛИ с двумя входами необходимое число логических элементов И-НЕ с двумя входами равно

30

а) 2

б) 3

в) 4

г) 8

12. Булево выражение для логического элемента И-НЕ с тремя

входами имеет вид:

а) X 1 ⋅ X 2 ⋅ X 3

б) X 1 ⋅ X 2 ⋅ X 3

в) X 1 ⋅ X 2 ⋅ X 3

г) X 1 ⋅ X 2 ⋅ X 3

13. Таблица истинности для логического элемента И-НЕ с тремя

входами должна содержать ... строк.

а) 3

б) 4

в) 8

г) 16

14.

– это условное обозначение элемента:

а) ИЛИ

б) ИЛИ-НЕ

в) ИСКЛЮЧАЮЩЕЕ ИЛИ

г) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

15. Булево выражение для логического элемента ИЛИ-НЕ с двумя входами имеет вид:

а) X1 + X2

б) X1 · X2

в) X 1 ⋅ X 2

г) X 1 + X 2

16. Если на оба входа схемы ИЛИ-НЕ поданы сигналы низкого

уровня, то на выходе появится сигнал ... уровня.

а) низкого

б) высокого

17.

– это условное обозначение элемента:

а) ИЛИ

б) ИЛИ-НЕ

в) ИСКЛЮЧАЮЩЕЕ ИЛИ

г) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

31

18. Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ иногда называют элементом:

а) сумма по модулю

б) сумма по модулю 2

в) сумма по модулю 3

г) сумма по модулю 4

19. Булево выражение для логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с двумя входами имеет вид:

а) X 1 ⋅ X 2 + X 1 ⋅ X 2

б) X 1 ⋅ X 2 + X 1 ⋅ X 2

в) X 1 ⋅ X 2 + X 1 ⋅ X 2

г) X 1 ⋅ X 2 + X 1 ⋅ X 2

20. Если на оба входа схемы ИСКЛЮЧАЮЩЕЕ ИЛИ поданы сигналы высокого уровня, то на выходе появится сигнал ... уровня.

а) низкого

б) высокого

21.

– это условное обозначение элемента:

а) ИЛИ

б) ИЛИ-НЕ

в) ИСКЛЮЧАЮЩЕЕ ИЛИ

г) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

22. Булево выражение для логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ с двумя входами имеет вид:

а) X 1 ⋅ X 2 + X 1 ⋅ X 2

б) X 1 ⋅ X 2 + X 1 ⋅ X 2

в) X 1 ⋅ X 2 + X 1 ⋅ X 2

г) X 1 ⋅ X 2 + X 1 ⋅ X 2

23. Если на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ присутствует сигнал высокого уровня, то на входы элемента поданы сигналы ... уровня.

а) один низкого, другой высокого

б) только низкого

в) только высокого

г) либо низкого, либо высокого

32

24.

– эта схема реализует функцию:

а) И

б) ИЛИ

в) ИЛИ-НЕ

г) И-НЕ

25.

– эта схема реализует функцию:

а) И

б) ИЛИ

в) ИЛИ-НЕ

г) И-НЕ

26.

– эта схема реализует функцию:

а) И

б) ИЛИ

в) ИЛИ-НЕ

г) И-НЕ

27.

– эта схема верна для следующего булева

выражения:

а) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

б) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

в) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

г) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

33

X1 X2

0

0

28. 0

1

1

0

1

1

Y

1

1

1

0

– эта таблица истинности верна для следующего

булева выражения:

а) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

б) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

в) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

г) X 1 ⋅ X 2 + X 1 ⋅ X 2 = Y

34

2. СХЕМЫ КОНТРОЛЯ ЧЕТНОСТИ,

ЦИФРОВЫЕ КОМПАРАТОРЫ, СУММАТОРЫ

2.1. Основные теоретические сведения

2.1.1. Контроль четности

Для передачи информации в цифровых системах используют цифровые сигналы. Хотя они по сравнению с аналоговыми менее подвержены действию помех, все же возможно появление ошибок. Если,

например, передается код 10012 = 910 и вследствие помех произойдет сбой во втором разряде слева, на приемный канал поступит код

11012 = 1310. В общем случае без специальной проверки факта ошибки не установить. В частном случае, если числовая информация закодирована в двоично-десятичном коде, нарушение легко обнаружить, поскольку число 1101 противоречит двоично-десятичному

коду. Наличие шести избыточных состояний в четырехразрядном

двоично-десятичном коде (1010, 1011, 1100, 1101, 1110, 1111) позволяет выявить некоторые, но не все возможные ошибки. Например,

указанный код не выявит ошибку, если вместо переданного кода

10012 на приемник информации поступит код 10002, так как число

1000 является допустимым в двоично-десятичном коде.

Известен простой и эффективный способ обнаружения ошибок,

основанный на допущении, что в каждый момент времени ошибка

может возникать только в одном разряде и проявляется она в лишней единице или в потере единицы. В обоих случаях число единиц

в слове изменяется на одну. Таким образом, если передаваемое слово

содержит четное число единиц по всем разрядам, а на конце линии

передачи это число окажется нечетным, значит, появилась ошибка.

Реализация этого метода обнаружения ошибок осуществляется

с помощью специальных устройств (схем контроля четности), кото35

рые выпускаются в микросхемном исполнении. Принцип действия

подобных устройств поясняет рис. 2.1.

1 разряд

2

Передатчик

дискретной

информации

Приемник

информации

n +1

Разрешение приема

(паритеты совпадают)

X1

X2

V

X1

Р

Конт.

бит

Xn

Р

Формирователь

контрольного бита

X2

Xn

Р

Р

Конт. К сигнализатору

бит Х ошибок (паритеты

не совпадают)

Контрольная схема

Рис. 2.1. Передача информации с контролем четности

На основе информации на выходе передатчика схема сравнения

(формирователь контрольного бита) формирует дополнительный бит

Р (1 или 0), так называемый паритетный или контрольный бит, который добавляется к выходной информации в качестве (n + 1) разряда.

Назначение контрольного бита – доводить число единиц в каждом передаваемом кодовом слове до четного или нечетного числа

в зависимости от выбранного вида паритета. При передаче информации, включая запись в память и считывание, контрольный бит передается вместе с информационным словом.

На приемном конце с помощью контрольной схемы происходит

проверка паритета (от англ. parity – соответствие, аналогия) поступивших сигналов. Если паритет соответствует выбранному, прием

информации разрешается. Если на линии имеет место искажение передаваемой информации (например, за счет обрыва одной из жил),

происходит включение сигнализатора ошибок.

Паритет может быть четным или нечетным. В случае нечетного

паритета контрольный бит формируется таким образом, чтобы сумма

всех единиц в передаваемом слове, включая контрольный бит, была

36

нечетной. Для четного, естественно, наоборот. Например, в коде 0111

число единиц нечетно. Поэтому для нечетного паритета дополнительный (контрольный) бит должен быть нулем, а для четного – соответственно единицей. На практике нечетный паритет используется чаще. Это связано со следующим обстоятельством. При контроле

по четности правильный исходный код «все нули» будет иметь контрольный бит, равный 0. В линию отправится посылка из сплошных

нулей, и на приемном конце она будет неотличима от весьма опасной

неисправности – полного пропадания связи. Напротив, контроль нечетности позволяет фиксировать полное пропадание информации,

поскольку слово из одних нулей (включая контрольный бит) противоречит нечетному паритету.

В качестве примера в табл. 2.1 приведены значения контрольного

бита при четном и нечетном паритете чисел от 0 до 9.

Таблица 2.1

Число

Значение контрольного бита

Десятичное

Двоичное

Нечетный

паритет

Четный

паритет

0

0000

1

0

1

0001

0

1

2

0010

0

1

3

0011

1

0

4

0100

0

1

5

0101

1

0

6

0110

1

0

7

0111

0

1

8

1000

0

1

9

1001

1

0

Простейший контроль по четности или нечетности не обнаруживает ошибок, возникающих в двух разрядах одновременно, однако на

практике вероятность их возникновения значительно меньше одинарных. В ответственных случаях для выявления и коррекции ошибок применяют специальные методы кодирования.

В случае проверки на четность двухразрядного двоичного числа схема формирования контрольного бита является простейшей –

она состоит из одного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Действи37

тельно, если сравнить таблицы истинности (рис. 2.2, а, б) элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ и схемы проверки на четность (число единиц в любой горизонтальной строке таблицы должно быть четным),

то можно убедиться в их идентичности. Следовательно, двухвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ реализует схему проверки на

четность двухразрядного двоичного числа. Выход схемы используется

в качестве контрольного бита.

б

а

2-разрядное число

X X1}

X

{X2

X1

=1

X1 X2

Y

X2

0

0

0

1

1

0

1

1

X1 X2

Y

0

X1

1

X2

1

Y

Схема проверок

на четность

0

Y

0

0

0

0

1

1

1

0

1

1

1

0

Рис. 2.2. Таблицы истинности:

а – элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; б – схема проверки

на четность двухразрядного числа

Многоразрядные формирователи контрольного бита также строят на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, исполняющих роль сумматоров по модулю 2 (т. е. сумматоров, сигналом переноса которых пренебрегают). На рис. 2.3 показано четырехразрядное

устройство проверки четности (нечетности).

X

X 01

X 21

X 32

X 43

Информационные

шины

Y

=1

X 2 ⊕X 3

=1

Y 1= X 0 ⊕ X 1⊕ X 2 ⊕ X 3

=1

X0 ⊕ X1

=1

Y 1= X 0⊕ X 1⊕ X 2⊕ X 3 ⊕ V

v

Рис. 2.3. Формирователь контрольного бита

для четырехразрядного слова

38

Структура схемы многоступенчатая (пирамидальная). В первой

ступени (ярусе) попарно суммируются все биты слова. Выходные

сигналы первого яруса X0 ⊕ Х1 и X2 ⊕ Х3 служат входными для второго – и так последовательно до окончательного определения четности (нечетности) суммы единиц всего слова.

Видно, что первые 2 яруса данной схемы образуют четырехвходовой сумматор по модулю 2. Полученный на выходе сумматора по

модулю 2 результат Y1 на последнем этапе сравнивается с управляющим сигналом V, задающим вид используемого паритета. Если принят четный паритет, т. е. число единиц в слове, включая контрольный

бит, должно быть четным, то контрольный бит Y должен быть равен

сумме по модулю 2 всех информационных разрядов слова Х0 – Х3.

Для нечетного паритета контрольный бит Y является инверсией указанной суммы (табл. 2.2).

Таблица 2.2

Входы

Выход Y

Х0

Х1

Х2

Х3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

При V = 0

четный паритет

0

1

1

0

1

0

0

1

1

0

0

1

0

1

1

0

При V = 1

нечетный паритет

1

0

0

1

0

1

1

0

0

1

1

0

1

0

0

1

Потенциал на входе V определяет вид используемого паритета: при

V = 0 паритет четный, при V = 1 – нечетный.

Устройства для проверки четности двоичных слов выпускаются

в виде самостоятельных изделий в нескольких сериях микросхем.

Они находят применение также в качестве сумматоров по модулю 2.

39

Примерами могут служить отечественные микросхемы К155ИП2

(ТТЛ) и 564СА1 (КМДП) (рис. 2.4).

б

а

8

D0

9

D1

10

D2

11

12 D3

D4

13 D5

1

D6

2 D7

5

6

3

4

7

6

5

4

3

2

1

15

14

13

12

11

M2

Y1

Y2

V1

10

V2

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

M2

9

Y

V

Рис. 2.4. Условное обозначение микросхем контроля

четности и нечетности:

а – К155ИП2; б – 564СА1

Микросхема К155ИП2 имеет восемь информационных входов

(D0 – D7), два управляющих входа V1, V2 для задания вида паритета

и два выхода Y1, Y2. Наличие двух управляющих входов и двух выходов расширяет функциональные возможности микросхемы. Например, сигналами на входах V1 и V2 можно управлять полярностью выходных сигналов.

По принципу действия микросхема 564СА1 сходна с показанной

на рис. 2.3 схемой и отличается только тем, что содержит больше элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» и входов. Эта микросхема определяет паритет двоичного числа длиной до 12 разрядов. Она имеет 12 информационных входов (D0 – D11), один управляющий вход V и один

выход Y. Сигнал на управляющем входе V задает режим работы схемы: когда V = 0, обеспечивается четный паритет, т.е. при четном числе единиц на информационных входах Y = 0, а при нечетном – Y = 1.

При V = 1 имеет место нечетный паритет, обратный рассмотренному. Когда число разрядов в слове превышает двенадцать, можно использовать несколько микросхем, соединяя выход Y предыдущей схемы с входом V последующей.

40

2.1.2. Устройства сравнения

На основе функции равнозначности (ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ)

реализуют одну из распространенных в цифровых системах логических операций – поразрядное сравнение двоичных чисел. Устройства, выполняющие эту операцию, называют цифровыми компараторами. Результат сравнения может использоваться, например для

определения дальнейшего хода решения задачи ЭВМ. Схемы сравнения на равенство чисел используются также при поиске устройств

(принтера, дисплея, накопителя на жестком диске и т. п.) по их номеру, опознании заданных слов, для отметки времени в часах и т. д.

Устройства сравнения могут быть построены также из отдельных логических элементов. Рассмотрим пример синтеза простейшего цифрового компаратора для сравнения двух одноразрядных

чисел Z0 и X0.

Представим схему сравнения в виде «черного ящика» с входными переменными X0 и Z0. Выходом является логическая функция Y,

описывающая устройство. Составим таблицу истинности, которая

соответствует равенству двух одноразрядных чисел X0 и Z0:

Х0

Z0

Схема

сравнения

X0

0

0

1

1

Y

Z0

0

1

0

1

Y

1

0

0

1

Из таблицы видно, что два одноразрядных двоичных числа равны, когда они оба равны нулю или оба равны единице. Для составления логической функции устройства воспользуемся следующим

правилом: для каждой строки таблицы истинности, в которой значение выходного сигнала Y равно 1, составляется логическое произведение входных сигналов и после этого – логическая сумма всех

произведений. Если значение входного сигнала равно 0, то в произведении участвует отрицание входного сигнала. В результате получим логическую функцию

Y = X 0⋅Z 0 + X 0⋅Z 0

(произведения X 0 ⋅ Z 0 и X 0 ⋅ Z 0 , как видно из таблицы, равны нулю

и поэтому не учтены).

41

Автомат, реализующий эту функцию, должен выполнить ряд логических операций согласно полученной формуле. В общем случае порядок выполнения операций задается правилами проведения логических и математических вычислений с учетом старшинства операций

и скобок. В приведенной формуле последнее действие, после которого появится сигнал Y = 1, – логическое сложение. Следовательно,

на выходе устройства должен стоять элемент ИЛИ (рис. 2.5, а).

а

б

X0

Z0

X 0 · Z0

X 0 · Z0

1

X0

X0

Z0

Z0

1

Y

Y= X 0 ·Z 0 +X 0 ·Z 0

в

г

X0

1

&

X 0· Z0

Y = X 0 ·Z 0 +X 0 ·Z 0

&

Z0

1

X0

Z0

Z0

&

X0

Z0

Z0

Y

X0

Z0

X0

& X 0· Z0

1

Y

1

&

Y

&

1

1

Y = X 0 ·Z 0 +X 0 ·Z 0

Y = X 0 ·Z0 + X 0 ·Z0

Рис. 2.5. Этапы синтеза схемы сравнения двух одноразрядных чисел:

а – реализация логического сложения; б – реализация логических

произведений; в – реализация инверсий сигналов X0 и Z0;

г – окончательная схема

В этом элементе происходит сложение двух составных сигналов

X 0 ⋅ Z 0 и Х0 · Z0, но таких сигналов у нас нет, их надо предваритель-

но получить из исходных, используя логические элементы. Как это

сделать?

Нетрудно заметить, что входные сигналы для схемы ИЛИ на рис. 2.5, а

представляют собой логические произведения двух сигналов X0

и Z0, X 0 и Z 0 . Эти сигналы можно получить, используя устройства, осуществляющие логическое умножение – элементы И.

На рис. 2.5, б показан следующий шаг проектирования схемы логического автомата. Далее необходимо получить инверсию сигналов Х0

42

и Z0, для чего используются элементы НЕ (рис. 2.5, в). Окончательная схема, полученная после соединения одноименных входов, показана на рис. 2.5, г.

По такой методике может быть построен цифровой автомат для

сравнения двоичных чисел любой разрядности. Синтезированная

схема (рис. 2.5, г) содержит целый ряд отдельных логических элементов и при практической реализации получится весьма громоздкой.

Для снижения аппаратных затрат при построении схем сравнения

в реальных цифровых устройствах поступают иначе – используют

свойства логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, который

выпускается в виде микросхем.

Действительно, если сравнить таблицу истинности синтезированной схемы сравнения с таблицей истинности элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, то можно заметить, что они одинаковы, т. е.

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ может быть использован для

сравнения двух одноразрядных чисел. В свою очередь, как известно,

для построения элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ на практике

используется последовательное включение элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и НЕ. В результате получается компактная и практичная

схема сравнения одноразрядных чисел, показанная на рис. 2.6.

Y= X 0 ·Z0 +X 0 ·Z0

X0

=1

&

Y= X 0·Z 0 +X 0 Z 0

Z0

Рис. 2.6. Практическая схема сравнения двух одноразрядных чисел

на стандартных логических элементах

Покажем тождественность данной схемы и синтезированной ранее. Для этого, используя за-коны алгебры логики, преобразуем логическую функцию Y:

Y = X 0 ⋅ Z 0 + X 0 ⋅ Z 0 = X 0 ⋅ Z 0 ⋅ X 0 ⋅ Z 0 = ( X 0 + Z 0) ⋅ ( X 0 + Z 0) =

= ( X 0 + Z 0) ⋅ ( X 0 + Z 0) = X 0 ⋅ X 0 + X 0 ⋅ Z 0 + X 0 ⋅ Z 0 + Z 0 ⋅ Z 0 =

= X 0 ⋅ Z 0 + X 0 ⋅ Z 0.

Отсюда следует, что схемы на рис. 2.5, г и 2.6 логически тождественны, однако последняя значительно проще в реализации.

43

Используя одноразрядные схемы сравнения, можно построить

устройства сравнения много-разрядных чисел. Очевидно, что многоразрядные двоичные числа равны друг другу, если равны одноименные разряды. Схемы побайтного сравнения многоразрядных чисел также содержат элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. Структура

цифрового компаратора, выполняющего сравнение двух n-разрядных

двоичных чисел X = {Xn,…, X2, X1, X0} и Z = {Zn,…, Z2, Z1, Z0}, показана на рис. 2.7. Там же приведено условное графическое обозначение схемы сравнения.

а

б

X0

=1

X0

X1

Z0

X1

=1

Z1

1

X

Xnn

Y

X =Z

Z0

Z1

X

Xnn

ZZnn

=1

Zn

n

Рис. 2.7. Цифровой n-разрядный компаратор:

а – структура; б – условное графическое обозначение

На выходе Y будет сигнал логической единицы при полном совпадении всех соответствующих разрядов чисел X и Z (X0 = Z0, X1 = Z1,

…, Xn = Zn). Число входов элемента ИЛИ-НЕ на рис. 2.7, а равно

числу разрядов чисел.

В качестве примера на рис. 2.8 показаны структура устройства

сравнения двух двухразрядных чисел и его таблица истинности.

Четырехразрядные цифровые компараторы выпускаются отечественной промышленностью в виде самостоятельных микросхем (например, К555СП1, К564ИП2). Они помимо определения равенства

или неравенства двух четырехразрядных чисел допускают наращивание (без дополнительных логических элементов) с целью увеличения разрядности.

44

а

б

X0

=1

Z0

1

X1

Y

=1

Z1

число Z = {Z1, Z0}

число X = {X1, X0}

X1

Z1

X0

Z0

Y

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

0

1

1

1

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

1

0

1

0

1

1

1

0

0

1

1

1

1

1

Рис. 2.8. Двухразрядный цифровой компаратор:

а – структура; б – таблица истинности устройства

2.1.3. Сумматоры

В цифровой технике все операции производятся в двоичной системе счисления. Для упрощения аппаратуры все математические

операции (умножение, деление, вычитание, возведение в степень,

извлечение корня и т. д.) сводятся к сложению. Узел, предназначенный для сложения двоичных чисел, называется сумматором. Многоразрядные сумматоры состоят из одноразрядных, каждый из которых складывает два одноразрядных слагаемых, прибавляет к ним

значение переноса из младшего разряда и при необходимости формирует единицу переноса в старший разряд.

Построим схему простейшего одноразрядного сумматора с двумя

входами, который осуществляет сложение двух одноразрядных чисел

без прибавления к ним значения переноса из младшего разряда. Такой сумматор с двумя входами обычно называют полусумматором.

Согласно правилам сложения двоичных чисел можно записать

возможные варианты сумм двух одноразрядных двоичных чисел:

45

0 + 0 = 00,

0 + 1 = 01,

1 + 0 = 01,

1 + 1 = 10.

Полусумматор должен функционировать по этим правилам. Если

обозначить первое слагаемое – Х, второе – Y, результат сложения в разряде – S, перенос в следующий разряд – Р, то при сложении двух двоичных слагаемых Х и Y получается сумма Х + Y = РS. Первоначально функциональную схему полусумматора можно представить в виде устройства

с двумя входами X и Y и двумя выходами S и P. Будем считать, что Р

и S есть логические функции от Х и Y. Тогда, исходя из правил сложения, можно составить таблицу истинности полусумматора, устанавливающую соответствие между его входными и выходными сигналами.

X

S

Y

Полусумматор P

X

0

0

1

1

Y

0

1

0

1

S

0

1

1

0

Р

0

0

0

1

Выразим логические функции S(Х, Y ) и Р(Х, Y ) в виде формул. Из

таблицы видно, что логическая функция Р является конъюнкцией Х

и Y (Р = Х · Y ), а функция S является функцией ИСКЛЮЧАЮЩЕЕ

ИЛИ, которую, как известно, можно записать в виде

S = X ⋅Y + X ⋅Y .

Полученные уравнения для S и P позволяют по методике, изложенной в п. 2.2, построить схему полусумматора, показанную на рис. 2.9.

a

б

X

в

&

1

1

Y

S=X⊕Y

X

=1

S

Y

&

1

& P=X·Y

&

P

Рис. 2.9. Полусумматор:

а – функциональная схема; б – эквивалентная схема;

в – условное графическое обозначение

46

X HS

S

Y

P

Полученная схема не является оптимальной с точки зрения количества входящих в нее логических элементов, она может быть упрощена. Для этого сначала преобразуем уравнение S = X ⋅Y + X ⋅Y .

Применим следующий искусственный прием: согласно алгебре Буля

к правой части уравнения мы имеем право добавить два слагаемых –

X ⋅ X и Y ⋅Y (так как они равны нулю). Тогда получим

S = X ⋅Y + X ⋅Y + X ⋅ X + Y ⋅Y .

Сгруппируем слагаемые и вынесем общие множители:

S = X (Y + X ) + Y (Y + X ) = (Y + X ) ⋅ ( X + Y ).

Согласно теореме де Моргана X + Y = X ⋅Y , но Х · Y = Р, а следовательно, X ⋅Y = P , тогда S = ( X + Y ) ⋅ P . Теперь схему полусумматора можно представить следующим образом (рис. 2.10).

X

1

X+Y

&

Y

P

1

&

S = X ⊕Y =

= (X +Y)·P

P =X ·Y

Рис. 2.10. Упрощенная схема полусумматора

По сравнению с предыдущей данная схема дает экономию двух

элементов. При большом количестве таких полусумматоров в устройствах получается существенный выигрыш.

Синтезированный полусумматор может быть использован лишь

в разряде единиц – у него нет третьего входа для единицы переноса из младшего разряда. Для сложения в других разрядах используются сумматоры с тремя входами: два входа используются для подачи слагаемых Х и Y, третий – для сигнала переноса Р с предыдущего

разряда. На рис. 2.11 показаны его графическое обозначение и вариант реализации на двух полусумматорах.

47

а

б

Xi

Yi

Pi

S

P

Si

Xi

Pi+1

HS S

Yi

P

S'i

Si

HS S

P'i

P

1

Pi+1

Pi

i-й разряд

Рис. 2.11. Полный сумматор:

а – условное графическое обозначение; б – одноразрядный сумматор,

построенный из двух полусумматоров

Полный сумматор имеет дополнительный вход переноса Pi из

предыдущего разряда. Сигналы Si и Pi+1 на его выходах получаются

в результате сложения трех входных сигналов. Таблица истинности для одноразрядного сумматора с тремя входами имеет следующий вид:

Xi

Yi

Pi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Последовательно соединяя полусумматор и несколько одноразрядных сумматоров с тремя входами, можно составлять многоразрядные двоичные сумматоры, складывающие одноименные разряды

слагаемых. В качестве примера на рис. 2.12 показана функциональная схема трехразрядного параллельного сумматора (разряды слагаемых на его входы поступают одновременно, в параллельном коде)

с последовательным переносом.

Такой сумматор складывает трехразрядные двоичные числа.

Числа-слагаемые обозначены {X2, X1, X0} и {Y2, Y1, Y0}. Сигналы, соответствующие значениям разряда единиц в слагаемых (X0 и

Y0), поступают на входы полусумматора. Входными сигналами для

48

первого сумматора являются сигнал переноса P1 с выхода полусумматора и значения X1 и Y1 второго разряда слагаемых. Наконец, второй полный сумматор складывает значения 3-го разряда слагаемых X2

и Y2 и сигнал переноса P2. В результате сложения двух трехразрядных двоичных чисел на выходе в зависимости от значения сигнала

переноса P3 получается трех- или четырехразрядная двоичная сумма.

Быстродействие параллельного сумматора ограничивается задержкой переноса, так как формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал

переноса младшего разряда не распространится последовательно во

всей системе. Для увеличения быстродействия сумматоров разработаны и применяются специальные схемы ускоренного (сквозного,

параллельного и группового) переноса.

Числа-слагаемые

Х2 Х1 Х0

Y2 Y1 Y0

S0

Х0

Y0

Полусумматор

Х1

Y1

Полный

сумматор

1

Х2

Y2

Полный

сумматор

2

P1

S1

P2

S2

P3

Рис. 2.12. Трехразрядный параллельный сумматор

с последовательным переносом

Особенность рассмотренных сумматоров в том, что выходные сигналы определяются в любой момент времени комбинацией входных

сигналов, по-данных одновременно на его входы. Снятие входных

сигналов приводит к исчезновению выходных сигналов, т. е. такие

49

сумматоры не обладают памятью. Результат сложения обычно запоминается в отдельных регистрах.

Кроме рассмотренных простейших схем сумматоров на практике широко используют также накапливающие двоичные сумматоры и десятичные сумматоры. Накапливающий сумматор производит суммирование слагаемых, поочередно поступающих на его вход

в параллельном коде, и запоминает результат суммирования. Десятичные сумматоры используют двоично-десятичную систему счисления. При этом каждая десятичная цифра – от 0 до 9 – кодируется

четверкой двоичных разрядов – тетрадой со значениями соответственно от 0000 до 1001.

В сериях интегральных микросхем есть одно-, двух- и четырехразрядные сумматоры, которые можно объединить для получения сумматоров с любой разрядностью. В серию К155, например, входят

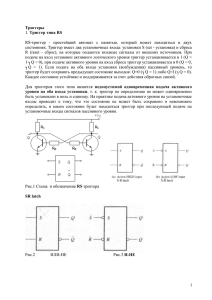

сумматоры: К155ИМ2 – двухразрядный и К155ИМ3 – четырехразрядный (рис. 2.13).