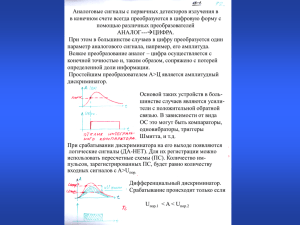

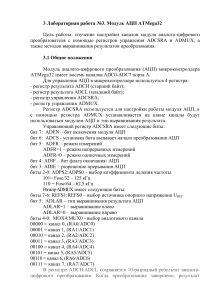

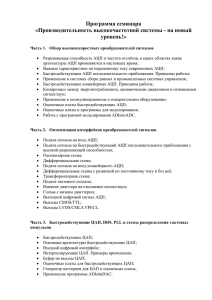

1. На языке Assembler можно использовать команду условного перехода «sbrs (регистр), (номер бита)», которая, в зависимости от того, равен ли заданный бит в заданном регистре нулю или нет, выполняет следующую за ней команду. Пример чтения 4го бита из порта А. ldi r16, 0 ldi r17, 0 in r16, PINA sbrs r16, 4 ser r17 2. Быстродействие многоступенчатого АЦП можно повысить, применив конвейерный принцип многоступенчатой обработки входного сигнала. Конвейерная архитектура позволяет существенно (в несколько раз) повысить максимальную частоту выборок многоступенчатого АЦП. То, что при этом сохраняется суммарная задержка прохождения сигнала, соответствующая обычному многоступенчатому АЦП с равным числом ступеней, не имеет существенного значения, так как время последующей цифровой обработки этих сигналов все равно многократно превосходит эту задержку. За счет этого можно без проигрыша в быстродействии увеличить число ступеней АЦП, понизив разрядность каждой ступени. В свою очередь, увеличение числа ступеней преобразования уменьшает сложность АЦП. Действительно, например, для построения 12-разрядного АЦП из четырех 3разрядных необходимо 28 компараторов, тогда как его реализация из двух 6- разрядных потребует 126 компараторов 3. Работа интегратора основана на том, что инвертирующий вход заземлён, согласно принципу виртуального замыкания. Через резистор R1 протекает входной ток IBX, в тоже время для уравновешивания точки нулевого потенциала, конденсатор будет заряжаться током одинаковым по величине IBX, но с противоположным знаком. В результате на выходе интегратора будет формироваться напряжение, до которого конденсатор заряжается этим током. Входное сопротивление интегратора будет равно сопротивлению резистора R1, а выходное сопротивление будет определяться параметрами ОУ. 𝑈вых = 1 ∫ 𝑈вх 𝑅1 𝐶1