презентация_лк_4_ОЭВМ

реклама

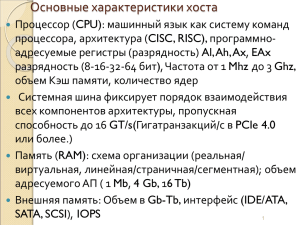

Обобщенная структура и алгоритм работы МП системы ША CPU МП ШД ПЗУ ОЗУ УВВ1 УВВn ШУ fclk ГТИ Обобщенный алгоритм работы МП системы 1 2 3 4 Структурная схема базового микропроцессора i8086 Регистр флагов FLAG CF (Carry Flag) - Флаг переноса - он устанавливается, если в результате операции формируется перенос или заем из старшего разряда результата. - PF (Parity Flag) - Флаг четности - он устанавливается, если в младшем байте результата сформировано четное количество двоичных единиц. - AF (Auxiliary Flag) – Флаг вспомогательного переноса –устанавливается если при формировании результата произошел перенос из младшего полубайта в старший или заем из старшего полубайта в младший. Он используется в операциях над двоично-десятичными числами. - ZF (Zero Flag) – Флаг нулевого результата – устанавливается, если результат операции равен нулю. SF (Signum Flag) – Флаг знака – принимает значение старшего разряда результата и в случае операций со знаком, характеризует его знак. - OF (Overflow Flag) – Флаг переполнения – устанавливается, если в результате операции происходит перенос в знаковый бит или заем из знакового бита результата. Является индикатором переполнения – ситуации, когда результат выходит за пределы допустимого диапазона значений для чисел TF (Trap Flag) – Флаг трассировки (флаг пошагового режима). При установке TF в «1» процессор переходит в режим пошагового выполнения команд. Используется в программах отладчиков. - IF (Interrupt-enable Flag) – Флаг разрешения прерываний. Если IF = 1, то процессор реагирует на прерывания, поступающие от внешних устройств. Если IF = 0, прерывания от внешних устройств запрещены. - DF – (Direction Flag) – Флаг направления, который определяет порядок обработки цепочек данных (строк). Если DF = 0, обработка начинается в прямом направлении, от меньших адресов к большим. Если DF = 1, то обработка происходит в обратном направлении. Работа МП с памятью Адресное пространство - число адресов, которое может сформировать МП на шине адреса Физический (полный) адрес PA ячеек памяти представляет собой 20 разрядный двоичный код на шине адреса МП A19A18A17….A1A0 0 0 0 … 0 0 = 0 = 00000h …………………………………. 1 1 1 … 1 1 = 220 – 1 = FFFFFh Число адресов составляет 220 =1024х1024=1.048.576 Максимальная емкость памяти составляет 220 х 8 = 220 байт = 1 Мбайт Работа МП с памятью Принцип сегментации памяти: 1.Память разбивается на сегменты длиной 216 = 64кбайт. Сегменты могут начинаться с адресов кратных 16: 0 - 00000000b – 00h 16 - 00010000b - 10h 32 - 00100000b - 20h 48 - 00110000b - 30h 64 - 01000000b - 40h адрес 00000 00001 00002 00003 0000F 00010 00011 00D4F 00D50 00D51 039EF 039F0 039F1 FFFFC FFFFD FFFFE FFFFF содержимое Обратиться к сегменту памяти можно, указав его базовый (сегментный) адрес SEG XXXX0h 2. Обратиться к ячейке внутри сегмента можно указав на сколько адресов она отстоит от начала сегмента (смещение OFFSET) 3. К любую ячейке можно обратиться указав пару 16 разрядных адресов SEG:OFFSET Это логический адрес ячеек памяти 0000 0000:0003 адрес 00000 00001 00002 00003 0001 0001:0001 0000F 00010 00011 00D5 0D5:0001 00D4F 00D50 00D51 039F 039EF 039F0 039F1 FFFFC FFFFD FFFFE FFFFF содержимое * ** *** PA = SEG*16 + OFFSET Программная модель МП системы Структурная схема базового микропроцессора i8086 NMI INTR CLK RESET READY TEST MN/MX HLDA (RQ/GT1) HOLD (RQ/GT0) CPU AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 A16/ST3 A17/ST4 A18/ST5 A19/ST6 BHE/ST7 GND GND Ucc RD WR(LOCK) M/IO(S2) DT/R(S1) DEN(S0) ALE(QS0) INTA(QS1)