1 без резисторов обратной связи

реклама

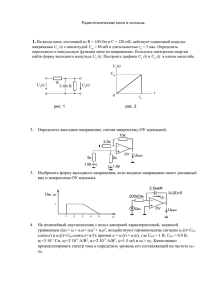

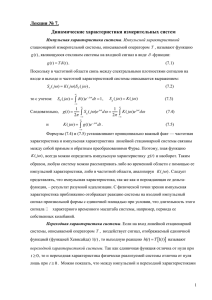

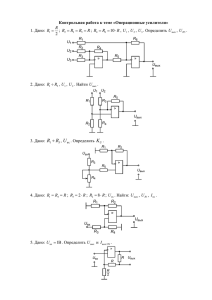

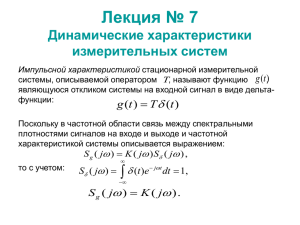

Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом Н.Н. Прокопенко, Н.В. Бутырлагин, И.В. Пахомов Россия, Донской государственный технический университет, e-mail: [email protected], [email protected], [email protected] ВВЕДЕНИЕ Современная теория электронных схем предлагает для построения микроэлектронных устройств преобразования сигналов более 50 различных типов активных элементов (АЭ) [1]. Среди них наиболее известны операционные усилители (ОУ). Многие из представленных в [1] АЭ имеют «экзотическое» применение, что обусловлено иногда недостаточной популяризацией наиболее выгодных для них областей использования. К таким АЭ относятся и мультидифференциальные операционные усилители (МОУ), которые, несмотря на ряд уникальных свойств, достаточно редко применяются в микроэлектронных изделиях. Это связано с тем, что МОУ является относительно новым функциональным узлом аналоговой микросхемотехники [2] и имеет специфические схемы включения. Достаточно перспективно использование МОУ в инструментальных усилителях [3], например, для работы с датчиками мостового типа. Синтез современных устройств частотной селекции в ряде случаев существенно упрощается при наличии МОУ [4]. Большой практический интерес представляют звенья активных фильтров на нескольких МОУ [3-11], так как такие схемы оказываются более высокочастотными при идентичном энергопотреблении [4]. МОУ используются в ЦАП и АЦП [12,13], специальных интерфейсах [13,15], в акселерометрах [16], управляемых усилителях [17], преобразователях «напряжениеток» [18], схемах интегрирования и дифференцирования сигналов [19], перемножителях напряжений, управляемых резисторах, модуляторах, дифференциальных интеграторах [19,10]. 2 ОСОБЕННОСТИ АРХИТЕКТУРЫ И СХЕМОТЕХНИКИ МОУ С ОДНИМ ВЫСОКОИМПЕДАНСНЫМ УЗЛОМ + I5 =3I0 2I0 I 6 =3I0 u1 A1 VT1 1 + uвх.1 I0 I0 VT5 VT6 2 gm1 Ск Вх.(-) 2 A2 I0 3 VT3 u3 3 +Е с БУ VT4 4 R2 Вх.(+)3 +1 S1 Вых. uвх.2 4 Вх.(-) 4 I0 I0 iБУ≈0 uS 2 Вх.(+)1 Cк i1=gm1uвх.1 - u2 VT2 R1 I0 А1 1 2I0 А2 Вых. +1 Σ1 + БУ i2=gm2uвх.2 uвых gm2 - Rк u4 ПТ1 Rк К i =-1 - Рис. 2. Функциональная схема перспективного МОУ с высокоимпедансным узлом S1 Рис. 1. Практическая схема МОУ на основе параллельного включения нескольких ДК (А1, А2) i1, i2 tg1 ~ 1 Rэ -Uгр Imax=I0 I max gm Uгр 1 Uгр Rэ u вх.1 ,uвх.2 Uгр -Imax=-I0 Рис. 3. Проходная характеристика преобразователей «напряжение-ток» А1, А2 МОУ с высокоимпедансным узлом S1 3 БАЗОВЫЕ СХЕМЫ ВКЛЮЧЕНИЯ Инвертирующий усилитель с Ky=-1 без резисторов обратной связи Дифференциальный усилитель разности двух сигналов без резисторов обратной связи 1 u1 uвх.1 2 А1 + gm1 - Σ1 uвх.2 А2 + gm2 - iБУ≈0 БУ Вых. uвх. +1 i2=gm2uвх.2 uвых u u2 Т (u1 u 2 ) 1 u1 u 2 , 1 Т 1 Т 1 Если g m1 g m 2 , то при uвых Rк K БУ g (u1 u2 ) m1 . gm2 А2 + gm2 - БУ i БУ 0 uвых Rк Рис. 5. Инвертирующий усилитель с Ky=-1 Основные уравнения при gm1 gm2 gm : u вых K БУ Rк g m (u вх.1 u вх.2 ) , u вых T (u вх u вых ) , u вых (1 T ) Tu вх , где T K БУ Rк g m 1 Таким образом, Ку u вых Т u вх K y u вх u вх 1 Т 1 1 - модуль коэффициента передачи. 1 Т -1 Когда g m1 2 g m 2 или g m2 2 g m1 где получаем соответственно В тех случаях, когда g m1 g m 2 , Rк K БУ : uвых 2(u1 u2 ), y вх.1 u2 0 u вых 0,5(u1 u 2 ) y d12 y c1 , y вх.2 u1 0 y d 21 y c 2 Вых. +1 i2 =gm2 uвх.2 4 Рис. 4. Дифференциальный усилитель на основе МОУ u S [(u1 u 2 ) g m1 u вх.2 g m2 ]Rк S1 uвх.2 Cк i1 =gm1 uвх.1 2 3 Rк 4 u вых А1 + gm1 - 1 uвх.1 u2 3 Cк i1=gm1(u1-u2) uвых g m1 uвх . gm2 4 БАЗОВЫЕ СХЕМЫ ВКЛЮЧЕНИЯ Неинвертирующий усилитель напряжения Вх. uвх А1 1 + gm1 - uвх.1 i1=gm1uвх.1 2 Σ1 А2 3 + gm2 - uвх.2 4 Неинвертирующий сумматор двух сигналов u1 iБУ≈0 uвх.1 i1=gm1uвх.1 2 БУ Σ1 Вых. Cк iБУ≈0 А2 + gm2 - 3 i2=gm2uвх.2 uвых u3 uвх.2 u S Rк ( g m1u вх.1 g m2 u вх.2 ), u вых K БУ Rк g m (u вх.1 u вх.2 ), 2u вх 2Т u вх K y u вх 2u вх , 1 Т 1 Т 1 Если g m1 g m 2 , то при Rк K БУ g uвых 1 m1 uвх . gm2 Входная проводимость схемы рис. 6: Rк Основные уравнения: u вых K БУ u S Rк g m K БУ (u вх.1 u вх.2 ), где T K БУ Rк g m 1 , K y 2(1 T ) uвых Рис. 7. Неинвертирующий сумматор двух сигналов Основные уравнения при gm1 gm 2 : 1 1 Вых. i2=gm2uвх.2 4 Rк БУ +1 +1 Рис. 6. Неинвертирующий усилитель u вых А1 + gm1 - 1 Cк gm gm1 gm2 ; T K БУ Rк g m 1 2 . u вых u1 u 2 u1 u 2 . 1 Т 1 В общем случае при g m1 g m 2 и T 1 u вых y вх y d12 y c1 y c3 y d34 (1 T ) u вых g m1 2 g m 2 2u1 u 3 g m1 u1 u 3 . g m2 u вых g m 2 2 g m1 0,5u1 u 3 5 ОСНОВНЫЕ НАПРАВЛЕНИЯ РАЗВИТИЯ СХЕМОТЕХНИКИ МОУ Быстродействие МОУ Схемы МОУ с рассматриваемой архитектурой потенциально имеют более высокое быстродействие, чем классические ОУ. С учетом [20] можно показать, что скорость нарастания выходного напряжения ( вых ) схем с МОУ: вых 2f 1U гр , где f1 – частота единичного усиления по петле обратной связи скорректированного МОУ; U гр – диапазон активной работы входных преобразователей «напряжение-ток» А1, А2 (например, U гр 2 3 В ). Таким образом, сформулированные ранее требования к входным каскадам А1, А2 рассматриваемого подкласса МОУ способствуют (в сравнении с классическими ОУ [20] при идентичных f1), повышению вых в N - раз, где N 10 30 . 6 ОСНОВНЫЕ НАПРАВЛЕНИЯ РАЗВИТИЯ СХЕМОТЕХНИКИ МОУ Петлевое усиление МОУ в схемах с отрицательной обратной связью. Преобразование токов i1, i2 в напряжение uвых в схеме рис. 2 ведется на достаточно большом сопротивлении Rк . Это позволяет получить большой коэффициент преобразования напряжений uвх.1, uвх.2 в напряжение uвых, который влияет на петлевое усиление Т>>1. В связи с малыми значениями крутизны передачи (gm) А1, А2 получение больших значений петлевого усиления T К БУ g m Rк 1 при К БУ 1 , связано, прежде всего, с увеличением эквивалентного сопротивления (Rк) в высокоимпедансном узле S1 . Оно зависит от выходных сопротивлений этих каскадов, а также входного сопротивления буферного усилителя БУ Rвх.БУ . В этой связи для увеличения Rк целесообразно использовать в выходных цепях А1, А2 каскодное включение транзисторов. Это позволит увеличить Rк до уровня сопротивления rк закрытых коллекторных переходов выходных транзисторов А1, А2, и, следовательно, получить Tmax rк r g m к 1 . 2 2Rэ Необходимо также принимать меры для минимизации входной проводимости БУ. Заметим, что полевые транзисторы в каскодных выходных цепях подсхем А1, А2 окажут положительное влияние на эквивалентное сопротивление Rк. 7 ОСНОВНЫЕ НАПРАВЛЕНИЯ РАЗВИТИЯ СХЕМОТЕХНИКИ МОУ Для получения в МОУ на биполярных транзисторах эквивалентных выходных сопротивлений Rк rк можно использовать схемотехнику, рассмотренную в [21]. Так, численное значение Rк в схеме рис. 8 определяется уравнением 1 2 3 1 1 4 Rк r r2 к1 1 rк1 rк2 , где i 1 - коэффициенты усиления по току эмиттера i-го транзистора . Это позволяет увеличить петлевое усиление T 1 в МОУ. + R1>>rэ1 Вх.i1 α4i2 VT1 i1 VT2 +Ec1 α1α4i1 rк1 i1 α2i1 Рис. 8. Метод повышения выходного сопротивления Rк в высокоимпедансном узле 1 БУ Вых. Σ1 +1 uΣ1 α3α2i1 α4i2 rк2 i2 VT4 Ec2 VT3 α2i1 Вх.i2 R2>>rэ3 - 8 ОСНОВНЫЕ НАПРАВЛЕНИЯ РАЗВИТИЯ СХЕМОТЕХНИКИ МОУ Дрейф нуля МОУ Точностные характеристики рассмотренных архитектур на основе МОУ (в частности напряжение смещения нуля Uсм), несколько хуже, чем у обычного ОУ. Действительно, расширение диапазона активной работы входных каскадов А1, А2 сопровождается ухудшением коэффициента усиления по напряжению (Ku) этих каскадов [20,22]. В свою очередь уменьшение Ku увеличивает приведенный ко входу дрейф э.д.с. смещения нуля, обусловленный влиянием второго каскада МОУ. Для разрешения этого противоречия рекомендуется использовать предлагаемые в [22] методы минимизации Uсм, связанные с введением слабой токовой асимметрии в структуру входных каскадов А1, А2. В работе [3] рассмотрены инструментальные усилители (ИУ) на базе двух МОУ. При выполнении ряда параметрических условий в таких ИУ минимизируется дрейф нуля [3]. В практическом отношении это позволяет решить важную задачу построения прецизионных аналоговых интерфейсов для мостовых резистивных датчиков, функционирующих в широком температурном диапазоне, а также использовать многоразрядные АЦП с менее стабильным опорным напряжением [3]. 9 Выводы Выполненный выше анализ, а также данные различных литературных источников показывают, что мультидифференциальный операционный усилитель с высокоимпедансным узлом характеризуется следующими основными свойствами и параметрами: 1. Обладает высокой степенью универсальности, вытекающей из свойств его структуры. МОУ обеспечивает реализацию многих функций, нереализуемых обычными ОУ, либо реализуемых с большими элементными, технологическими или энергетическими затратами. 2. Имеет, как минимум, два идентичных входных дифференциальных каскада (ДК) – один для входных сигналов (ДК1), другой – для сигналов обратной связи (ДК2). Каждый из входных ДК МОУ является интерфейсом для входной дифференциальной цепи и дифференциальной цепи обратной связи (ООС). Это так называемая активная обратная связь. Данная архитектура устраняет прямое взаимодействие между сигналом ООС и входной цепью, которое традиционно вызывает проблемы с деградацией некоторых параметров в схемах на обычных ОУ (входное сопротивление Rвх, коэффициент ослабления входных синфазных сигналов Кос.сф и т.п.). 10 3. Проводимости передачи входных ДК имеют небольшую величину. Это крайне важное ограничение. Оно означает, что входы МОУ способны воспринимать большие дифференциальные напряжения (например, 2÷3 В) и, в отличие от классических ОУ, линейны в широком диапазоне дифференциальных сигналов. Данное обстоятельство является обязательным условием минимизации нелинейных искажений сигналов, подаваемых на дифференциальные входы ДК1 и ДК2 в устройствах на основе МОУ. Таким образом, принципиальное отличие МОУ от классического ОУ состоит в том, что диапазон линейной работы их входных каскадов (ДК1, ДК2), который характеризуется напряжением ограничения (Uгр), должен быть достаточно U U 2 3 В. широким, например, В то же время у классического ОУ на биполярных транзисторах U 50 100мВ. 4. Максимальные синфазные напряжения на входах универсального МОУ также должны быть большими. Таким образом, все четыре входных вывода МОУ с двумя ДК могут находиться при существенно разных потенциалах. Поэтому понятие «виртуального потенциального нуля», которое используется для обычных ОУ, для МОУ неприменимо. Когда к дифференциальным входам ДК1, ДК2 приложены одинаковые по величине, но противоположные по знаку дифференциальные напряжения, выходные токи ДК1 и ДК2 под действием обратной связи компенсируют друг друга в узле суммирования. То есть в высокоимпедансном узле S1 происходит алгебраическое суммирование выходных токов входных ДК1, ДК2, причем сумма этих токов в установившемся режиме равна нулю. В этом смысле узел S1 можно рассматривать 11 как «виртуальный токовый ноль». вх гр гр 5. Потенциально МОУ имеет значительно лучшие параметры по быстродействию (максимальной скорости нарастания выходного напряжения, вых ) по сравнению с классическим ОУ. Это объясняется тем, что в нем минимизированы нелинейные режимы работы входных каскадов, ухудшающие вых . Данное качество МОУ связано с обязательным построением ДК1 и ДК2 на основе дифференциальных усилителей с местной отрицательной обратной связью, которая реализуется за счет введения сравнительно высокоомных резисторов Rэ в эмиттерные цепи транзисторов каждого дифференциального каскада МОУ (ДК1, ДК2). 6. Динамические характеристики для некоторых схем включения МОУ (например, инвертирующий и неинвертирующий инструментальные усилители) одинаковы (например, Rвх, Кос.сф и др.). Это выгодно отличает МОУ от классических усилителей с ООС по напряжению и ООС по току. В МОУ без резисторов обратной связи обеспечиваются симметричные характеристики как с коэффициентом передачи Ky=1, так и с коэффициентом передачи Ky=+1. Это позволяет переключать дифференциальные входы «сигнального» ДК с целью изменения полярности (фазы) усиления. 7. МОУ имеет во многих схемах включения, в т.ч. без резисторов обратной связи, низкую чувствительность параметров усиления к сопротивлению источника сигнала, т.к. его высокое Rвх определяется входным сопротивлением «сигнального» ДК1 с глубокой местной отрицательной обратной связью, которая вводится резистором Rэ. 8. В связи с особенностями архитектуры МОУ имеет ряд уникальных свойств. Основным является то, что возможно множество схем включения без резисторов обратной связи. Внешние резисторы для многих включений МОУ – не требуются. 12 9. Традиционное построение входных каскадов МОУ – на основе дифференциальных усилителей с местной резистивной отрицательной обратной связью (Rэ), подчеркивает влияние второго каскада МОУ на напряжение смещения нуля (Uсм). Это связано с тем, что увеличение Rэ до единиц (иногда до десятков килом) приводит к уменьшению проводимости передачи ДК1 и ДК2 и увеличивает вклад в Uсм второго каскада. 10. Одна из проблем построения широкополосных МОУ с двухкаскадной архитектурой – повышение эквивалентного сопротивления в высокоимпедансном узле до единиц-десятков мегаом. Это позволяет при малых проводимостях передачи входных ДК получить большие значения петлевого усиления, определяющего погрешности многих схем включения МОУ. 11. Наличие емкости коррекции Ск в МОУ приводит к появлению на АЧХ полюса и она становится похожей на АЧХ обычного ОУ. Амплитудно-частотная характеристика МОУ с одним высокоимпедансным узлом и методы ее коррекции такие же, как в классическом ОУ. 12. Схемотехника МОУ по элементным затратам, а также промежуточным и выходным каскадам, практически не отличается от схемотехники классических ОУ . 13. Наличие у МОУ как минимум двух входных дифференциальных каскадов (ДК1, ДК2) позволяет во многих задачах преобразования сигналов уменьшить общий ток потребления микросхемы, который в основном связан с выходным и промежуточным каскадами. 13 14. Специфика работы входных дифференциальных каскадов МОУ (широкий диапазон допустимых входных дифференциальных напряжений) позволяет в ряде случаев избежать включения на их входах защитных нелинейных ограничителей напряжений (например, встречно-параллельно включенных p-n переходов). В конечном итоге это уменьшает эквивалентную входную емкость МОУ, расширяет его диапазон рабочих частот в основных схемах включения. 15. Одно из перспективных направлений практического использования МОУ – инструментальные усилители. Практическую значимость вышеназванных свойств МОУ трудно переоценить. Это позволяет сделать важный вывод – при планировании номенклатуры перспективной элементной базы для аналого-цифровых интерфейсов и датчиковых систем необходимо предусмотреть выпуск (в рамках программ импортозамещения) российских МОУ со схемотехникой нового поколения. Полученные в статье основные уравнения МОУ позволяют выполнять сравнительно простые аналитические расчеты как известных, так и новых схем их включения. 14 ЛИТЕРАТУРА 1. Dalibor Biolek, Raj Senani, Viera Biolkova. Active Elements for Analog Signal Processing: Classification, Review, and New Proposals // Radioengineering. 2008. Vol. 17. No. 4. Pp.1532. 2. Säckinger E., Guggenbühl W. A versatile building block: the CMOS differential difference amplifier // IEEE J. Solid-State Circuits. 1987. Vol. SC-22. Pp. 287-294. 3. Крутчинский С.Г. и др. Прецизионные аналоговые интерфейсы на базе двух мультидифференциальных операционных усилителей // Электронный научный журнал «Инженерный вестник Дона», №3. 2013. http://ivdon.ru/magazine/archive/n3y2013/1802. 4. Крутчинский С.Г. Принцип собственной компенсации в прецизионных RС-фильтрах. Шахты: ФГБОУ ВПО «ЮРГУЭС», 2012. 100 с. 5. Singh, В., Singh, A. K., & Senani, R. A new universal biquad filter using differential difference amplifiers and its practical realization // Journal of Analog Integrated Circuits and Signal Processing. 2013. Vol. 75. Pp. 293-297. 6. Viera Biolkova, Zdenek Kolka, and Dalibor Biolek. Dual-Output All-Pass Filter Employing Fully-Differential Operational Amplifier and Current-Controlled Current Conveyor // 7th International Conference on Electrical and Electronics Engineering (ELECO), 2011. Pp. II-340 - II-344 7. Shu-Chuan Huang. A Wide Dynamic Range CMOS Differential Difference Amplifier Design with Application to Continuous-time Filters. Ohio State University. 1990. 148 p. 8. Stornelli V., Pantoli L., Leuzzi G., Ferri G. Fully differential DDA-based fifth and seventh order Bessel low pass filters and buffers for DCR radio systems // Analog Integrated Circuits 15 and Signal Processing. 2013. Vol. 75. No 2. Pp. 305-310. 9. Toker, A., & Özoğuz, S. Novel all-pass filter section using differential difference amplifier // AEU - International Journal of Electronics and Communications. 2004. Vol. 58. No. 2. Pp. 153-155. 10. Mahmoud S.A., Soliman A.M. The Differential Difference Operational Floating Amplifier: A new block for analog signal processing in MOS technology // IEEE Trans. On CAS – II. 1998. Vol. 45. No. 1. P. 148-158. 11. Крутчинский С.Г., Старченко Е.И. Мультидифференциальные операционные усилители и прецизионная микросхемотехника // Электроника и связь / Под ред. Ю.И. Якименко. 2004. T. 9. № 21. С. 101–107. 12. Shu-Chuan Huang, Mohammed Ismail. Design of a CMOS Differential Difference Amplifier and its Applications in A/D and D/A Converters // IEEE Asia-Pacific Conference on Circuits and Systems. 1994. Pp. 478-483. 13. Theory and Monolithic CMOS Integration of a Differential Difference Amplifier : A dissertation submitted to the Swiss Federal Institute of Technology Zurich for the degree of Doctor of Technical Science / Eduard Säckinger. Hartung-Gorre Verlag, 1989. 213 p. 14. Cilingiroglu U., Hoon S.K. An accurate self-bias threshold voltage extractor using differential difference feedback amplifier // IEEE International Symposium on Circuits and Systems. 2000. Vol. 5. Pp. V-209 – V-212. 15. Shin-Il Lim, In-Sub Choi, Han-Ho Lee. Biochemical Sensor Interface Circuits with Differential Difference Amplifier // IEEE Asia Pacific Conference on Circuits and Systems. 2012. Pp. 176-179. 16 16. Jiangfeng Wu, Gary K. Fedder, and L. Richard Carley. A Low-Noise Low-Offset Capacitive Sensing Amplifier for a 50 g Hz Monolithic CMOS MEMS Accelerometer // IEEE journal of solid-state circuits. May 2004. Vol. 39. No. 5. Pp. 722-730. 17. Kai-Wen Yao, Wei-Chih Lin, Cihun-Siyong Alex Gong, Yu-Ying Lin, and Muh-Tian Shiue. A Differential Difference Amplifier for Neural Recording System with Tunable Low-Frequency Cutoff // IEEE International Conference on Electron Devices and Solid-State Circuits. 2008. Pp. 355-358. 18. S.-C. Huang. M. Ismail, and S. R. Zarabadi. A wide range differential difference amplifier: A basic block for analog signal processing in MOS technology // IEEE Transactions on Circuits and Systems-II: Analog and digital signal processing. May 1993. Vol. 40. No. 5. Pp. 289-301. 19. Kewei Yang, Andreas G. Andreou. A Multiple Input Differential Amplifier Based on Charge Sharing on a Floating-Gate MOSFET // Analog Integrated Circuits and Signal Processing. 1994. Vol. 6. Issue 3. Pp. 197-208. 20. Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. Операционные усилители с непосредственной связью каскадов. Л.: 1979. 148 с. 21. Прокопенко Н.Н. , Ковбасюк Н.В. Архитектура и схемотехника аналоговых микросхем с собственной и взаимной компенсацией импедансов. Шахты: Изд-во ЮРГУЭС, 2007. 326 с. 22. Прокопенко Н.Н., Серебряков А.И. Архитектура и схемотехника операционных усилителей. Методы снижения напряжения смещения нуля в условиях температурных и радиационных воздействий. Изд-во: LAP Lambert Academic 17 Publishing. 2013. 127 c