приложения к отчету по умк-7

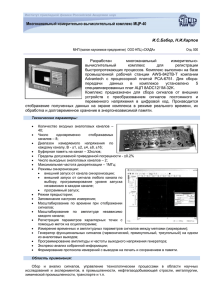

реклама

ПРИЛОЖЕНИЕ 7

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ «МИЭТ»

«УТВЕРЖДАЮ»

Ректор МИЭТ

чл.-корр. РАН

____________________ Ю.А. Чаплыгин

«_____» _____________________ 2011 г.

ПРОГРАММА ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

«СХЕМОТЕХНИЧЕСКОЕ ПРОЕКТИРОВАНИЕ АНАЛОГОВЫХ УСТРОЙСТВ

С ТОПОЛОГИЧЕСКИМИ НОРМАМИ 90 НМ»

2011 г.

1

Рабочая программа профессионального модуля утверждена на заседании учебно-методического

совета образовательных программ опережающей профессиональной подготовки (уровень магистратура)

и

переподготовки

в

области

проектирования и

производства

топологическими нормами 90 нм, протокол от 16 ноября 2011 г. № 2.

Организация-разработчик: Национальный исследовательский университет «МИЭТ»

Авторы:

Мушта А.И. к.т.н., профессор

Сумин А.М., аспирант

2

СБИС

с

СОДЕРЖАНИЕ

1. ПАСПОРТ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ............................................... 4

2. РЕЗУЛЬТАТЫ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ............................................ 6

3. СТРУКТУРА И СОДЕРЖАНИЕ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ..................................... 7

4. УСЛОВИЯ РЕАЛИЗАЦИИ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ................... 9

5. КОНТРОЛЬ И ОЦЕНКА РЕЗУЛЬТАТОВ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО

МОДУЛЯ (ВИДА ПРОФЕССИОНАЛЬНОЙ ДЕЯТЕЛЬНОСТИ) ................................................. 11

3

1. ПАСПОРТ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

«СХЕМОТЕХНИЧЕСКОЕ ПРОЕКТИРОВАНИЕ АНАЛОГОВЫХ УСТРОЙСТВ

С ТОПОЛОГИЧЕСКИМИ НОРМАМИ 90 НМ»

1.1. Область применения программы

Программа профессионального модуля является частью профессиональной образовательной

программы опережающей переподготовки специалистов по проектированию ультрабольших

интегральных микросхем с топологическими нормами 90 нм в части освоения вида

профессиональной деятельности: проектирование ультрабольших интегральных микросхем с

топологическими нормами 90 нм и соответствующих профессиональных компетенций (ПК).

1. Базовые компетенции (знания) БКЗ

- Знание основ теории автоматизированного проектирования, моделирования и характеризации

УБИС топологическими нормами до 90 нм;

- Знание методологии и маршрутов проектирования аналоговых схем и устройств смешанного

сигнала (по маршрутам):

- проектирование аналоговых УБИС с топологическими нормами до 90 нм;

- проектирование смешанных УБИС с топологическими нормами до 90 нм;

- Знание теории схемотехнического и физического проектирования аналоговых СБИС с

топологическими нормами до 90нм

2. Базовые компетенции (умения и навыки) БКУ

- Навыки использования современных программных средств Cadence для ускоренного

моделирования и статистического анализа СБИС с топологическими нормами до 90 нм;

-

Навыки использования современных программных средств физического проектирования и

верификации с учетом технологических требований компании Cadence;

-

Умение использовать средства автоматизации проектирования аналоговых и устройств

смешанного сигнала:

- проектирование аналоговых устройств;

- проектирование смешанных устройств.

3. Специальные компетенции (знания) СКЗ

- Знание маршрута проектирования базовых технологических библиотек компонентов с

топологическими нормами до 90 нм для САПР компании Cadence;

- Знание особенностей маршрута проектирования полузаказных и заказных СБИС по

технологическим нормам 90нм

4. Специальные компетенции (умения и навыки) СКУ

4

- Владение пакетами программ Cadence и Mentor Graphics для физической и временной

характеризации и верификации СБИС с топологическими нормами 90 нм;

- Навыки проектирования наноэлектронных СБИС повышенной энергоэффективности с

применением САПР Cadence;

- Умение контролировать параметры разрабатываемых приборов на всех этапах маршрута

проектирования, владение методами физической характеризации и верификации УБИС с

топологическими нормами 90 нм.

1.2. Цели и задачи модуля - требования к результатам освоения модуля

С целью овладения указанным видом профессиональной деятельности и соответствующими

профессиональными компетенциями обучающийся в ходе освоения профессионального модуля

должен:

иметь практический опыт: проектирования аналоговых УБИС с топологическими нормами до

90 нм; проектирования смешанных УБИС с топологическими нормами до 90 нм.

уметь:

использовать

современные

программные

средства

Cadence

для

ускоренного

моделирования и статистического анализа СБИС с топологическими нормами до 90 нм;

использовать современные программные средства физического проектирования с учетом

технологических требований компании Cadence, применять пакеты программ Cadence и Mentor

Graphics для физической и временной характеризации и верификации СБИС с топологическими

нормами 90 нм; проектировать наноэлектронные СБИС повышенной энергоэффективности с

применением САПР Cadence; контролировать параметры разрабатываемых приборов на всех

этапах маршрута проектирования.

знать: основы теории автоматизированного проектирования, моделирования и характеризации

УБИС топологическими нормами до 90 нм; методологию и маршруты проектирования

аналоговых схем и устройств смешанного сигнала; теорию схемотехнического и физического

проектирования

аналоговых

СБИС

с

топологическими

нормами

до

90

нм;

маршрут

проектирования базовых технологических библиотек компонентов с топологическими нормами до

90 нм для САПР компании Cadence; особенности маршрута проектирования полузаказных и

заказных СБИС по технологическим нормам 90нм.

1.3. Рекомендуемое количество часов на освоение программы профессионального модуля:

5

всего - 70 часов, в том числе: максимальной учебной нагрузки обучающегося - 70 часов, включая:

обязательной аудиторной учебной нагрузки обучающегося - 34 часов.

6

2. РЕЗУЛЬТАТЫ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

Результатом освоения программы профессионального модуля является овладение обучающимися

видом профессиональной деятельности «Схемотехническое проектирование аналоговых устройств с

топологическими нормами 90 нм», в том числе профессиональными компетенциями (ПК):

Код ПК

БКЗ-1

БКЗ-2

БКЗ-2.1

БКЗ-2.3

БКЗ-3

БКУ-1

БКУ-2

БКУ-3

БКУ-3.1

БКУ-3.3

СКЗ-1

СКЗ-2

СКУ-1

СКУ-2

СКУ-3

Наименование результата обучения

Знание основ теории автоматизированного проектирования, моделирования и

характеризации УБИС топологическими нормами до 90 нм

Знание методологии и маршрутов проектирования цифровых, аналоговых схем и

устройств смешанного сигнала (по маршрутам)

Знание методологии и маршрутов проектирования аналоговых схем и устройств

смешанного сигнала по маршруту проектирование аналоговых УБИС с топологическими

нормами до 90 нм

Знание методологии и маршрутов проектирования аналоговых схем и устройств

смешанного сигнала по маршруту проектирование смешанных УБИС с топологическими

нормами до 90 нм

Знание теории схемотехнического и физического проектирования аналоговых СБИС с

топологическими нормами до 90нм

Навыки использования современных программных средств Cadence для ускоренного

моделирования и статистического анализа СБИС с топологическими нормами до 90нм

Навыки использования современных программных средств физического проектирования

и верификации с учетом технологических требований компании Cadence

Умение использовать средства автоматизации проектирования цифровых, аналоговых и

устройств смешанного сигнала

Умение использовать средства автоматизации проектирования аналоговых устройств

Умение использовать средства автоматизации проектирования смешанных устройств

Знание маршрута проектирования базовых технологических библиотек компонентов с

топологическими нормами до 90 нм для САПР компании Cadence

Знание особенностей маршрута проектирования полузаказных и заказных СБИС по

технологическим нормам 90нм

Владение пакетами программ Cadence и Mentor Graphics для физической и временной

характеризации и верификации СБИС с топологическими нормами 90нм

Навыки проектирования наноэлектронных СБИС повышенной энергоэффективности с

применением САПР Cadence

Умение контролировать параметры разрабатываемых приборов на всех этапах маршрута

проектирования, владение методами физической характеризации УБИС с

топологическими нормами 90 нм

7

3. СТРУКТУРА И ПРИМЕРНОЕ СОДЕРЖАНИЕ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

3.1. Тематический план профессионального модуля

Коды

профессиональных

компетенций

1

БКЗ-1, БКЗ-2.1, БКЗ3, БКУ-1, БКУ-2,

КУ-3.1, БКУ-3.3,

СКЗ-1, СКЗ-2, СКУ2, СКУ-3

Наименования разделов

профессионального

модуля

Всего часов

(макс. учебная

нагрузка и

практики)

2

Раздел 2.

Проектирование

аналоговых устройств

УБИС.

3

70

Всего:

70

Объем времени, отведенный на освоение

междисциплинарного курса (курсов)

Обязательная аудиторная

учебная нагрузка

обучающегося

Всего,

в т.ч.

часов

лабораторны

е работы и

практические

занятия,

часов

4

5

17

34

34

8

17

Самостоятельна

я работа

обучающегося,

часов

6

36

36

Производственное

обучение (в т.ч.

производственная

практика)

Учебная, Производстве

часов

нная,

часов

(если

предусмотрен

а

рассредоточен

ная практика)

7

8

-

-

-

-

3.2. Содержание обучения по профессиональному модулю (ПМ)

Наименование разделов

профессионального модуля

(ПМ), междисциплинарных

курсов (МДК) и тем

Раздел ПМ 1.

Проектирование

аналоговых устройств

УБИС

МДК 1.1.

«Схемотехническое

моделирование аналоговых

устройств УБИС»

Тема 1.1.

«Схемотехническое

моделирование аналоговых

устройств УБИС»

Содержание учебного материала, лабораторные работы и практические занятия,

самостоятельная работа обучающихся, курсовая работ (проект) (если предусмотрены)

Объем

часов

Уровень

освоения

70

70

Содержание

1

Основы аналогового моделирования

1

6

2

Библиотеки и модели элементов

3

Аналоговое моделирование

Лабораторные работы

1

Лабораторная работа № 1. Среда проектирования аналоговых устройств Cadence

2

Лабораторная работа № 2. Аналоговое моделирование в симуляторе Spectra

3

Лабораторная работа № 3. Аналоговое моделирование в симуляторе UlitraSim

Самостоятельная работа при изучении раздела ПМ 2 (МДК 2.1) Рефераты «Принципы аналогового моделирования»,

«Библиотеки элементов для схемотехнического моделирования с проектными нормами 90 нм БиКМОП технологии»,

«Язык SPICE», «Особенности моделирования в симуляторе Spectra»

9

5

6

8

5

4

36

2

3

4. УСЛОВИЯ РЕАЛИЗАЦИИ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

4.1. Требования к минимальному материально-техническому обеспечению

Реализация программы модуля предполагает наличие специализированных учебных лабораторий,

оснащенных рабочими станциями с ОС Linux.

4.2. Информационное обеспечение обучения

Перечень рекомендуемых учебных изданий, Интернет-ресурсов, дополнительной литературы

Основные источники:

1.

Reference Manual For Generic 90nm Salicide 1.2V/2.5V 1P 9M Process Design Kit (PDK) Revi-

sion 4.5. Cadence Design Systems

2.

GPDK 90 nm Mixed Signal GPDK Spec. Cadence Design Systems

3.

Сафонов И.А., Шеховцев Д.В. Методология проектирования аналоговых устройств УБИС.

Моделирование аналоговых устройств. Конспект лекций. Воронеж: Воронеж. гос. техн. ун-т, 2010

4.

Virtuoso® Spectre® Circuit Simulator Reference. Cadence Design Systems

5.

Virtuoso® Spectre® Circuit Simulator User Guide. Cadence Design Systems

6.

Русанов А.В., Сафонов И.А., Среда проектирования аналоговых устройств Cadence.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

7.

Русанов А.В., Сумин А.М. Аналоговое моделирование в симуляторе Spectra. Методические

указания к лабораторным работам. Воронеж: Воронеж. гос. техн. ун-т, 2010.

8.

Шеховцев Д.В. Аналоговое моделирование в симуляторе UlitraSim. Методические указания к

лабораторным работам. Воронеж: Воронеж. гос. техн. ун-т, 2010

9.

Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том I: Пер. с нем. - М.: ДМК

Пресс, 2008. - 832 с.

10.

Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том II: Пер. с нем. - М.: ДМК

Пресс, 2007. - 942 с.

11.

Сафонов И.А., Сумин А.М. Схемотехническое проектирование аналоговых устройств.

Конспект лекций. Воронеж: Воронеж. гос. техн. ун-т, 2010.

12.

Русанов А.В. Схемотехническое проектирование источников тока и токовых зеркал.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

13.

Макеев С.Н Схемотехническое проектирование усилителей с общим истоком и истоковых

повторителей. Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т,

2010.

14.

Макеев С.Н Схемотехническое проектирование дифференциальных каскадов усиления.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

10

15.

Сумин А.М. Тарасов В.С. Схемотехническое проектирование операционных усилителей.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

16.

Котенев А.В. Схемотехническое проектирование резистивно-емкостных каскадов усиления.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

17.

Шеховцев Д.В. Схемотехническое проектирование преобразователя частоты. Методические

указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010

18.

Русанов А.В., Сафонов И.А. Проектирование топологии аналоговых устройств. Конспект

лекций. Воронеж: Воронеж. гос. техн. ун-т, 2010.

19.

Кирпичев Г.А., Русанов А.В., Сумин А.М. Проектирование топологии аналогового

устройства на примере операционного усилителя. Методические указания к лабораторным

работам. Воронеж: Воронеж. гос. техн. ун-т, 2010

20.

Русанов А.В., Котенев А.В. Физическая и функциональная верификация топологии

аналоговых устройств. Конспект лекций. Воронеж: Воронеж. гос. техн. ун-т, 2010.

21.

Русанов А.В., Котенев А.В. Физическая и функциональная верификация топологии

аналоговых устройств. Методические указания к лабораторным работам. Воронеж: Воронеж. гос.

техн. ун-т, 2010.

Дополнительные источники:

1.

Наундорв Уве. Аналоговая электроника. Основы, расчет, моделирование. Москва:

Техносфера, 2008.- 472 с.

2.

Антипенский Р.В., Фадин А.Г. Схемотехническое проектирование и моделирование

радиоэлектронных устройств. Москва: Техносфера, 2007.- 128с.

4.3. Общие требования к организации образовательного процесса

Для реализации компетентностного подхода при изучении дисциплин профессионального модуля

используются:

в лекционном курсе конспекты лекций, презентации по теме, согласно содержанию дисциплины ;

в качестве самостоятельной работы специалистов подготовка, доклад и обсуждение рефератов по

тематике дисциплины, подготовка к лекциям по конспектам.

Рубежный контроль текущей успеваемости в виде компьютерного тестирования.

4.4. Кадровое обеспечение образовательного процесса

Требования

к

квалификации

педагогических

кадров,

обеспечивающих

обучение

по

междисциплинарному курсу (курсам): доктора и кандидаты наук, а также аспиранты, имеющие

11

опыт практической и научно-методической работы в области проектирования УБИС с

топологическими нормами порядка 90 нм.

12

5. КОНТРОЛЬ И ОЦЕНКА РЕЗУЛЬТАТОВ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО

МОДУЛЯ (ВИДА ПРОФЕССИОНАЛЬНОЙ ДЕЯТЕЛЬНОСТИ)

Образовательное учреждение, реализующее подготовку по программе профессионального модуля,

обеспечивает организацию и проведение текущего и итогового контроля демонстрируемых

обучающимися знаний, умений и навыков. Текущий контроль проводится преподавателем в

процессе обучения. Итоговый контроль проводится экзаменационной комиссией после обучения

по междисциплинарному курсу.

Формы и методы текущего и итогового контроля по профессиональному модулю разрабатываются

образовательным учреждением и доводятся до сведения обучающихся в начале обучения.

Для текущего и итогового контроля образовательными учреждениями создаются фонды

оценочных средств (ФОС). ФОС включают в себя педагогические контрольно-измерительные

материалы,

предназначенные

для

определения

соответствия

(или

несоответствия)

индивидуальных образовательных достижений основным показателям результатов подготовки

(таблицы).

Раздел (тема)

междисциплинарног

о курса

№2

«Проектирование

аналоговых

устройств УБИС»

Результаты

(освоенные

профессиональные

компетенции)

БКЗ-1

БКЗ-2.1

БКЗ-3

БКУ-1

БКУ-2

БКУ-3.1

БКУ-3.3

СКЗ-1

СКЗ-2

СКУ-2

СКУ-3

Основные показатели

результатов подготовки

Обоснование схем построения,

принципов использования в

аналоговых УБИС. Выполнение

моделирования аналоговых

устройств: источников тока и

токовых зеркал, стоковых

повторителей, резистивноемкостных каскадов усиления,

дифференциальных каскадов

усиления, операционных

усилителей, компараторов,

преобразователей частоты,

умножителей частоты,

модуляторов.

Выполнение схемотехнического

аналогового моделирования

(моделирование по постоянному

току, в частотной и временной

области) в различных режимах на

основе библиотек элементов для

схемотехнического

моделирования с проектными

нормами 90 нм БиКМОП

технологии

Создание топологии аналоговых

устройств по проектным нормам

БиКМОП 90 нм, особенности

13

Формы и

методы

контроля

Тест

проектирования топологии

аналоговых УБИС.

Оценка знаний, умений и навыков по результатам текущего и итогового контроля производится в

соответствии с универсальной шкалой (таблица).

Процент

результативности

(правильных ответов)

90 ÷ 100

80 ÷ 89

70 ÷ 79

Менее 70

Качественная оценка индивидуальных

образовательных достижений

балл (отметка)

вербальный аналог

5

Отлично

4

Хорошо

3

Удовлетворительно

2

Не удовлетворительно

На этапе промежуточной аттестации по медиане качественных оценок индивидуальных

образовательных достижений экзаменационной комиссией определяется интегральная оценка

освоенных обучающимися профессиональных и общих компетенций как результатов освоения

профессионального модуля.

14

1. ПАСПОРТ ПРОГРАММЫ УЧЕБНОЙ ДИСЦИПЛИНЫ

«СХЕМОТЕХНИЧЕСКОЕ МОДЕЛИРОВАНИЕ АНАЛОГОВЫХ УСТРОЙСТВ»

1.1. Область применения программы

Программа учебной дисциплины является частью профессиональной образовательной программы

опережающей переподготовки специалистов по проектированию ультрабольших интегральных

микросхем с топологическими нормами 90 нм

по профессиональной деятельности:

проектирование ультрабольших интегральных микросхем с топологическими нормами 90 нм.

1.2. Место дисциплины в структуре профессиональной образовательной программы:

Дисциплина входит в состав модуля «Схемотехническое проектирование аналоговых устройств

УБИС с топологическими нормами 90 нм» опережающей переподготовки специалистов по

направлению «Проектирование и производство СБИС с проектными нормами 90 нм».

Для изучения данной дисциплины специалист должен владеть знаниям, умениями и

профессиональными

«Методология

компетенциями

проектирования

в

рамках

аналоговых

предшествующих

устройств

модулей

УБИС»

и

и

дисциплин

«Схемотехническое

проектирование аналоговых устройств УБИС». В том числе:

Входные знания:

Знание основ теории автоматизированного проектирования, моделирования и характеризации

УБИС топологическими нормами до 90 нм (БКЗ-1);

Знание методологии и маршрутов проектирования цифровых, аналоговых схем и устройств

смешанного сигнала (проектирование аналоговых УБИС с топологическими нормами до 90 нм - БКЗ2.1).

Умения:

Умение использовать средства автоматизации проектирования цифровых, аналоговых и устройств

смешанного сигнала (проектирование аналоговых устройств - БКУ-3.1).

Профессиональные компетенции:

Знание

маршрута

проектирования

базовых

технологических

библиотек

компонентов

с

топологическими нормами до 90 нм для САПР компании Cadence (СКЗ-1);

Знание

особенностей

маршрута

проектирования

полузаказных

и

заказных

СБИС

по

технологическим нормам 90нм (СКЗ-2).

1.3. Цели и задачи учебной дисциплины - требования к результатам освоения дисциплины:

15

Целью дисциплины является теоретическая и практическая подготовка специалистов в области

схемотехнического моделирования и проектирования аналоговых интегральных схем по

субмикронным топологическим нормам, по БиКМОП технологии.

Рассматриваются принципы схемотехнического аналогового моделирования, виды и типы анализа

(моделирование по постоянному току, в частотной и временной области). Изучаются особенности

моделирования аналоговых блоков в различных режимах. Проводится обзор расширенных видов

анализа, таких как спектральный анализ, анализ шумов, анализ чувствительности. Изучаются

состав, структура библиотек элементов для схемотехнического моделирования с проектными

нормами 90 нм БиКМОП технологии.

Основные задачи дисциплины состоят в:

- изучении основ аналогового моделирования интегральных схем в современных САПР;

- формировании у специалиста практического опыта разработки проектирования базовых

аналоговых устройств.

Процесс изучения дисциплины направлен на формирование следующих компетенций:

Знание основ теории автоматизированного проектирования, моделирования и характеризации

УБИС топологическими нормами до 90 нм (БКЗ-1);

Знание методологии и маршрутов проектирования цифровых, аналоговых схем и устройств

смешанного сигнала (проектирование аналоговых УБИС с топологическими нормами до 90 нм - БКЗ2.1);

Знание теории схемотехнического и физического проектирования аналоговых СБИС с

топологическими нормами до 90 нм (БКЗ-3);

Навыки

использования

современных

программных

средств

Cadence

для

ускоренного

моделирования и статистического анализа СБИС с топологическими нормами до 90 нм (БКУ-1);

Умение использовать средства автоматизации проектирования цифровых, аналоговых и устройств

смешанного сигнала (проектирование аналоговых устройств - БКУ-3.1);

Знание

маршрута

проектирования

базовых

технологических

библиотек

компонентов

с

топологическими нормами до 90 нм для САПР компании Cadence (СКЗ-1);

Знание

особенностей

маршрута

проектирования

полузаказных

и

заказных

СБИС

по

технологическим нормам 90нм (СКЗ-2);

Умение контролировать параметры разрабатываемых приборов на всех этапах маршрута

проектирования, владение методами физической характеризации и верификации УБИС с

топологическими нормами 90 нм (СКУ-3).

В результате изучения дисциплины студент должен:

16

Знать: маршрут аналогового моделирования и проектирования аналоговых интегральных схем,

состав и структуру технологических библиотек для аналогового синтеза интегральных схем,

методы частотно-временного анализа, анализа на постоянном токе, параметрические анализы

базовых аналоговых устройств, теории автоматизированного проектирования и моделирования

СБИС с топологическими нормами до 90 нм.

Уметь:

использовать

современные

программные

средств

Cadence

для

моделирования,

использовать технологические библиотеки, проводить моделирование базовых аналоговых

интегральных

схем,

контролировать

параметры

разрабатываемых

приборов

на

этапе

моделирования УБИС с топологическими нормами 90 нм.

Владеть: средствами автоматизации проектирования аналоговых устройств, ускоренного

моделирования фирмы Cadence, методами частотно-временного анализа, методами анализа на

постоянном токе, методами параметрического анализа базовых аналоговых устройств.

1.4. Рекомендуемое количество часов на освоение учебной дисциплины:

максимальной учебной нагрузки обучающегося 68 часов, в том числе:

обязательной аудиторной учебной нагрузки обучающегося 34 часа.

17

2. СТРУКТУРА И ПРИМЕРНОЕ СОДЕРЖАНИЕ УЧЕБНОЙ ДИСЦИПЛИНЫ

2.1. Объем учебной дисциплины и виды учебной работы

Вид учебной работы

Количество

часов

Максимальная учебная нагрузка (всего)

68

Обязательная аудиторная учебная нагрузка (всего)

34

в том числе:

лабораторные занятия

17

практические занятия

-

контрольные работы

-

Итоговая аттестация в форме экзамена

18

2.2. Примерный тематический план и содержание учебной дисциплины

«Схемотехническое моделирование аналоговых устройств УБИС»

Наименование

разделов и тем

1

Раздел 1.

Основы

аналогового

моделировани

я

Тема 1.1.

Содержание учебного материала, лабораторные и практические работы обучающихся. (если

предусмотрены)

2

Содержание учебного материала

Среда проектирования аналоговых устройств.

Маршрут проектирования аналоговых устройств Cadence IC. Средства схемотехнического

моделирования. Симулятор Spectra и UlitraSim

Тема 1.2.

Тема 1.3.

Раздел 2.

Библиотеки и

модели

элементов

Тема 2.1.

Тема 2.2.

Количест

во часов

3

Уровень

освоения

4

2

1

2

Содержание учебного материала

Принципы аналогового схемотехнического моделирования.

Виды и типы анализа

Содержание учебного материала

Расширенные виды анализа

Самостоятельная работа: реферат «Принципы аналогового моделирования»

2

2

3

8

Содержание учебного материала

Библиотеки элементов

Состав, структура библиотек элементов для схемотехнического моделирования с проектными нормами

90 нм БиКМОП технологии

Содержание учебного материала

Модели элементов. Их параметры.

3

3

2

3

Раздел 3.

Аналоговое

моделировани

е

Тема 3.1.

Тема 3.2.

Тема 3.3.

Лабораторные занятия: Среда проектирования аналоговых устройств Cadence

8

Самостоятельная работа: реферат «Библиотеки элементов для схемотехнического моделирования с

проектными нормами 90 нм БиКМОП технологии»

9

Содержание учебного материала

Задание на моделирование. Список соединений. Язык SPICE

Содержание учебного материала

Симулятор Spectra

Особенности моделирования в симуляторе Spectra. Отличия от стандартного SPICE.

Содержание учебного материала

Симулятор UltraSim

Лабораторные занятия:

Схемотехническое моделирование в симуляторе Spectra

Схемотехническое моделирование в симуляторе UltraSim

Введение в САПР Cadence. Схемотехническое моделирование в Virtuoso Schematic Editor

Самостоятельная работа: реферат «Язык SPICE», «Особенности моделирования в симуляторе Spectra»

2

5

4

8

17

Всего:

51

20

3

2

2

2

3

3. УСЛОВИЯ РЕАЛИЗАЦИИ ПРОГРАММЫ УЧЕБНОЙ ДИСЦИПЛИНЫ

3.1. Требования к материально-техническому обеспечению

Реализация программы модуля предполагает наличие специализированных учебных лабораторий,

оснащенных рабочими станциями с ОС Linux: Дизайн-центра ОАО «Концерн «Созвездие» и ГОУ

ВПО «Воронежский государственный технический университет». САПР Cadence IC.

Программное и коммуникационное обеспечение: САПР Cadence IC

Рубежный контроль текущей успеваемости в виде компьютерного тестирования.

Для реализации компетентностного подхода при изучении дисциплин используются:

в лекционном курсе конспекты лекций, презентации по теме, согласно содержанию дисциплины.

в качестве самостоятельной работы специалистов подготовка, доклад и обсуждение рефератов по

тематике дисциплины, подготовка к лекциям по конспектам.

Кроме того, в рамках учебного курса предусмотрена встреча с ведущими специалистами: ОАО

«Концерн «Созвездие», ФГУП «НИИЭТ», «MicroDesign».

3.2. Информационное обеспечение обучения

Перечень рекомендуемых учебных изданий, Интернет-ресурсов, дополнительной литературы

Основные источники:

1. Virtuoso® Spectre® Circuit Simulator Reference. Cadence Design Systems

2. Virtuoso® Spectre® Circuit Simulator User Guide. Cadence Design Systems

3. Reference Manual For Generic 90nm Salicide 1.2V/2.5V 1P 9M Process Design Kit (PDK) Revision

4.5. Cadence Design Systems

4. GPDK 90 nm Mixed Signal GPDK Spec. Cadence Design Systems

5. Сафонов И.А., Сумин А.М. Моделирование аналоговых устройств. Конспект лекций. Воронеж:

Воронеж. гос. техн. ун-т, 2010.

6. Русанов А.В., Сафонов И.А., Среда проектирования аналоговых устройств Cadence.

Методические указания к лабораторной работе. Воронеж: Воронеж. гос. техн. ун-т, 2010.

7. Русанов А.В., Сумин А.М. Аналоговое моделирование в симуляторе Spectra. Методические

указания к лабораторным работам. Воронеж: Воронеж. гос. техн. ун-т, 2010.

8. Шеховцев Д.В. Аналоговое моделирование в симуляторе UlitraSim. Методические указания к

лабораторным работам. Воронеж: Воронеж. гос. техн. ун-т, 2010

Дополнительные источники:

1. Наундорв Уве. Аналоговая электроника. Основы, расчет, моделирование. Москва: Техносфера,

2008.- 472

2. Антипенский Р.В., Фадин А.Г. Схемотехническое проектирование и моделирование

радиоэлектронных устройств. Москва: Техносфера, 2007.- 128с.

21

4. КОНТРОЛЬ И ОЦЕНКА РЕЗУЛЬТАТОВ ОСВОЕНИЯ УЧЕБНОЙ ДИСЦИПЛИНЫ

Образовательное учреждение, реализующее подготовку по учебной дисциплине, обеспечивает

организацию и проведение промежуточной аттестации и текущего контроля демонстрируемых

обучающимися знаний, умений и навыков. Текущий контроль проводится преподавателем в

процессе проведения практических занятий и лабораторных работ, тестирования, а также

выполнения обучающимися индивидуальных заданий. Формы и методы текущего контроля по

учебной дисциплине самостоятельно разрабатываются образовательным учреждением и доводятся

до сведения обучающихся в начале обучения.

Для текущего контроля образовательными учреждениями создаются фонды оценочных средств

(ФОС).

ФОС включают в себя педагогические контрольно-измерительные материалы, предназначенные

для

определения

соответствия

(или

несоответствия)

индивидуальных

образовательных

достижений основным показателям результатов подготовки (таблицы).

Раздел (тема) учебной

дисциплины

№1

«Основы аналогового

моделирования»

№2

«Библиотеки и модели

элементов»

№3

«Аналоговое

моделирование»

Результаты

(освоенные умения,

усвоенные знания)

БКЗ-1

БКЗ-2.1

БКЗ-3

Основные показатели

результатов подготовки

Обоснование выбора

схемотехнического аналогового

моделирования, виды и типы

анализа

Создание модели на основе

библиотек элементов для

схемотехнического

моделирования с проектными

нормами 90 нм БиКМОП

технологии.

Выполнение схемотехнического

аналогового моделирования

(моделирование по постоянному

току, в частотной и временной

области).

СКЗ-1

БКЗ-2.1

БКУ-1

БКУ-3.1

СКЗ-2

СКУ-3

Формы и

методы

контроля

тест

тест

тест

Оценка знаний, умений и навыков по результатам текущего контроля производится в

соответствии с универсальной шкалой (таблица).

Процент

результативности

(правильных ответов)

90 ÷ 100

80 ÷ 89

70 ÷ 79

Менее 70

Качественная оценка индивидуальных

образовательных достижений

балл (отметка)

вербальный аналог

5

Отлично

4

Хорошо

3

Удовлетворительно

2

Не удовлетворительно

На этапе промежуточной аттестации по медиане качественных оценок индивидуальных

образовательных достижений экзаменационной комиссией определяется интегральная оценка

22

освоенных обучающимися профессиональных и общих компетенций как результатов освоения

профессионального модуля.

23

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПРЕПОДАВАТЕЛЯМ

Образовательные цели и ожидаемые результаты курса

Целью дисциплины является теоретическая и практическая подготовка специалистов в

области схемотехнического моделирования аналоговых интегральных схем по субмикронным

топологическим нормам по БиКМОП технологии.

Рассматриваются принципы схемотехнического аналогового моделирования, виды и типы

анализа (моделирование по постоянному току, в частотной и временной области). Изучаются

особенности моделирования аналоговых блоков в различных режимах. Проводится обзор

расширенных видов анализа, таких как спектральный анализ, анализ шумов, анализ

чувствительности. Изучаются состав, структура библиотек элементов для схемотехнического

моделирования с проектными нормами 90 нм БиКМОП технологии.

Основные задачи дисциплины состоят в:

- изучении основ аналогового моделирования интегральных схем в современных САПР;

- формировании у специалиста практического опыта разработки проектирования базовых

аналоговых устройств.

Освоение

курса

позволяет

повысить

заинтересованность,

творческий

потенциал,

профессиональный уровень и квалификацию молодых специалистов и преподавательского

состава,

обеспечить

повышение

качества

и

сокращение

сроков

автоматизированного

моделирования аналоговых устройств по субмикронным топологическим нормам, по БиКМОП

технологии.

Список обязательной и дополнительной учебной литературы по курсу

1. Mantooth A., Chaudhary V., Francis M., and Lemaitre L., Automatic Generation of Compact

Semiconductor Device Models using Paragon and ADMS // BMAS 2004 - http://www.bmas-conf.org.

2. Cadence Virtuoso Custom Design platform overview // Cadence Design Systems, Inc., 2003.

3. Wang S., An-Chang Deng. Delivering a Full-chip Hierarchical Circuit Simulation & Analysis

Solution for Nanometer Designs // White paper of Nassda Corporation, 2001.

4. Virtuoso® UltraSim Simulator User Guide, Version 6.0 // Cadence Design Systems, Inc., May

2005.

5. Денисенко В.В. Проблемы схемотехнического моделирования КМОП СБИС //

Компоненты и технологии. - 2002. - № 3. - С. 74-78.

6. Spectre® Circuit Simulator User Guide, Version 6.0 // Cadence Design Systems, Inc., November 2004.

1

7. K. Kundert. The Designer's Guide to SPICE and Spectre® // Kluwer Academic Publishers,

1995.

8. K. Kundert, O. Zinke. Designer's Guide to VERILOG-AMS // Kluwer Academic Publishers,

2004.

Лекция № 1. Тема: Понятие «моделирование». Проблемы схемотехнического моделирования.

Уделить внимание понятию «моделирование». Рассмотреть проблемы, связанные с

точностью проведения моделирования с применением существующих САПР, в связи с переходом

технологии производства ИС в субмикронную, в частности в нанометровую область. В связи с

этим, определяются задачи схемотехнического моделирования на современном этапе.

Лекция № 2. Среда проектирования аналоговых устройств. Маршрут моделирования и

проектирования аналоговых устройств Cadence IC.

Рассмотреть среду проектирования аналоговых устройств Cadence IC, уделить внимание

описанию процедур проведения анализа и моделирования аналоговых электронных устройств с

применением прикладной платформы Virtuoso Cadence IC

Лекция № 3. Принципы аналогового схемотехнического моделирования. Виды и типы

анализа.

Рассмотреть классы аналоговых электронных устройств, и основные принципы их

моделирования на каждом этапе проектирования. Рассмотреть подробно виды и типы анализа,

необходимые и применяемые на каждом этапе моделирования и разработки аналоговых

устройств.

Лекция № 4. Расширенные виды анализа.

Выделить и дать под запись общие положения математической формулировки задач

моделирования элементов БИС, детально рассмотреть процедуры

уравнений основных

физических процессов внутри структур приборов и граничных условий. Привести примеры

дополнительных видов анализа аналоговых электронных устройств в САПР Cadence.

Лекция № 5. Библиотеки элементов. Состав, структура библиотек элементов для

схемотехнического моделирования с проектными нормами 90 нм БиКМОП технологии.

Уделить внимание правилам и нормам проектирования. Объяснить назначение необходимых

технологических файлов (PS, DRC, LVS, RCX), входящих в состав библиотеки (PDK) БиКМОП

технологии 90 нм. Дать общий обзор об инструментах моделирования - «Spectre», «UltraSim»,

инструментам создания схематики и топологии аналоговых устройств, таких как ComposerSchematic и Virtuoso Layout Editor. Обсудить с аудиторией

проектирования.

Лекция № 6. Модели элементов. Их параметры.

2

примеры описания правил

Дать под запись примеры описания моделей элементов (резисторов, конденсаторов,

биполярные транзисторы,

МОП - транзисторы, источники питания и сигналов в виде spice-

параметров.

Лекция № 7. Задание на моделирование. Список соединений. Язык SPICE.

Разьяснить принципы составления задания моделирования аналоговых электронных

устройств с применением унифицированных алгоритмов языка spice, уделить внимание отдельно

расчетам режимов по постоянному току, многовариантного расчета режима по постоянному току,

расчет малосигнальных чувствительностей

Лекция № 8. Методики проектирования автоматизированных систем.

Лекция обзорная, с целью введения в принципы построения систем синтеза и моделирования

электронных устройств на современном этапе. Уделяется внимание особенностям проектирования

автоматизированных систем для анализа электронных устройств.

Процесс изучения дисциплины направлен на формирование следующих компетенций:

1) Знание

основ

теории

автоматизированного

проектирования,

модели-рования

и

характеризации УБИС топологическими нормами до 90 нм.

2) Знание методологии и маршрутов моделирования аналоговых схем и устройств

смешанного сигнала (проектирование аналоговых УБИС с топологическими нормами до 90 нм.

3) Знание теории схемотехнического и физического проектирования аналоговых СБИС с

топологическими нормами до 90 нм.

4) Навыки использования современных программных средств Cadence для ускоренного

моделирования и статистического анализа СБИС с топологическими нормами до 90 нм.

5) Умение использовать средства автоматизации проектирования цифровых, аналоговых и

устройств смешанного сигнала (проектирование аналоговых устройств.

6) Знание маршрута моделирования базовых технологических библиотек компонентов с

топологическими нормами до 90 нм для САПР компании Cadence.

7) Умение контролировать параметры разрабатываемых приборов на всех этапах маршрута

проектирования, владение методами физической характеризации и верификации УБИС с

топологическими нормами 90 нм.

3

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО САМОСТОЯТЕЛЬНОЙ РАБОТЕ СЛУШАТЕЛЕЙ

В качестве самостоятельной работы слушателей по данной дисциплине в рабочей учебной

программе предусмотрено индивидуальное выполнение десяти рефератов:

1) «Принципы аналогового моделирования»

2) «Библиотеки элементов для схемотехнического моделирования с проектными нормами 90

нм БиКМОП технологии»

3) «Язык SPICE»

4) «Параметры аналоговых устройств»

5) «Схемотехника и топологические особенности каскадов на МОП транзисторах»

6) «Коммерческие фабрики по производству ИС»

7) «Методологии и маршруты проектирования цифровых, аналоговых схем и устройств

смешанного сигнала»

8) «Технические условия ИС»

В теме «Принципы аналогового моделирования» рассмотреть проблемы, связанные с

точностью проведения моделирования с применением существующих САПР, в связи с переходом

технологии производства ИС в субмикронную, в частности в нанометровую область

В теме «Библиотеки элементов для схемотехнического моделирования с проектными

нормами 90 нм БиКМОП технологии» рассмотреть среду проектирования аналоговых устройств

Cadence IC, подробно пояснить назначение технологических норм и правил моделирования

В теме «Язык SPICE» описать историю развития языка spice, уделить внимание

особенностям устройств, реализованных с применением данного алгоритма

В теме «Параметры аналоговых устройств» материал уделяется основному классу усилителям. В связи с этим, необходимо в теме раскрыть классы, типы УУ, рассмотреть основные

параметры каждого класса и типа.

В теме «Схемотехника и топологические особенности каскадов на МОП транзисторах»

рассмотреть физику работы полевого транзистора, его строение, уделить внимание схемам

построения каскадов на МОП-транзисторах

В реферате «Коммерческие фабрики по производству ИС» описать истории развития и

совершенствования технологии производства УБИС, описать известные на сегодняшний день

фабрики по проектированию и производству УБИС (зарубежные и отечественные), детально

уделить внимание трудностям, которые существуют на этапе производства.

В теме «Методологии и маршруты проектирования цифровых, аналоговых схем и устройств

смешанного сигнала» описать базовые этапы проектирования УБИС разного типа сигналов,

указать различие и общее сходство для всех типов схем

4

В реферате «Технические условия ИС» раскрыть сам термин «технические условия»,

пояснить, что в себя включает данный термин, какими способами достигается и что необходимо

соблюдать в процессе моделирования УБИС, чтобы достичь заявленных параметров.

Методические указания слушателям

Рабочая учебная программа предусматривает по дисциплине курс из восьми лекций и

самостоятельную работу слушателей в виде рефератов. Основой для изучения дисциплины

является лекции преподавателя, конспекты лекций и образовательные ресурсы по дисциплине.

Для реализации компетентностного подхода при изучении дисциплин используются:

1) в лекционном курсе конспекты лекций, презентации по теме, согласно содержанию

дисциплины;

2) в качестве самостоятельной работы специалистов подготовка, доклад и обсуждение

рефератов по тематике дисциплины, подготовка к лекциям по конспектам;

3) в

лабораторном

практикуме

индивидуальные

задания

и

консультация

высококвалифицированных специалистов;

4) Кроме того, в рамках учебного курса предусмотрена встреча с ведущими специалистами:

ОАО «Концерн «Созвездие», ФГУП «НИИЭТ», «MicroDesign».

В курсе программы будут рассмотрены принципы схемотехнического аналогового

моделирования, виды и типы анализа (моделирование по постоянному току, в частотной и

временной области); особенности моделирования аналоговых блоков в различных режимах.

Проводится обзор расширенных видов анализа, таких как спектральный анализ, анализ шумов,

анализ

чувствительности.

Изучаются

состав,

структура

библиотек

элементов

для

схемотехнического моделирования с проектными нормами 90 нм БиКМОП технологии.

Перечень рефератов по дисциплине

По каждому из разделов дисциплины предусматриваются в качестве самостоятельной

индивидуальной работы в виде рефератов на следующие темы:

1) Принципы аналогового моделирования

2) Библиотеки элементов для схемотехнического моделирования с проектными нормами 90

нм БиКМОП технологии

3) Язык SPICE

4) Параметры аналоговых устройств

5) Схемотехника и топологические особенности каскадов на МОП транзисторах

5

6) Основы технологии производства УБИС

7) Топологические библиотеки 90 нм

8) Коммерческие фабрики по производству ИС

9) Методологии и маршрутов проектирования цифровых, аналоговых схем и устройств

смешанного сигнала

10) Технические условия ИС

Цифровые образовательные ресурсы

Весь методический материал по тематике дисциплины, включающий восемь лекций,

лабораторный практикум, тематику рефератов и рекомендации хранится в цифровом виде на

сервере кафедры и представлен в виде презентации Microsoft Office PowerPoint.

1) Mantooth A., Chaudhary V., Francis M., and Lemaitre L., Automatic Generation of Compact

Semiconductor Device Models using Paragon and ADMS // BMAS 2004 - http://www.bmas-conf.org.

2) Cadence Virtuoso Custom Design platform overview // Cadence Design Systems, Inc., 2003.

3) Wang S., An-Chang Deng. Delivering a Full-chip Hierarchical Circuit Simulation & Analysis

Solution for Nanometer Designs // White paper of Nassda Corporation, 2001.

4) Virtuoso® UltraSim Simulator User Guide, Version 6.0 // Cadence Design Systems, Inc., May

2005.

5) Денисенко В.В. Проблемы схемотехнического моделирования КМОП СБИС //

Компоненты и технологии. - 2002. - № 3. - С. 74-78.

6) Spectre® Circuit Simulator User Guide, Version 6.0 // Cadence Design Systems, Inc., November 2004.

7) K. Kundert. The Designer's Guide to SPICE and Spectre® // Kluwer Academic Publishers,

1995.

8) K. Kundert, O. Zinke. Designer's Guide to VERILOG-AMS // Kluwer Academic Publishers,

2004.

Вопросы по самопроверке

Тема № 1. Понятие «моделирование». Проблемы схемотехнического моделирования

1)

Дайте определение термину «моделирование».

2)

В чем, по вашему мнению, отличие моделирования от проектирования? Что общего в

этих понятиях?

6

3)

Какими трудностями сопровождается процесс моделирования?

4)

Назовите основные задачи моделирования

5)

С помощью каких средств осуществляется процесс моделирования?

Тема № 2. Среда проектирования аналоговых устройств. Маршрут моделирования и

проектирования аналоговых устройств Cadence IC.

Как строятся концепции моделирования проектирования аналоговых устройств при

иерархическом проектировании «сверху вниз» и «снизу вверх».

Назовите основные преимущества и отличия симуляторов для схемотехнического анализа.

Какие программы по моделированию АИС существуют на современном рынке?

Поясните

процесс

верификации

аналогового

блока

(устройства)

на

примере

поведенческой модели.

Что включает в себя процесс исследования архитектуры

В чем заключается точность построения spice-модели устройства?

Тема № 3. Принципы аналогового схемотехнического моделирования.

1) Перечислите классификации аналоговых интегральных схем.

2) Из каких этапов состоит процесс проектирования АИС. Перечислите и назовите главные

особенности

3) Назовите категории воздействий технологического процесса на схемотехническое

проектирование

4) Какие стандарты моделей ИМС применяются в проектировании?

5) Перечислите основные и дополнительные виды анализа аналоговых интегральных схем.

Какие дополнительные (необходимые) виды анализа вы знаете

6) Опишите процедуру синтеза АИС

Тема № 4. Расширенные виды анализа.

Для чего нужен анализ Фурье? Для каких сигналов он проводится?

Когда необходимо проводить дополнительные виды анализа?

В чем заключается dc-анализ на постоянном токе в окрестности рабочей точки?

Для каких целей служит анализ чувствительности?

Какой анализ позволяет определить разброс параметров (характеристик) АИС?

Тема

№

5.

Библиотеки

элементов.

Состав,

структура

библиотек

элементов

для

схемотехнического моделирования с проектными нормами 90 нм БиКМОП технологии.

1)

Что такое PDK и что он в себе содержит?

2)

Какие программные приложения позволяют провести маршрут схемотехнического и

топологического проектирования?

7

3)

Перечислите основные средства для проверки точности и верности выполнения

проектирования схемы?

4)

Что включают в себя правила проектирования DRC и LVS?

5)

В каких уровнях иерархии позволяет работать САПР Cadence

6)

Что подразумевается под понятием «инстанция»?

7)

Опишите структуру компонентов САПР Cadence

Тема № 6. Модели элементов. Их параметры.

1)

Из каких компонентов состоят параметры макромоделей элементов АИС?

2)

Сколько уровней в описании моделей АИС вам известны?

3)

Как описывается устройство ИС в spice-программе?

4)

В чем отличие моделей Гумеля - Пуна и модели Эберса - Молла для биполярного

транзистора? Что учитывается одной моделью и не учитывается другой?

5)

Какие директивы описания параметров моделей вы знаете?

Тема № 7. Задание на моделирование. Список соединений. Язык SPICE.

1)

Поясните структуру моделирования ИС в spice-программах

2)

Почему spice-алгоритм принят как наиболее универсальным для анализа АИС?

3)

Какие параметры в описании spice-моделей вам известны?

4)

Какие виды анализа возможно провести в spice-программах?

5)

Приведите пример описания алгоритма расчета параметра ИС

Тема № 8. Методики проектирования автоматизированных систем.

Какие среды проектирования УБИС вам известны

Что, по вашему мнению, лежит в основе всех систем автоматизированного проектирования

Какие модели входят в состав разработки систем САПР? Что общего в методологии

разработки САПР и моделирования системы УБИС?

Какое программное и техническое обеспечение необходимо для реализации задач

проектирования и моделирования?

Что важно знать при проектировании УБИС и систем САПР?

Какие меры по безопасности разработки УБИС необходимо предусмотреть, и что будет

являться безопасностью?

8

Конспект лекций

Лекция № 1. Понятие «моделирование». Проблемы схемотехнического моделирования

1. Понятие «моделирование»

При оценке средств моделирования обычно выделяют два основных требования производительность

и

достоверность

получаемых

результатов.

Первое

обусловлено

необходимостью проектировать все более сложные изделия в коммерчески приемлемые сроки.

Второе

-

необходимостью

безошибочного

проектирования,

поскольку

каждая

ошибка

разработчика может обойтись в сотни тысяч долларов.

Базовые математические методы и алгоритмы, используемые при автоматизации расчета

электрических схем, были разработаны сравнительно давно. Однако поиск новых подходов в этой

области идет постоянно при тесном взаимодействии разработчиков САПР и специалистов в

области

численного

моделирования.

На

ранних

этапах

развития

схемотехнического

моделирования основными критериями были экономия машинной памяти и сокращение

временных затрат.

Со временем мощности вычислительных средств выросли, а стоимость оперативной памяти

сильно упала. Однако размеры проектируемых схем также увеличились, и требования к САПР по

сути остались прежними. Но изменились приоритеты. Сегодня на первый план, несомненно,

вышла задача повышения производительности программ моделирования.

Для ее решения в основном используются две группы методов: учет структурных

особенностей проектируемых схем и использование упрощенных моделей элементов. Благодаря

учету структурных особенностей схем можно значительно повысить скорость моделирования и

снизить объем необходимой оперативной памяти, но только для отдельных специальных типов

схем, например схем памяти. Использование упрощенных моделей элементов в программах так

называемого "FastSpice" быстрого схемотехнического моделирования (NanoSim, UltraSim, HSim)

позволяет существенно сократить время моделирования, но приводит к снижению точности

получаемых результатов из-за более грубых моделей. Еще одно направление повышения

производительности моделирования - создание специализированных аппаратных вычислителей, в

которых наиболее трудоемкие вычисления реализованы на аппаратном уровне. Основная

проблема аппаратного подхода - дороговизна, отсутствие универсальности, а также быстрый рост

производительности

вычислительных

систем

общего

назначения,

в

результате

чего

специализированные аппаратные комплексы быстро устаревают. Например, с появлением

многоядерных микропроцессоров рост производительности персональных компьютеров (ПК)

начал превышать рост производительности рабочих станций.

9

При этом цена ПК в разы и даже десятки раз ниже стоимости сопоставимой по

характеристикам рабочей станции. Если алгоритмы и программное обеспечение позволяют

распараллелить процесс вычислений с учетом особенностей многоядерной архитектуры, то

производительность программ моделирования на ПК может быть существенно увеличена.

2. Задачи схемотехнического моделирования СБИС

Целью применения средств автоматизации является сокращение срока выхода на рынок и

снижение стоимости проектирования СБИС. Жесткая конкуренция фактически не оставляет

времени на исправление ошибок, допущенных на стадии проектирования и выявленных после

изготовления кристаллов.

Кроме того, переход к субмикронным технологиям увеличивает цену устранения ошибки,

поскольку возрастает стоимость изготовления пробной партии ИС. Цена одной ошибки в типовых

современных проектах составляет около 1 миллиона долларов. С другой стороны, в

потребительской электронике новые разработки становятся старыми в считанные месяцы.

Поэтому кратчайшие сроки выполнения проектов очень важны для завоевания рынка и

сохранения позиций на нем.

Для получения конкурентных преимуществ выполняется также оптимизация проекта на

схемотехническом уровне по критериям быстродействия, потребляемой мощности, надежности,

параметрического выхода годных. С расширением рынка телекоммуникационной электроники к

этим критериям добавились частота, фаза, уровень шума, искажения.

Значительное влияние на выход годных кристаллов при существенно субмикронных

технологиях (менее 0,35 мкм) оказывает технологический разброс параметров элементов схемы,

приводящий к так называемому параметрическому браку. Параметрический брак в настоящее

время превышает долю брака, возникающего по причине дефектов кремниевых пластин.

Моделирование

с

учетом

статистического

разброса

параметров

элементов

позволяет

спроектировать СБИС с максимальным процентом выхода годных кристаллов.

Размеры элементов СБИС приблизились к фундаментальным физическим пределам и

поведение

элементов

цифровых

цепей

стало

аналоговым.

В

цифровых

СБИС

стали

существенными перекрестные помехи, индуктивность и сопротивление шин питания, земли и

межсоединений, взаимные индуктивности, электромиграция атомов, паразитное потребление

мощности в статическом режиме.

При технологии 0,25 мкм только 20% задержек в БИС определяются затворами МОПтранзисторов, а 80% - межсоединениями. Для технологии 0,18 мкм задержка даже в медных

линиях связи сравнялась с задержкой в вентилях. Индуктивные паразитные связи потребовали

экранирования линий передачи на кристалле. В связи с уменьшением напряжения питания СБИС

10

до 1,2 В увеличилась относительная величина выбросов на шинах питания и земли. Таким

образом, возросло общее число параметров электрической схемы, технологический разброс

которых

может

вывести

СБИС

за

границу технологического

допуска.

Поэтому

при

проектировании СБИС уже нельзя обойтись только логическим моделированием, появилась

необходимость моделирования всей СБИС целиком на предельно детальном схемотехническом

уровне, с учетом всех паразитных элементов.

Если раньше основные затраты приходились на стадию верификации проекта, то теперь

резко возросли затраты на стадии размещения элементов, поскольку критерии размещения с

учетом паразитных связей существенно усложнили этот процесс и он стал зависеть от результатов

схемотехнической верификации СБИС. То есть с переходом в субмикронную область повысилась

актуальность схемотехнического моделирования при проектировании топологии СБИС.

Многообразие задач проектирования и невозможность создания единого средства их

решения породили целый спектр систем схемотехнического моделирования (рис.1.1). Общая

закономерность в их характеристиках состоит в том, что с ростом быстродействия программы или

предельного размера моделируемой цепи уменьшается точность и достоверность полученного

результата. Несколько необычным на рис.1.1 является указание тестового кристалла в одном ряду

со средствами моделирования, однако нужно учесть, что моделирование на компьютере является

лишь разновидностью моделирования в широком смысле этого понятия, которое включает в себя

также и физическое моделирование. При физическом моделировании соответственные величины

натуры и модели имеют одинаковую физическую природу. Поэтому транзисторы и электрические

цепи, расположенные на тестовом кристалле, можно рассматривать как физические модели

фрагментов будущей СБИС.

11

Рис.1.1. Соотношение возможностей и областей применения

средств моделирования на транзисторном уровне

Причем место тестового кристалла в начале координат связано с тем, что он является

предельно точной моделью и используется в системах моделирования в качестве эталона, для

«калибровки кремнием» средств моделирования. С другой стороны, тестовый кристалл является и

самой быстродействующей моделью.

Максимальной

схемотехнического

точностью

и

моделирования

достоверностью

(SPICE-подобные

обладают

классические

программы),

которые

программы

основаны

на

машинном составлении системы обыкновенных дифференциальных уравнений электрической

цепи и их решении без применения упрощающих предположений. В них используются численные

методы Рунге - Кутта или метод Гира для интегрирования системы дифференциальных уравнений,

метод Ньютона-Рафсона для линеаризации системы нелинейных алгебраических уравнений и

метод Гаусса или LU-разложение для решения системы линейных алгебраических уравнений.

Модификации этих методов направлены на улучшение сходимости или вычислительной

эффективности без упрощения исходной задачи. Современные программы классического

схемотехнического моделирования позволяют анализировать электрические цепи, содержащие до

50 тыс. транзисторов при использовании типовых рабочих станций проектирования СБИС.

12

3. Проблемы схемотехнического моделирования КМОП СБИС

Преодоление полупроводниковой технологией 0,18 мкм барьера привело к тому, что

поведение чисто цифровых схем стало аналоговым и появилась потребность в применении Spiceподобных программ для моделирования цепей, состоящих из миллионов и десятков миллионов

транзисторов.

Источником успехов полупроводниковой промышленности в первую очередь является сфера

проектирования полупроводниковых изделий. Крупнейшая фабрика проектирования СБИС Силиконовая Долина (США, Калифорния) не имеет на своей территории полупроводниковых

заводов, занимаясь исключительно наукоемкими разработками и проектированием. Относительно

новым явлением в полупроводниковой промышленности стало появление в начале 1990-х годов

полупроводниковых компаний, не имеющих собственных полупроводниковых заводов (Fabless

companies), которые обеспечивают полный бизнес-цикл изделия от идеи до продажи, исключая

только изготовление кристаллов, которое выполняется по контракту с кремниевыми мастерскими.

Отсутствие собственных заводов позволяет компании сосредоточить усилия на проектировании и

новых разработках.

Два последних десятилетия на рынке полупроводниковой электроники доминирующее

положение занимает КМОП-технология. Успешное применение КМОП-технологии для построения

аналоговых, в том числе радиочастотных СБИС позволило объединить на одном кристалле

разнородные функции, которые ранее выполнялись различными ИС, расположенными на печатной

плате.

При

проектировании

КМОП

СБИС

используется

функционально-логическое,

схемотехническое и физико-технологическое моделирование. На протяжении двух последних

десятилетий возможности моделирования постоянно отставали от темпов бурного развития

технологии и растущих потребностей полупроводниковой промышленности. Так, уменьшение

характерных размеров элементов СБИС на каждые 0,1 микрона приводит к появлению новых

физических эффектов в МОП-транзисторах, для учета которых необходимо создавать новые

компонентные модели. Появление новых моделей порождает новые проблемы верификации,

достоверности, точности, стандартизации, обучения. Для помощи в решении этих проблем

созданы такие организации, как совет по компонентным (компактным) моделям (Compact Model

Council - CMC), рабочая группа Американского национального института стандартов (NIST

Working Group on Model Validation), подкомитет по моделированию при Ассоциации

полупроводниковых компаний (FSA Modeling Subcommittee).

Наряду с проблемой достоверности существует проблема быстродействия средств

моделирования, которая приводит к необходимости использовать предельно упрощенные модели

транзисторов и приближенные методы моделирования электронных цепей. Используемые в

13

настоящее время модели и методы рождены в результате борьбы противоречий между точностью

и вычислительной эффективностью.

Одновременное увеличение количества транзисторов на кристалле и уменьшение их

размеров (процессор Intel Pentium 4 содержит 42 млн транзисторов и выполнен по технологии 0,18

мкм) привели к тому, что поведение цифровых элементов стало аналоговым и при разработке

даже цифровых СБИС уже нельзя обойтись только логическим моделированием. Требуется

детальный схемотехнический анализ на электрическом уровне.

Традиционный подход к моделированию МОП-транзисторов основан на математическом

моделировании с использованием элементарных алгебраических функций, обыкновенных

дифференциальных уравнений и их решению численными методами. Для получения экономичной

компонентной модели используют упрощающие допущения, которые неизбежно приводят к

потере достоверности моделирования и возрастанию неопределенности в области ее допустимого

применения. Неопределенность возрастает также при изменении технологического процесса

изготовления

СБИС.

Трудоемким

процессом

становится

верификация

(обоснование

достоверности) такой модели.

Проектирование СБИС обычно начинается с составления технического задания и

формулирования технических требований на системном уровне. После проверки реализуемости

технических

требований

выполняется

функциональный

синтез

системы,

определение

функциональных взаимосвязей между ее регистрами или аналоговыми блоками. Проектирование

на этом этапе выполняется так, чтобы обеспечить тестируемость изделия после его изготовления.

Далее выполняется разработка электрических схем или логический синтез субблоков системы, их

оптимизация, верификация и синтез топологии СБИС (размещение на кристалле и трассировка).

Схемотехническое моделирование выполняется в два этапа: до проектирования топологии и после

него. Второй этап выполняется с

учетом паразитных элементов схемы, полученных

автоматически, с помощью программ экстракции, поставляемых в комплекте с программами

схемотехнического

моделирования.

В

зависимости

от

сложности

проекта

циклы

схемотехнического моделирования и проектирования топологии могут выполняться на разных

уровнях иерархии проекта, чередуясь с этапами верификации топологии и коррекции

электрической схемы. Схемотехническое моделирование выполняется с учетом технологического

разброса параметров компонентов СБИС.

После

выполнения

последнего

этапа

верификации

топологии

изготавливается

экспериментальный образец, который тщательно тестируется и при удовлетворительных

результатах начинается серийное производство изделия.

В связи с переходом полупроводниковой технологии в нанометровую область (минимальные

размеры элементов менее 0,18 мкм) появилось множество новых электрических эффектов,

14

которые ранее наблюдались только в аналоговых схемах и которые не могут быть учтены

средствами

упрощенного

телекоммуникации,

временного

потребительской

и

анализа.

Кроме

автомобильной

того,

бурный

электроники,

а

рост

средств

также

средств

индустриальной автоматизации привел к тому, что уже в настоящее время 25% всех

проектируемых систем на кристалле (SoC) являются аналого-цифровыми и их доля к 2006 году

достигнет 70%. Логические схемы, память и аналоговые блоки, которые раньше располагались в

отдельных микросхемах на печатной плате, теперь располагаются на одном кристалле.

Верификация такой системы имеющимися средствами моделирования стала невозможной. По

этой причине резко возросла актуальность точного схемотехнического (SPICE-подобного)

моделирования, которое еще 5-10 лет назад использовалось исключительно для моделирования

аналоговых цепей или небольших фрагментов цифровых БИС.

Лекция № 2. Среда проектирования аналоговых устройств. Маршрут моделирования

и проектирования аналоговых устройств Cadence IC

1. Среда проектирования аналоговых устройств

«Cadence» - система автоматизированного проектирования (САПР), которая позволяет в

единственной программной оболочке проводить моделирование и разработку интегральных схем

(ИС) в едином технологическом базисе.

Классические программы моделирования аналоговых электронных схем, такие как Spice,

Spectre и другие, обеспечивают хорошую сходимость решения в большинстве случаев и

гарантируют достаточную точность. Однако, постоянный рост сложности и объемов проектов

БИС привел к увеличению размеров схем до десятков и сотен миллионов узлов. Как следствие,

производительность классических программ моделирования, построенных на традиционном

подходе составления и решения системы ОДУ с применением методов разреженных матриц, стала

явно недостаточной для решения системы уравнений, описывающей всю схему.

Подходы, применявшиеся несколько лет назад, состоят в расчете фрагментов схем, базовых

ячеек или в комбинированном применении логических и временных расчетов совместно с

моделированием аналоговых фрагментов схем на уровне транзисторов. Широкое распространение

нашло также макромоделирование.

В последние годы, интенсивно начали развиваться программы моделирования нового

поколения, так называемые «быстрые симуляторы» [3-5]. Их применение дает качественный

скачок в производительности. Появилась возможность моделировать БИС объемом в десятки и

сотни миллионов узлов с точностью и требованиями к вычислительным ресурсам, близкими к

традиционным программам моделирования (рис.2.1).

15

Рис.2.1. Возможности систем моделирования различных поколений

Решение, предлагаемое Cadence на данном сегменте рынка, - платформа Virtuoso и система

FastSPICE Ultrasim. Наряду с известными системами моделирования, Ultrasim интегрирован в

общую среду разработки Virtuoso и дает возможность быстро получить решение с приемлемой

точностью при возрастании сложности проекта на несколько порядков.

2) Постановка задачи и платформа Cadence Virtuoso как метод решения

Технические требования к аналоговым, заказным цифровым, радиотехническим и

смешанным проектам росли экспоненциально в последнее десятилетие (рис.2.2). Экономические

факторы и конкуренция на рынке электроники вынуждают разработчиков применять новые

технологии и объединять прежде независимые блоки на одном кристалле (System-On-Chip, SOC).

Многие производители переходят на современные технологии проектирования по нормам 0.13

мкм - 65 нм, и совмещают аналоговое проектирование, с нанометровыми цифровыми дизайнами.

Более того, основой цифрового проектирования является использование библиотек стандартных и

специализированных заказных блоков, разрабатываемых с применением средств аналогового

моделирования.

Рис.2.2. Взаимосвязь технологии, сложности и стоимости проекта

В зависимости от сложности и объема решаемых задач, Vittuoso ADE (Analog Design

Environment) (рис.2.3) может интегрировать различные системы аналогового моделирования

(Spice, Spectre, UltraSim, Multi-mode Simulation), обепечивать обратную аннотацию паразитных

16

параметров, экстрагируемых с помощью Assura RC, поддерживать кросс-пробинг между схемным

вводом (Virtuoso Schematic Editor), топологическим редактором (Virtuoso Layout Editor) и

системой анализа результатов моделирования.

Рис.2.3. Основные компоненты среды проектирования Virtuoso ADE

Платформа Virtuoso может работать с базой данных Cadence CDBA или с базой OpenAccess.

С этой платформой, возможно быстрое проектирование с высоким выходом годных для геометрий

от 1 мкм до 90 нм и менее.

3. Маршрут моделирования аналоговых устройств

Важную роль при проведении моделирования физических процессов, протекающих в

аппаратуре, играет его правильный порядок. Он определяется с одной стороны логикой

проектирования аппаратуры, а с другой взаимосвязью моделей физических процессов между

собой.

Порядок проведения тех или иных работ в процессе автоматизированного проектирования

регламентируется соответствующими методиками. На рис.2.4 представлена схема алгоритма

методики моделирования РЭС.

Предлагаемая методика включает базовый набор работ, которые необходимо провести при

проектировании любой аппаратуры и, по сути, является типовой. Однако при проектировании

конкретных классов РЭС в эту методику могут быть добавлены дополнительные работы,

отражающие специфику аппаратуры или исключены имеющиеся. Может быть изменен и порядок

проведения работ, однако, с условием ненарушения взаимосвязи моделей физических процессов.

В предложенной методике взаимосвязь моделей физических процессов отражается в

дублировании

некоторых

работ,

например,

моделировании

электрических

процессов

и

исследовании разбросов. При моделировании электрических процессов и исследовании разбросов

в первый раз, нам не известны температуры радиоэлементов, поэтому учесть их нет возможности

и они задаются равными 25 градусам Цельсия.

17

Рис.2.4. Схема алгоритма методики моделирования РЭС

Возникает вопрос. Имеет ли смысл эти работы проводить здесь? Практика проектирования

показывает, что имеет, поскольку результаты этих работ, во-первых, позволяют правильно

сравнить полученные результаты моделирования с требованиями ТЗ, а во-вторых, грамотно

сформулировать требования к конструкции. Второй раз моделирование электрических процессов

и исследование разбросов проводится после разработки конструкции и моделирования тепловых

процессов конструкции, поэтому температуры радиоэлементов становятся известными и

появляется возможность их учесть.

Итогом выполнения работ является исследование надежности аппаратуры, которое

интегрирует результаты всех работ и позволяет дать оценку качества разработанной схемы и

конструкции.

18

4. Маршрут проектирования аналоговых устройств

Маршрут проектирования аналоговых устройств заключается в определении состава

функциональных модулей входящих в состав ИМС на основе требований, определяемых

предварительной спецификацией.

Важное замечание. Формально этот уровень не привязан к технологическому процессу, так

как при разбиении алгоритма на реализующие его функции мы можем на первом этапе

игнорировать ограничения, накладываемые физической реализацией ИМС.

Однако в связи с тем, что параметры технологического процесса могут оказать серьезное

влияние на архитектуру ИМС исследования на уровне архитектуры по обоим направлениям алгоритмическому и технологическому ведутся параллельно (рис.2.5).

Рис.2.5. Моделирование на системном уровне

Задача системного моделирования - подтвердить правильность выбранного алгоритма для

решения задачи. Эта задача решается с помощью программно-аппаратных средств, используя

описательные модели, выполненные на языках высокого уровня: SystemC, SystemVerilog, Verilog,

VerilogA, VerilogAMS и др. или формально на уровне математических формул. Создается

высокоуровневая поведенческая модель всей разрабатываемой системы. Она, как правило,

строится в виде блок-схемы. Для верификации разработанной поведенческой модели создается

тестовый испытательный стенд (тестовое окружение) системы (Testbench), которое включает в

себя генераторы входных сигналов, тестовые последовательности блоки отображения выходной

информации, нагрузку. Тестовое окружение должно максимально полно проверять работу

системы. Впоследствии на основе этого тестового окружения будут разрабатываться тестовые

векторы для верификации проекта на нижних уровнях проектирования и для тестирования

опытных образцов СБИС.

Поведенческая модель верифицируется путем компьютерного моделирования. Если в

процессе верификации обнаруживаются какие-либо отклонения от требований системной

спецификации, то модель корректируется и моделирование повторяется. Кроме верификации, на

данном шаге можно выбрать оптимальные параметры алгоритма системы. Например, разработчик

может найти компромисс между вычислительной сложностью и точностью.

Исследование архитектуры включает в себя анализ состояния проблемы на сегодняшний

день для правильного выбора архитектуры соответствующей выбранному технологическому

процессу. Анализ должен проходить по трем направлениям:

19

ИМС, выполняющие такую же функцию (если существуют) и имеющие спецификацию

(ТУ);

перспективные разработки;

патентные исследования;

Задачи, решаемые этими направлениями (рис.2.6)

Рис.2.6. Алгоритм исследования на уровне архитектуры

Спецификация модулей полученная с использование моделирования на системном уровне и

исследования и выбора архитектуры позволяет разработать схемы модулей, используя тот же

подход, что и на системном (функциональном) уровне. Основное отличие - вместо

идеализированных

представлений

модулей

необходимо

использовать

схемотехническое

представление элементов интегральной схемы, имеющихся в данном технологическим процессом.

Перед проведением этого этапа необходимо тщательно проанализировать документацию,

предоставленную

обладателем

технологического

характеризующим

технологический

процесс

процесса.

является

Основным

спецификация

документом,

процесса,

которая

определяет:

Набор элементов, доступных в технологическом процессе и их базовые характеристики;

ограничения, накладываемые на использование этих приборов;

физические характеристики слоев формирующих устройства, которые определяют