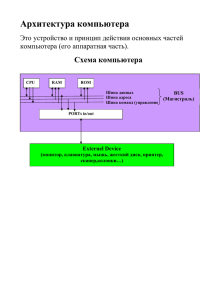

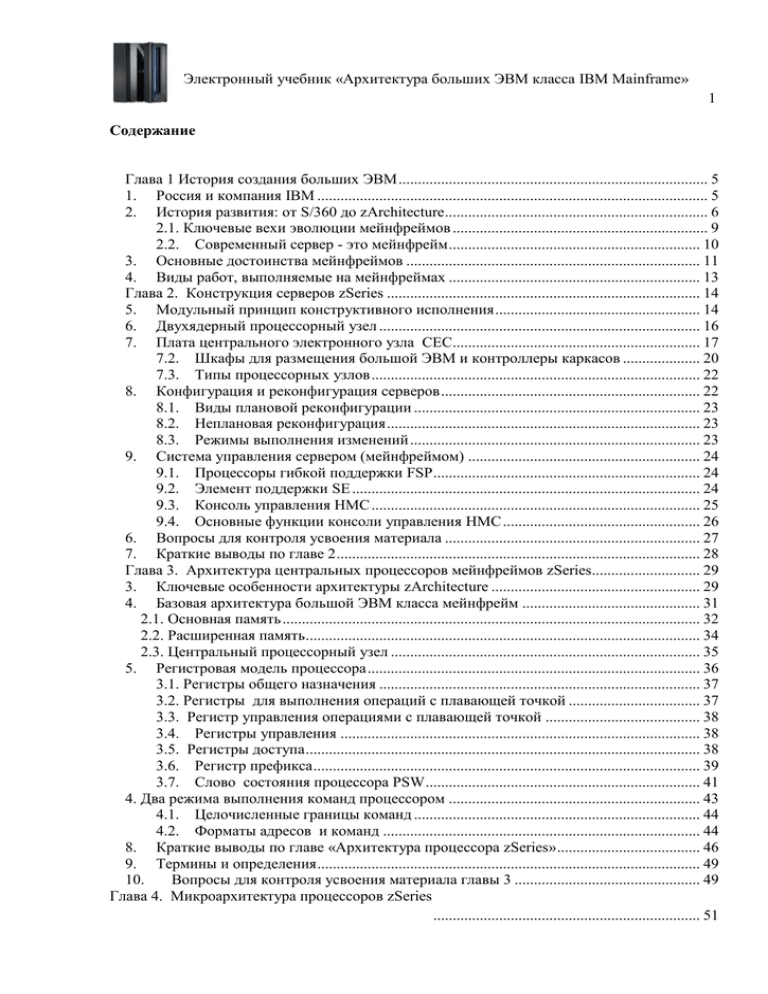

Архитектура больших ЭВМ Файл

реклама