Интерфейс последовательной передачи блоков данных

реклама

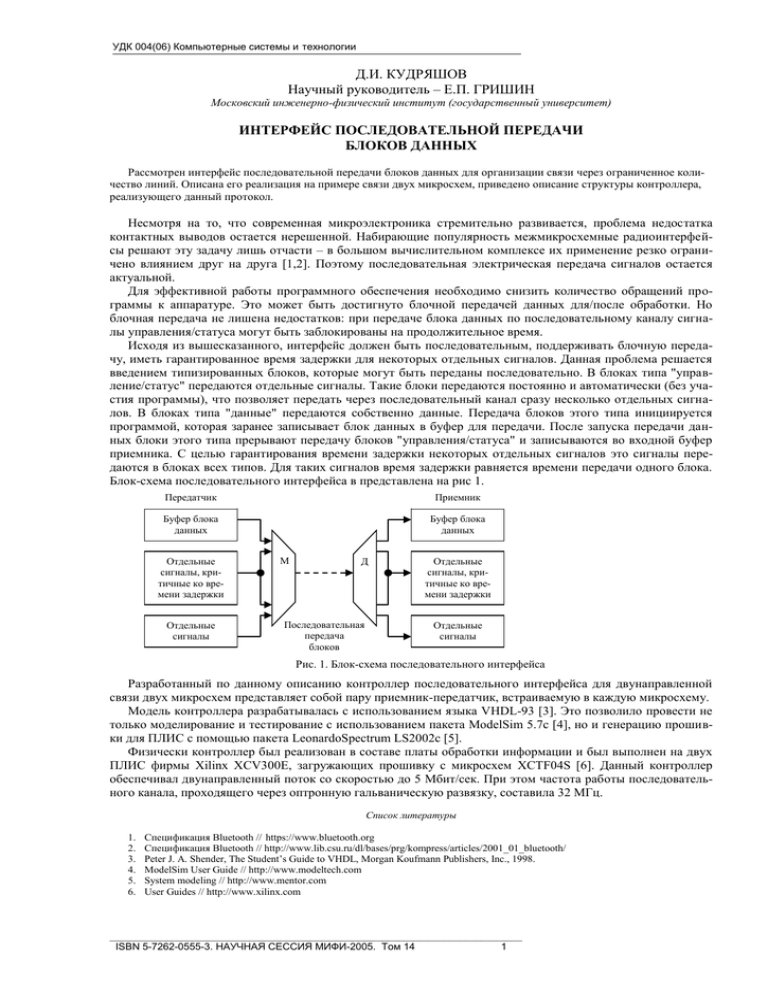

УДК 004(06) Компьютерные системы и технологии Д.И. КУДРЯШОВ Научный руководитель – Е.П. ГРИШИН Московский инженерно-физический институт (государственный университет) ИНТЕРФЕЙС ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ БЛОКОВ ДАННЫХ Рассмотрен интерфейс последовательной передачи блоков данных для организации связи через ограниченное количество линий. Описана его реализация на примере связи двух микросхем, приведено описание структуры контроллера, реализующего данный протокол. Несмотря на то, что современная микроэлектроника стремительно развивается, проблема недостатка контактных выводов остается нерешенной. Набирающие популярность межмикросхемные радиоинтерфейсы решают эту задачу лишь отчасти – в большом вычислительном комплексе их применение резко ограничено влиянием друг на друга [1,2]. Поэтому последовательная электрическая передача сигналов остается актуальной. Для эффективной работы программного обеспечения необходимо снизить количество обращений программы к аппаратуре. Это может быть достигнуто блочной передачей данных для/после обработки. Но блочная передача не лишена недостатков: при передаче блока данных по последовательному каналу сигналы управления/статуса могут быть заблокированы на продолжительное время. Исходя из вышесказанного, интерфейс должен быть последовательным, поддерживать блочную передачу, иметь гарантированное время задержки для некоторых отдельных сигналов. Данная проблема решается введением типизированных блоков, которые могут быть переданы последовательно. В блоках типа "управление/статус" передаются отдельные сигналы. Такие блоки передаются постоянно и автоматически (без участия программы), что позволяет передать через последовательный канал сразу несколько отдельных сигналов. В блоках типа "данные" передаются собственно данные. Передача блоков этого типа инициируется программой, которая заранее записывает блок данных в буфер для передачи. После запуска передачи данных блоки этого типа прерывают передачу блоков "управления/статуса" и записываются во входной буфер приемника. С целью гарантирования времени задержки некоторых отдельных сигналов это сигналы передаются в блоках всех типов. Для таких сигналов время задержки равняется времени передачи одного блока. Блок-схема последовательного интерфейса в представлена на рис 1. Передатчик Приемник Буфер блока данных Буфер блока данных Отдельные сигналы, критичные ко времени задержки Отдельные сигналы М Д Последовательная передача блоков Отдельные сигналы, критичные ко времени задержки Отдельные сигналы Рис. 1. Блок-схема последовательного интерфейса Разработанный по данному описанию контроллер последовательного интерфейса для двунаправленной связи двух микросхем представляет собой пару приемник-передатчик, встраиваемую в каждую микросхему. Модель контроллера разрабатывалась с использованием языка VHDL-93 [3]. Это позволило провести не только моделирование и тестирование с использованием пакета ModelSim 5.7с [4], но и генерацию прошивки для ПЛИС с помощью пакета LeonardoSpectrum LS2002c [5]. Физически контроллер был реализован в составе платы обработки информации и был выполнен на двух ПЛИС фирмы Xilinx XCV300E, загружающих прошивку с микросхем XCTF04S [6]. Данный контроллер обеспечивал двунаправленный поток со скоростью до 5 Мбит/сек. При этом частота работы последовательного канала, проходящего через оптронную гальваническую развязку, составила 32 МГц. Список литературы 1. 2. 3. 4. 5. 6. Спецификация Bluetooth // https://www.bluetooth.org Спецификация Bluetooth // http://www.lib.csu.ru/dl/bases/prg/kompress/articles/2001_01_bluetooth/ Peter J. A. Shender, The Student’s Guide to VHDL, Morgan Koufmann Publishers, Inc., 1998. ModelSim User Guide // http://www.modeltech.com System modeling // http://www.mentor.com User Guides // http://www.xilinx.com ________________________________________________________________________________ ISBN 5-7262-0555-3. НАУЧНАЯ СЕССИЯ МИФИ-2005. Том 14 1