Гибридная нейронномикропроцессорная система обработки

advertisement

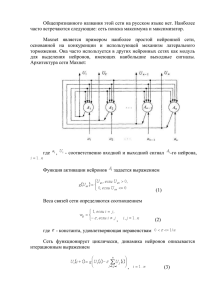

Гибридная нейронномикропроцессорная система обработки информации. Большие перспективы развития нейронных систем по выполнению анализа образов и нечеткой информации требуют создания в настощее время гибридных систем на базе их и современных вычислительных систем. В данном варианте по моему мнению функции нейронных систем будут аналогичны функциям сопроцессоров, т.е. основные функции координации и управления возьмет на себя микропроцессорная или цифровая часть системы, хотя на определенном этапе развития для нее могут быть оставлены только вспомогательные и контрольные задачи. Предлагается в любую стандартную цифровую вычислительную систему, в том числе и в систему с разделяемой распределенной памятью, ввести один или несколько блоков нейронных матриц с полным доступом со стороны цифровой части ко всем ее внутренним параметрам. Входы и выходы матрицы при этом будут являться входами и выходами всей системы полностью. Понятие полный доступ означает,что все внутренние параметры нейронов (веса синапсов и т.д.), значения величин в цепях внутренних и внешних связей, а так же входные и выходные сигналы матрицы могут быть считаны и принудительно изменены цифровой частью,как содержимое ячеек памяти или регистров устройств ввода/вывода. Сама архитектура системы может иметь произвольный вид, в частности,как показано на фиг.1,2.На фиг.1 изображена структурная схема системы со стандартной архитектурой с разделяемой памятью и одной нейронной матрицей, на фиг.2 - сегмент системы с разделяемой распределенной памятью с несколькими нейронными матрицами, подключенными к разным системным магистралям, на фиг.3 - к системным магистралям локальных блоков устройств ввода/вывода и памяти, на фиг.4 - внутренняя структура блока нейронной матрицы. 1 - устройства обработки информации; 2 - блоки устройств ввода/вывода и памяти; 3 - магистрали адреса/данных/управления или системные магистрали; 4 - блоки нейронных матриц; 5 - входные сигналы нейронной матрицы 4; 6 - выходные сигналы нейронной матрицы 4; 7 - объединенные магистрали сигналов 5 и 6; 8 - магистрали межматричных связей; 9 - блок интерфейса системной магистрали 3; 10 - порты ввода/вывода (обращение к ним может производиться и как к памяти); 11 - нейронная матрица в "чистом" виде; 12 - распределительные блоки, в которых реализованы средства коммутации входных и выходных сигналов и просто их отключение; 13 - внутренняя магистраль адреса/данных/управления блока 4, по ней в частности обеспечивается доступ к внутренним весам нейронов блока 11 и прочим их управляющим параметрам как к ячейкам памяти или регистрам устройств ввода/вывода; 14 - входные сигналы нейронов матрицы 11; 15 - выходные сигналы нейронов матрицы 11; 16 - входные/выходные сигналы нейронов матрицы 11 для других блоков 4; Так как на данный момент времени уже наблюдается широкое разнообразие в конструкциях нейронов и их матриц, а так же, так 2 как по моему мнению в нейронных матрицах допускается широкая свобода при определении входных и выходных сигналов нейронов, причем их функции могут меняться в процессе обучения, то разделение их сигналов и распределительных блоков по функциям в принципе является бесполезным. В данных системах возможны следующие режимы работы: 1. Автоматическая тренировка или обучение матрицы 4 или их группы.В этом случае цифровая часть системы(маг.3,блоки 1,2) моделирует необходимую для тренировки ситуацию и выставляет соответствующие ей сигналы 14 в блоке или блоках 12.1, после чего контролирует процесс тренировки и прочее и,возможно,корректирует его,принудительно изменяя параметры нейронов. После достижения необходимого результата внутренние параметры нейронов или "программа" блока или блоков 11 запоминаются в базу данных, архив и т.д. для долговременного хранения. 2. Режим работы системы,как нейронной матрицы.В этом случае цифровая часть загружает в матрицу или матрицы 4 необходимую "программу" и возможно, контролирует и корректирует последующий процесс.Основные функции системы выполняет нейронная матрица. 3. Режим работы системы,как стандартной цифровой. 4. Комбинированный.В этом случае возможны два варианта: 4.1. С ведущей ролью цифровой части. На нейронную матрицу возлагаются функции сопроцессора, т.е. матрица используется для выполнения операций нечеткого сравнения,анализа и т.д.,реализация которых на цифровых системах требует больших ресурсов. 4.2. С ведущей ролью нейронной части. В этом случае в нейронную часть загружается одна или группа "программ" и по результатам их работы цифровая часть замещает участки этой "программы", одновременно контролируя систему и корректируя выходные сигналы,чтобы исключить переходные процессы. В патентных бюллетенях за 1995 год уже была опубликована информация о системе,предназначенной для работы в первом режиме на основе стандартной архитектуры,которую можно взять в качестве прототипа. Данная статья с рисунками была заверена мной у нотариуса (наподобие депонента) в августе 1996 года.