Маршрут проектирования цифровых интегральных схем в

реклама

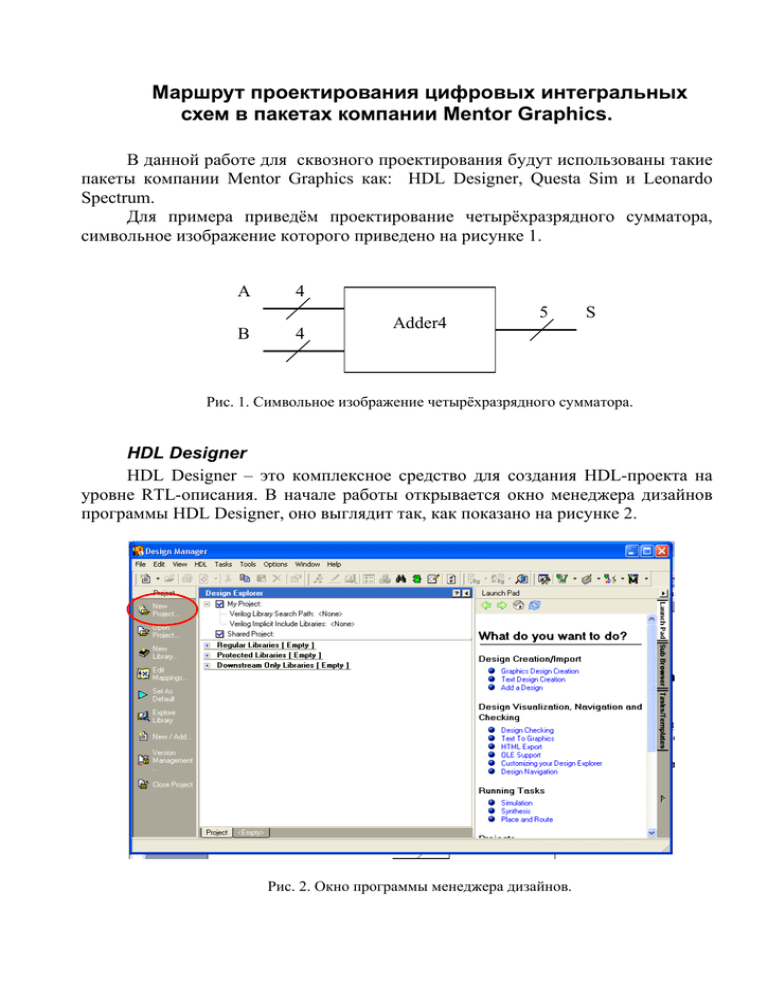

Маршрут проектирования цифровых интегральных схем в пакетах компании Mentor Graphics. В данной работе для сквозного проектирования будут использованы такие пакеты компании Mentor Graphics как: HDL Designer, Questa Sim и Leonardo Spectrum. Для примера приведём проектирование четырёхразрядного сумматора, символьное изображение которого приведено на рисунке 1. A B 4 4 Adder4 5 S Рис. 1. Символьное изображение четырёхразрядного сумматора. HDL Designer HDL Designer – это комплексное средство для создания HDL-проекта на уровне RTL-описания. В начале работы открывается окно менеджера дизайнов программы HDL Designer, оно выглядит так, как показано на рисунке 2. Рис. 2. Окно программы менеджера дизайнов. Для создания нового проекта необходимо кликнуть по значку NewProject в левой части окна менеджера дизайнов (рис.2), либо выполнить последовательность действий: File/New/Project… После этого на экране появится окно, изображённое на рисунке 3, в котором следует указать имя проекта, имя основной рабочей библиотеки и место размещения проекта на компьютере (рабочая директория). Рис. 3. Окно создания проекта. В окне Project Content выбираем строку Create new design files. Далее будет предложен набор возможных типов ввода создаваемой схемы: графический, табличный, с помощью диаграмм состояний, текстовый и т.д (рис. 4). В нашем случае выберем способ ввода с помощью языка VHDL. В поле File Types выбираем строку Combined. Рис. 4. Выбор типа исходного файла. В следующем окне (рис. 5) необходимо выбрать библиотеку, в которую будет добавляться создаваемый файл, имена Entyti и Architecture, а также имя файла. После нажатия кнопки Finish Автоматически откроется окно текстового редактора (рис. 7) с заготовками Entyti и Architecture, а в окне менеджера проектов появятся страницы проекта, содержащая списки используемых и стандартных библиотек и открытой рабочей библиотеки, которая содержит список всех объектов содержащихся в библиотеке (рис. 6) Рис.5. Окно текстового редактора. Рис. 6. Содержание созданной библиотеки. Для проектирования 4-х разрядного сумматора создадим ещё два файла один текстовый, для описания полного одноразрядного сумматора и полусумматора, для описания которой воспользуемся редактором блок-диаграмм (рис. 7). Для сборки схемы полусумматора использованы элементы управления указанные на рисунке 7. Вставка портов ввода/вывода Вставка соединительных линий Вставка компонента схемы Рис.7. Окно схемотехнического редактора. Текст реализации полного одноразрядного сумматора приведён в листинге 1. LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; Листинг 1 ENTITY FullAdder IS port( A : in STD_LOGIC; B : in STD_LOGIC; C : in STD_LOGIC; S : out STD_LOGIC; C_out : out STD_LOGIC ); END ENTITY FullAdder; -ARCHITECTURE FullAdder_1 OF FullAdder IS BEGIN S<=(A and B and C)or(A and (not B) and (not C))or((not A) and (not B) and C)or((not A) and B and (not C)); C_out<=(A and B)or(A and C)or(C and B); END ARCHITECTURE FullAdder_1; Четырёхразрядный сумматор состоит из одного полусумматора и трёх полных сумматоров. Текстовая реализация четырёхразрядного сумматора представлена в листинге 2. LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; Листинг 2 ENTITY Adder4 IS port(A: in std_logic_vector (3 downto 0); B: in std_logic_vector (3 downto 0); S: out std_logic_vector (4 downto 0)); END ENTITY Adder4; LIBRARY Adder4_lib; ARCHITECTURE Adder4_1 OF Adder4 IS component HalfAdder is port(A: in std_logic; B: in std_logic; C: out std_logic; S: out std_logic); end component; component FullAdder is port(A: in std_logic; B: in std_logic; C: in std_logic; S: out std_logic; C_out: out std_logic); end component; Signal C: std_logic_vector (2 downto 0); BEGIN add1: HalfAdder port map (A(0),B(0),C(0),S(0)); add2: FullAdder port map (A(1),B(1),C(0),S(1),C(1)); add3: FullAdder port map (A(2),B(2),C(1),S(2),C(2)); add4: FullAdder port map (A(3),B(3),C(2),S(3),S(4)); END ARCHITECTURE Adder4_1; Если после проверки верхнего компонента (значок Check на левой панели) ошибок не оказалось, то можно приступать к симуляции. Для симуляции всей схемы четырёхразрядного сумматора необходимо параметр Model Sim Flow установить в значение Through Components (рис. 8), иначе программа не будет воспринимать файлы компонентов и выдаст ошибку. Рис. 8. Выбор потока симуляции. Для запуска симуляции нужно выбрать верхний компонент иерархии и щёлкнуть по значку Simulate на левой панели менеджера дизайнов. На окне Start ModelSim нажмите кнопку OK. Questa Sim Questa Sim – это система моделирования и средства верификации. После того, как откроется окно программы QuestaSim нужно задать сигналы для входных портов. Для этого нужно кликнуть правой кнопкой мыши по нужному порту в окне Objects и в появившемся окне команд выбрать пункт Create wave, как показано на рисунке 9. Рис. 8. Задание сигнала для входного порта. Для примера наиболее подходящим будет выбрать изменение сигнала в виде счётчика, для этого в окне Create Pattern Wizard поставим отметку напротив слова Counter и зададим параметры Start Time = 0, End Time =10000, Time Unit = ns. В следующем окне настроек параметры установим следующим образом: Start Value = 0000, End Value = 1111, Time Period = 500, Time Units = ns, Counter Type = Range, Count Direction = Up и Step Count = 1. Установим сигналы входов ‘A’ и ‘B’ аналогично друг другу. Для удобства анализа можно выводить значения сигналов на диаграммах в десятичной форме, для этого в окне Wave щёлкнув правой кнопкой мыши по нужному сигналу и выбрать строки Radix/Unsigned. Изменив для удобства масштаб, временные диаграммы будут выглядеть так, как показано на рисунке 9. Рис. 9. Временные диаграммы входных сигналов. Теперь перетащив выходной сигнал на окно временных диаграмм, можно запускать симуляцию. Для чего на верхней панели устанавливаем длительность симуляции и жмём на кнопку Run. Если всё сделано правильно, то на временной диаграмме появится выходной сигнал ‘S’ (рис.10). Рис. 10. Временные диаграммы работы четырёхразрядного сумматора. Для тестирования однотипных схем в программе QuestaSim есть возможность сохранять файл управления в формате *.do и файл VHDL TestBench в формате *.vhd. Для сохранения файла VHDL TestBench нужно проследовать по пути File/Export…/Waveform… и в открывшемся окне выбрать нужный формат файла и имя. Для сохранения файла *.do нужно проследовать по пути File/Save Format…, после чего появится окно предлагающее сохранить файл управления в рабочей директории. Также есть возможность сравнения полученных временных диаграмм с полученными ранее. Для этого нужно запустить инструмент Tools/WaveForm/Comparison Wizard. После чего начнут открываться окна в которых следует указать файл *.wlf (файл временных диаграмм с которыми необходимо сравнить полученные диаграммы) и комбинацию отображаемых сигналов. По завершении работы мастера сравнения на экране диаграмм появится картинка подобная рисунку 11. Подтверждение совпадения Рис. 11. Результаты сравнения временных диаграмм. Leonardo Spectrum Leonardo Spectrum – это средство логического синтеза интегральных схем. Для запуска средств синтеза нужно в окне менеджера проектов кликнуть по значку Synthesize с левой стороны. После этого появится окно, в котором нужно указать библиотеку используемых элементов, либо тип ПЛИС, параметры оптимизации и т.д., и нажать кнопку OK. В запустившемся окне Leonardo Pectrum, для просмотра синтезированной схемы нужно нажать на соответствующий значок панели инструментов (рис. 12). Если схема относительно сложная, то программа разделит схему по страницам. Чтобы просмотреть схему целиком нужно щёлкнуть по открытой странице правой кнопкой мыши и убрать галочку со строки MultiPage Schematics. Сохранение схемы возможно в форматах EDIF, VHDL и т.д. Оно производится на вкладке Output кнопкой Write, предварительно установив нужный формат сохраняемого файла Сохранение схемы возможно в форматах EDIF, VHDL и т.д. Оно производится на вкладке Output кнопкой Write, предварительно установив нужный формат сохраняемого файла Открытие схемы на библиотечных элементах Выбор формата сохраняемого файла Сохранение файла Рис. 12. Рабочее окно Leonardo Spectrum. .