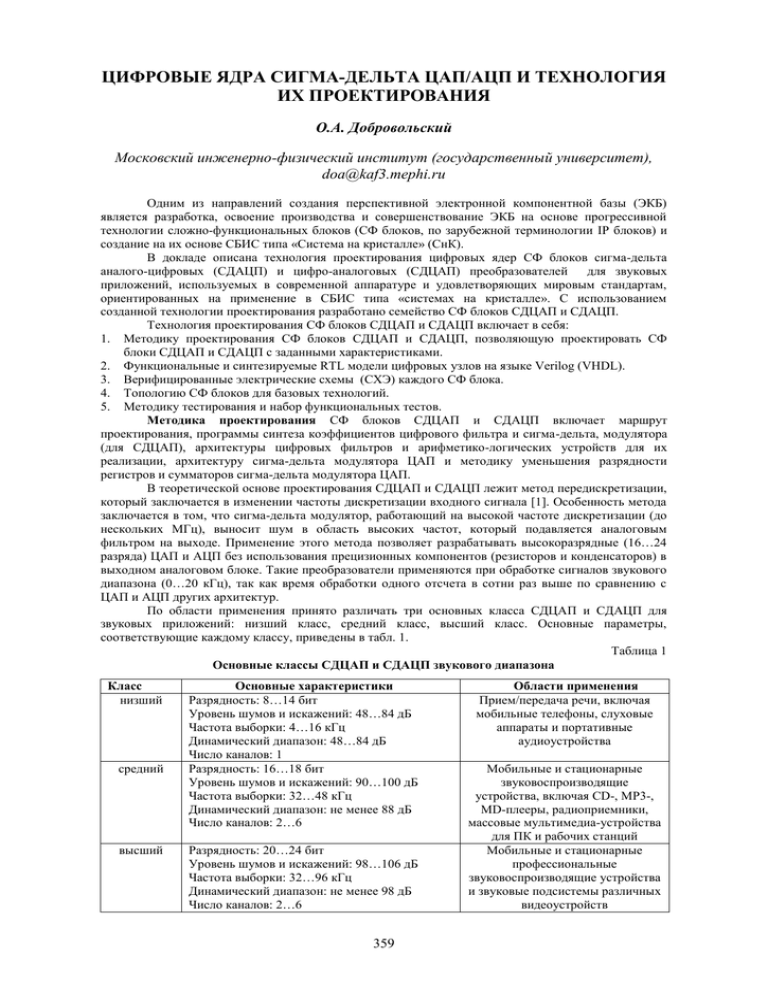

Размер топологии разработанных СФ блоков

реклама

ЦИФРОВЫЕ ЯДРА СИГМА-ДЕЛЬТА ЦАП/АЦП И ТЕХНОЛОГИЯ ИХ ПРОЕКТИРОВАНИЯ О.А. Добровольский Московский инженерно-физический институт (государственный университет), [email protected] Одним из направлений создания перспективной электронной компонентной базы (ЭКБ) является разработка, освоение производства и совершенствование ЭКБ на основе прогрессивной технологии сложно-функциональных блоков (СФ блоков, по зарубежной терминологии IP блоков) и создание на их основе СБИС типа «Система на кристалле» (СнК). В докладе описана технология проектирования цифровых ядер СФ блоков сигма-дельта аналого-цифровых (СДАЦП) и цифро-аналоговых (СДЦАП) преобразователей для звуковых приложений, используемых в современной аппаратуре и удовлетворяющих мировым стандартам, ориентированных на применение в СБИС типа «системах на кристалле». С использованием созданной технологии проектирования разработано семейство СФ блоков СДЦАП и СДАЦП. Технология проектирования СФ блоков СДЦАП и СДАЦП включает в себя: 1. Методику проектирования СФ блоков СДЦАП и СДАЦП, позволяющую проектировать СФ блоки СДЦАП и СДАЦП с заданными характеристиками. 2. Функциональные и синтезируемые RTL модели цифровых узлов на языке Verilog (VHDL). 3. Верифицированные электрические схемы (СХЭ) каждого СФ блока. 4. Топологию СФ блоков для базовых технологий. 5. Методику тестирования и набор функциональных тестов. Методика проектирования СФ блоков СДЦАП и СДАЦП включает маршрут проектирования, программы синтеза коэффициентов цифрового фильтра и сигма-дельта, модулятора (для СДЦАП), архитектуры цифровых фильтров и арифметико-логических устройств для их реализации, архитектуру сигма-дельта модулятора ЦАП и методику уменьшения разрядности регистров и сумматоров сигма-дельта модулятора ЦАП. В теоретической основе проектирования СДЦАП и СДАЦП лежит метод передискретизации, который заключается в изменении частоты дискретизации входного сигнала [1]. Особенность метода заключается в том, что сигма-дельта модулятор, работающий на высокой частоте дискретизации (до нескольких МГц), выносит шум в область высоких частот, который подавляется аналоговым фильтром на выходе. Применение этого метода позволяет разрабатывать высокоразрядные (16…24 разряда) ЦАП и АЦП без использования прецизионных компонентов (резисторов и конденсаторов) в выходном аналоговом блоке. Такие преобразователи применяются при обработке сигналов звукового диапазона (0…20 кГц), так как время обработки одного отсчета в сотни раз выше по сравнению с ЦАП и АЦП других архитектур. По области применения принято различать три основных класса СДЦАП и СДАЦП для звуковых приложений: низший класс, средний класс, высший класс. Основные параметры, соответствующие каждому классу, приведены в табл. 1. Таблица 1 Основные классы СДЦАП и СДАЦП звукового диапазона Класс низший средний высший Основные характеристики Разрядность: 8…14 бит Уровень шумов и искажений: 48…84 дБ Частота выборки: 4…16 кГц Динамический диапазон: 48…84 дБ Число каналов: 1 Разрядность: 16…18 бит Уровень шумов и искажений: 90…100 дБ Частота выборки: 32…48 кГц Динамический диапазон: не менее 88 дБ Число каналов: 2…6 Разрядность: 20…24 бит Уровень шумов и искажений: 98…106 дБ Частота выборки: 32…96 кГц Динамический диапазон: не менее 98 дБ Число каналов: 2…6 359 Области применения Прием/передача речи, включая мобильные телефоны, слуховые аппараты и портативные аудиоустройства Мобильные и стационарные звуковоспроизводящие устройства, включая CD-, MP3-, MD-плееры, радиоприемники, массовые мультимедиа-устройства для ПК и рабочих станций Мобильные и стационарные профессиональные звуковоспроизводящие устройства и звуковые подсистемы различных видеоустройств СФ блоки СДЦАП для звуковых приложений представляют собой стерео- или монопреобразователи входного цифрового потока данных в аналоговый сигнал. Цифровое ядро СДЦАП звукового диапазона включает в себя блоки цифрового фильтра и сигма-дельта модулятора, блок ввода данных. Это основные составляющие СФ блоков, которые определяют их основные характеристики. Основные функции СДЦАП различных классов: преобразование цифрового потока данных в выходной аналоговый стерео или моно сигнал; программное подавление входного сигнала (soft mute); цифровое ослабление входного сигнала (digital attenuation); цифровая коррекция предыскажений (de-emphasis) (только для среднего и высшего классов); микширование сигналов (кроме низшего класса); Основные количественные характеристики СДЦАП: поддержка 8, 16, 18, 20, 24 разрядных входных данных с частотой дискретизации fs = 8 кГц, 16 кГц, 32 кГц, 44,1 кГц, 48 кГц, 96кГц, 192 кГц; выходной сигнал – стерео, моно; коэффициент нелинейных искажений (КНИ) – (0.0001…0,4)%; отношение сигнал/шум (SNR) – (48…106) дБ; рабочая полоса частот – 20Гц…20кГц; системная частота – 256fs; динамический диапазон – (48…106) дБ; Блок схема тракта данных СДЦАП показана на рис. 1. Входные данные обрабатываются блоком цифрового интерполирующего фильтра, повышающего частоту дискретизации сигнала в требуемое число раз. Выходные отсчеты цифрового фильтра обрабатываются блоком сигма-дельта модулятора. Далее в аналоговом блоке формируются выходной аналоговый стерео или моно сигнал. fs, N-bit Mxfs Блок ввода цифровых данных Цифровой интерполирующий фильтр fs Блок СДмодулятора Kxfs,V-bit Mxfs Аналоговый блок outL outR Рис. 1. Тракт данных СДЦАП Разработанный маршрут проектирования СДЦАП для звуковых приложений, позволяет проектировать СДЦАП низшего, среднего и высшего классов и включает в себя: 1. Формулирование технического задания. 2. Определение основных функциональных узлов СДЦАП. 3. Определение требований к основным блокам СДЦАП. 4. Расчет передаточной функции сигма-дельта модулятора, выбор порядка сигма-дельта модулятора, коэффициента передискретизации и количество ступеней цифрового фильтра. 5. Расчет коэффициентов цифрового фильтра для каждой ступени с помощью разработанной программы. 6. Компиляцию блока ОЗУ необходимого объема для цифрового фильтра. 7. Реализацию рассчитанного цифрового фильтра путем выбора одной из двух разработанных архитектур. 8. Формирование структуры сигма-дельта модулятора и первоначальный выбор коэффициентов с помощью программных средств MATLAB. 9. Моделирование сигма-дельта модулятора с помощью математических моделей и окончательный выбор коэффициентов сигма-дельта модулятора (включая их представление в виде суммы степеней с основанием два). 10. Реализацию сигма-дельта модулятора на регистрах и сумматорах по выбранной структуре: определяются разрядности регистров и сумматоров. 11. Написание, моделирование и отладка RTL модели СДЦАП на языке Verilog или VHDL. 12. Синтез схемы и топологии СФ блока СДЦАП на основе собственной библиотеки цифровых и аналоговых элементов. 13. Верификация и моделирование схемы СДЦАП с учетом паразитных параметров топологии. Цифровой фильтр совместно с сигма-дельта модулятором определяет основные классификационные характеристики СДЦАП – частотные характеристики. Цифровой фильтр 360 формирует частотную характеристику СДЦАП в звуковом диапазоне 0…20 кГц на основе операции интерполяции сигнала для повышения частоты дискретизации. Цифровой фильтр имеет конечную импульсную характеристику, что важно для аудио применений [2]. Цифровой фильтр повышает частоту дискретизации входного сигнала в 8 раз и подавляет симметричные составляющие спектра сигнала, попадающие в полосу при интерполяции. Повышение частоты дискретизации производится в три этапа. На каждом этапе происходит удвоение частоты. Таким образом, рассчитываются 3 цифровых фильтра, входящие в состав СДЦАП. Синтез цифрового фильтра разбивается на три этапа: синтез фильтра с представлением коэффициентов в виде действительных чисел, разложение полученных коэффициентов в виде степени 2, оптимизация коэффициентов. Особенность реализации синтезированного цифрового фильтра заключается в том, что операция умножения отсчета на коэффициент заменяется операцией сдвиг-сложение. Полученные коэффициенты раскладываются на сумму степеней 1/2 с заданной точностью . Для этого разработан оригинальный алгоритм, позволяющий получить квантованные коэффициенты. Число полученных сумм определяет число операций сдвиг-сложение в цифровом фильтре. Поэтому полученные суммы минимизируются таким образом, чтобы полученная характеристика фильтра не ухудшилась до неприемлемых результатов. Для реализации расчета и оптимизации коэффициентов цифрового фильтра написана программа в среде MATLAB, которая позволяет получить модифицированные коэффициенты цифрового фильтра. Применение данной программы обеспечивает автоматизацию и гарантию того, что полученное разложение коэффициентов фильтра будет минимальным с точки зрения длины разложения. Общая архитектура блока цифровой фильтрации (рис. 2) для звуковых устройств разработана для реализации алгоритмов цифровой фильтрации с использованием методов замены умножения операцией суммирования-сдвига. Она остается неизменной для любых классов СДЦАП. Функции цифровой фильтрации выполняются несколькими функциональными блоками: Блок арифметического устройства - выполняет вычисление сверток. Блок хранения данных - организует циклические буфера и передачу данных в сигма-дельта модулятор. Блок управления обработкой данных - управляет выполнением алгоритма фильтрации. Блок Управления Арифметическое устройство ОЗУ Рис. 2. Структура цифрового фильтра Устройство управления обработкой данных вырабатывает последовательность микрокоманд, поступающих на контроллеры блоков арифметического и запоминающего устройств. Микрокоманды обрабатываются контроллерами и выполняются самими устройствами. Для реализации цифрового фильтра разработано два вида арифметических устройств (АЛУ), выполняющие операции цифровой фильтрации под управлением микропрограммы, заложенной в ПЗУ. Такой подход позволяет разделить аппаратную и программную реализации цифрового фильтра и на едином арифметическом устройстве выполнять дополнительные операции цифровой обработки. Арифметические устройства управляются блоком контроллера арифметического устройства. Первый вид АЛУ предназначен для использования в СДЦАП среднего и низшего классов, так как его производительности достаточно для обеспечения требуемых в данных классах быстродействия и характеристик. Второй тип АЛУ предназначен для использования в СДЦАП высшего класса. Первое АЛУ требует меньших аппаратных затрат при реализации, чем второе АЛУ приблизительно в 2 раза. Вторым основным блоком СДЦАП является сигма-дельта модулятор. Основной задачей при его синтезе является расчет коэффициентов. При их вычислении необходимо следить за характеристикой выходного сигнала модулятора и за его устойчивостью. Известно, что передаточная функция обеспечивает большее отношение сигнал шум при большем порядке сигма-дельта модулятора. Однако сигма-дельта модулятор, порядок которого больше двух, не стабилен. При этом отношение сигнал шум меньше, чем предсказанное линейными моделями. 361 Расчет производится поэтапно. На первом этапе синтезируется передаточная функция (ПФ) модулятора исходя из порядка модулятора, коэффициента передискретизации. Если полученная передаточная функция не удовлетворяет требуемым характеристикам, то производится ее перерасчет. Для этого изменяется либо порядок, либо коэффициент передискретизации. После получения ПФ, удовлетворяющей заданным параметрам, производится выбор структуры модулятора и расчет его коэффициентов. Все эти операции производятся с помощью специальных программных средств, написанных либо на языке программирования, либо на внутреннем языке специальных математических приложений (например, MATLAB). Полученные коэффициенты представляют собой действительные числа, которые представляются в виде 1/2n, так как это позволит выполнять умножение коэффициента, например на 0.5, простым сдвигом на один разряд двоичного числа и, таким образом, уменьшить аппаратные затраты. При переводе коэффициентов в вид 1/2 n необходимо учитывать изменение характеристики выходного сигнала модулятора и его устойчивости. Как правило, они ухудшаются. Поэтому ПФ модулятора необходимо синтезировать с запасом не менее 20%. Практика показывает, что максимальная длина разложения одного коэффициента обычно не превышает 3. Это позволяет существенно сократить аппаратные затраты, так как для реализации одного коэффициента требуется выполнять меньшее количество операций сдвиг-сложение. Сигма-дельта модулятор в СДЦАП реализуется на сумматорах и регистрах. Для предотвращения переполнения в регистрах и сумматорах интеграторов разрядность данных на 3-4 бита больше, чем разрядность входных данных. Поэтому чем больше разрядность входных данных, тем больше площадь модулятора, занимаемая на кристалле. Однако ее можно сократить, уменьшением разрядности внутренних регистров и сумматоров путем отсечения младших разрядов. Как показывает практика, такая операции позволяет более чем в 2 раза сократить размер модулятора без потерь в характеристиках выходного сигнала. Разработан метод сокращения разрядности регистров и сумматоров. Суть метода заключается в увеличении разрядности регистров и сумматоров сигма-дельта модулятора на 10 разрядов. Далее производится моделирование сигма-дельта модулятора, на основе которого выявляются старшие разряды, которые никогда не меняют своего состояния. Следовательно, они убираются из системы. Далее производится усечение регистров и сумматоров первого интегратора. Усечение производится до тех пор, пока характеристика выходного сигнала удовлетворяет требуемой характеристике. После этого производится такая же операция для всех последующих интеграторов. Таким образом, применение данного метода позволяет сократить аппаратные затраты при реализации сигма-дельта модулятора более чем в два раза, так как один разряд регистра занимает большую площадь на кристалле при топологической реализации. СФ блоки СДАЦП для звуковых приложений представляют собой стерео или моно преобразователи входного аналогового сигнала в выходной цифровой поток данных. Основные характеристики и функции СДАЦП: поддержка 12, 16 разрядных выходных данных с частотой дискретизации fs = 4 кГц … 48 кГц; выходной сигнал – стерео, моно; коэффициент нелинейных искажений (КНИ) – (0,01…0,4)%; отношение сигнал/шум (SNR) – не менее 72 дБ; рабочая полоса частот – 0Гц…20кГц; системная частота – 256fs; динамический диапазон – не менее 72 дБ. СДАЦП состоит из аналогового сигма-дельта модулятора, блока цифрового фильтра дециматора и интерфейсного блока. Блок сигма-дельта модулятора преобразует входной аналоговый сигнал. Состоит из самого модулятора и одноразрядного квантователя. В СДАЦП данный блок является аналоговым и описание его разработки выходит за рамки доклада. Блок цифрового фильтра понижает частоту дискретизации сигнала, поступающего из сигма-дельта модулятора и преобразует данные в N-разрядный выходной формат. Тракт данных СДАЦП показан на рис. 3. аналоговый сигнал СД-модулятор Kfs,1bit Kfs,1bit Цифровой фильтр дециматор fs, Nbit правый канал fs,Nbit левый канал Рис. 3. Тракт данных СДАЦП Разработанный маршрут проектирования СДАЦП для звуковых приложений аналогичен маршруту проектирования СФ блоков СДЦАП. Отличие заключается только в отсутствии пунктов проектирования сигма-дельта модулятора и добавлении пунктов расчета comb фильтра и компенсатора. 362 Цифровой фильтр формирует частотную характеристику СДАЦП в звуковом диапазоне 0…20 кГц на основе операции децимации сигнала для понижения частоты дискретизации. Цифровой фильтр имеет конечную импульсную характеристику. Частота дискретизации сигнала на входе цифрового фильтра высокая (несколько МГц), поэтому применение КИХ-фильтра, используемого в СДЦАП, невозможно из-за большого количества вычислений. Для решения этой проблемы используется структура блока цифровой фильтрации, приведенная на рис. 4 [3]. В качестве примера на рисунке показано понижение частоты дискретизации с 64fs до fs. Рис. 4. Структура блока цифровой фильтрации Для децимации данных используются три фильтра. Первая ступень – гребенчатый фильтр, понижающий частоту дискретизации, как правило, в 16 раз. Далее отсчеты обрабатываются двухступенчатым КИХ-фильтром, понижающего частоту дискретизации входного сигнала еще в 4 раза. На выходе, данные обрабатываются компенсатором, представляющим собой фильтр высоких частот. Данный фильтр необходим, из-за завала АЧХ в полосе пропускания, вследствие характерного завала АЧХ гребенчатого фильтра. Для расчета первой ступени фильтра применяется метод, заложенный в пакете программ MATLAB. Данный метод основан на получении передаточной функции фильтра. Расчет коэффициентов не нужен. Для расчета остальных ступеней фильтра применяются такие же методы расчета, что и в звуковых СДЦАП. В частности расчет коэффициентов ведется с помощью метода синтеза фильтров с использованием алгоритма замены Ремеза. Расчет компенсатора проводится в среде MATLAB, для чего написана соответствующая функция. Разложение коэффициентов цифрового фильтра и их оптимизация проводится с помощью методов и разработанных программ для СДЦАП. Разработанные функциональные модели необходимы для моделирования СФ блока в составе СнК интегратором. Поведенческая модель включает в себя четыре основных модуля: модуль ввода цифровых данных для СДЦАП или вывода цифровых данных для СДАЦП, модуль синхронизации, модуль цифрового фильтра и модуль сигма-дельта модулятора (для СДЦАП). Модуль синхронизации осуществляет преобразование входного синхросигнала в системный синхросигнал, всегда имеющий частоту 256fs. Модуль ввода цифровых данных (для СДЦАП) принимает входные отсчеты цифрового аудио-сигнала, поступающие по последовательному или параллельному порту, и передает их в модуль цифрового фильтра. Модуль вывода цифровых данных (для СДАЦП) принимает отсчеты, поступающие из блока цифрового фильтра, и передает их в требуемом виде на выход. Модуль цифрового фильтра осуществляет обработку поступающих входных отсчетов в соответствии с алгоритмом работы цифрового фильтра, и выдает результаты в модуль сигма-дельта модулятора в СДЦАП или в модуль вывода цифровых данных в СДАЦП. Модуль сигма-дельта модулятора в СДЦАП осуществляет обработку поступающих из модуля цифрового фильтра результирующих данных в соответствии с алгоритмом работы сигма-дельта модулятора и выдает результаты в каждом такте системной синхронизации. Функциональные модели СФ блоков СДЦАП и СДАЦП позволяют разработчику на начальном этапе проектирования оценить характеристики СФ блока в целом и провести предварительный расчет основных его блоков. Также функциональные модели позволяют системному интегратору проводить моделирование системы, частью которой является разрабатываемый СФ блок. Поведенческая модель включает в себя четыре основных модуля: модуль ввода цифровых данных, модуль синхронизации, модуль цифрового фильтра и модуль сигма-дельта модулятора. Для каждого из модулей были определены интерфейсы с учетом временной сетки (в тактах системной синхронизации). Модуль синхронизации осуществляет преобразование входного синхросигнала в системный синхросигнал, всегда имеющий частоту 256fs. Модуль ввода цифровых данных в СДЦАП принимает входные отсчеты цифрового аудио-сигнала, поступающие извне, и передает их в модуль цифрового фильтра в СДЦАП. Модуль вывода цифровых данных в СДАЦП и принимает данные из цифрового фильтра и передает их на внешнюю шину. Модуль цифрового фильтра осуществляет обработку поступающих входных отсчетов в соответствии с алгоритмом работы цифрового фильтра, и выдает результаты в модуль сигма-дельта модулятора. Длительность обработки одного отсчета определяется в 128 тактов системного синхросигнала. Один раз за это время в модуль поступают данные из модуля ввода цифровых данных. Для хранения входных данных используются промежуточные переменные. 363 Модуль сигма-дельта модулятора в СДЦАП осуществляет обработку поступающих из модуля цифрового фильтра результирующих данных в соответствии с алгоритмом работы сигмадельта модулятора и выдает результаты в каждом такте системной синхронизации. Разработанные RTL модели являются универсальными, что дает возможность синтеза электрических схем цифровых модулей СФ блоков на различных ASIC и FPGA библиотеках. После определения алгоритмов, интерфейсов и основных временных характеристик работы каждого модуля осуществляется реализация моделей модулей на RTL-уровне. Сигма-дельта модулятор представляется в виде набора интеграторов, каждый из которых состоит из одного регистра и сумматора. Верификация моделей на соответствие исходным алгоритмам выполнена в среде САПР Cadence (NC-Verilog) с использованием разработанного набора тестов. Тестировались поведенческие и RTL модели. Верифицированные электрические схемы (СХЭ) каждого СФ блока представлены результатами синтеза RTL-моделей (netlist) в среде САПР Cadence (Build Gates) на основе собственных библиотек цифровых элементов для технологий уровня 0.5-0.6 мкм, 0.25 мкм и 0.18 мкм. Моделирование полученных в результате синтеза электрических схем на исходных тестах показало функциональную идентичность результатов синтеза исходной RTL-модели. В табл. 2 приведены характеристики разработанных СФ блоков: Таблица 2 Разработанные СФ блоки СДЦАП и СДАЦП Наименование СДЦАП1 СДЦАП2 СДЦАП3 СДАЦП1 СДАЦП2 Основные характеристики Разрядность: 8 бит. Уровень шумов и искажений: 48 дБ. Коэффициент нелинейных искажений: 0,4%. Частота выборки: 4…16 кГц. Динамический диапазон: 48 дБ. Число каналов: 1. Разрядность: 16…18 бит. Уровень шумов и искажений: 90 дБ. Коэффициент нелинейных искажений: 0,01%. Частота выборки: 32…48 кГц. Динамический диапазон: не менее 88 дБ. Число каналов: 2. Разрядность: 20…24 бит. Уровень шумов и искажений: 106 дБ. Коэффициент нелинейных искажений: 0,002%. Частота выборки: 32…96 кГц. Динамический диапазон: не менее 98 дБ. Число каналов: 2. Разрядность: 12 бит. Уровень шумов и искажений: 72 дБ. Коэффициент нелинейных искажений: 0,4%. Частота выборки: 8 кГц. Динамический диапазон: 72 дБ. Число каналов: 1. Разрядность: 16 бит. Уровень шумов и искажений: 93 дБ. Коэффициент нелинейных искажений: 0,01%. Частота выборки: 4…48 кГц. Динамический диапазон: не менее 88 дБ. Число каналов: 2 Методика тестирования включает разработанные и откорректированные наборы тестов, в которых использованы средства функционального тестирования блоков, встроенного самотестирования, технологического тестирования, а также системные средства тестирования JTAG в соответствии со стандартом IEEE Std 1149.1. В результате анализа мирового опыта в области тестирования «систем на кристалле» разработано 2 системы тестирования СДЦАП и СДАЦП [4]. Первая система тестирования предназначена для разработчика и позволяет сканировать внутренние шины СДЦАП и СДАЦП. Вторая система тестирования предназначена для производственного тестирования. В случае первой системы тестирования СДЦАП и СДАЦП содержат специальную логику, обеспечивающую возможность мониторинга в процессе функционирования системы выходов 364 цифрового фильтра и сигма-дельта модулятора. Режим мониторинга задается программированием специального управляющего регистра. Результаты мониторинга выдаются в последовательном коде на выход. При мониторинге цифрового фильтра на выход выдается состояние системной шины в момент передачи данных в сигма-дельта модулятор. В качестве стандарта для второй подсистемы тестирования принят стандарт IEEE Std 1149.1 (JTAG), так как этот стандарт используется в большинстве СБИС «система на кристалле». В состав СДЦАП и СДАЦП интегрируется контроллер и регистр инструкций с последовательной загрузкой. Разработчики системы получают возможность решать проблему кодирования инструкций системного уровня и уровня СДЦАП и СДАЦП и выбирать способ тестирования блоков. Топология СФ блоков спроектирована для технологий уровня 0,5-0,6 мкм, 0,25 мкм и 0,18 мкм. Размеры топологии разработанных СФ блоков СДЦАП и СДАЦП приведены в табл. 3. Таблица 3 Размер топологии разработанных СФ блоков СДЦАП и СДАЦП Наименование СДЦАП1 СДЦАП2 СДЦАП3 СДАЦП1 СДАЦП2 Размер по технологии 0,6 мкм 2,0 2,1 мм2 3,7 2,1 мм2 3,4 3,3 мм2 2,51 2,57 мм2 6,3 4,0 мм2 Размер по технологии 0,25 мкм 0,63 0,7 мм2 1,12 0,66 мм2 1,5 0,6 мм2 1,51 0,83 мм2 2,0 1,4 мм2 Размер по технологии 0,18 мкм 0,9 0,57 мм2 0,88 0,41 мм2 - Топология верифицирована на соответствие электрической схеме и проведено моделирование каждого СФ блока с учетом паразитных параметров, экстрагированных из топологии. Результаты моделирования показали полную работоспособность СФ блоков. Для аттестации СФ блоков разработана топология тестовых схем (тестовых кристаллов) для технологии уровня 0,5-0,6 мкм и 0,25 мкм. Проведены испытания изготовленных БИС по разработанным методикам, составлены протоколы их исследования. Результаты испытаний показали соответствие разработанных СФ блоков требованиям технического задания. Каждый разработанный СФ блок сопровождается документацией, соответствующей требованиям нормативных документов [5]. Разработанная технология проектирования может быть использована для разработки СДЦАП и СДАЦП, ориентированных на более широкий частотный диапазон. Однако для этого необходима адаптация отдельных блоков, таких как цифровой фильтр и сигма-дельта модулятор под новые требования, которые характеризуются ужесточением требований к быстродействию и основным характеристикам (сигнал/шум, динамический диапазон). Таким образом, использование разработанной технологии проектирования позволяет синтезировать СФ блоки СДЦАП и СДАЦП звукового диапазона, которые по основным техническим характеристикам соответствуют требованиям и по совокупности параметров в своем классе не уступают, а по отдельным характеристикам превосходят зарубежные аналоги таких фирм как Texas Instruments и Analog Devices. ЛИТЕРАТУРА 1. 2. 3. 4. 5. J.C. Candy, Gabor C. Temes. Oversampling Delta-Sigma Data Converters // IEEE Press. – 1992. P. 363. J.C. Candy, An-Ni Huynh. Double interpolation for digital-to-analog conversions // IEEE Trans. Communications. – 1986. - V. COM-34. - P. 77-81. R. W. Adams. Design and implementation of an audio 18-bit analog-to-digital converter using oversampling techniques // Audio Eng. Soc, March 1986. - V. 34, no. 3. - P. 153-166. Benabdenbi M., Maroufi W., Marzouki M. Testing TAPed Cores and Wrapped Cores With The Same Test Access Mechainsm // IEEE Design, Automation and Test in Europe (DATE). – March 2001. P. 150-155. Состав информации и форматы ее передачи для аналого-цифровых СФ блоков (Вторая редакция). // РТМ ШИЛГ 430109.001 РМ. – М.: ФГУП НИИМА «Прогресс» – 2002. – 12 с. 365