Схемотехника - Ухтинский государственный технический

реклама

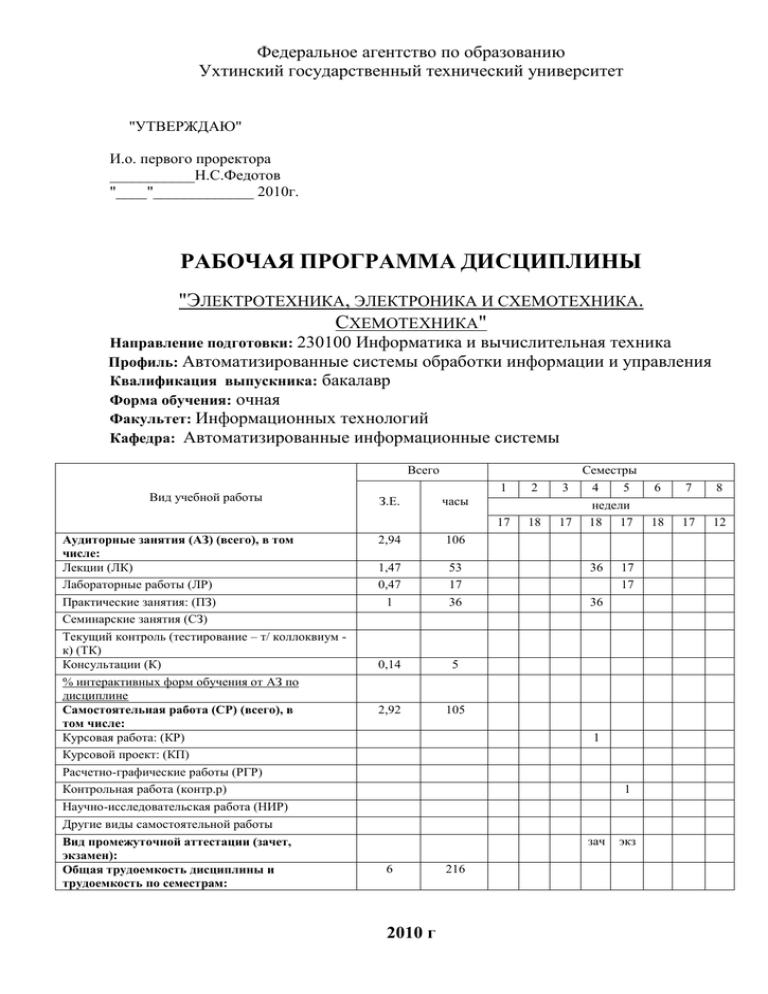

Федеральное агентство по образованию Ухтинский государственный технический университет "УТВЕРЖДАЮ" И.о. первого проректора ___________Н.С.Федотов "____"_____________ 2010г. РАБОЧАЯ ПРОГРАММА ДИСЦИПЛИНЫ "ЭЛЕКТРОТЕХНИКА, ЭЛЕКТРОНИКА И СХЕМОТЕХНИКА. СХЕМОТЕХНИКА" Направление подготовки: 230100 Информатика и вычислительная техника Профиль: Автоматизированные системы обработки информации и управления Квалификация выпускника: бакалавр Форма обучения: очная Факультет: Информационных технологий Кафедра: Автоматизированные информационные системы Всего Вид учебной работы Аудиторные занятия (АЗ) (всего), в том числе: Лекции (ЛК) Лабораторные работы (ЛР) Практические занятия: (ПЗ) Семинарские занятия (СЗ) Текущий контроль (тестирование – т/ коллоквиум к) (ТК) Консультации (К) % интерактивных форм обучения от АЗ по дисциплине Самостоятельная работа (СР) (всего), в том числе: Курсовая работа: (КР) Курсовой проект: (КП) Расчетно-графические работы (РГР) Контрольная работа (контр.р) Научно-исследовательская работа (НИР) Другие виды самостоятельной работы Вид промежуточной аттестации (зачет, экзамен): Общая трудоемкость дисциплины и трудоемкость по семестрам: З.Е. 1 2 17 18 часы 2,94 106 1,47 0,47 1 53 17 36 0,14 5 2,92 105 Семестры 3 4 5 недели 17 18 17 36 17 17 36 1 1 зач 6 2010 г 216 экз 6 7 8 18 17 12 1. Цели и задачи освоения дисциплины 1.1. Цель преподавания дисциплины: Целью преподавания дисциплины является ознакомление с современными схемотехническими технологиями разработки и построения цифровых узлов и устройств, изучение основ построения цифровых логических схем, обучению систематизированному подходу к изучению сложных схем, рассмотрение возможностей и путей использования схемотехнических технологий при анализе, синтезе и проектировании МПС. 1.2. Задачи изучения: научить студентов понимать логику функционирования ЛЭ и ЛС, разрабатывать ЛС, используя математические основы построения ЛС, представлять их роль в функционировании компьютерных систем. 2. Место дисциплины в структуре ООП ВПО Дисциплина "Схемотехника" относится к Профессиональному циклу, базовая часть. Перечень дисциплин с указанием разделов (тем), усвоение которых студентами необходимо для изучения данной дисциплины: «Дискретная математика», «Физика» с разделами Электричество и электрические цепи; «Информатика» с разделами Булевы операции, Алгебра логики; «Электротехника и электроника» с разделами Переходные процессы в электрических цепях, Электрические приборы и аппараты, Биполярные транзисторы, МОП-транзисторы, Арифметические и логические основы ЭВМ; «Алгоритмические языки и программирование». Для изучения данной дисциплины студент должен уметь использовать основные законы естественнонаучных дисциплин для понимания преподаваемой дисциплины, иметь навыки работы с компьютером как средством управления информацией, знать основные средства разработки программ для возможности последующего моделирования схем. Дисциплина является предшествующей для изучения дисциплин "ЭВМ и периферийные устройства», «Системные средства организации и взаимодействия программ», «Сети и телекоммуникации», «Системы реального времени». 3. Требования к результатам освоения дисциплины: Изучение дисциплины направлено на формирование следующих компетенций: Выпускник по направлению подготовки 2301000062 «Информатика и вычислительная техника» с квалификацией (степенью) «бакалавр» должен обладать следующими компетенциями: владеет культурой мышления, способен к обобщению, анализу, восприятию информации, постановке цели и выбору путей её достижения (ОК– 1); умеет логически верно, аргументировано и ясно строить устную и письменную речь (ОК-2); способен находить организационно - управленческие решения в нестандартных ситуациях и готов нести за них ответственность (ОК-4); стремится к саморазвитию, повышению своей квалификации и мастерства (ОК-6); использует основные законы естественнонаучных дисциплин в профессиональной деятельности, применяет методы математического анализа и моделирования, теоретического и экспериментального исследования (ОК-10); осознает сущность и значение информации в развитии современного общества; владеет основными методами, способами и средствами получения, хранения, переработки информации (ОК-11); имеет навыки работы с компьютером как средством управления информацией (ОК-12); способен работать с информацией в глобальных компьютерных сетях (ОК-13); осваивать методики использования программных средств для решения практических задач (ПК-2); разрабатывать интерфейсы «человек-ЭВМ» (ПК-3); использовать современные инструментальные средства и технологии программирования (ПК-5); обосновывать принимаемые проектные решения, осуществлять постановку и выполнять эксперименты по проверке их корректности и эффективности (ПК-6); готовить презентации, научнотехнические отчеты по результатам выполненной работы, оформлять результаты исследований в виде статей и докладов на научно-технических конференциях (ПК-7); участвовать в настройке и наладке программно-аппаратных комплексов (ПК-9); сопрягать аппаратные и программные средства в составе информационных и автоматизированных систем (ПК-10); инсталлировать программное и аппаратное обеспечение для информационных и автоматизированных систем (ПК-11). В результате освоения дисциплины обучающийся должен: 3.1. Знать: фундаментальные законы электроники и электротехники, методы синтеза комбинационных и последовательных схем, классификацию и назначение функциональных узлов ЭВМ, принципы построения структурных, функциональных и принципиальных схем узлов ЭВМ. 3.2. Уметь: выполнять расчет и проектирование цифровых узлов и устройств ЭВМ, моделировать их работу программными средствами, анализировать и применять современные схемотехнические методы и разработки для проектирования ЦУ. 3.3. Владеть: современными методами и средствами проектирования функциональных узлов ЭВМ, программами автоматизированного анализа схем, иметь навыки синтеза схем ЭВМ. 4. Структура и содержание дисциплины 4.1. Содержание разделов дисциплины: № п/п 1. 2. 3. Наименование Содержание раздела Трудоемко раздела дисциплины сть, (модуля) часы з.е. 1Логические основы Основные понятия и определения. 1 построения цифровых схем Математические основы построения цифровых 1 логических схем. Логические функции 1 и 2х переменных 2 Аксиомы и законы алгебры логики. Таблицы 2 истинности. Суперпозиция логических функций. Базисы 2 Нормальные и совершенные нормальные формы 2 ЛФ Применение матриц Карно для оптимизации 2 логических функций 2 Цифровые узлы Логические элементы. комбинационного Дешифраторы. Шифраторы. 2 типа Мультиплексоры. Демультиплексоры. 2 Арифметические устройства: сумматор, АЛУ, 2 компаратор. Схемы контроля данных: мажоритарные 4 элементы, контроль по модулю 2, схемы кодирования-декодирования кода Хэмминга. Формы представления информации. 4 Интегральные Классификация и система обозначений ИС. схемы Схемотехника базовых элементов ТТЛ и КМОПлогики. Проблемы проектирования. Сопряжение интегральных схем 1 4. 5. 6. 7. Цифровые узлы Временные булевы функции. Проблемы и методики проектирования ЦУ последовательного последовательного типа. ВБФ, БФ 1 и 2 рода. типа Синтез и схемы реализации ВБФ. Триггеры. Синхронные, асинхронные. асинхронный RS, синхронный RS-триггер, MSтриггер, асинхронный и синхронный T-триггер, D-триггер, с динамическим управлением, JKтриггер. Временные диаграммы работы. Регистры. Счетчики. Автоматы с памятью. Классификация и система параметров ЗУ Электронная память Построение оперативной памяти. Статическая, динамическая. Организация. Параметры. Характеристики. Виды. Постоянная память. Программируемые логические матрицы. ПМЛ. Базовые матричные кристаллы. Драйверы. Буферные регистры. Интерфейсные устройства Параллельные порты и адаптеры. Микропроцессор и Сравнительный обзор. Функции. Принципы построения. Области применения. микроконтроллер Автоматизация этапов проектирования ЦУ. Итого: 7 6 2 2 1 2 2 2 53 4.2. Разделы дисциплины и виды занятий № п/п Наименование раздела дисциплины (модуля) ЛК1 ЛР ПЗ Логические основы построения цифровых схем Цифровые узлы комбинационного типа Интегральные схемы + + + + + + 4. Цифровые узлы последовательного типа + 5. 6. 7. Электронная память Интерфейсные устройства Микропроцессор и микроконтроллер + + + 1. 2. 3. + КP (контр. и курс. раб.) + + + + + СР + + + + ТК + + + + + + + + + + 5. Лабораторный практикум № п/п 1 Наименование раздела дисциплины (модуля) Наименование лабораторных работ Используемый вид занятий при прохождении данного раздела помечается знаком “+” Трудоемко сть 1. 2. 3. 4. 5. Цифровые узлы Моделирование работы логических комбинационного типа комбинационных схем на базе ЛЭ заданной серии, дешифратора, мультиплексора. Цифровые узлы Разработка и моделирование двоичнопоследовательного типа кодированных счетчиков с произвольным модулем Цифровые узлы Построение и моделирование триггерных последовательного типа схем. Построение динамических временных диаграмм. Цифровые узлы Моделирование работы регистровых схем последовательного типа для передачи информации. Построение динамических временных диаграмм. Интерфейсные устройства Моделирование работы шинных формирователей. Итого: 6. Практические и семинарские занятия № Наименование Содержание раздела п/п раздела дисциплины 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Логические основы построения цифровых схем Логические основы построения цифровых схем Логические основы построения цифровых схем Логические основы построения цифровых схем Логические основы построения цифровых схем Цифровые узлы комбинационного типа Цифровые узлы комбинационного типа Цифровые узлы комбинационного типа Цифровые узлы последовательного типа Синтез логических условий. Задачи логические условия, таблицы истинности. часы 4 3 3 4 3 17 Трудоемко сть, часы з.е. на 2 ЛФ, ЛС, построение элементарных ЛС. 4 Логические функции. Совершенные формы. Преобразование ДНФ, КНФ в совершенный вид. 2 Построение ЛС в базисах и – не, или – не. Применение закона де Моргана для построения. 4 Оптимизация ЛФ методом матриц Построение оптимальных схем. Карно. 4 Построение схем на базе дешифраторов. Реализация совершенных и смешанных форм функций. Построение схем на базе мультиплексоров. Реализация логических условий. 4 Задачи на сумматоры, АЛУ. Проблема состязаний – методика решения. Схемы контроля данных. Задачи на временные булевы функции, БФ 1 и 2 рода. Построение последовательных схем и временных диаграмм. 4 Цифровые узлы Построение триггерных схем, временных последовательного диаграмм их работы. з.е. 4 4 4 типа Итого: 36 7. Примерная тематика курсовых проектов (работ) №№ п-п 1. Наименование проекта (работы) Номер темы Проектирование комбинационных схем для реализации ЛФ 2 Конкретная цель выполнения проекта (работы) Объем заданий Врем я допо лн. час. Построение 2 части комбинационных схем для заданной логической функции на базе ЛЭ с оптимизацией, в заданном базисе с поиском оптимального решения, на базе дешифратора, мультиплексора заданной серии. 8. Образовательные технологии На лекционных и практических занятиях используется активная и интерактивная формы проведения занятий. На лабораторных работах выполняются задания по разработке моделирующих программ с использованием современных пакетов, предназначенных для создания и редактирования схем и динамических диаграмм. 9. Оценочные средства для текущего контроля успеваемости, промежуточной аттестации по итогам освоения дисциплины и учебно-методическое обеспечение самостоятельной работы студентов К ежемесячному контролю относится контроль выполнения лабораторных работ.. Рубежный контроль осуществляется посредством выполнения тестовых заданий по пройденной теме. Итоговый контроль осуществляется приемом курсовой работы и экзамена. Зачёт 1. Двоичная система счисления для функционирования ЦС. 2. Законы и теоремы булевой алгебры логики. 3. Логические функции одной и двух переменных. Базовые элементы ЦУ. 4. СДНФ, СКНФ. Свойства. 5. Базисы. 6. Применение матриц Карно для оптимизации логических функций 7. Формы представления информации 8. Схемотехника базовых элементов ТТЛ-логики 9. Проблемы проектирования ЦУ комбинационного типа 10. Дешифраторы и шифраторы 11. Мультиплексоры 12. Демультиплексоры 13. Сумматоры 14. Арифметические устройства 15. Драйверы 16. Компараторы 17. Схемы контроля: мажоритарные элементы, контроль по модулю 2, код Хэмминга Экзамен 1. Матрицы Карно. Оптимизация ЛС. Задачи. 2. Базисы. Задачи. 3. ТТЛ-схема И-НЕ с третьим состоянием, с разрешением по входу. Задачи. 4. Реализация ЛФ на базе дешифраторов, мультиплексоров. Задачи. 5. Передача данных через ЦУ комбинационного типа. Задачи. 6. Временные булевы функции, 1 рода, 2 рода. Задачи. 7. Реализация логических условий на базе триггеров. Задачи. 8. Триггерные схемы, структура, таблицы истинности, диаграммы состояний, таблицы переходов. Задачи. 9. Построение n-разрядных схем регистров – сдвига, реверсивных, статических. Задачи. 10. Построение счетчиков: асинхронных, синхронных, с параллельным переносом, реверсивных, с заданным модулем пересчета. Метод управляемого сброса. Задачи. 11. Программируемые логические матрицы. Построение. Задачи. Тренировочные задачи и упражнения Задача 1. 1. Перевести числа 891, 123, 25 в следующие системы счисления: а) двоичную б) шестнадцатеричную 2. Перевести число 1001110101001010 в шестнадцатеричную систему счисления. 3. Перевести число 5DC8AF в двоичную систему счисления. Задача 2. Построить таблицу истинности по условиям: сигнал Х формируется при условии равнозначности первого и третьего сигналов с трех датчиков и низком уровне второго. Записать логическую функцию. Задача 3. Некий объект может перемещаться в двух направлениях – в пункты 1,2,3 или в пункты 4,5,6. Построить таблицу истинности для логической функции формирования сигнала на включение механизма перемещения объекта при поступлении не менее двух требований из пунктов 4,5,6. Записать логическую функцию. Задача 4. Построить таблицу истинности и записать логическую функцию. Положение механизма определяется сигналами с трех датчиков. При равнозначности сигналов первых двух датчиков механизм поднимается в том случае, если сигнал с третьего датчика равен "1". При их неравнозначности механизм опускается, если сигнал с третьего датчика равен "0". В других случаях привод механизма не включается. Задача 5. Оптимизировать логическое выражение: 1). X ab a b cd a b ab e f a b ab cd 2). X ab c ab c d ab a bc d k 3). X a bc d a b a c d 4). X a bc d k a b c d k Задача 6. Для логической функции построить схему на комбинационной логике: X ab c e f m d k l Задача 7. По данной схеме записать логическую функцию. Задача 8. Построить логическую схему с двумя выходами: 1). Х1= ab c de Х2= ab d c 2). Х1= ab a b cd Х2= ab a d e c 3). Х1= a m(b c d )k Х2= k (b c d )( a m) Задача 9. Построить схему для сравнения двух двухразрядных двоичных чисел, формирующую “1” значение сигнала на выходе при их равенстве. Задача 10. Построить схему по условиям: положение затвора может быть “закрыто – открыто”, и определяется тремя датчиками (a,b,c). При равнозначности сигналов второго и третьего датчиков команда на открытие затвора подается, если сигнал с первого датчика “0”. При неравнозначности сигналов второго и третьего датчиков и значении первого датчика “1”, затвор закрывается. В остальных случаях привод отключен. Задача 11. Построить логическую функцию для сравнения двух трехразрядных двоичных чисел, формирующую “0” при их равенстве. Задача 12. Проверить равносильность: X 1 ab a c ab X 2 b c a b ab Задача 13. Определить, при каких наборах сигналов a, b, c логическая функция принимает значение "1". 1). X ab b c ac 2). X a b ac 3). X a b a c bc Задача 14. Определить, при каких наборах сигналов a, b, c логическая функция принимает значение "0". 1). X a b b c a c 2). X acd a b d 3). X a c b c a c Задача 15. Записать логическое выражение по заданным условиям. Если датчики 1 и 2 выдают одинаковые сигналы и при этом: если датчик 3 выдает "1" и одновременно датчик 4 –"0" или датчик 5 выдает "1", то включается механизм М1; если датчик 3 выдает "0" или датчик 4 выдает "1", a с пятого датчика сигнал имеет низкий уровень, то включается механизм М2. Построить схемы в смешанном базисе. Задача 16. При каких наборах abc функция принимает: 1). Значение “1” X a b ac 2). Значение ”0” X a cb c Задача 17. Записать отрицание логической функции в СДНФ и СКНФ. Х(аbc)=П 1,3,5,6 Задача 18. Построить схему в базисе: a) ”и – не”; б) “или – не”. X ab a b c d Задача 19. Построить схему в базисе: a) ”и – не”; б) “или – не”. X a b cd f Задача 20. Построить логическую схему на базе трехвходового элемента “или – не”. X abcd Задача 21. Построить логическую схему на базе трехвходового элемента "или - не". _ _ X=avbvcvd Задача 22. Построить логическую схему: 1) в базисе “или – не” (элемент на два входа) X ab c adc 2) в базисе “и – не” (элемент на два входа) X ab cde cd e Задача 23. Построить оптимальную логическую функцию, если: a ~ b и c d , то X = d; a b и c ~ d , то X = c; a b и c d , то X = 0; a ~ b и c ~ d , то X = 1; Задача 24. Построить оптимальную схему. Имеется четыре датчика в некотором технологическом процессе. В зависимости от формируемых ими сигналов контролируемый объект занимает крайнее левое или крайне правое положение. Крайнее левое, если сумма сигналов первого и третьего датчиков равнозначна сигналу с четвертого датчика. Крайнее правое, если сигналы с датчиков составляют двоичный код чисел 2,6,8,12. В других случаях привод механизма отключен. Задача 25 . Построить оптимальную схему. Сигнал Х появляется при высоком уровне сигнала В или высоком уровне сигналов А и С, или при отсутствии А, В и С. Задача 26. Построить схему, используя только 5 элементов по условиям: сигнал Х исчезает при появлении только одного сигнала В, или только двух сигналов А и С, или при отсутствии А, В и С. Базис - смешанный. Задача 27. Построить оптимальную логическую схему в смешанном базисе: X abcd 0,1,4,10,11,14 Задача 28. Построить оптимальную логическую схему в базисе “или – не”: X abcd 0,2,5,7,8,13 Неопределенные условия - 3,14 Задача 29. На базе дешифратора с прямыми и с инверсными выходами построить схему, реализующую логические функции: X 1 abc 0,1,4; X 2 abc 1,2,4,6. Задача 30. Построить схему для сравнения двух трехразрядных двоичных чисел по условию: "1" на выходе формируется в случае, если число A > B в два раза. Задача 31. Реализовать логическую функцию на базе трехразрядного дешифратора: X abcd 4,5,7,12,14,15 Задача 32. Построить схему для сравнения трех трехразрядных двоичных чисел на базе дешифратора. При выполнении условия равенства А=В=С формируется логическая "1". Задача 33. Построить на базе трехразрядного дешифратора функции: 1). Х1(abcd)= ∑ 5, 6, 14 Х2(abcd)= П 4, 7, 12, 14, 15 2). Х1(abcd)= ∑ 0, 8, 10, 14 Х2(abcd)=П 2, 4, 12 Задача 34. Реализовать функцию Х(abcd)= ∑ 0, 3, 6, 8, 11, 13, 14, 15 на базе трехразрядного дешифратора при условиях, что вход разрешения заземлен, сигналы распределены на входах: 20=a, 21=b, 22=c. Задача 35. Реализовать функцию Х(abcd)= ∑ 0, 3, 6, 8, 11, 15 на базе трехразрядного дешифратора, используя дополнительную логику, включая логический элемент равнозначность. Задача 36. Построить схему на базе MХ 8:1, реализующую следующую логическую функцию: X abcd 2,3,7,9,10,11,13,14 при условии, что вход разрешения заземлен. Задача 37. Построить схему на базе МХ 8:1. Х(abcd)= П 0, 3, 5, 7, 10, 11, 14, 15 Задача 38. Построить схему на базе мультиплексора 8:1, реализующую логическую функцию: X a bc ab c a b c abc d 1). Используя вход разрешения; 2). При условии, что вход разрешения заземлен. Задача 39. На базе DC и MХ с прямым выходом построить схему для сравнения двух трехразрядных двоичных чисел. Задача 40. Построить схему системы управления коммуникационным оборудованием по условиям: 1. C 1 до 5 часов система отключается, если имеют место три одновременных запроса от сервисной службы. 2. C 5 до 19 часов система отключается, если имеет место хотя бы один запрос от сервисной службы. 3. C 19 до 24 часов система отключается, если имеют место любые два запроса от сервисной службы. 4. C 24 до 1 часов сервисная служба осуществляет технический контроль системы. Задача 41. Заданы а, b – входные переменные, Х – выходная функция. Если а = 0, то x = b. Если а = 1, то Х сохраняет свое значение. Построить оптимальную схему. Задача 42. Механизм включается по сигналу а. При наличии сигнала b он остается включенным и при исчезновении сигнала а. В противном случае (b = 0), при исчезновении сигнала а механизм отключается. Построить оптимальную схему. Задача 43. По данной схеме записать логическое выражение. Задача 44. Реализовать логическую функцию X a x b на базе дешифратора. Задача 45. Система находится в рабочем состоянии при наличии сигнала с и отсутствии а. Также система будет работать, если отсутствуют только сигналы b и с. Известно, что одновременно с этими условиями выходной сигнал Х поступает в систему в инвертированном виде. Построить схему: 1. в базисе ИЛИ – НЕ; 2. в смешанном базисе; 3. на базе дешифратора. Задача 46. Реализовать схему по заданной ЛФ: xt a1t a 2t a3t a1t 1 a 2t 2 Задача 47. Вывести формулы для логических функций, описывающих работу выходов Q и Q для RS – триггера с прямым управлением, для RS – триггера с инверсным управлением. Задача 48. Реализовать ЛФ на базе RS – триггера с прямым и инверсным управлением. 1). X ab x c d 2). X a b x c de Задача 49. Построить схему включения – отключения двух систем контроля. По сигналу а=1 и нажатию кнопки “Set” запускается система 1. По сигналу а=0 и нажатию кнопки “Set” запускается система 2. Отключение производится кнопкой “Reset”. Сигналы от кнопок являются кратковременными. Задача 50. Объект перемещается по замкнутому пути в одном направлении, разделенному на 3 участка. Построить схему индикации объекта на каждом участке. Задача 51. Построить схему автоматического открывания дверей при приближении к ним с обеих сторон человека. Положение двери контролируется 2 датчиками (открыто – закрыто). Задача 52. Построить схему управления объектом, который контролируется двумя лицами с равным приоритетом, находящимися на расстоянии друг от друга. Задача 53. Преобразовать типы триггеров: 1. Д в асинхронный Т. 2. JK в Д. 3. RS в JK. 4. JK в асинхронный Т. 5. Синхронный RS в асинхронный Т. Задача 54. Построить реверсивный трехразрядный регистр и временную диаграмму. Задача 55. 1. Построить суммирующий счетчик с М = 8. 2. Построить вычитающий счетчик с М = 8. Построить временные диаграммы. 10. Учебно-методическое и информационное обеспечение дисциплины (модуля) 10.1. Основная и дополнительная литература: №№ п-п Л-1 Л-2 Л-3 Л-4 Л-5 Л-6 Л-7 Л-8 Год издания Кол-во экз. в библиотек е И.А. Базарова Цифровая схемотехника - Ухта: УГТУ Уч. п. Е.П. Угрюмов Цифровая схемотехника: Учеб.пособие Уч.п. для вузов. - 2-е изд., перераб. и доп. – СПб.: БХВПетербург Барри Уилкинсон, Основы проектирования цифровых Др. схем. - «Вильямс» схемы. Методология И.А. Базарова Комбинационные и последовательные Уч.мет схемы. Сборник контрольных работ для студентов .разр. специальности 230102 АСОиУ заочной формы обучения - Ухта: УГТУ И.А. Базарова Разработка и проектирование ИС. Уч.мет Сборник контрольных и практических заданий – Ухта: .разр. УГТУ 2004 2004 150 1 2004 1 2009 65 2006 65 И.А. Базарова Схемотехника. Практикум к решению Уч.мет задач – Ухта: УГТУ .разр. И.А. Базарова Проектирование двоичных счетчиков. Уч.мет Методические указания к выполнению курсовой .разр. работы – Ухта: УГТУ И.А. Базарова Разработка и построение цифровых Уч.мет узлов процессорной системы. Методическое указание .разр. к выполнению лабораторных работ по дисциплине «Схемотехника» - Ухта: УГТУ Дополнительная 2001 150 2007 65 2004 100 Автор и наименование Вид пособи я Л-9 В.Л.Горбунов, Д.И.Преснухин, Д.Л.Преснухин Справочное пособие по микропроцессорам и микроЭВМ: под ред. Л.Н.Преснухина – Москва: Высшая школа Др. 1988 2 10.2. Программное обеспечение и Интернет-ресурсы http://www.intuit.ru/department/hardware/ http://de.ifmo.ru/bk_netra/ http://www.radioland.net.ua/ http://www.ref.by/ ОС Windows XP, CorelDRAW Graphics Suite X3 v13.0 Rus, Photoshop 9 CS2 Rus Интегрированная среда разработки ПО Delphi 7.0 11. Материально-техническое обеспечение дисциплины "Схемотехника": Лекции проводятся в лекционной аудитории 218к, рассчитанной на 50 посадочных мест, площадью 66,9 м2. Аудитория оборудована проектором, экраном, учебной доской, ноутбуком. Лабораторные занятия проводятся в 204к - "Лаборатория новых информационных технологий", площадь 48,5 м2, рассчитана на 10 посадочных мест. Аудитория оборудована: 10 компьютеров на базе процессора Intel-P4, CPU 2.8 GHz, 256 МБ ОЗУ, НDD 80 Gb; 10 мониторов LG FLETRON F700P 17'; учебная доска. Практические занятия проводятся в 213к, площадь 49,4 м2, рассчитана на 24 посадочных места. Аудитория оборудована пластиковой доской для ведения записей, рабочим местом преподавателя. 12. Методические рекомендации по организации изучения дисциплины: Рабочая учебная программа по дисциплине "Схемотехника" составлена в соответствии с требованиями Федерального Государственного образовательного стандарта ВПО с учетом рекомендаций ПрООП ВПО по направлению 230100 Информатика и вычислительная техника и учебного плана по профилю подготовки Автоматизированные системы обработки информации и управления. Автор: доц. каф. АИС УГТУ ___________________ ( И.А.Базарова ) Рецензент(ы) ______________________________ ( ) Рабочая учебная программа рассмотрена на заседании учебно-методического совета университета протокол № от “ “ ________ 20___ г. и признана соответствующей требования Федерального Государственного образовательного стандарта и учебного плана по направлению 000000.00 "…………………………." Председатель УМС ______________ Бабаевский П.Г. Рабочая учебная программа рассмотрена методическим Советом факультета №___ и признана соответствующей требования Федерального Государственного образовательного стандарта и учебного плана по направлению 000000.00 "…………………………." Декан факультета № ____ _______________ . ( Председатель методического Совета факультета № ____ ____________ ( Программа согласована с УМУ университета ______________ Козлов Н.А. ) )