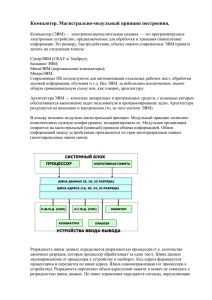

Московский государственный университет печати Кафедра «Информационные системы» Курс лекций по дисциплине: «Архитектура ЭВМ и систем» Москва, 2006 г. Содержание Лекция No1 Логические элементы ............................................. 3 Понятие о комбинационной схеме и цифровом автомате 4 Лекция No2 Цифровые автоматы. Арифметические и логические основы работы...................................................... 6 Лекция No3 Триггеры............................................................. 9 RSтриггер............................................................. 9 Лекция No4 Триггеры (продолжение).......................................... 12 Ттриггер............................................................... 13 Dтриггер.............................................................. 13 JKтриггер.............................................................. 14 Регистры............................................................. 16 Лекция No5 Регистры(продолжение).......................................... 18 Дешифраторы....................................................... 19 Мультиплексоры................................................... 21 Лекция No6 Счетчики............................................................. 23 Сумматоры.......................................................... 25 Лекция No7 Процессоры ЭВМ.................................................. 29 Лекция No8 Процессоры (продолжение)..................................... 34 Лекция No9 Память............................................................... 40 Классификация памяти................................................ 42 Лекция No10 Структура и общие характеристики ЭВМ.................... 45 Команды............................................................. 49 Лекция No11 Структура процессоров.......................................... 51 Определение вычислительного процесса............................... 52 Лекция No12 Основы формирования системных шин...................... 56 Формирователи шин адресов........................................... 56 Формирователи шин управления..................................... 56 Организация ввода-вывода в вычислительных системах............ 57 2 Лекция No 1 Логические элементы В схемах вычислительных устройств значения изменяются не непрерывно, а только в дискретные моменты времени обозначаемыми целыми неотрицательными числами. Временной интервал между двумя соседними моментами дискретного времени называется тактом. Как правило, все схемы цифровых устройств содержат специальный блок, который вырабатывает синхронизирующие сигналы, отвечающий в моменты дискретного времени, т.е. границы такта. Для физического представления информации в цифровых устройствах ЭВМ применяют потенциальные и импульсные способы представления информации. При потенциальном способе двум значениям двоичной переменной соответствуют разные формы потенциалов, соответствующей точки схемы цифрового электронного устройства. Электрический сигнал при потенциальном ходе сохраняет постоянный уровень в течение такта, а его значения в переходные моменты времени не являются определёнными. При импульсном способе передачи информации единичное и нулевое значение двоичной переменной отображаются наличием или отсутствием электрического импульса или разно-полярными импульсами в соответствующей точке электронной схемы. Импульсный сигнал характеризует амплитудой импульса, продолжительностью импульса по основанию, а так же длительностью фронта импульса и среза импульса. Потенциальный сигнал характеризует разность верхнего и нижнего уровня напряжений представляющих двоичную единицу и двоичный ноль. В соответствии с типом используемых сигналов устройства вычислительной техники делят на импульсные, потенциальные и смешанные. Двоичная информация может быть представлена двоичным словом (32 двоичных разряда) или полусловом (16 разрядов). Соответственно двоичная информация может быть представлена последовательным или параллельным кодом. При последовательном коде все разряды двоичного слова разбиваются на временные такты таким образом, что каждый разряд представляется на отдельном такте. В этом случае все разряды слова фиксируются отдельными элементами и проходят через одну линию передачи информации. При параллельном коде все разряды двоичного слова представляются в одном временном такте, каждый разряд фиксируется отдельным элементом и каждый разряд проходит через отдельную линию, каждая из которых служит для представления и передачи только одного разряда слова. При параллельной передаче информации код слова развёртывается не во времени, а в пространстве, т.к. значения всех разрядов передаются одновременно. В зависимости от применяемого кода для обработки информации устройства ВТ называют последовательными или параллельными. Устройства, реализующие последовательный код работают значительно медленнее, поэтому в современных ЭВМ основные устройства, участвующие в обработке информации для достижения высокого быстродействия строятся как параллельные, хотя и требуют большего количество аппаратуры. Для экономии оборудования в некоторых устройствах применяют последовательно-параллельный код, при котором слова разбиваются на части и обработка информации производится последовательно слог за слогом, а в свою очередь каждый слог представляется параллельным кодом. 3 Понятие о комбинационной схеме и цифровом автомате Рис. 1.1. Схема цифрового автомата Преобразование информации в ЭВМ осуществляется электронными устройствами (логическими схемами) двух классов: комбинационными схемами или цифровыми автоматами. В комбинационных схемах совокупность выходных сигналов. Выходное слово Y в любой момент времени однозначно определяется входными сигналами X, поступающими на входы в те же моменты времени. Реализуемый в этих электронных схемах способ обработки информации называется комбинационным, т.к. зависит только от комбинации входных сигналов и вырабатывает сразу же при поступлении информации на вход комбинационной схемы. Закон функционирования комбинационной схемы определён, если соответствие между её входными и выходными словами задано в виде таблицы. Это соответствие может быть задано в виде булевых функций. В отличие от комбинационной схемы, цифровой автомат имеет некоторое конечное состояние, которое определяется его конструктивной особенностью. Цифровой автомат может иметь одно или несколько состояний. Под воздействием входного слова переходит из одного состояния в другое и выдаёт выходное слова. Выходное слова на выходе цифрового автомата в такте определяется в общем случае входным словом, поступившем в этот временной такт на вход автомата и внутреннем состоянием автомата, которое является результатом воздействия на автомат выходных слов в предыдущие такты. q1 ЗЭ1 q1 y1 q2 qk q2 y2 x1 x2 qk yk xn КС1 ЗЭ2 КС2 ЗЭ3 012 Условные обозначения: КС – комбинационная схема; ЗЭ – запоминающий элемент. 4 Контрольные вопросы к лекции No 1 1. Что такое такт? Что определяет границы такта? 2. Назовите два способа представления информации в цифровых устройствах. 3. Что происходит при потенциальном способе передачи информации? 4. Что происходит при импульсном способе передачи информации? 5. На какие категории делят устройства вычислительной техники в соответствии с типом используемых сигналов? 6. Чем отличается представление информации с помощью последовательного кода от представления информации с помощью параллельного кода? 7. Какой код применяется в устройствах для экономии оборудования? 8. Как устроена комбинационная схема? 9. Как работает цифровой автомат? 5 Лекция No 2 Цифровые автоматы. Арифметические и логические основы работы. Цифровой автомат содержит память, которая обладает возможностью фиксировать состояние автомата в предшествующие моменты времени. Состояние запоминающих элементов, определяющих состояние автомата, передается в форме сигналов qj по цепям прямой связи на входы комбинационной схемы No 2 и по цепям обратной связи на входы комбинационной схемы No1. На входы комбинационных схем и первой и второй поступают входные сигналы xn. Выходное слово цифрового автомата вырабатывается в комбинационной схеме No2, причем входными переменными служат буквы входного слова икс энное, а также состояния qj запоминающих элементов. Одновременность появления новых значений входного слова на всех входах цифрового автомата достигается с помощью тактирующих сигналов, обеспечивающих передачу информации с запоминающих элементов на входы комбинационной схемы одновременно с сигналами, поступающими на ее входы с других устройств. Смотрите рис. 1.1. В некоторых случаях при анализе работы цифрового автомата его можно заменить автоматом с одним эквивалентным входом и одним эквивалентным выходом и считать, что эквивалентные входные сигналы x(t) и выходные сигналы y(t) принимают значения из преобразованных алфавитов P и S входных и выходных сигналов. Для однозначного задания цифрового сигнала должны быть указаны: 1. Входной алфавит p=p1..., pn 2. Выходной алфавит s=s1, s2,...sn 3. Алфавит состояний Q=Q1, Q2...Qr 4. Начальное состояние автомата Q0 5. Функции перехода A=Q, x; функции выходов B=Q, x; однозначно определяющих зависимость состояний автомата в такте t+1 и выходного сигнала y(t) в такте t от состояния автомата Q(t) и входного сигнала x(t). Поведение цифрового автомата можно описать выражениями: Q(t+1)=A[Q(t), x(t)] (1) y(t)=B=[Q(t), x(t)] (2) Q(0)=Q0 Выражениям (1) и (2) соответствует автомат, выходной сигнал которого зависит от состояния автомата и от сигнала на входе цифрового автомата. Такой цифровой автомат называется автоматом Мили. В устройствах вычислительной техники применяется цифровой автомат, у которого поведение может быть описано следующим образом: Q(t+1)=A[Q(t), x(t)] (3) y(t)=B=[Q(t) (4) Поведение такого цифрового автомата на выходном такте t зависит исключительно от состояния автомата в этом такте и не зависит от входного сигнала на этом такте. Цифровой автомат, поведение которого описывается выражениями (3) и (4), называется автоматом Мура. Функции переходов и выходов могут задаваться различными способами, например, в форме таблиц или графов. При задании состояния автомата вершинами могут быть заданы состояния автомата, а переходы из состояния в состояние могут быть заданы дугами или ребрами. При этом на дугах указываются значения входных сигналов, вызывающих переход автомата из одного состояния в другое. Выходные сигналы автомата Мура указываются 6 рядом с вершинами графа, выходные сигналы автомата Мили, вырабатываемые перед переходом, указываются на соответствующих ребрах графа. В теории цифровых автоматов вводят понятие полной системы переходов и полной системы выходов автоматов. Если для двух любых состояний qi и qj автомата имеется входной сигнал, переводящий автомат из состояния qi в состояние qj, то такой автомат называется автоматом с полной системой переходов. Автомат Мура имеет полную систему выходов, если выходные сигналы различны для всех его состояний. При построении узлов и элементов электронных вычислительных машин в качестве запоминающих элементов используются элементарные автоматы, как правило, это автоматы Мура с двумя состояниями, обладающие полными системами переходов и выходов. Для описания законов функционирования комбинационных автоматов используется математический аппарат булевых функций, которые представляют собой функции двоичных переменных 0 и 1. Система булевых функций W называется функционально полной, если для любой булевой функции f(x1, x2, ..., xn) может быть построена равная ей функция путем суперпозиции функций (x1, x2, ..., xn), взятых в любом конечном числе экземпляров каждая. Если система булевых функций содержит конъюнкцию x1x2, дизъюнкцию x1∨x2 и x, то такая система является функционально полной. Функциональной полнотой будут обладать системы булевых функций: И-НЕ: x1x2, x; ИЛИ-НЕ: x1∨x2, x. Функционально полной является система булевых функций xx 21– штрих Шеффера. Функциональной полнотой будет обладать и система, содержащая функцию ИЛИ-НЕ, стрелка Пирса, которую можно описать x 21 ∨ x . Техническим аналогом булевой функции является комбинационная схема, выполняющая соответствующее этой функции преобразование информации. Постоянные уровни электрического напряжения соответствующие представлению сигналов 0 и 1, рассматриваются, как технические аналоги констант 0 и 1. Логические операции над двоичными переменными реализуются схемами, которые называются комбинационными логическими элементами. Число входов комбинационного логического элемента соответствует числу аргументов, воспроизводимых им одной или несколькими булевыми функциями. В свою очередь комбинационная схема строится из элементарных схем, называемых логическими элементами. Последовательное соединение комбинационных схем соответствует подстановке в булевой функции в качестве аргументов других булевых функций. Пересоединение на входах комбинационных схем соответствует перестановке аргументов булевых функций. Схемы, в которых показаны связи между различными логическими элементами, называют функциональными. При этом сами элементы представляются условными обозначениями (смотрите рис. 2.1) И ИЛИ НЕ y= x1x2...xn y= x1∨x2...∨xn y= x x1 x2 & y x1 x2 1 y x 1 y xn xn Рис. 2.1. Условные обозначения логических элементов 7 Комплекс логических элементов обладает функциональной полнотой для построения цифровых автоматов, если он содержит функционально полный набор логических элементов с полной системой переходов и выходов. В электронных вычислительных машинах в качестве элементарных автоматов используется электронная схема триггеров. Передача информации от одного элемента вычислительной техники к другому осуществляется двумя способами: 1. Асинхронным (несинхронизируемым) способом 2. Синхронным способом, который, как правило, используется при передаче информации в устройство памяти. При асинхронном способе передачи информации входные сигналы логических элементов преобразуются с небольшой задержкой в выходные сигналы, которые передаются в другие комбинационные схемы. При синхронизируемом способе передачи информации входные сигналы воздействуют на запоминающие логические элементы в строго определенные моменты времени, которые соответствуют появлению синхронизирующих импульсов. Передача информации между запоминающими логическими элементами в общем случае требует выполнения следующего условия. Как правило, она производится после завершения передачи информации о предыдущем состоянии принимающего информацию элемента другому запоминающему элементу. Для выполнения этого условия в потенциальных схемах используется несколько серий запоминающих синхронизирующих сигналов, сдвинутых во времени относительно друг друга таким образом, чтобы в том случае, когда сигнал одной серии принимает значение 1, сигнал другой серии был равен 0. Системой или комплексом или серией логических элементов ЭВМ называется предназначенный для построения цифровых устройств функционально полный набор логических элементов, объединяемых общими электрическими, конструктивными и технологическими параметрами, использующий одинаковый тип представления информации и одинаковый способ межэлементных связей. Контрольные вопросы к лекции No 2 1. Опишите работу цифрового автомата. 2. Что необходимо указать для однозначного задания цифрового сигнала (перечислить 5 пунктов)? 3. Опишите поведение цифрового автомата Мили. 4. Опишите поведение цифрового автомата Мура. 5. Как задать функции переходов и выходов автомата в виде графа? 6. Что такое автомат с полной системой переходов? 7. Что используется в качестве запоминающих элементов при построении узлов и элементов ЭВМ? 8. Когда система булевых функций является полной? Приведите примеры функционально полных систем булевых функций. 9. Что является техническим аналогом булевой функции? 10. Перечислите логические элементы, напишите их функции и нарисуйте условные обозначения. 11. Опишите асинхронный способ передачи от одного элемента вычислительной техники к другому 12. Опишите синхронный способ передачи от одного элемента вычислительной техники к другому 13. Что такое система логических элементов ЭВМ? 8 Лекция No 3 Триггеры Триггер является основным элементом, на базе которого строятся различные элементы и устройства вычислительных машин. Триггер может находиться в одном из двух устойчивых состояний. Одному из этих состояний условно присваивается значение 1, другому значение 0. Состояние триггера распознается по его выходному сигналу. Под влиянием входного сигнала триггер скачкообразно переходит из одного устойчивого состояния в другое, при этом изменяется уровень напряжения его выходного сигнала. Как правило, в схемах вычислительных устройств триггеры имеют Q(x) два выхода: прямой Q(x) и инверсный . В единичном состоянии триггера на его прямом выходе – высокий уровень выходного сигнала, на инверсном выходе – низкий уровень выходного сигнала. В интегральных схемах триггер и схема, которая управляет его входами, выполняются на одном кремниевом кристалле. Как правило, на одном кристалле выполняется несколько триггеров, до нескольких тысяч. Существует несколько схем триггеров. • Схема триггеров с установочными входами или RS-триггер • Схема со счетным входом или Т-триггер • Триггер, обладающий временной задержкой или D-триггер • Универсальный или JK- триггер. Если хотя бы с одного входа информация в триггер заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронным (синхронизируемым). Если занесение информации в триггер производится без синхронизирующего сигнала, то такой триггер называют асинхронным (несинхронизируемым). RS-триггер Обозначение триггеров: а) Синхронизируемый однотактный триггер с дополнительными входами s и r несинхронизируемой установки. Смотрите рис. 3.1. S TT x1 C x2 R Рис. 3.1. Схема синхронизируемого однотактного триггера б) Синхронизируемый двухтактный триггер с дополнительными входами S и R несинхронизируемой установки. Смотрите рис. 3.2. Рис. 3.2. Схема синхронизируемого двухтактного триггера QQ S TT x1 C x2 R Q Q 9 в) Функциональная схема RS-триггера на элементах ИЛИ, НЕ. Смотрите рис. 3.3. R11 S QQ Рис. 3.3. Функциональная схема RS-триггера Приняты следующие условные обозначения: Т или ТТ – обозначают одно- или двухтактный триггер До поле может быть разделено на части: асинхронную и синхронную. В асинхронной части проставляются несинхронизируемой установки триггера в 1 и 0. В синхронной части отмечаются входные сигналы x1 и соответствии с типом триггера. Для входов используются следующие обозначения: S – вход установки триггера в 1; R – вход установки триггера в 0; T – вход триггера со счетным входом; D – вход D-триггера; J – вход для синхронизируемой установки состояния 1 в JKтриггере; K– вход для синхронизируемой установки состояния 0 в JK-триггере; C – вход синхронизации. Состояние триггера определяется сигналом Q на прямом выходе триггера. Законы фун триггера задаются таблицами переходов, в которых в столбце состояний должно быть указано совп состояние триггера с предыдущим или нет. Асинхронный RS-триггер. Образован из двух комбинационных схем ИЛИ-НЕ, соединенных так возникают положительные обратные связи, благодаря которым в устойчивом состоянии выходной транз схемы ИЛИ-НЕ закрыт, а другой открыт. Для этого триггера таблица переходов выглядит следующим о R S Q Примечание 0 0 Q Хранение информации 0 1 1 Установка 1 1 0 0 Установка 0 1 1 – Запрещено При наличии 1 на входе R и на входе S, на прямом и инверсном выходах устанавливается Триггерное кольцо превращается в два независимых инвектора, а триггер может устанавливаться в л произвольно. Поэтому такая комбинация запрещена. Функционирование этого триггера может следующим выражением: Q(t+1)=S(t)∨Q(t) )t(R 10 S(t)R(t)=0 t – момент времени, предшествующий смене состояний триггера. Синхронный RS-триггер. Таблица переходов для синхронизируемых входов R и S. R S Q Примечание 1 1 Q Хранение информации 1 0 1 Установка 1 0 1 0 Установка 0 0 0 – Запрещено Рис. 3.4. Функциональная схема синхронизируемого однотактного RS-триггера На рисунке 3.4 представлена схема синхронизируемого однотактного RS-триггера на эл Элементы 1 и 2 образуют схему входной логики асинхронного RS-триггера, построенного на элемен триггер имеет два информационных входа: R и S, и вход синхронизации C. Этот триггер м несинхронизируемые входы R и S. В соответствии с таблицей работа триггера осуществляется при сигнале синхронизации C=1 Контрольные вопросы к лекции No 3 1. Что такое триггер? 2. Какие существуют разновидности триггеров? 3. В чем отличие синхронны асинхронных? 4. Чем определяется состояние триггера? 5. Как задаются законы функционирова 6. Расскажите об устройстве асинхронного RS-триггера. 7. Нарисуйте схему синхронизируемого RS-триггера и его таблицу переходов. SCR R &&12&&34 QQ QQ 11 Лекция No 4 Триггеры (продолжение) Двухтактный RS-триггер Рис. 4.1. Условное обозначение двухтактного RS-триггера Двухтактный RS-триггер построен на элементах И-НЕ. Эта схема состоит из двух однотактных инвертора в цепи синхронизации. При поступлении на вход этого триггера сигнала синхрониза информация заносится в первый однотактный RS-триггер, при этом во втором однотактном три информация, которая относится к предыдущему временному периоду. По окончании действия сигнала когда С=0, первый RS-триггер переходит в режим хранения, а второй – принимает то же состояние, результате к следующему моменту времени на выходе RS-триггера появится сигнал нового состояния. Таблица переходов для двухтактного RS-триггера t t+1 R S Q Примечание 0 0 Q(t) Хранение информации 1 0 0 Установка 0 0 1 1 Установка 1 1 1 – Запрещенное состояние Именно поэтому из схем двухтактных триггеров можно строить произвольные схемы и в том сигналы с выхода триггера на его вход. Для установки триггера в состояние нуля или единицы без синхронизации в схему вводят дополнительные инверсные входы S и R несинхронизируемой устано триггеров представляет собой основу для построения других триггерных схем, таких как T- триггер, триггеры. S TT S C R R Q Q 12 Т-триггер S TT TT Q & R Q & Рис. 4.2. Несинхронизируемый T-триггер Рис. 4.3.Синхронизируемый T-триггер Т-триггер может быть построен с использованием двухтактного синхронизируемого RS-триггера. схема несинхронизируемого T-триггера (рис. 4.2.) приводит к записи в двухступенчатый RS-тригге противоположного ранее хранимому. При этом, так как триггер двухступенчатый, на его выходе сигна только по завершении действия сигнала t=1. Это исключает возникновение генерации в схеме с обра В данной схеме единичный входной сигнал представляется спадом сигнала t=1 и при любой продол сигнала t=1 изменение состояния T-триггера происходит только один раз при снятии сигнала. При необходимости представлять потенциалом последовательность единиц на входе T-триггера и вторая схема двухтактного синхронизируемого RS-триггера (рис.4.3.). Единичный входной сигнал представляется высоким уровнем сигнала t при наличии сигнала синхронизации C=1. Высоким уровн можно представить последовательность единиц. Причем смена состояния такого триггера проис окончания действия сигнала синхронизации при t=1. Состояние триггера изменяется на противополо состояние триггера не меняется. D-триггер Рис. 4.4. Синхронизируемый D-триггер D-триггер является интегральной схемой, которая реализует функцию временной задержки. D-т только режимы установки 1 и 0, и в этой связи несинхронизируемый D-триггер реализует функ входного сигнала. Синхронизируемый D-триггер задерживает распространение входного сигн паузы между синхросигналами т.е. осуществляется задержка на пол периода. Для задержки на по используются схемы двухтактных D-триггеров. D-триггер вносит запаздывание Q(t QQ SCR SCR T D 13 JK-триггер Рис. 4.5. Условное обозначение JK-триггера Рис. 4.6. Функциональная схема JK-триггера У JK-триггера имеются входы несинхронизируемой установки R и S, с помощью которых при отсутс синхронизации триггер может быть установлен в состояние 1 путем подачи R=1 и S=0 либо в состоя подачи R=0 и S=1. В том случае, если на входы R и S подаются единичные сигналы, которые состояние схемы, работа триггера осуществляется под воздействием синхронизируемых входов. В схема функционирования триггера описывается следующей таблицей переходов. t t+1 J K Q Примечание 0 0 Q(t) Хранение информации 0 1 0 Установка 0 1 0 1 Установка 1 1 1 Q(t) Функцию переходов можно представить в виде булевой функции Q(t+1)= ∨ )t(Q)t(K )t(Q)t(J при услови триггер удобен своей универсальностью, так как при различных вариантах подключения его входов реализованы схемы таких триггеров, как D-триггер, T- триггер, RS-триггер и т.д. (рис. 4.7) S TT J C K R Q Q & J TT TT QQ K &SCR 14 TT QQ D J TT TT TQQ S TT J TT J Q 1 C K C K R K Q TT C а) б) в) Рис. 4.7. Схемы D-триггера (а), Т-триггера (б) и RS-триггера (в), реализованные на базе JK-триггера 15 Регистры Регистром называется устройство, предназначенное для запоминания машинного слова, а также дл выполнения над словом некоторых логических преобразований. Регистр представляет собой совокупность триггеров, число которых соответствует числу разрядо также вспомогательных схем, обеспечивающих выполнение следующих операций: 1) Установка регистра в 0 или сброс; 2) Прием слова из другого устройства; 3) Передача слова в дру или устройство; 4) Сдвиг слова вправо или влево на требуемое число разрядов; 5) Преобразование последовательного кода слова в параллельный и наоборот; 6) Поразрядные логические операции. Могут быть построены различные функциональные схемы регистров. xn S S T S S R R n RR Рис. 4.8. Схема регистра, построенная на RS-триггерах На рисунке 4.8 показана возможная вариация построения схемы регистра на нескольких RS-триггерах триггеров соответствует разрядности n. Необходимым условием является наличие сигнала синхрон которая устанавливает триггер в нужное состояние независимо от той информации, которая в нем хр правило, операция передачи кода с регистра объединяется с операцией приема этого кода в др Операция сдвига кода – перемещение в регистре всех разрядов кода слова на одинаковое число ра или вправо. В этом случае разряды слова, вышедшие из разрядной сетки регистра теряются, а в осво разряды регистра записываются нули. Рис. 4.9. Условное обозначение регистра Tn S nx n ⋅⋅⋅ x nn ⋅⋅⋅ Прием Вход Выход 1 2 3 ... n 1 2 3 ... n C Прием 16 Контрольные вопросы к лекции No 4 1. Расскажите об устройстве двухтактного RS-триггера. 2. Почему из схем двухтактных триггеров строить схемы? 3. Как устроен T-триггер? 4. Каким образом D-триггер реализует функцию време задержки? 5. Как устроен JK-триггер? 6. Нарисуйте схемы триггеров, которые можно реализоват триггера. 7. что такое регистр? 8. Перечислите операции, выполняемые регистром 9. Что такое о сдвига кода в регистре? Что при этом происходит с разрядами слова? 17 Рис.5.1. Схема регистра сдвига на однотактных RS-триггерах. Сигналом Сдв(t1) код в регистре передается со сдвигом с выходных триггеров на выход соседних разрядов. Сигналом Сдв(t2) переписывается информация с выходных триггеров на выходн разрядах. По времени эти сигналы не совпадают. Регистры выступают как устройства памяти. В состав регистры выполняют функции общего назначения и специализированные. Лекция No5 Регистры (продолжение) 18 Рис.5.2. Функциональная схема дешифратора. Рис. 5.3. Условное обозначение дешифратора Дешифратор – комбинационная схема с несколькими входами и выходами, преобразующая к подаваемый на входы в сигнал на одном из выходов. Если на входы дешифратора подаются двоичные переменные, то на одном из выходов вырабатывается сигнал, соответствующий 1, а на остальных выходах сохраняются сигналы, соотве общем случае дешифратор с n входами имеет 2n выходов, т.к. n-разрядный код входного слова може различных значений и каждому из этих значений соответствует сигнал 1 на одном из выходов деш выходах дешифраторов с номерами от 0 до 2n-1 вырабатываются значения булевых функций следующ Дешифраторы 19 xx xx=f 121-nn0 K xx=f 121-nn1 Kxx xx=2f 121-nn Kxx LLLLLLLL xx=f 1-2 n 121-nn Kxx Дешифраторы устанавливаются в схемах вычислительных устройств, на выходах рег счетчиков и служат для преобразования кода слова, находящегося в регистре или счетчике, в управ сигнал на одном из выходов дешифраторов. На рисунке 5.2 показан способ построения дешифратор инверсными выходами для 3-разрядного входного слова. Схема представляет собой набор из восьм элементов И-НЕ, на входы которых поданы все возможные комбинации прямых и инверсных значен слова. Если каждый выходной элемент дешифратора имеет вход для сигнала синхронизации, то так дешифратор называется синхронизируемым, и при сигнале синхронизации С=1 все выходы такого дешифратора будут иметь единичное значение, а при сигнале С=0 он будет работать также, как и д инверсными выходами. Из логических элементов, выполняющих функции дешифраторов можно строить дешифраторы на бо входов, при этом используются дешифраторы с инверсными выходами и инверсными входами син Для наращивания числа дешифрируемых переменных используют каскадное включение таких схем Рис.5.4. Схема каскадного включения дешифратора 20 Рис.5.5. Схема мультиплексора на четыре входных канала Мультиплексором называется схема, осуществляющая передачу сигналов с одной из входных линий Выбор входной информационной линии производится кодом, поступающим на управляю мультиплексора. Мультиплексор имеет k управляющих входов и имеет 2k информационных линий ( Функция, реализуемая мультиплексором, может быть представлена выражениями: 1100 1-21-2 xx=y 02-k1-k102-k1-k002-k1-k K Dx ∨ xx K Dx ∨ xx K =Dx 1-2 k k Rj – конъюнкция, равная 1 на наборе значений переменных, т.е наборе, представляющем в двоичном виде число j. Эта функция – нелинейна, немонотонна, несамодвойственна и, согласно теореме о функциональной полноте, позволяет при использовании констант единицы и ноль путем суперпозиций реализовать любую булеву функцию. Синтез комбина схем на мультиплексорах удобно осуществлять с помощью теоремы разложения. Эта теорема позв представить любую булеву функцию по двум переменным x и R, которая позволяет в свою очередь, синтезировать различные схемы на мультиплексоре. Корпус микросхем, как правило, может содержать несколько тысяч мультиплексорных с мультиплексора может быть, как прямым, так и инверсным по отношению к сигналам информа Мультиплексор может быть снабжен входом синхронизации (или выборки). Число управля мультиплексора, как правило, находится в пределе от 1 до 16, при необходимости построения муль с большим числом входов строятся каскадные схемы. k DR= ∨ DR ∨ RjDj ∨ DR Мультиплексоры 21 Контрольные вопросы к лекции No 5 1. Какие функции выполняют регистры в составе процессоров? 2. Что такое дешифратор? 3. Нап значения булевых функции, вырабатываемых на выходах дешифраторов с номерами от 0 до 2n-1 4. Для чего используются дешифраторы? 5. Для чего используют каскадное включение дешифраторов? 6. Что такое мультиплексор? 7. Напишите функцию, реализуемую мультиплексором. Каким может быть выход мультиплексора? 22 Q 1 Q 2 Q3 Q4 TT 3 JCK TT 4 TT 1 TT 2 J J C C K K J C K Рис.6.3. Синхронный последовательный суммирующий счетчик на JK-триггерах Счетчик – узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используют образования последовательности. Счетчики подразделяются на: • суммирующие; • вычитающие; • реверсивные. Схемы несинхронизируемого счетчика с последовательным переносом (рис.6.1) построена на JK которых на входы J и K подаются сигналы соответствующие двоичной единице. Выход каждого п триггера соединен с входом синхронизации Лекция No6 Счетчики Рис.6.1. Несинхронизируемый двоичный счетчик с последовательным переносом Рис.6.2. Параллельный синхронный счетчик на JK-триггерах 23 Cn последующего триггера. Каждый JK-триггер выполняет функцию несинхронизируемого тригг входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разря противоположное. В последующих разрядах аналогичное действие выполняет математическую опер единицы в старший разряд. Как правило, счетчик имеет цепь установки в нулевое состояние. Начал счетчика не обязательно может быть нулевым. Начальное состояние может быть задано перед некоторого числа, с которого затем будет начинаться операция подсчета единиц. Такой режим раб счетчику при образовании последовательности адресов команд при заданном исходном адресе. С рост счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности с возрастать задержка поступления сигнала на вход синхронизации некоторого j-го разряда относитель входного сигнала x счетчика на вход синхронизации младшего разряда счетчика. Чтобы повысить быстродействие счетчиков часто используется схема с параллельным перен Особенностью данной схемы является то, что выходы всех предшествующих разрядов подаются на триггера. Длительность переходного процесса в таком счетчике равна длительности переключения од возрастанием порядкового номера триггера увеличивается число входов в элементах i JK- триггеров входов J и K и нагрузочная способность триггеров ограничены, то разрядность счетчика с параллель невелика (8, 16 разрядов). Поэтому при числе разрядов счетчика большем максимального числа входо разбивают на группы и внутри каждой группы строят цепи параллельного переноса. В тако последовательном переносе возрастает разрядность счетчика. Рис. 6.4. Обозначение двоичного счетчика на электрических схемах 24 Сумматоры Наиболее часто выполняемой математической операцией при обработке информации в эле машин является операции суммирования двух или более чисел. По правилам арифметики числа системах счисления как двоичные, так и десятичные, суммируются по разрядам, начиная с младших. В слагаемых суммируется бит первого слагаемого с битом второго слагаемого с учетом переноса из пр разряда. Для того чтобы организовать выполнение операции суммирования следует предусмотреть с входа. Если предположить, что одно слагаемое х, второе y, а перенос p, то разрядами для синтеза сум yi и pi. Функции, формируемые сумматором будут: cумма Si и перенос в следующий более старш Алфавит выходных функций для каждого разряды состоит из Si и pi +1, где первое – это разрядное су перенос в следующий более старший разряд. Сумматор – узел ЭВМ, который обеспечивает выполнение математических операций (сложе кодов чисел. Как правило, сумматор представляет собой комбинацию одноразрядных суммирующих сх yi pi xi СМ Si pi+1 Рис.6.5. Схема одноразрядного сумматора на три входа Рис.6.6. Функциональные схемы цепей формирования разрядной суммы Si (а) и переноса рi+1 (б) 25 Быстродействие одноразрядного сумматора характеризуется временем установления выходн суммы и переноса после установления сигналов на входы сумматоров. Для обработки информации в современных ЭВМ производится обработка информации не то арифметических операций, но также и по правилам логических операций, которые необходимо выполня компьютеру функций искусственного логического интеллекта. Как, правило, логические операци поразрядно и поэтому для выполнения различных операций процессором электронных вычислительных одноразрядных сумматоров необходимо наличие управляемых логических цепей, выполняющих логи двух переменных. Разрядная логическая цепь, выполняющая функцию одноразрядного сумматора, и логических цепей функции двух переменных, называется одноразрядным арифметико-логическим устр Функций логических переменных может быть не более 16 и, следовательно для реализации из 16 достаточно иметь мультиплексор на 16 каналов. При этом на информационные входы м необходимо подавать функции от F0 до F15, а на управляющие входы подаются управляющи определяющие вид функции двух переменных, которые подаются на единственный выход мультиплекс Рис.6.7. Функциональная схема ондоразрядного АЛУ, формирующего значения сумм Si, переноса pi+1 и любой ф шестнадцати функций двух переменных Обработка производится n-разрядных параллельных кодов чисел. При таком способе обрабатываются сразу все n разрядов. Чтобы обеспечить выполнение этих операций устройства ЭВ входы для всех n разрядов числа. Обрабатывающим устройством является параллельный n-разря который составляется из n одноразрядных сумматоров на три входа. На входы всех одноразрядных су разрядов слагаемых подаются одновременно. Однако разрядные суммы Si будут формироваться не од как сумма второго разряда с номером 1 будет формироваться только тогда, когда на нее поступит пере разряда. Перенос поступает с задержкой на время, определяемое интервалом выполнения процеду связи с задержкой времени формирования переноса процесс сложения может быть организован за счет полусумм, которое будет определяться, как время распространения переноса, которое зависит от колич сумматора. Такой сумматор, у которого формирование суммы происходит с задержкой на время переноса, называется параллельным сумматором с последовательным переносом. Другой тип сумматора, в котором переносы из разряда в разряд формируются одновре разрядах, называют параллельным сумматором с параллельным переносом. Как правило, реализов такие операции полностью не удается. Быстродействие такого сумматора велико, но при этом разрядности обрабатываемых чисел. В настоящее время используют параллельные сумматоры с 26 групповыми параллельно-последовательными переносами, у которых внутри групп перенос осуществл параллельно, а между группами последовательно. Рис. 6.8. Структура параллельного сумматора с групповыми параллельно – последовательными переносами 27 Контрольные вопросы к лекции No 6 1. Что такое счетчик? 2. Какие типы счетчиков существуют? 3. С чем связано понижение предель работы счетчика с последовательным переносом при росте разрядности счетчика? 4. Какая схема используется дл быстродействия счетчика? 5. В чем недостаток схемы с параллельным переносом? Что предпри его устранить? 6. Что такое сумматор? 7. Назовите: а) разряды, необходимые для синтеза сумматора; б) функции, формируемые сумматором; в) ал выходных функций сумматора. 8. От чего зависит быстродействие сумматора? 9. Почему логиче двух переменных может быть не больше шестнадцати? 10. Как работает параллельным сумматором с последовательным переносом? От зависит его быстродействие? 28 Лекция No7. Процессоры ЭВМ Процессоры современных ЭВМ ориентированы на обработку информации и упра вычислительного процесса. Процессоры являются основой ЭВМ, основная особенность его функцион программируемость работы. Под архитектурой микропроцессора понимается его схема техническа организация. Основным узлом микропроцессора является арифметико-логическое устрой непосредственно предназначено для выполнения технических и логических операций с данными. микропроцессоры современных ЭВМ могут быть представлены, как два взаимодействующих модуля, из выделить устройство управления (УУ) и арифметико-логическое устройство (АЛУ). Выходная шина РОН Условные обозначения: РОН – регистры общего назначения; РгБ – буферный регистр; РгСдв – регистр сдвига; Рис.7.1. Структурная схема обрабатывающей части микропроцессора В состав обрабатывающей части микропроцессора входят: • блок регистров общего назначения, который часто называется сверхоперативным запоминающим • буферный регистр; • регистр сдвига. Регистры общего назначения предназначены для хранения информационных слов, подлежащ АЛУ. Здесь же хранятся промежуточные результаты обработки информации и управляющие слова. Р назначения допускают считывание и запись информации, для чего предусмотрена их связь с выходной указания адреса, а также содержат управляющий вход, сигнал на котором создает режим работы микро запись, хранение или чтение информации. Информация из регистров общего назначения может либо непосредственно поступать в АЛУ, быть предварительно помещена в буферный или сдвиговый регистры, АЛУ РгБ РгСдв Входная шина 29 которые служат для предварительного хранения информации или осуществляют сдвиг информации непосредственно перед обработкой в АЛУ. В обрабатывающей части микропроцессора при подаче соответствующих управляющих сигналов во выполнение следующих операций: • передача данных из одного РОН в другой (1-ый РОН → буферный регистр → АЛУ → 2-ой РОН); • увеличение или уменьшение на 1 содержимого любого РОН путем изменения в АЛУ выбран значения на 1 и засылки полученного результата в тот же регистр (в процессорах “Intel” эти функци функция инкремента–декремента); • сдвиг содержимого любого РОН на определенное количество разрядов путем передачи выбранног РгСдв, сдвига этого числа и записи через АЛУ в тот же РОН; Выполнение этих операций возможно т поступлении управляющих сигналов, которые соответствующим образом распределены во времени выполнения операций определяется частотой поступления тактовых синхронизирующих сигналов. Д управления выполнением операций, выбором команд программы в необходимой последовательнос дешифровки и обработки составляющих модулей служат входящие в микропроцессор устройства уп Упр. МП сигналы Вход Выход Признак Управляющи микроком е анд Микрокоманды ЗУ Адреса Условные обозначения: МП – микропроцессор; ДШ – дешифратор; ЗУ – запоминающее устройство. Рис.7.2. Микропрограммная схема управления Вход Выход Упр. МП сигналы ДШ микроком Признаки и анд условия Рис.7.3. Схема управления с фиксированной системой команд 30 В настоящее время применяются микропроцессоры с двумя типами устройств управления: • микропрограммным управлением (рис.7.2); • с фиксированной системой команд (рис.7.3). Микропрограммным способом управления позволяет легко вносить изменения в с микропроцессора путем записи в запоминающее устройство микропрограммы выполнения новой пр устройства управления имеют недостатки, вызванные ограниченностью скоростью быстродействия ми быстродействие управляющего запоминающего устройства. В микропроцессоре с фиксированной системой команд управляющий блок расшифровывае команду и в соответствии с ее кодом вырабатывает управляющие сигналы в необходимой после Расшифровке поддаются только те команды, которые входят в систему команд данного микропроцессор организации управления получил название жесткого или схемного. К недостаткам такого способа управл жесткость и сложность структуры управляющего устройства. Положительным качеством явл быстродействие такой схемы управления. Команды, составляющие программу управления, размещаются во внешнем запоминающ команд. Микропроцессор обеспечивает выборку команд в необходимой последовательности с и дешифровкой и выработкой управляющих воздействий. Для выполнения таких функций микропроцессо • программный счетчик, хранящий текущий адрес команды; • регистр команд, предназначенный для хранения команд управления. Для обработки информации в микропроцессоре, который построен на жесткой системе упра предусмотрено наличие запоминающего устройства команд, предназначенного для хранения ком информации. Команда, выбранная из ЗУК, поступает в буфер данных, а затем на регистр команд расшифровывается дешифратором команд. После расшифровки код выполняемой операции передает управления выполнением операций. Устройство выполнения вырабатывает последовательность сигналов. В настоящее время существуют микропроцессоры с различным количеством внутренних шин трехшинной организации микропроцессор может выполнять логические и арифметические операци работы микропроцессора. Преимуществом трехшинной организации является высокая скоро информации, а также разделения информационных потоков на три, т.е. на поток команд, поток данных и С соответствующими потоками могут быть связаны соответствующие шины. Могут быть выделены: шин адресов и шина команд (или управляющая шина). Недостатки: большая площадь, которую зани поверхности кристалла (до 40%). При одношинной организации, когда весь информационный поток передается по одной ш занимаемая шиной, не превышает 10% от всей площади кристалла, но выполнение операций услож необходимости введения дополнительных регистров. Выполнение различных операций мик осуществляется в результате выполнения команд. В зависимости от архитектуры микропроцессора вы • команды изменения содержимого ячеек памяти, • команды изменения содержимого регистра-аккумулятора, • команды выполнения операций с памятью-стеком, • команды выполнения операций в АЛУ, • команды изменения содержимого регистра состояний. Чем больше команд способен выполня микропроцессор, тем эффективнее может быть реализован алгоритм решения какой-либо прикладной правило, 31 конкретный тип микропроцессора может быть предназначен для конкретной области применения. К системе команд, микропроцессоры различаются организацией режима прерываний. ОЗУ БД ЗУК Шина А АЛУ РОН АЛУ РНК ПС РгБ РгСдв ДшК Система управления Шина В Рис. 7.4. Структура микропроцессора, который построен по жесткой схеме управления. 32 Контрольные вопросы к лекции No 7 1. Назовите основную особенность процессора ЭВМ. 2. Что понимают под понятием «архитектур Какие компоненты входят в обрабатывающую часть микропроцессора? 4. Назовите функцию рег назначения. 5. Выполнение каких операций происходит в микропроцессоре? 6. По какому пути о передача данных из одного регистра общего назначения в другой? 7. Назовите два типа устройств управления микропроцессоров. Чем они от друг от друга? 8. Назовите недостатки микропрограммного способа управления. 9. Назовите нед микропроцессора с фиксированной системой команд. 10. Где размещаются команды, составляю программу управления? 11. Расскажите о микропроцессоре, который построен на жесткой систе 12. Перечислите команды микропроцессора. 33 Лекция No 8 Процессоры (продолжение) В полиграфии наибольшее применение в настоящее время находят компьютеры фи использующие микропроцессоры фирм Intel, Motorola. Процессоры фирмы Intel на сегодняшний день применяются в ПК, применяемых в полиграфии. Фирма Intel выпускает микропроцессоры, используемые ЭВМ, с 1978 года. Эти микропроцессоры образуют семейство связанных между собой общими принципа фирм таких, как AMD, Cerics и др., разрабатывают и изготовляют процессоры-клоны, о которых го являются Intel-подобными микропроцессорами. В основе особенности архитектуры микропроцессоров Intel лежит распределение зон операти сегменты, которые специализируются по применению, а именно сегменты данных, сегменты кодов, се т.д. Адреса обращения к этим сегментам формируются с использованием различных аппаратны характерная особенность отражается на структуре команд и на архитектуре построения микропр совместимости с микропроцессорами фирмы Intel необходимо полное соблюдение стандартов, разр этой платформы. Важной стороной микропроцессоров фирмы Intel является их «совместимость сверху» использовать богатый комплекс программных продуктов, которые созданы для ЭВМ, построе микропроцессоров более ранних версий. Это может быть возможно только в том случае, когда сохра команд микропроцессоров. В то же время система команд компьютеров старшего типа использует д команды, которых нет в микропроцессорах ранних версий. Фирмой Intel так организована система кома команд процессоров, выпущенных ранее, является подмножеством команд компьютера старшего тип фирмы Intel утверждают, что компьютеры младших моделей являются составной частью от моделей Например, при оценке производительности процессоров, производительность микропроцессора Intel 8 единицу, и производительность остальных микропроцессоров оценивается исходя из этих предположе Рис. 8.1. Примерные характеристики ЭВМ типа PC IBM 34 На рис. 8.1 по оси ординат указаны номера или наименования процессора и его производительност ICOMP (Intel Comparative Microprocessor Performance), выводимому по результатам нескольких испытаний и довольно объективно характеризующему относительную производительность. Производительность процессоров 80086, 80186 и 80286 не оценивается, т.к. производительность i80 за единицу, а производительность 80186 и 80286 интереса не представляет. Кроме того, проц выпускался только опытной партией и промышленного значения не имел. В дальнейшем он рассма будет. По оси абсцисс указаны количества транзисторов в корпусе, из которых изготовлены процес стоящие на этой оси, умножаются на 103. Внутри прямоугольников рисунка по оси ординат указаны объемы внутренней памяти, к кот произвольно обращаться процессор. Там же внутри прямоугольников указаны разрядности шин данн (nd – nа). Для оценки вычислительной мощности микропроцессоров следует оценивать разрядность шин данны Разрядность шины данных определяет возможности компьютера передавать информацию от зап устройства к процессору, либо от процессора к запоминающему устройству. Эта характеристик важное влияние на производительность компьютера. С другой стороны точность вычислений о разрядностью данных. Таким образом, для обеспечения вычислений с заданной точностью, дан представляться соответствующим числом разрядов, число разрядов при этом может оказаться бо разрядов шины данных. В этом случае информация из запоминающего устройства в процессо пересылается за несколько циклов шины данных. Такие многократные пересылки снижают произво процессора, так как информацию можно обрабатывать только после поступления всех разр Разрядность шины адресов определяет адресное пространство запоминающего устройства, процессор обращается с произвольным доступом, т.е. к ячейке по любому адресу адресного п непосредственно. Адресное пространство в свою очередь определяет емкость запоминающего устро наглядно это характеристика представлена в таблице: Тип процессора Важной характеристикой процессоров, определяющей не только его быстродействие, но и не теплоотвода для обеспечения нормального температурного режима работы, является тактовая ускорения обработки информации микропроцессором проводятся работы по повышению такто обработки информации. С другой стороны повышение тактовой частоты приводит к увеличению микропроцессора. Микропроцессор Intel 80486 содержит более 300 000 транзисторов, потребляющих суммарный ток тактовая частота доходит до 130 МГц. Для обеспечения нормального температурного режима теплоо микропроцессора осуществляется за счет установки специального вентилятора, который уста непосредственно над корпусом микропроцессора. Процессоры Pentium разработаны на более низкое Разрядность АП Емкость ЗУ в байтах Емкость ЗУ в килобайтах Емкость ЗУ в мегабайтах Емкость ЗУ в гигабайтах 80068/80086 286 386/486 Pentium Pentium Pro 20 24 32 32 36 1 048 576 16 777 216 4 294 967 296 4 294 967 296 68 719 476 736 1 024 16 384 4 194 304 4 194 304 67 108 864 1 16 4 096 4 096 65 536 - - 4 4 64 35 питания 3,3 В. Особенностью этих процессоров является пленочный корпус, который обеспеч теплообмен. В корпусах микропроцессоров Pentium используются тактовые частоты свыше 1000 МГц и сосредоточено порядка 5,5 млн. транзисторов. Важной характеристикой микропроцессоров, влияющих на производительность, является нали процессора кэш-памяти. Задачей кэш-памяти является избавление процессора от необходимости данными или адресами к медленно- работающей оперативной памяти. Как правило, ОЗУ изготавливаются, как динамическая память, которая асинхронна процессору. В связи с тем, чт регенерации данных при соответствующем хранении. Поэтому при работе процессора с динамич неизбежны простои (циклы ожидания). Для уменьшения простоя процессора часть программ копирует из оперативной памяти. Кэш-память имеет ограниченную емкость и поэтому копируется только не программ нужных процессору в текущий момент времени. Кэш-память процессоров изгота быстродействующая статическая память с временем выборки порядка 20 наносекунд. Процессо информацию, обращается не к динамической памяти, а к быстродействующей кэш-памяти на статиче При этом, как правило, исключаются холостые циклы ожидания. Извлечение программ и данных называется попаданием, при оптимальном выборе емкости кэш-памяти достигается до 95% попадани одной текущей задачи. Если же при обращении к кэш-памяти процессор не обнаруживает команд лили д ситуация называется промахом. Промах является поводом для изменения содержимого кэш-памяти запись новых программ и данных в кэш-память. Эта операция называется подкачкой или свопинго свопинг производится из динамической памяти, значительно реже непосредственно с дисков. С производительность процессора, но, как правило, производится редко при решении одной текущей за значение имеет расположение кэш-памяти. Минимальные потери времени при обращении к кэш-пам случае, когда входы и выходы кэш совмещаются с внутренними шинами данных и адресов. Как прави добиться, размещая кэш-память непосредственно на кристалле процессора. С другой стороны больш памяти будет занимать определенную площадь на кристалле процессора. Для решения этого конфли разделяют на два уровня. Кэш-память первого уровня размещается на кристалле процессора. Кэшуровня размещается вне корпуса микропроцессора непосредственно на материнской плате. Емко второго уровня, как правило, больше емкости первого кэша. Кэш второго уровня, как правило, в статических элементах и подкачка кэша первого уровня производится из быстродействующего кэша При такой организации кэш-памяти, кэш второго уровня называется внешним, а кэш первого – внутрен что кэш второго уровня устанавливается на плате его объем может быть увеличен. При этом кэш-пам одно- иди двунаправленной. Однонаправленная кэш-память, это память только читаемая. Запись в не при загрузке оперативной памяти или кэша второго уровня. Двунаправленная кэш-память допускает к запись информации, при этом производительность компьютера повышается. Кэш-память второго уров как статическая память, при этом время выборки может составлять 12 наносекунд и меньше. 36 Наличие кэш-памяти различных уровней у процессоров иллюстрирует следующая таблица: Тип процессора Внутренний кеш (к/байт) Тип кеш (направленность) Внешний кеш (к/байт) 80086 нет - - 80286 нет - - 80386 нет - - 80486 8 ЧТ 256 Pentium 2*8 ЧТ/ЗП 512 2 При развитии архитектур микропроцессоров фирмой Intel был сделан вывод о том, что произво микропроцессора может достигаться не только за счет увеличения тактовой частоты, но и за счет изменений. Для того, чтобы совершенствовать скорость обработки информации процессором, б решение о выделении двух режимов работы микропроцессоров: • реального режима • защищенного режима. Реальный режим предполагает, что каждый последующий процессор разраб фирмой рассматривается, как микропроцессор Intel 8088. При этом все программы, составленные д процессоров с низкими номерами, будут выполняться компьютерами с более высокими микропроце каких бы то ни было переделок. Защищенный режим представляет собой особый режим работы микропроцессора для которого с специальное программное обеспечение, которые учитывают его новую структуру. Перевод п защищенный режим всегда переходит из реального режима за счет настройки некоторы микропроцессора программным способом. Выход из защищенного режима в реальный осуществляе также программным способом. Защищенный режим представляет собой режим многозадачно информации, в котором решается несколько различных задач. Разные задачи при этом могут различных операционных системах, каждой задаче при этом отводится своя часть ресурса выч системы пользование которой запрещено для других приложений. Внутри защищенного ресурса м свою очередь еще несколько ресурсов. По мере развития и совершенствования микропроцессоров фирмой Intel можно было выдели характерных особенностей. Особенностями микропроцессора Intel 80486 по сравнению с первы микропроцессоров Intel (8086, 8088) можно выделить следующие компоненты. Появились устройст микропроцессора, которые работали автономно и параллельно по времени, этими устройствами яви • устройства шинного интерфейса; • внутренняя кэш-память; • устройства, опережающей предвыборки команд; • двухступенчатый дешифратор команд; • устройство управления; • целочисленное устройство; • устройство сегментации; • устройство страничного преобразования адреса; • сопроцессор, предназначенный для обработки чисел в форме с плавающей запятой. Все перечисл устройства объединены 32-разрядной шиной данных, а также линиями управляющих связей, по кото передаются управляющий сигналы от управляющего устройства микропроцессора (рис. 8.2). При инициализации текущей задачи 37 ее программа загружается в динамическую оперативную память, при этом параллельно на обрабатываемой программы загружается в кэш-память второго уровня и через шину данных и устройство загружается во внутреннюю кэш-память. Это и есть та часть программы, которая будет об текущий момент времени микропроцессором. Рис.8.2. Структурная схема процессора PC i80x86 38 Контрольные вопросы к лекции No 8 1. Назовите основную особенность процессора ЭВМ. 2. Что такое «совместимость сверху»? 3. Ч разрядность шины данных? 4. Что представляет собой адресное пространство? 5. К чему приво тактовой частоты? 6. Назовите основную задачу кэш-памяти. 7. Как работает кэш-память? 8. В ч между одно- и двунаправленной кэш-памятью? 9. Какие существую режимы работы процессора? отличаются друг от друга? 10. Какие устройства появились в микропроцессоре Intel 80486? 39 Лекция No 9 Память Разрядность шины данных определяет возможности вычислительной системы передавать запоминающего устройства к процессору и от процессора к запоминающему устройству. Эта существенно влияет на производительность компьютера. Точность вычислений определяется разрядн Для обеспечения вычислений с требуемой точностью данные предоставляются соответств разрядов. Если число разрядов больше чем число разрядов шины данных, то информация из ЗУ в проц пересылается за несколько циклов шины данных. Разрядность шины адресов определяет адресное пространство устройства памяти, к котор обращается с произвольным доступом, т.е. к ячейке памяти по любому адресу адресного пространства В общем случае память вычислительной системы может быть представлена в ви многополюсника, который имеет соответствующую систему входов и выходов. На вход приходит инф данных и адресов, а на выходе формируются сигналы, которые передаются в процессор. Один тип входов позволяет вводить информацию в память, а выход этого многополюсник собой сформированные указания, куда будет размещаться выводимая информация, и откуда информация, выводимая из памяти. Вход для ввода информации это некоторый массив данных (na), а места хранения информации (nd). Таким образом, для ввода информации предусмотрено два в них предназначен для ввода первичной информации, т.е. для ввода программы данных, для обесп компьютера и обработки информации от внешних устройств. Другой вход предназначен для ввода процессора во время обработки информации. Память ЭВМ работает тактами. Полный такт работы называется временем обращения к памя к памяти может быть реализовано для записи информации в нее или для считывания из нее информа при одном обращении обе процедуры, т.е. записи и считывания, одновременно невозможно. Т выполняется за время T обр. При записи информации в память на вход na подается указание о том, куда в памяти информация. Затем на один из входов nd выставляется информация, подлежащая записи. После команда write. При чтении информации из памяти на вход na подается указание, откуда будет выбираться затем подается команда read. На выходе многополюсника появляется считываемая информац фиксируется процессором. Выделяют два такта обращения к памяти: 1) время обращения по записи; 2) время обращения по чтен практике, как правило, Tобр.чт = T обр.зап. Время обращения – это отрезок времени от момента устано месте нахождения информации (или о месте ее записи) до момента четкой фиксации информации пам процессором. Время обращения характеризует быстродействие памяти и соответственно характеризуе обработки информации ЭВМ. Для повышения быстродействия ЭВМ время должно уменьшаться. Вся и которая записывается в память или считывается из памяти независимо от оттого данные это или кома данными. Указания о месте расположения данных в памяти называют адресами. Под данными понима разрядное слово. Разрядность данных определяется задачей. Принято, что 40 разрядность данных определяется в байтах. Это могут быть двоичные слова, протяженностью в один ба и более байт. За основу хранения и обработки информации принимается слово в один байт. Для хранен создается специальный узел памяти, называемый ячейкой. Ячейка памяти имеет только одной ей п называемый адресом ячейки памяти. Байт данных состоит из восьми битов, принимающих значени хранения одного бита служит специальное устройство, называемое элементом памяти. Т.о. ячейка па восьми элементов памяти, объединенных одним адресом. Адрес активизирует все элементы памяти этой ячейке при обращении к памяти по этому адресу. Сигналы или от процессора подаются на все эл и определяют режим работы ячейки. Если в задаче обрабатываются данные с разрядностью больше че таких данных выделяются 2, 4 и более ячеек. Количество ячеек, выделяемое для хранения многоразр четное. Ячейки имеют адреса, увеличивающиеся на 1 от адреса начальной ячейки. При обращении за т указывается адрес начальной ячейки и количество байтов, составляющих обрабатываемые данные. обрабатываются 4-байтные данные, то обработка производится за 4 такта обращения, причем первый является полным, а последующие такты укороченными. Разрядность адресов ячеек памяти определяется на основании их количества в памяти. А должно обеспечить указания к любой ячейке памяти, разрядность адреса определяется na=log2E. Е ячеек памяти, входящих в реальное устройство памяти. Ячейки памяти образуют накопи представляет собой основной узел памяти. В свою очередь элементы памяти могут изготавливатьс принципам и по-разному объединятся в ячейки памяти. Накопители также могут формироваться по- раз принцип организации памяти и алгоритмы работы являются одинаковыми. В соответствии с общим алго простейшая ЭВМ состоит из процессора и памяти. Процессор выбирает из памяти очередную кома выбирает данные, обрабатывает эти данные по команде и отправляет промежуточный результат в памя устройство. В простейшем случае для выполнения одной команды процессор должен трижды обратит командой, за данными, отправить результат. На выполнение одной команды тратиться 3 Т обр. Ес данные и результат будут многобайтными, то время выполнения команды увеличивается еще больш емкости памяти приводит к еще большему времени обращения. Быстродействующие процессоры п работе с памятью ЭВМ. Для сокращения простоя центрального процессора память разбивают на неско которые по отношению к процессору включаются каскадом. В наиболее близком к процессору каскаде у память относительно небольшой емкости, которая обладает максимальным быстродействием. С процессор общается практически без простоев. В других более дальних от процессора каскадах распол большей емкости, с большим временем обращения. Эта память как бы подпитывает память пер практически не влияет на быстродействие процессора. Таких каскадов может быть несколько. В пос располагается память максимальной емкости, и ее низкое быстродействие слабо влияет на работу про 41 Классификация памяти В разных каскадах память может быть построена по различным принципам и может им характеристики. Классификация памяти может производиться по различным признакам. 1. Одним из важных признаков классификации является возможность хранения информации с в выключенным питанием. По этому признаку память может быть: • энергозависимой. Хранит инфор при включенном напряжении питания. К таким устройствам памяти относится вся электронная • энергонезависимая память. Сохраняет информацию при выключенном источнике питания. электромагнитная память, различного типа диодные и транзисторные матрицы, а также опти которых информация может сохраняться длительное время. 2. Другим признаком классификации является место расположения памяти. • Внутри ЭВМ – внутренняя память; • Вне ЭВМ – внешняя память. Названия внутренняя и внешняя являются условными. В настоя внутреннюю память определяют не только по месту ее расположения, а по тому, что обращение к ней по адресам, располагающимися непосредственно в командах процессора. Внешняя память, которая ра внутри системного блоку или вне его адресуется через специальные программы или программы и друг устройства. 3. Признаком классификации памяти может быть возможность записи информации в память в решения задач, к которой относится эта информация. • Если такая запись является возможной, то память называется оперативной. • Если в процессе решения задачи из памяти информацию можно только читать, то такая пам постоянной. В настоящее время только читаемую память называют ROM. В такую память инф вне цикла решения задачи. Например, при ее изготовлении на предприятии или при ее подгот задачи. Если информация может вноситься однократно, то память обозначается, ка многократно, с уф стиранием информации, то такая память обозначается EPROM, если использоваться многократно с электрическим стиранием информации, то такая память назыв Последний вид памяти называется flash-memory или флэш-память. 4. Признаком классификации является порядок выборки. • Если по адресу, выставленному на адресный вход памяти сразу находится ячейка нужного н память называется памятью с произвольным доступом. • Если такая память выполняет функции оперативной памяти, то ее называют сокращенн access memory). Если после выставки адреса производится поиск нужной ячейки просмотром ячеек, то такая память называется памятью с последовательным доступом. 42 В современных компьютерах используется еще один тип энергозависимой памяти с особым п выбираемой ячейки памяти. Ячейки памяти на всех этапах работы имеют раз и навсегда установл которые являются адресами. Другим способом адресации ячеек является присвоение каждой ячейке определенного призна записи данных в такую ячейку памяти в специальную часть накопителя записывается тэг, который явля ячейки. При выборе ячейки для считывания информации на адресный вход памяти подается адресное содержит тэг нужной ячейки памяти. Затем происходит сравнение тэгов всех ячеек накопителя с тэгом а Выбирается та ячейка, тэг которой совпадает с тэгом адресного слова. Этот тип памяти, явля произвольным доступом, называют еще ассоциативной памятью. Такой принцип выборки адресов исп памяти всех уровней. 5. По способу хранения информации • В настоящее время существуют элементы памяти, которые принимают информацию и могу тех пор, пока не будет выключено электрическое питание. Выборка и считывание информац ее содержание. Такой способ хранения информации определил название памяти, как стати Элементы статической памяти выполняются на основе кодовых триггеров, ячейкой памяти, данных, является регистр из восьми кодовых RS-триггеров, выбираемых адресным слов триггерах является энергозависимой, а ее статическая особенность указывается как SRAM. • Другой способ хранения информации предполагает, что элемент памяти может терять процессе хранения и для того, чтобы информацию не утратить, ее необходимо периодическ или восстанавливать. Процесс восстановления информации называется регенера Регенерацию производят периодически через каждые 15-20 микросекунд. Регенерируемую п динамической, если она является энергозависимой, то ее называют DRAM. В современной в технике это наиболее часто применяемая память. 43 Контрольные вопросы к лекции No 9 1. Что определяет разрядность шины данных? 2. Расскажите о представлении памяти в общем случае. 3. Что называется временем обращения к памяти? 4. Как происходят запись и чтение информации из памяти? 5. Что такое адрес? 6. Расскажите о ячейках памяти. 7. Как классифицируется память: а) по возможности хранения информации с включенным или выключенным питанием; б) по месту расположения; в) по возможности записи информации в память в процессе реше задач; г) по порядку выборки; д) по способу хранения информации? 44 Лекция No 10 Структура и общие характеристики ЭВМ Под структурой современных ЭВМ понимают состав устройств, позволяющие уяснить функци всех режимах работы компьютера. Структурно может быть отображена вся ЭВМ, какое-то ее устройство и отдельный узел. Устр входящие в структуру, представляют собой законченные в функциональном отношении автоматы, имею выходные узлы, связь между которыми описывается детерминированными зависимостями. Под архитектурой ЭВМ понимается структура компьютера, существующая в текущий моме выполнения ЭВМ конкретной задачи. Если будет решаться другая задача, то ЭВМ может быть предс структурой, в которой содержатся другие устройства и блоки, отличные от первой архитектуры. Одним предъявляемых к архитектуре, должно быть представление о функционировании ЭВМ в соответствии Устройства и блоки ЭВМ могут определяться по двум признакам: 1. функциональному; 2. конструктивному. По функциональному признаку блок или устройство – это авт которого есть входы и выходы, между которыми существуют детерминированные связи. По конструктивному признаку устройства и блоки определяются технологическим процессом. блок может содержать несколько функциональных устройств, а может содержать только часть ф устройства ЭВМ. Основными устройствами и блоками, отображаемыми в структурах ЭВМ, являются: • Арифметико-логическое устройство (АЛУ) • Управляющее устройство (УУ) • Запоминающее устройство (ЗУ) • Устройство ввода (ВвУ) • Устройство вывода (ВывУ) • Согласующее и обменное устройства (УСО) • Блок питания (БП). Управляющее устройство предназначено для управления и синхронизац устройств и блоков ЭВМ. Структурно-управляющее устройство входит в состав микропроцессора ЭВМ. Арифметико-логическое устройство предназначено для выполнения всех операций соста арифметических, логических и устройств обмена информацией с запоминающим устройством ЭВ арифметико-логическое устройство входит в микропроцессор. Устройство согласования и преобразования информации предназначено для эле энергетического согласования сигналов, формируемых ЭВМ, и входными устройствами вн воспринимающих эти сигналы. Из многообразия структур, по которым строится ЭВМ, выделяют две: • Централизованную (рис. 10.1) • Магистральную (шинную) (рис. 10.2) Все остальные структуры вычислительных комплексов собой комбинацию первых двух. По централизованной структуре разрабатываются сверхбольшие ЭВМ (мэйнфрей специализированные вычислительные комплексы. Достоинством этой структуры является устойчивос блоками, недостатками является перегрузка АЛУ процедурами операций обмена информацией меж блоками ЭВМ. 45 Рис. 10.1. Структура централизованной ЭВМ Второй тип структуры ЭВМ опирается на магистраль, состоящую из трех шин, а именно: • шину данных • шину адресов • шину управления Рис. 10.2. Структура магистральной ЭВМ Условные обозначения: ПР – процессор; СПР– сопроцессор; 46 ПЗУ – постоянное ЗУ, или ROM; ОЗУ – оперативное ЗУ, или ЗУ с произвольной выборкой адресов(RAM память – запоминающие устройства на вращающихся магнитных дисках; ГМД – дисковая память на гиб дисках – дискетах; ЖМД – дисковая память на жестких магнитных дисках (Винчестер); CD – ROM – дис читаемая память; ВвУ—устройство ввода, обеспечивающее ввод данных в компьютер, чаще всего в О устройство вывода, обеспечивающее вывод данных из компьютера во внешние устройства; КПДП – ко прямого доступа к памяти, обеспечивающий управление особым режимом прямого доступа к памяти, к устройства и дисковая память общаются непосредственно с оперативной памятью компьютера: по зап внешних устройств DACK; КПР–контроллер прерываний, обеспечивающий управление особым режимо вычислительного процесса, когда от выполнения одних программ процессор переходит к выполнению программ по запросам на прерывание от внешних устройств (сигналы IRQ) с обеспечением возможнос на прерванные программы. По шине данных пересылается информация, предназначенная для обработки во время т работы компьютера. По шине адресов выставляются адреса мест хранения информации (адреса яч шине управления передаются все управляющие и синхронизирующие ЭВМ сигналы со стороны устройс микропроцессора. Обмен информацией между всеми устройствами компьютерной системы произво данных, представляющей собой n-разрядную двунаправленную шину, по которой данные могут п процессора к любому устройству системы и от любого устройства системы к процессору. Адреса устро участвующих в обмене информацией, как правило, устанавливаются процессором. Адреса выставляют на n-разрядную шину адресов и по ней доводятся до абонентов, участвующих в обмене. В случаях пр памяти и обслуживания прерываний адреса на шину адресов выставляют контроллеры прямого доступ и контроллер прерываний. Управляющие и синхронизирующие сигналы выставляются процессором или пдп и прерываний на n-разрядную шину управления и затем доводятся до нужных точек всех элемент При такой структуре шины представляют собой не только соединительные магистрали, но и им контроллеров шинных формирователей, усилителей, регистров, дешифраторов и т. д., работающ протоколам. Такое объединение шин устройств и протоколов называют интерфейсом. Интерфейс может быть для компьютера внутренним или внешним. Через внешний интерфей подключаются дополнительные внешние устройства, прежде всего устройства ввода-вывода информ видеомонитор, клавиатура, манипулятор мышь, принтер, сканер и т. д., обеспечивающие ввод и вывод ЭВМ. Состав внешних - периферийных устройств может изменяться в зависимости от назначения и компьютера. Это могут быть различные датчики, преобразователи информации и различные устройств объектом управления. В современных компьютерах может быть несколько шин, управляемых различными проце данных адресов и управления, созданные шинными формирователями и специальными контроллерам которым подключаются внутренние абоненты компьютера, называют системными шинами. Для уск информации между процессором и основной памятью может создаваться специальная шина памяти m шины создаются по тем или иным стандартам, в соответствии с которыми производится подключе шинам процессора. 47 В настоящее время современная ЭВМ представляет собой сложное техническое устройств которого по обработке информации определяются множеством технических характеристик, отдел компьютера. Для решения различных задач вводится понятие о коммерческих характеристиках ЭВМ. К характеристикам относятся технические и стоимостные параметры, дающие общие представление о ко возможностях. В состав коммерческих характеристик компьютера обычно включают: 1) Сведения о процессо т.е. a) его наименование или товарный знак, b) указание о фирме изготовителе или разработчике, c) тактов синхронизации компьютерной системы в Гц (МГц), тактовая частота определяет скорость переключени прохождение сигналов по логическим цепям компьютера, но не всегда напрямую определяет его произ частота задается тактовым генератором, эта частота является тактовой для элементов системной пла являющийся элементом системной платы, может работать на более высокой частоте, которая формир процессора умножением основной частоты на 1,5, 2, 2,5 или 3. 2) Объем оперативной памяти, которая байтах. Объем памяти с произвольной выборкой может достигать сотне Мб и выше. Объем памяти с пр выборкой во многом определяет производительность компьютера т.к. память больших объемов позвол использовать сложные приложения по обработке данных, хранящихся в более медленных накопителях Производительность ЭВМ повышается при вводе в ее структуру сверхбыстродействующей памяти на с элементах с особыми формами обращения и выборки данных. Эта память кэш-память включается пар оперативной памяти при обработке информации и решении задач. 3) Типы шин 4) Характеристики диск их емкости, а именно a) емкость HDD, b) тип FDD, c) тип CD-rom, кратностью вращения диска по отношению к основной б скорости вращения. Технические характеристики дают полное представление о структуре и возможностях ЭВМ. процессоров важной технической характеристикой является выполняемая процессором система коман представляет собой упорядоченную последовательность команд, выполняемых ЭВМ одна за другой по обработки входной информации. 48 Команды Команда – есть четкое и строго определенное указание о действиях ЭВМ на определенном о называемом командным машинным циклом КМЦ. В команде тем или иным способом указывается и данные, которые должны быть обработаны в этой команде. Данные указываются адресами расположе устройствах ЭВМ или непосредственно содержатся в команде так называемые непосредственные данн Указания о поведении ЭВМ на командном машинном цикле называют кодом операции. Код к четко отличатся от кода предыдущей команды для отображения кода команды выделяется n двои n=log2N. N – количество команд в Qi и. Qi – система команд, которая выполняетс микропроцессором. Вторым элементом команды являются непосредственные данные или адрес неп нахождения данных. Данным в команде может быть число, адрес ячейки памяти или просто символ (имя перемен командах называются операндом. Команды могут быть безоперандовыми, одно-, двух- или трех Операнды в командах указываются адресами их расположения, тогда команды называют безадресны или трехадресными. Разрядность операндов определяется с учетом специфики операнда, если оп непосредственным данным, то его разрядность есть разрядность чисел в основном формате машины. Е является адресом, то его разрядность определяется адресным пространством, которое может просм помощи этого адреса. Адресное пространство определяет емкость запоминающего устройства. Кроме и операндов в составе команд могут содержатся различные служебные признаки. Общий вид команды этой команде в начале следует служебный признак, затем Q – код операции, A1, A2, A3 – операнды. Слу определяет особенности выполнения команды, отмеченной признаком по отношению к команде с операции, но не отмеченной или отмеченной другим признаком. Служебные признаки могут определя формирования адреса команды или операндов. Служебный признак, а также операнды являются не элементами команды. Код операции – обязательный элемент команды. Чем содержательнее команда, т в исполнении. Для непосредственного исполнения выполняемая команда и ее элементы вызываются размещаются в соответствующих узлах процессора. Процессор не может выполнять новой команды вся команда не будет целиком размещена в нем. Суммарная разрядность команд определяется как ра операции + разрядность служебного признака + разрядность операндовых и двухоперандовых ком случаях разрядность команды может оказаться больше разрядности шины данных, по которой команд из ОЗУ или кэш-памяти в процессор. Тогда пересылка команды занимает несколько циклов работы ш производительность компьютера. Во всех случаях цикл шины влияет на производительность ЭВМ. Этот параметр стандартизир является одной из характеристик ЭВМ. 49 Контрольные вопросы к лекции No 10 1. Что понимается под архитектурой ЭВМ? 2. По каким признакам определяются устройства и бл чем их особенности? 3. Назовите основные устройства и блоки, отображаемыми в структурах ЭВМ. 4. Ч выполняет управляющее устройство? 5. Что такое арифметико-логическое устройство? 6. Расск централизованной структуре ЭВМ. 7. Расскажите о магистральной (шинной) структуре ЭВМ 8. Чт внутренний и внешний интерфейс компьютера? 9. Что входит в понятие «коммерческие характе ЭВМ»? 10. Что такое команда? 11. Расскажите о синтаксисе кода команды. 50 Лекция No11 Структура процессоров Множество возможных задач, решаемых на компьютерах, может быть разделено на два подм 1. Подмножество задач, подлежащих решению на компьютерах, посредством развитой системы команд 2. Подмножество зада, решение которых обеспечивается при помощи системы команд. Для решения задач подмножества первого типа создана структура процессора instruction system command). Команды различной длины и сложности, различных форматов. Узким мест структуры является шина данных, так как длинные команды пропускаются через несколько циклов. Для решения задач второго подмножества разработаны процессоры RISC структуры. Все к укороченного формата. Процессор RISC не совместим с процессором CISC-архитектуры. Универсальной структурой для решения задач различного характера является процессор M Микропроцессор такой структуры сочетает свойства RISC и CISC архитектур. Основой процессора является структура RISC- процессора. В одном кристалле с этим процессором создается мощное микр устройство, программное подключение которого к RISC-процессору по мере необходимости преобраз CISC структуру. Для ускорения обмена информацией между микропроцессором и запоминающим устройство различные способы обращения к внешним или внутренним запоминающим устройствам. В свя организацией обращения к устройствам памяти, которые используют дополнительные программ обращение к некоторому поименованному массиву памяти, называемому файлом. Адресом обращ массиву является имя файла, а в некотором случае его атрибуты. Исполнительный адрес устройств определенную разрядность, определяющую адресное пространство, в котором может осуществлятьс доступ к ячейкам памяти. Как правило, адресное пространство составляет определенное колич зависящих от разрядности шины адресов, например, если шина адресов имеет разрядность 2 пространство составляет 1 Мб адресов. Адресное пространство в 1 Мб адресов позволяет работать с м 1 Мб. Адресом обращения к ячейке памяти является адрес байта с меньшим адресом. Это ад содержимым команды или адресным операндом. Адрес второго байта формируется автоматически данных разряда они размещаются в четырех смежный ячейках, каждая из которых хранит 1 байт. Адре слова является адрес байта с меньшим номером. Для повышения производительности ЭВМ 2 мл исполнительного адреса назначают нулевыми, такое назначение называют выравниванием по па уменьшения числа вынужденных ожиданий процессора при обработке информации он в первую очеред кэш-памяти, при этом обмен информацией осуществляется за один такт работы процессора. Учиты память может поместиться только часть обрабатываемых программ и данных производится обновлен кэш-памяти следующими участками программ и новыми данными. Такая новая информация пост оперативной памяти без обращения к накопителям на магнитных дисках. При этом процессор пере ожидания и простаивает. Для снижения количества простоев процессора в структуру ЭВМ вводят еще о которая располагается вне кристалла процессора. Такую кэш-память 51 называют кэш-памятью второго уровня. время подкачки из КЭШа второго уровня в кэш первого уровня время простоя процессора сокращается до минимума. Производительность и быстродействие ЭВМ исчисляются в количестве действий компьютер за единицу времени. Быстродействие оценивает структуру ЭВМ и физические переключательны отдельных элементов. Наиболее общей единицей оценки быстродействия и производительност является количество выполняемых операций в секунду. В настоящее время для оценки прои процессоров и компьютеров в целом существуют специальные показатели производительности. определяют относительную производительность конкретного типа микропроцессора по отношению базовому процессору. Например, фирма Интел за базовую производительность принимает прои процессора пентиум с тактовой частотой 120 МГц и условно принимают эту производительность Производительность других микропроцессоров вычисляется при работе конкретного микропроцессора системной плате при выполнении смеси типовых вычислительных операций, а именно при обработке данных, чисел с плавающей точкой, а также при обработке графиков и видео сигналов. Например, прои процессора пентиум два определяется как 303 единицы. Определение вычислительного процесса При инициализации прикладных программ ЭВМ даются все необходимые указания по обрабо информации решаемой с помощью данной конкретной программы, а именно: • Начальный адрес программы; • Имена сегментов памяти, где располагаются данные по этой задаче; • Указываются связи с другими прикладными задачами, а также различные другие атрибуты прикладной задачи. Программы начального запуска как и прикладные программы составляются практически команд, входящих в общую систему команд конкретного микропроцессора. Таким образом програ последовательности команд, в которой она в дальнейшем и будет реализована. Для выполнения к отводится строго определенное время, называемое командным машинным циклом, которое выполняе командного машинного цикла. Естественная последовательность команд программы предполагает и естественном последовательном порядке. В ряде случаев естественный порядок следования командных машинных циклов может н командой с номером i будет следовать не команда с номером i+1, а команда с номером i+y. Такой поря командных машинных циклов называется принудительным. Существует два способа реализации принудительного порядка следования команд. Первый способ называется безусловным. При этом способе вычислительный процесс, последовательностью командных машинных циклов переходит от команд с номером i к командам с ном Второй способ предполагает возможность перехода от команды с номером и к альтернативн номерами i+1 или i+y. Выбор пути перехода определяется по некоторому условию. Если это условие в переход осуществляется к команде с номером i+y, если это условие не выполняется, то переход ос следующей команде, т.е. к команде с номером i+1. Такой способ перехода вычислительного проце условным переходом. Признаков условия может быть несколько, поэтому и команд условного перехо быть несколько. Вычислительный процесс при этом может ветвиться, причем ветвление может происходить н нарастающим номерам команд, но и по убывающим номерам, т.е. 52 от команды с номером и к команде с номером i-y. Такой переход и прохождение по командным машинн однажды пройденным, называется циклами. В вычислительном процессе циклов может быть множество может повторяться большое количество раз. Подсчет количества прохождений по циклам производится счетчиками, а в некоторых специализированных ЭВМ и аппаратными счетчиками. Организация принудительного и циклического процессов перехода от команды к команде, называется вычислительного процесса. Процедура перехода от команды к команде является вычислительным про В самом общем виде командный машинный цикл можно представить в виде нескольких эта отрезки времени внутри машинных циклов, на которых аппаратурой процессора выполняются определе четких границ между этапами не существует. В процессе этапы никак не выражены и не фиксированы. микропроцессорах этапы командных машинных циклов используются для конвейеризации данн производительности ЭВМ. Наиболее общим разбиением командного машинного цикла на этапы, является разбиение, пр можно выделить 5 этапов: 1. Этап формирования адреса очередной команды 2. Этап выборки команды из оперативной размещения кода команды в процессоре 3. Этап формирования адресов операндов 4. Этап выборки кода операнда из операт или посылка операнда в оперативную память 5. Этап выполнения текущей команды На этапе формирования адреса кома очередной командой понимается команда, выполняемая в данном командном машинном цикле. При эт сформированный адрес выставляется на шину адресов и находится в ней в течение всей продолжител командного машинного цикла. Адрес очередной команды фиксируется специальным регистром адреса формирование адресов производится в соответствии со способом управления вычислительным проце управление вычислительным процессом осуществляется последовательно, то формирование номера команды реализуется счетчиком, при этом счетчик называется счетчиком команд, а процедура формир очередной команды реализуется как i+1. В том случае, если реализуется принудительный способ форм адреса очередной команды, этот алгоритм определяется как i±y. Такой алгоритм вычисления адреса, к реализую параллельным сумматором, где первое слагаемое представляет собой содержимое счетчика второе слагаемое представляет собой операнд команды безусловного или условного перехода. На этапе выборки кода команды по выставленному на регистре числу (адресу) выбирается команды и размещается в регистре кода команды процессора, где хранится до конца выполнения те Для этапа выборки кода команды на время пересылки кода магистраль процессора будет занята и пересылок информации между блоками ЭВМ выполняться не может. В этой связи введен кр производительности магистрали так называемый цикл шины, который представляет собой отрезок врем по шине данных пропускается от источника до приемника слово основного формата. Словом основного быть 1, 2, 3 или 4 байта. Затем следует этап формирования адреса операнда. Для современных ЭВМ выполняемые быть безоперандовыми, однооперандовыми и двухоперандовми. В безоперандовых командах операнда В однооперандовых командах может быть один адресуемый операнд или два операнда. Двухоперан адресуют сразу оба операнда, которые могут располагаться в процессоре. Вычисление адреса операнда производится по правилам адресации, принятым 53 для ЭВМ определенного класса. Для двухоперандовых команд один из операндов располагается в регис и его адрес может быть дешифрован по признакам, содержащимся в команде, а адрес другого о вычисляться при помощи вычислительных средств, например, Аллу самого процессора. Вычисленный выставляется на регистр адреса как и адрес команды. На этапе выборки кода операнда по установленному в регистре адресу операнд извлекается размещается в соответствующем адресе процессора. Этап выполнения текущей команды начинается с момента, когда код операции расположен команд и подключен к дешифратору кода команды, а операторы подключены, например к АЛУ. 54 Контрольные вопросы к лекции No 11 1. На какие подмножества делится множество задач, решаемых на ЭВМ? 2. Чем отличаются CIS от RISC-процессоров? 3. Почему MISC-процессор является универсальным? 4. Что такое файл? является показателем быстродействия и производительности ЭВМ? 6. Какие указания даются Э инициализации прикладных программ? 7. Назовите два способа реализации принудительного по следования команд. В чем они состоят? 8. Что представляет собой вычислительный процесс? 9. Перечислите этапы машинного командного цикла. 10. Опишите, что происходит: а) На этапе формирования адреса очередной команды; б) На этапе выборки команды из о памяти и размещения кода команды в процессоре; в) На этапе формирования адресов оп этапе выборки кода операнда из оперативной памяти или посылка операнда в оперативну На этапе выполнения текущей команды? 55 Лекция No 12 Основы формирования системных шин Шины данных предназначены для передачи информации в двух направлениях. Шинные представляют собой двунаправленные устройства. Управление шинами формирователями посредством двух сигналов: 1. Первый сигнал определяет время передачи данных. 2. Второй сигнал определяет направление пе сигнала формируются микропроцессором в каждом цикле шины. В общем случае шинный форми представляет собой n-разрядное устройство одинаковое во всех разрядах. Разрядность шинного фо определяется исходя из разрядности шины данных микропроцессора. Шинные формирователи мо составными частями в более крупные интегральные схемы, размещенные на системной плате компь интегральные схемы называют чипсетом. Они совместно с процессором выполняют объединение все единую вычислительную систему. Формирователи шин адресов В отличие от шин данных на шинах адресов выставляемые сигналы должны сохраняться значи чем входные сигналы. Шинные формирователи адресов обязательно должны иметь память. Отл формирователей адресов от шин формирователей данных является их однонаправленность. Адресные формируются микропроцессором и выставляются на шины адресов со стороны микропроцессора. Подключение формирователя шин адресов осуществляется через системный регистр, микропроцессоре. В каждом разряде системного регистра используется D- триггер. На каждый и микропроцессора подаются соответствующие разряды адреса, сформированного микропроц синхронизации триггеров объединяют между собой, образую один управляющий вход записи в сист Управляющий сигналы подаются на входы системного регистра, причем управляющим сигналом мож синхронизирующий выставку адресного слова на шину адресов. Специфика работы системного регистра в качестве шинного формирователя адресов заключается в запоминании, фиксации и хранении адреса. часто называют индексными регистрами или регистрами с защелками. В компьютерах IBM PC они выпо шинных формирователей адресов. Формирователи шин управления Шина управления представляет собой самостоятельную шину, по которой выставляются управляющие и синхронизирующие сигналы. Многие сигналы, поступающие на шину управления микропроцессором. Для того, чтобы сформировать большое число управляющих сигналов разл необходимых для управления внешними устройствами мощности микропроцессора недостаточно. Т подаются на сравнительно большие расстояния. Для того, чтобы обеспечить необходимую мощность необходимо иметь достаточную площадь проводников, подводящих эти сигналы к выходам из микропр локальную шину. Во многих управляющих сигналах, выставляемых на шину управления процессором, м сигналы, повторяющие сигналы частоты системной платы по длительности и форме, сигналы инвер сигналам частоты системной платы, сигналы большей длительности, чем сигналы системной платы. 56 Шинный формирователь представляет собой усилитель мощности. Сигналы от шинного могут формироваться как сигналы, аналогичные сигналам системной шины, как сигналы инверсные и м большей длительности. Усилители, входящие в шинный формирователь, усилители-инверторы и блокиобъединяются в контроллеры, составляющие системные шины, шины ввода- вывода и шины контроллеры называют мостами. Например, мост, который называется системный контроллер и буф данных в зависимости от цикла микропроцессора организует обмен данными между локальной шино системной шиной, а также между локальной шиной и шиной ввода-вывода. В процессе обмена мог следующие операции: 1. Чтение данных из памяти; 2. Чтение данных из устройств ввода-вывода информации; 3. Запись данных в память; 4. Запись данных в устройство вводавывода; 5. Подтверждение прерываний. Организация ввода-вывода в вычислительных системах Обмен информацией между микропроцессором и внешними устройствами может производи объемами и занимать много времени, так как основное время затрачивается на синхронизацию мик внешнего устройства. Для освобождения микропроцессора от работы по управлению обменом данн специальные устройства, называемые контроллерами ввода-вывода. Обмен по каналу ввода-вывода может быть последовательным или параллельным. Последовательн передача информационных символов и сигналов сопровождения по одной линии. Сообщением наз информации. Признаки начала и конца сообщения оговариваются протоколом. Количество со сообщение сигналов, как и количество бит данных, содержащихся в сообщении, оговаривае Существует асинхронный и синхронный последовательный обмен. Обмен может быть однона (полудуплексным) и двунаправленным (дуплексным). Параллельный обмен – это когда по каналу связи передается одновременно слово осно компьютера, при этом сигнал сопровождения передается посредством дополнительной парал Параллельный обмен также может быть асинхронным и синхронным, однонаправленным (полу двунаправленным (дуплексным), а также программно-управляемым и с квитированием. Квитирован сигналов, подтверждающих готовность канала к работе, выставку информации и сигналов о приеме д квитирования являются внепрограммными и микропроцессор в их формировании не участвует. Последовательный обмен менее производительный, чем параллельный. Он более сложно протоколам, но лучше защищен от помех. Параллельный обмен организуется на коротком последовательный обмен предназначен для передачи информации на большие расстояния. Для обмена между микропроцессором и внешними устройствами создаются контроллеры, которые размеща расширения. Контроллер параллельного обмена с принтером или другими устройствами компьютера портами LPT. Эти порты программируются и управляются базовой системой ввода-вывода BIOS. 57 Организация параллельного обмена Для организации параллельного обмена используют специальные микросхемы, называемые программируемым адаптером (ППА). ППА предназначен для организации разнонаправленного обмен под управлением программ, находящихся в адаптере. Процесс программирования адапте инициализацией и заключается в записи во внутренние регистры адаптера специальных управляющ данных программируемого адаптера подключается к шине данных и является двунаправленным. О микропроцессора в ППА через буфер данных вводятся управляющие слова настройки, слова установки подлежащие выдаче. На шину данных микропроцессора из адаптера через буфер данных поступ внутренних портов ППА, пришедшие от внешних объектов и слова состояния адаптера, отображающ работ. Слова состояния адаптера определяют статус ППА в текущий момент времени. ППА может рабо трех режимов: 1. Нулевой режим. Когда все три внутренние канала адаптера независимы и работают асинхронно на ввод-вывод информации. 2. Первый режим. Когда два внутренних канал прием или выдачу данных. 3. Второй режим. Когда только один внутренний канал работает, как двунаправленный ввод или вывод ППА. Основой структуры ППА является восьмиразрядная в шина, к которой подключаются внутренние абоненты адаптера. Абонентами являются буфер данных, с управления и три внутренних канала a, b, c. Каналы (порты) a, b, c имеют регистры приема и выдачи да принимают и фиксируют данные при выдаче их внешним устройствам, транслируют принимаемые от а данные на буфер данных. Организация последовательного обмена Последовательный обмен предполагает передачу информации от датчика к приемнику по одному – информационному и второму – общему. Передача производится символами, состоящими из б последовательно выдаваемых в канал связи. Биты могут быть следующих категорий: • Информационные; • Служебные; • Контрольные. Их количество и место расположения определяется протоколами, известными приемнику. Управление обменом осуществляется контроллерами. Контроллеры одинаковы для датчик и называются универсальными синхронно- асинхронными приемопередатчиками. Эти контроллеры мо одном из двух режимов: асинхронном и синхронном. Асинхронный режим заключается в передаче информации символами, произвольно следую обмена, каждый символ имеет самостоятельное значение и синхронизируется отдельно от др сообщения. Каждый символ содержит определенные категории бит, их разные количества и строго места для бит. Стандарт передачи последовательного интерфейса называется RS 232. Протокол асинх заключается в следующем: ЭВМ датчика и ЭВМ приемника настраивают свои устройства синхрон передачи на необходимый режим. Затем процессор датчика выставляет информационно последовательно байт за байтом, в свое устройство синхронно-асинхронной приемопередачи. В синхронном режиме передатчик выставляет на устройство синхронно-асинхронной переда синхросигнала, которые переводятся в последовательный код и посылаются в канал для передачи. 58 Контрольные вопросы к лекции No 12 1. Посредством чего осуществляется управление шинами-формирователями? 2. Что такое чипс отличаются шинные формирователи адресов от шин формирователей данных? 4. Как устроены формирователи шин адресов? 5. Что представляет собой шина управле операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной? 7. Что такое сообщение? 8. Чем отличаются параллельный и последовательный обмен по каналу вводавывода? 9. Что такое параллельный программируемый адаптер? 10. В каких режимах могут рабо контроллеры последовательного обмена информацией? 59