МИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра ЭУТ

ОТЧЕТ

по домашнему заданию

по дисциплине «Современные проблемы электроники и

микропроцессорных систем в приборостроение»

Тема: Язык описания аппаратуры AlteraHDL

Вариант №2

Студент гр. 6584

Нгуен В.Ф.

Преподаватель

Петров Г.А.

Санкт-Петербург

2021

ЗАДАНИЕ НА РАБОТУ

Цифровая схемотехника. Язык описания аппаратуры

AlteraHDL.

Вариант 2

На

языке

AlteraHDL

разработать

описание

схемы,

реализующей приведенную диаграмму. Схема представляет собой

делитель входной частоты, подаваемой на вход clk. На выходах

схемы должны формироваться сигналы, обозначенные out1, out2 и

т.д.

clk

out1

out2

……

outN

Отчет по работе должен содержать листинг программы,

описание использованных элементов, комментарии к программе и

выводы.

2

(

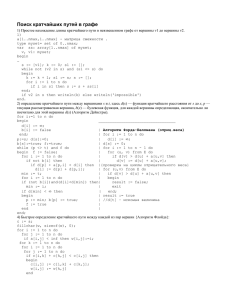

ЛИСТИНГ ПРОГРАММЫ

SUBDESIGN Variant2

{

clk: INPUT;

//описание входа и выходов

out1, out2, out3: OUTPUT;

}

VARIABLE

d11, d12: DFF;

//описание переменных

d21, d22: DFF;

A0, A1, B0, B1: NODE;

BEGIN

d1[0..1].clk = clk;

// счетчик А

d1[0..1].d=(d1[0..1] . q+1) and !A;

A[0..1] = d1[0..1] . q;

d2[0..1] . clk = !clk;

// счетчик B

d2[0..1] .d=(d2[0..1] . q+1) and !B;

B[0..1]=d2[0..1] . q;

IF (А[0..1] . q==3) THEN // условие сброса счетчика А

A = GND;

END IF;

IF (B[0..1] . q==3) THEN // условие сброса счетчика B

B=GND;

END IF;

// выход 1 Out1

IF ((A==2 or A==3) or (B==2 or B==3)) THEN

out1 = VCC;

ELSE

out1 = clk;

END IF;

// выход 2 Out2

IF ((A!=2 and A!=0) or (B!=1 and B!=3)) THEN

out2 = VCC;

ELSE

out2 = GND;

END IF;

3

// выход 3 Out3

IF (A<2 or B<2) THEN

out3 = VCC;

ELSE

out3=clk;

END IF;

END;

4

ОПИСАНИЕ ИСПОЛЬЗОВАННЫХ ЭЛЕМЕНТОВ

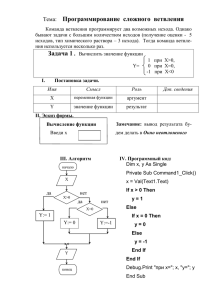

1. Оператор If Then.

Оператор If Then содержит список операторов, выполняемых в том случае,

если булевское выражение, расположенное между ключевыми словами IF и

THEN, принимает истинное значение.

2. Раздел Subdesign

Раздел Subdesign определяет входные, выходные и двунаправленные

порты данного проекта.

3. Раздел Variable

Необязательный раздел Variable используется для описания и/или

генерации переменных, используемых в разделе Logic. Переменные языка

AHDL сходны с переменными, используемыми в языках высокого уровня; они

используются для определения внутренней логики. Раздел Variable может

включать следующие операторы и конструкции:

1.

Описание объектов.

2.

Описание узлов.

3.

Описание регистров.

4.

Описание конечных автоматов.

5. Описание псевдоимен конечных автоматов.

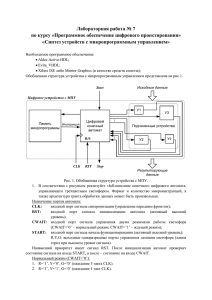

4. Объявление регистров.

Объявление регистров используется для определения регистров,

включая D, Т, JK и SR триггеры (DFF, DFFE, TFF, TFFE, JKFF, JKFFE, SRFF

и SRFFE) и защёлки (LATCH). В этой работе используется D-триггер, схема

которой представлена на рис. 1

5

PRN – входы асинхронного переключения.

D – вход данных.

CLK – такт.

Q – выход.

6