А.А. Макаренко

М.Ю.Плотников

РАСЧЕТ ЦИФРОВЫХ

ФИЛЬТРОВ МЕТОДОМ

АВТОМАТИЗИРОВАННОГО

ПРОЕКТИРОВАНИЯ

Учебное пособие

Санкт-Петербург

2014

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ

ФЕДЕРАЦИИ

САНКТ-ПЕТЕРБУРГСКИЙ НАЦИОНАЛЬНЫЙ

ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ

ИНФОРМАЦИОННЫХ ТЕХНОЛОГИЙ, МЕХАНИКИ И ОПТИКИ

А.А. Макаренко

М.Ю.Плотников

РАСЧЕТ ЦИФРОВЫХ

ФИЛЬТРОВ МЕТОДОМ

АВТОМАТИЗИРОВАННОГО

ПРОЕКТИРОВАНИЯ

Учебное пособие

Санкт-Петербург

2014

А.А.Макаренко, М.Ю.Плотников. Расчет цифровых фильтров методом

автоматизированного проектирования. Учебное пособие. – СПб:

НИУИТМО, 2014. – 50 с.

В учебном пособии кратко рассмотрены структуры цифровых

фильтров, а также способ их проектирования и расчета средствами

автоматизированного проектирования - средой проектирования Matlab.

Учебной пособие адресовано студентам бакалавриата и

магистрантам,

обучающихся

по

направлению

210700

Инфокоммуникационные технологии и системы связи» и изучающим

курс «Цифровая обработка сигналов»

Рекомендовано к печати Ученым советом Факультета

инфокоммуникационных технологий 19.06.2014 года, протокол

№06/14.

В 2009 году Университет стал победителем многоэтапного

конкурса, в результате которого определены 12 ведущих

университетов России, которым присвоена категория «Национальный

исследовательский университет». Министерством образования и науки

Российской Федерации была утверждена программа его развития на

2009–2018 годы. В 2011 году Университет получил наименование

«Санкт-Петербургский национальный исследовательский университет

информационных технологий, механики и оптики»

Санкт-Петербургский национальный исследовательский

университет информационных технологий, механики и оптики, 2014

А.А.Макаренко, М.Ю.Плотников 2014

2

Содержание

1. Структуры цифровых фильтров .................................................................... 4

1.1. Структура нерекурсивных фильтров ................................................ 4

1.2. Структуры рекурсивных фильтров ................................................... 5

2. Генерация входных тестовых сигналов ...................................................... 11

2.1 Классификация сигналов .................................................................. 11

2.2. Написание скрипта для генерации тестовых сигналов в среде

Matlab................................................................................................. 10

2.3. Контрольные задания ........................................................................ 13

3. Создание цифрового фильтра в среде Matlab ............................................. 15

3.1. Генерация коэффициентов цифрового фильтра в среде Matlab ..... 15

3.2. Контрольные задания ........................................................................ 17

4. Работа в среде Xilinx ISE Design Suite 14.4 ................................................ 18

4.1. Генерация цифрового фильтра в среде Xilinx ISE Design Suite

14.4 .................................................................................................. 18

4.2. Контрольные задания ........................................................................ 31

5. Моделирование цифрового фильтра в среде Xilinx ISE Design Suite

14.4 ............................................................................................................... 31

5.1. Создание програ1ммной оболочки для моделирования

средствами языка VHDL ................................................................ 31

5.2. Моделирование цифровых фильтров с помощью средства

верификации логических схем ...................................................... 36

5.3. Контрольные задания ........................................................................ 40

Литература ....................................................................................................... 41

Приложение А. Скрипт генерации входных сигналов в среде Matlab ......... 42

Приложение B. Пример программной оболочки для моделирования фильтра

в среде ISE Xilinx Design Suite 14.4 ..................................... 44

Приложение C. Скрипт обработки данных в среде Matlab ........................... 47

3

В настоящем учебном пособии кратко рассмотрены структуры

цифровых фильтров, а также способ их проектирования и расчета

средствами автоматизированного проектирования - средой проектирования

Matlab.

1. Структуры цифровых фильтров

1.1 Структура нерекурсивных фильтров

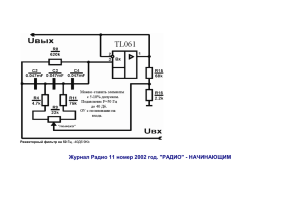

В цифровых фильтрах структура нерекурсивного фильтра

изображается схемой, которая соединяет вход и выход фильтра и в

которую введены элементы задержки, перемножители и сумматоры. Такая

схема - это способ визуализировать прохождение отсчетов исходной

последовательности и отобразить, где и когда эти отсчеты подвергается

задержкам и математической обработке. Структура непосредственно

следует из формулы передаточной функции или разностного уравнения

фильтра. Такая простая структура нерекурсивного фильтра называется

прямой структурой (рис.1). Выходы элементов задержки последовательно

умножаются на ряд коэффициентов, определяющих вид импульсной

характеристики фильтра, и полученные произведения суммируются для

формирования выходного сигнала. Таким образом, выходной сигнал

определяется сверткой входного сигнала со значениями импульсной

характеристики. Данный фильтр содержит в передаточной функции лишь

нули (поскольку в нем нет рекурсивных элементов обратной связи), и,

следовательно, для получения частотной характеристики с крутым срезом

необходимо относительно большое число элементов задержки.

Достоинством нерекурсивного фильтра является то, что такой фильтр

всегда устойчив и может обеспечить линейную фазовую характеристику.

Рис. 1. Прямая структура КИХ-фильтра

4

Выходной сигнал нерекурсивного фильтра определяется следующим

разностным уравнением:

y(k)=b0x(k)+...+bN-1x(k-N+1) .

1.2 Структуры рекурсивных фильтров

Фильтр с бесконечной импульсной характеристикой (рекурсивный

фильтр, БИХ-фильтр) - электронная схема, в состав которой входят

элементы задержки, перемножители и сумматоры. В основе структуры

рекурсивного фильтра находится цепь обратной связи, соединяющая один

или более выходов рекурсивного фильтра с его входом через

перемножители,

коэффициенты

которых

заданы

параметрами

передаточной функции фильтра. Отличительной чертой таких фильтров

является то, что их импульсная характеристика теоретически имеет

бесконечную длину во временной области, а передаточная функция имеет

дробно-рациональный вид. Рекурсивные фильтры могут быть построены в

соответствии с различными структурами.

Прямая форма 1

В этой части обратимся к прямой канонической структуре, которая

характеризуется следующей функцией передачи:

(1)

Во-первых, мы вводим промежуточную переменную x1(k):

.

(2)

Передаточная функция (1) может быть представлена как произведение

двух передаточных функций:

5

.

(3)

Формуле (3) соответствует последовательное включение рекурсивного

фильтра с передаточной функцией H1(z) и нерекурсивного фильтра с

передаточной функцией H2(z) (рис.2).

Рис. 2. Последовательное включение фильтров H1(z) и H2(z)

Такая структура рекурсивного фильтра (непосредственная реализация)

называется прямой формой 1 (рис.3).

6

Рис. 3. Структура БИХ-фильтра "прямая форма 1"

Прямая форма 2

Для реализации БИХ-фильтра в соответствии с прямой формой 1 требуется

(N+M-2) элементов задержки. Но как сократить число элементов задержки,

разделив их между рекурсивной и нерекурсивной частями фильтра?

Решением этой задачи является реализация БИХ-фильтра в соответствии

со структурой, называемой "прямая форма 2" (рис.4).

7

Рис. 4. Структура БИХ-фильтра "прямая форма 2"

Альтернативный подход состоит из разложения передаточной функции,

представленной уравнением (1), на последовательно соединенные БИХфильтр, а затем КИХ-фильтр.

Промежуточной переменной x1(k) соответствует разностное уравнение

8

.

(4)

Выходной сигнал y(k) через переменную x1(k) может быть выражен

следующим образом:

.

(5)

Следует отметить, что

,

Используя уравнения (4)

представленную на рис.5.

(6)

.

и (5),

можно

организовать

(7)

структуру,

Рис. 5. Структура прямой формы до объединения элементов задержки

9

Каноническая форма

После объединения элементов задержки образуется структура БИХфильтра, называемая канонической формой БИХ-фильтра (рис.6).

Рис. 6. Структура "Каноническая форма" БИХ-фильтра

На практике часто используется ячейка - БИХ-фильтр, в котором М=N=2

10

(рис.7). Такая ячейка второго порядка применяется в качестве

элементарного модуля при каскадной реализации фильтра относительно

высокого порядка. Каскадная реализация обеспечивает создание более

устойчивого БИХ-фильтра и снижает влияние ошибок округления

результатов промежуточных вычисления на точность работы всего

фильтра.

Рис. 7. Каноническая структура ячейки второго порядка

2. Генерация входных тестовых сигналов

2.1 Классификация сигналов

Под сигналом обычно понимают принятые данные или просто

материальный носитель информации. Принять рассматривать сигналы как

функции, заданные в каких-то координатах: одномерные сигналы,

заданные в виде функций времени x(t), двумерные сигналы (например,

изображения) P(x,y), заданные на некоторой плоскости, и т. д. На практике

чаще всего рассматриваются сигналы, описываемые действительными

функциями.

11

Рис. 8. Основные виды сигналов: а) аналоговый, б) импульсный, в)

цифровой

Аналоговый или непрерывный сигнал описывается непрерывной или

реже кусочно-непрерывной функцией времени x(t), причем значения как

самой функции, так и ее аргумента принадлежат бесконечному множеству.

Сигнал x(t) называется аналоговым, потому что такой сигнал является

аналогом изменения значений какой-то физической величины,

порождающей этот сигнал.

Импульсные или дискретные сигналы xP(t) образуются путём

дискретизации аналогового сигнала во времени: умножения аналогового

сигнала x(t) на функцию дискретизации y(t), представляющую собой

периодическую последовательность δ-функций, следующих с интервалом

дискретизации Δt. Отметим, что и у такого сигнала значения функции

принадлежат бесконечному множеству.

Цифровой сигнал xS(k) - это импульсный сигнал, подвергнутый

дискретизации по уровню. Цифровой сигнал описывается квантованной

решетчатой функцией (рис.9), т. е. решетчатой функцией, значения

которой принадлежат конечному множеству и принимают лишь ряд

дискретных уровней уровней квантования, число которых определяется

разрядностью числа, посредством которого описывается значения

цифрового сигнала.

Рис. 9. К определению цифрового сигнала

12

Финитный или ограниченный во времени сигнал характеризуется тем,

что длительность этого сигнала имеет конечное значение, т.е. такой сигнал

отличен от нуля лишь на конечном интервале T.

Очень важным является класс сигналов с конечным или финитным

спектром. Спектр таких сигналов X(jω) обращается в нуль вне некоторого

конечного интервала частот.

2.2 Написание скрипта для генерации тестовых сигналов в среде

Matlab

Для моделирования цифровых фильтров в среде ISE Xilinx Design

Suite 14.4 необходимо создать входной тестовый сигнал в правильном

формате в среде Matlab. Этот тестовый сигнал должен быть записан в

текстовый файл, в котором цифровые отсчеты тестового сигнала записаны

построчно.

Приведем пример скрипта, выполняющего генерацию подобного

тестового сигнала и записывающего его в текстовый файл. Следует

отметить, что генерируемый приведенным способом тестовый сигнал

соответствует реальному сигналу, который можно получить, например, с

16-ти разрядного АЦП, выдающего знаковые цифровые отсчеты в формате

дополнения до двух (two’s complement).

Для генерации входного тестового сигнала необходимо выполнить

следующие шаги:

- запустить Matlab.

- создать новый скриптовый *.m файл, выбрав команду «New» >

«Script» в меню «Файл»;

- записать в скриптовый файл последовательность команд,

осуществляющих генерацию тестового сигнала и его запись в текстовый

файл (см. пример в Приложении А).

- запустить выполнение скрипта кнопкой «Run», расположенной на

верхней панели управления средой Matlab.

В результате выполнения скрипта, приведенного в Приложении А, на

экран будет выведен сигнал, математически описываемый выражением:

I=A*cos(2*π*f1*t)+A1*cos(2*π*f2*t),

(8)

Этот сигнал представляет собой сумму двух косинусоидальных

сигналов с амплитудами A=10000, A1=4000 и частотами f1=1 кГц и f2=10

кГц. В результате выполнения скрипта цифровые отсчеты сигнала (8)

будут записаны в тестовый файл IPUT_DATA.txt в формате two’s

complement fixed-point. На экран будет выведен результат выполнения

скрипта, представленный на рис.10.

13

Входной сигнал

4

Амплитуда, отн.ед.

1.5

x 10

1

0.5

0

-0.5

-1

-1.5

0

0.001

0.002

0.003

0.004

0.005

Время, с

0.006

0.007

0.008

0.009

0.01

Спектр входного сигнала

Амплитуда, отн.ед.

10000

8000

6000

4000

2000

0

0

1000

2000

3000

4000

5000

6000

7000

8000

Частота, Гц

9000

10000

11000

12000

13000

14000

15000

Рис.10. Результат выполнения скрипта генерации входного тестового

сигнала

Далее создадим цифровой фильтр низких частот, с помощью которого

можно отфильтровать сигнал на частоте f2.

2.3. Контрольные задания

Напишите скрипт для генерации тестовых сигналов в среде Matlab.

Тестовый сигнал должен задаваться формулой:

I=A*cos(2*π*f1*t)+A1*cos(2*π*f2*t) +A2*cos(2*π*f3*t),

и иметь следующие параметры (Табл.1):

Таблица 1 Варианты тестовых сигналов

Номер

Частота

A

A1

A2

f1, Гц f2, Гц f3, Гц

варианта Дискретизации,

Гц

1

100000

10000 5000 3000 1000 3000 5000

2

100000

8000 3000 5000

500

2000 3500

3

100000

9000 7000 4000

850

3700 4900

4

100000

5000 1000 4000 3000 6000 9000

5

100000

2500 1000 7000

100 10000 15000

6

50000

2000 3000 6000 3000 13000 13500

7

50000

7000 12000 11000 4000 6000 8000

14

(9)

8

9

10

11

12

13

14

15

16

17

18

19

20

50000

50000

50000

125000

125000

125000

125000

125000

200000

200000

200000

200000

200000

2000

3000

9000

13000

2000

1000

5000

7000

10000

4000

2000

4000

1000

5000

6000

7000

1000

5000

8000

7000

3000

4000

2000

8000

1000

3000

14000

8000

2000

3000

7000

2000

2000

8000

1000

8000

1000

17000

4000

7000

4500

2500

20000

16500

17000

1000

2000

3500

14500

17000

10000

8000

8000

6000

4000

25000

21500

18000

3000

4000

5500

16000

19000

15000

10000

9000

8500

5500

30000

23000

20000

5000

6500

8000

18500

21000

20000

15000

3. Создание цифрового фильтра в среде Matlab

3.1 Генерация коэффициентов цифрового фильтра в среде Matlab

Для расчета коэффициентов нужного нам фильтра низких частот

воспользуемся утилитой среды Matlab Filter Design and Analysis Tool

(FDATool), функционал которой позволяет конвертировать коэффициенты

цифровых фильтров в формат two’s complement fixed-point и записывать их

в специализированный файл коэффициентов, интегрируемый в среду

Xilinx ISE Design Suite 14.4.

Для создания цифрового фильтра с конечной импульсной

характеристикой (КИХ фильтра) в среде Matlab необходимо выполнить

следующие действия:

- запустить Matlab;

- набрать в командной строке Matlab команду «fdatool», вызывающую

GUI интерфейс утилиты FDATool (см. рис.11);

- на вкладке «Set quantization parameters», расположенной в левой

нижней части GUI-интерфейса необходимо в окне «Filter arithmetic»

установить параметр «fixed-point»;

- далее необходимо перейти на вкладку «Design Filter»;

- занести в нижеперечисленные поля следующие значения:

Response Type – Lowpass – выбор типа фильтра: фильтр низких

частот;

Design Method – FIR, Equiripple – особенности построения фильтра:

эллиптический фильтр c конечной импульсной характеристикой (КИХ);

Filter Order – Minimum order (минимизировать количество

коэффициентов фильтра);

15

Frequency Specifications (задание частотной характеристики фильтра):

Units, Hz – единицы измерения частоты, Гц;

Fs

– частота дискретизации входных сигналов: 100000 Гц;

Fpass

– полоса пропускания до 2000 Гц;

Fstop

– полоса подавления с 5000 Гц;

Magnitude Specifications (задание амплитудной характеристики

фильтра):

Units, dB

– единицы измерения, дБ;

Apass

– неравномерность АЧХ фильтра в полосе пропускания:

0,1 дБ;

Astop

– ослабление сигналов в полосе подавления: 80 дБ.

Рис. 11. GUI интерфейс утилиты FDATool

После внесения всех значений в поля интерфейса необходимо

запустить процесс генерации фильтра путем нажатия на кнопку «Design

Filter» для запуска процесса расчета коэффициентов фильтра.

В результате генерации получается фильтр низких частот 111-го

порядка, с АЧХ (синим) и ФЧХ (зеленым), представленными на рис.11.

Для просмотра полученных коэффициентов фильтра необходимо нажать

кнопку «Filter Coefficients», расположенную над графиком АЧХ фильтра

на панели управления FDATool.

16

Для переноса рассчитанных коэффициентов фильтра в среду Xilinx

ISE Design Suite 14.4 необходимо сгенерировать специализированный

файл коэффициентов с расширением *.coe. Данный тип файлов

распознается средой Xilinx ISE и может быть использован для создания

реального цифрового фильтра на ПЛИС фирмы Xilinx.

Генерация файла коэффициентов для среды Xilinx ISE Design Suite

14.4 в формате two’s complement fixed-point производится путем выбора

пункта меню утилиты FDATool «Targets» > «XILINX Coefficient (.COE)

file». После этого нужно задать имя файла и указать путь к месту

сохранения файла (имя файла и путь к нему не должны содержать

пробелов, русских букв и спецсимволов).

3.2. Контрольные задания

Сгенерируйте цифровой фильтр средствами утилиты Matlab FDATool

и создайте файл коэффициентов *.coe. Параметры фильтра приведены

согласно вариантам:

1. Тип фильтра: фильтр низких частот, полоса пропускания 2000 Гц.

2. Тип фильтра: полосовой фильтр, полоса пропускания от 1000 Гц до

3000 Гц.

3. Тип фильтра: фильтр высоких частот, полоса пропускания от 1000

Гц.

4. Тип фильтра: заграждающий фильтр, полоса заграждения от 4000

Гц до 8000 Гц.

5. Тип фильтра: фильтр высоких частот, полоса пропускания от 500

Гц.

6. Тип фильтра: фильтр низких частот, полоса пропускания 5000 Гц.

7. Тип фильтра: фильтр низких частот, полоса пропускания 6000 Гц.

8. Тип фильтра: фильтр высоких частот, полоса пропускания от 3000

Гц.

9. Тип фильтра: полосовой фильтр, полоса пропускания от 5000 Гц до

7000 Гц.

10. Тип фильтра: фильтр низких частот, полоса пропускания 1000 Гц.

11. Тип фильтра: полосовой фильтр, полоса пропускания от 22000 Гц

до 27000 Гц.

12. Тип фильтра: фильтр низких частот, полоса пропускания 1000 Гц.

13. Тип фильтра: заграждающий фильтр, полоса заграждения от 17000

Гц до 20000 Гц.

14. Тип фильтра: фильтр низких частот, полоса пропускания 1500 Гц.

15. Тип фильтра: полосовой фильтр, полоса пропускания от 3000 Гц

до 6000 Гц.

16. Тип фильтра: полосовой фильтр, полоса пропускания от 4000 Гц

до 10000 Гц.

17

17. Тип фильтра: фильтр низких частот, полоса пропускания 11000 Гц.

18. Тип фильтра: фильтр высоких частот, полоса пропускания от

12000 Гц.

19. Тип фильтра: полосовой фильтр, полоса пропускания от 11000 Гц

до 18000 Гц.

20. Тип фильтра: фильтр низких частот, полоса пропускания 8000 Гц.

Параметры Apass = 0,1 дБ и Astop=80 дБ одинаковы для всех

вариантов.

4. Работа в среде Xilinx ISE Design Suite 14.4

4.1. Генерация цифрового фильтра в среде Xilinx ISE Design Suite 14.4

Цифровой КИХ фильтр на основе созданного файла коэффициентов

*.coe может быть добавлен как в новый проект среды Xilinx ISE Design

Suite 14.4, так и в уже существующий. Рассмотрим подробнее процесс

создания цифрового фильтра в новом проекте.

Для создания нового проекта программы для конкретной ПЛИС,

который в будущем будет содержать генерируемый цифровой фильтр

необходимо запустить среду Xilinx ISE Design Suite 14.4 и в меню «File»

выбрать опцию «New project» - программа предложит выбрать имя проекта

и его расположение на диске. Эти данные необходимо заполнить на

английском языке и без пробелов (см. рис. 3):

Name:

FIR_FILTER - название проекта.

Location: D:\Xilinx_projects\TESTS\FIR_FILTER – расположение

проекта на диске.

Top level source type: Schematic – верхний уровень иерархии проекта:

блок-схема.

18

Рис. 12. Создание нового проекта в среде Xilinx ISE Design Suite 14.4 – шаг

1

Следующим шагом создания нового проекта является указание

конкретной ПЛИС, под которую создается этот проект. При выборе ПЛИС

из приведенного в окне списка следует помнить, что существующие ПЛИС

могут значительно отличаться как по своей архитектуре, так по

техническим характеристикам. Поэтому некоторые стандартные функции

среды Xilinx ISE Design Suite 14.4 могут поддерживаться для одной ПЛИС

и не поддерживаться для другой. В качестве примера остановимся на

выборе ПЛИС Xilinx Spartan 3 XC3S1000 FT256. Создание цифровых

фильтров для этой ПЛИС осуществляется с использованием стандартного

блока генерации фильтров из библиотеки Core Generator - Fir Compiler

v5.0.

Для указания конкретной ПЛИС необходимо установить в

интерфейсном окне настроек проекта следующие параметры (см. рис.13):

Evaluation Development Board: None Specified – отладочная плата:

не задана.

Product Category:

All

– категория продукта: все.

Family:

Spartan 3

– семейство ПЛИС.

Device:

XC3S1000

– модель ПЛИС.

FT:

256

– общее

число

вводоввыводов.

Speed:

-5

– быстродействие ПЛИС.

19

Synthesis Tool:

XST(VHDL/Verilog) – основная утилита

для синтеза.

Simulator:

iSim

– симулятор.

Preferred Language:

VHDL

– предпочитаемый

язык.

Property Specification in project file: Store all values – параметры

хранения данных.

VHDL Source Analysis Standard:

VHDL-93 – стандарт языка

VHDL.

Создание проекта будет осуществлено после нажатия кнопок «Next» и

«Finish».

Рис. 13. Создание нового проекта в среде Xilinx ISE Design Suite 14.4 – шаг

2

Следующим шагом генерации цифрового фильтра является

добавление в проект файла верхнего уровня иерархии схематического типа

(Schematic), который станет основным рабочим полем проекта. Создание

этого файла производится путем выбора опции «New source» в

выпадающем меню, вызываемом правым щелчком мыши по

наименованию ПЛИС, для которой создается проект (см. рис.14):

20

Рис. 14. Создание рабочего поля проекта

Далее необходимо осуществить выбор типа нового файла для

добавления в проект. Для этого в поле «Select Source Type» выбираем

«Schematic» и указываем имя файла (например, «FILTER_TOP_LEVEL» см. рис.15).

Рис. 15. Добавление новых файлов в проект

После этого вновь созданный файл появится в окне иерархии и будет

открыт в рабочем пространстве среды Xilinx ISE Design Suite 14.4. Файл

автоматически станет файлом иерархии верхнего уровня (Top Module). В

21

дальнейшем на рабочее поле этого файла могут помещаться цифровые

блоки, логические примитивы и соединения между ними, схематично

отображающие связи между элементами проекта.

Теперь сгенерируем и добавим на рабочее поле проекта цифровой

фильтр на основе созданного ранее в среде Matlab файла коэффициентов

*.coe. Для этого добавим в проект новый файл с именем

«LOWPASS_FILTER» типа «IP (Core generator & Architecture Wizard)», как

это осуществлялось ранее для файла основного рабочего поля проекта

(рис.16):

Рис. 16. Генерация цифрового фильтра в среде Xilinx ISE Design Suite 14.4

– шаг 1

После нажатия кнопки «Next» на экран будет выведен список всех

доступных стандартных программно-аппаратных блоков для выбранной

ПЛИС. Функционал имеющихся блоков очень широк и включает в себя не

только базовые арифметические операции, но и другие, гораздо более

сложные функции: цифровую фильтрацию, децимацию, интерполяцию,

быстрое преобразование Фурье, тригонометрические операции, работу со

стандартными интерфейсами передачи данных и т.д.

Для генерации цифрового фильтра воспользуемся блоком генерации

цифровых фильтров «Fir Compiler v5.0» из библиотеки Core Generator. Для

этого запустим GUI-интерфейс этого блока, выделив его среди перечня

стандартных программно-аппаратных блоков в каталоге «Digital Signal

Processing/Filters» (рис.17).

22

Рис. 17. Генерация цифрового фильтра в среде Xilinx ISE Design Suite 14.4

– шаг 2

В результате на экран будет выведен GUI-интерфейс блока генерации

цифровых фильтров Fir Compiler v5.0 (рис.18):

Рис. 18. Интерфейс блока Fir Compiler v5.0.

23

Для создания цифрового фильтра с требуемыми коэффициентами в

первую очередь необходимо указать путь к созданному ранее файлу *.coe.

Для этого параметру «Select Source» необходимо задать значение «COE

File» и указать путь к файлу коэффициентов .*coe через меню «Browse…».

После этого на экран «Freq. Response» будет выведена АЧХ фильтра в

соответствии с коэффициентами файла *.coe (рис.19).

Рис.19. Генерация цифрового фильтра с заданными коэффициентами – шаг

1

Далее необходимо корректно настроить блок «Fir Compiler v5.0» с

тем, чтобы получить цифровой фильтр с нужными характеристиками. Для

этого на первой странице GUI-интерфейса необходимо дополнительно

выставить следующие параметры:

- указать тип фильтра без изменения частоты дискретизации: Filter

Type – Single Rate;

- установить количество каналов фильтра, равное 1: Number of

Channels 1;

- определить формат указания частоты дискретизации фильтра

указание частоты: Select format - Frequency Specification;

24

- входная частота дискретизации - Input Sampling Frequency: 0.1 MHz

- тактовая частота работы блока (определяется возможностями ПЛИС)

- Clock Frequency: 25 MHz.

На второй странице GUI-интерфейса параметры фильтра должны быть

установлены в соответствии с рис.20:

- архитектура построения фильтра – Filter Architecture: Systolic

Multiply Accumulate;

- структура коэффициентов фильтра (унаследованная) – Coefficient

Structure: Inferred;

- тип коэффициентов фильтра (знаковые) – Coefficient Type: Signed;

- разрядность коэффициентов фильтра – Coefficient Width: 16;

- число путей параллельной обработки – Number of Paths: 1;

- разрядность входного сигнала – Input Data Width: 16;

- число разрядов дробной части входного сигнала – Input Data

Fractional Width: 0;

- параметры округления выходного сигнала (максимальная точность) –

Output Rounding Mode: Full Precision;

- число разрядов дробной части выходного сигнала – Output Data

Fractional Bits: 0;

- удержание значений выходного сигнала (текущий выходной

цифровой отсчет остается на выходе фильтра до генерации следующего

отсчета выходного сигнала) – Registered Output:yes.

25

Рис.20. Генерация цифрового фильтра с заданными коэффициентами – шаг

2

На третьей странице GUI-интерфейса параметры фильтра должны

быть установлены в соответствии с рис.21:

- параметры оптимизации фильтра (минимизация занимаемых

ресурсов) – Optimization Goal: Area;

- в области опций контроля (Control Options) должен быть помечен

пункт ND (New Data), высокий логический уровень этого входного сигнала

сообщает фильтру о приходе нового цифрового отсчета на вход фильтра;

- в области Memory Options все значения должны быть установлены на

Automatic.

26

Рис. 21. Генерация цифрового фильтра с заданными коэффициентами –

шаг 3

На четвертой странице GUI-интерфейса

настроенные ранее параметры фильтра – см. рис.22:

27

представлены

все

Рис. 22. Генерация цифрового фильтра с заданными коэффициентами –

шаг 4

После установки всех параметров GUI-интерфейса в соответствии с

указанными ранее значениями запуск процесса генерации фильтра

осуществляется путем нажатия на кнопку «Generate» (см. рис.22). После

завершения процесса генерации сгенерированный фильтр появится в окне

иерархии проекта Xilinx ISE Design Suite 14.4 (см. рис.23).

Рис. 23. Сгенерированный фильтр в окне иерархии проекта

28

В связи с некоторыми особенности этой среды разработки желательно

осуществить повторную генерацию этого фильтра (либо путем его

открытия через окно иерархии и повторной генерации, либо путем

выполнения команды Regenerate Core в окне доступных процессов,

расположенном ниже окна иерархии).

После генерации фильтра необходимо добавить его в качестве блока

на основное рабочее поле проекта «FILTER_TOP_LEVEL.sch» - в файл

верхнего уровня иерархии, созданный ранее. Для этого среди вкладок под

областью доступных команд и процессов необходимо выбрать вкладку

«Symbols». После этого в списке доступных файлов необходимо найти

сгенерированный фильтр «LOWPASS_FILTER» (см. рис.24) и

«перетащить» его на основное рабочее поле проекта - схему.

Рис. 24. Выбор фильтра для переноса на основное рабочее поле проекта

После «перетаскивания» схематичное изображение фильтра появится

на основном рабочем поле проекта, как это показано на рис.25.

Рис. 25. Схематичное изображение фильтра на основном рабочем поле

проекта

29

Появившийся на основном рабочем поле проекта цифровой фильтр

содержит следующие интерфейсные элементы:

входы:

- DIN (15:0) – входная шина данных с разрядностью 16 бит (т.е.

значения входного сигнала для фильтра могут меняться в пределах от -2N-11 до 2N-1-1, где N=16);

- ND (New Data) – входной сигнал с разрядностью 1 бит, высокий

логический уровень которого сообщает фильтру о приходе на вход DIN

(15:0) нового отсчета данных;

- CLK – вход тактового сигнала, определяющего быстродействие

логических элементов фильтра

выходы:

- DOUT (38:0) – выходная шина данных с разрядностью 39 бит (т.е.

значения выходного сигнала фильтра могут меняться в пределах от -2N-1-1

до 2N-1-1, где N=39);

- RFD (Ready For Data) – выходной сигнал с разрядностью 1 бит,

высокий логический уровень которого сообщает о том, что фильтр

выполнил предыдущее преобразование и готов к приему нового цифрового

отсчета данных на входе DIN (15:0);

- RDY (Ready) - выходной сигнал с разрядностью 1 бит, высокий

логический уровень которого сообщает о том, что на выходе фильтра

появился новый цифровой отсчет выходного сигнала.

При необходимости схематичное изображение фильтра можно

изменить путем вызова всплывающего меню правой кнопкой мыши и

выбора пунктов меню «Symbol» > «Edit Symbol», как это показано на рис.

26.

Рис. 26. Изменение схематичного изображения фильтра

30

После добавления цифрового фильтра на основное рабочее поле

проекта остается проверить его работоспособность путем его

функционального моделирования с помощью встроенного в среду

разработки Xilinx ISE Design Suite 14.4 средства для верификации

логических схем.

4.2 Контрольные задания

Сгенерируйте цифровой фильтр среде Xilinx ISE Design Suite 14.4 на

основе файлов коэффициентов, полученных в ходе выполнения задания по

п. 2.2.

5. Моделирование цифрового фильтра в среде Xilinx ISE Design Suite

14.4

5.1 Создание программной оболочки для моделирования средствами

языка VHDL

Рассмотрим подробнее процесс моделирования вновь созданного

цифрового фильтра. Для моделирования фильтра необходимо добавить в

проект новый файл: программную оболочку для моделирования - VHDL

Test

Bench. С помощью такой программной оболочки и

специализированных библиотек и команд языка VHDL можно описать

входные сигналы для цифрового фильтра, в том числе и те сигналы,

которые были созданы и записаны ранее в текстовый файл с помощью

скрипта среды Matlab.

Для создания файла VHDL Test Bench необходимо сгенерировать и

добавить его в проект тем же способом, как это осуществлялось ранее для

файлов основного рабочего поля проекта и самого цифрового фильтра

(рис.27):

31

Рис. 27. Добавление в проект файла программной оболочки для

моделирования (VHDL Test Bench)

После добавления файла в проект пользователю будет предложено

выбрать Unit Under Test (UUT) – файл, который будет моделироваться

программной оболочкой VHDL Test Bench. В качестве такого файла

необходимо выбрать цифровой фильтр (см. рис.28).

Рис. 28. Выбор файла для симуляции (UUT)

После завершения выбора нужного файла моделирования для

пользователя будет открыт текстовый файл VHDL Test Bench, который

32

уже содержит информацию о моделируемом фильтре – его портах вводавывода (см. рис.29).

Рис. 29. Программная оболочка для моделирования VHDL Test Bench

Этот файл теперь необходимо модифицировать – описать сигналы на

входных портах моделируемого фильтра, подключить текстовые файлы

для чтения входного сигнала и записи выходного, а также правильно

задать периодичность записи выходного сигнала. Полный текст VHDL Test

Bench со всеми необходимыми внесенными изменениями представлен в

Приложении B. Рассмотрим подробнее основные части программной

оболочки для моделирования VHDL Test Bench. Стоит отметить, что для

языка VHDL не важен регистр, поэтому все команды можно писать как

обычными, так и заглавными буквами.

В первую очередь необходимо убедиться в том, что в файл

программной оболочки включены все необходимые для моделирования

библиотеки языка VHDL, а именно:

LIBRARY ieee - задает основную библиотеку стандарта VHDL IEEE;

USE ieee.std_logic_1164.ALL - выбор всех компонентов части

библиотеки IEEE std_logic_1164, отвечающей за использование типов

сигналов std_logic (один бит данных) и std_logic_vector (шина данных);

use IEEE.std_logic_arith.all - выбор всех компонентов части

библиотеки IEEE std_logic_arith, отвечающей за использование

математических операций;

use IEEE.std_logic_unsigned.all - выбор всех компонентов части

библиотеки IEEE std_logic_unsigned, отвечающей за беззнаковые

вычисления над типом данных std_logic_vector;

33

use ieee.numeric_std.all - выбор всех компонентов части библиотеки

IEEE numeric_std, отвечающей как за знаковые, так и беззнаковые

математические операции;

USE IEEE.STD_LOGIC_TEXTIO.ALL - выбор компонентов части

библиотеки IEEE IEEE.STD_LOGIC_TEXTIO, отвечающей за чтение и

запись данных в текстовые файлы;

use std.textio.all - выбор всех компонентов библиотеки std.textio,

отвечающей за работу с текстовыми файлами;

LIBRARY UNISIM задает имя основной библиотеки для

функционального моделирования логических элементов на ПЛИС фирмы

Xilinx;

USE UNISIM.Vcomponents.ALL - выбор всех компонентов части

библиотеки UNISIM Vcomponents, содержащей описания всех логических

примитивов ПЛИС фирмы Xilinx.

Далее в тексте программной оболочки VHDL Test Bench должны

следовать описания архитектуры моделируемого фильтра: портов вводавывода и одноименных сигналов. После этого должны следовать описания

основных констант, используемых при моделировании и определение

путей к входным и выходным файлам:

constant clk_period : time := 40 ns; – задание входной тактовой

частоты для цифрового фильтра;

constant N: integer := 30000000;

– задание максимального числа

записей выходного сигнала (желательно не использовать слишком

большие значения, кроме того – выставленного параметра хватит для

моделирования и записи выходного сигнала цифрового фильтра с частотой

дискретизации 100 кГц длительностью в 300 секунд).

FILE INPUT

: TEXT OPEN READ_MODE IS

"D:\Xilinx_projects\TESTS\INPUT_DATA.TXT"; – открытие текстового

файла INPUT_DATA.TXT для чтения;

FILE OUTPUT : TEXT OPEN WRITE_MODE

IS

"D:\Xilinx_projects\TESTS\OUTPUT_DATA.TXT"; – создание и открытие

текстового файла OUTPUT_DATA.TXT для записи.

Следующим важным элементом программной оболочки VHDL Test

Bench является непосредственное описание процессов для входных

сигналов цифрового фильтра.

Nd_process :process

– создание процесса;

begin

– начало процесса

ND <= '0';

– запись в порт ND (New Data) логического

значения «0» (данных нет);

wait for 9960 ns;

– ожидание в течение 9960 наносекунд;

ND <= '1';

– запись в порт ND (New Data) логического

значения «1» (появились данные на входном порте);

34

wait for 40 ns;

– ожидание в течение 40 наносекунд и затем

переход к первой команде процесса и повторение всей последовательности

команд процесса;

end process;

– конец описания процесса.

Поскольку частота дискретизации для моделируемого фильтра

составляет 100 кГц, то период следования цифровых отсчетов 1/100 кГц =

10000 нс, поэтому период следования стробов ND также должен

составлять 9960 + 40 нс = 10000 нс. Длительность строба в 40 нс

соответствует тактовой частоте работы фильтра – настройкам

сгенерированного фильтра и константе constant clk_period : time := 40 ns,

объявленной ранее.

Подобным образом описываются все процессы для входных портов

моделируемого фильтра, в том числе и основной процесс симуляции чтения входного тестового сигнала из текстового файла:

stim_proc: process

–

создание

основного

процесса

моделирования и чтения данных из текстового файла;

variable L: line;

– объявление вспомогательной переменной

L;

variable DIN_TXT :

STD_LOGIC_VECTOR (15 DOWNTO 0) :=

x"0000"; – объявление вспомогательной переменной DIN_TXT и задание

ее нулевого начального значения;

file

vector_file:

text

is

in

"D:\Xilinx_projects\TESTS\INPUT_DATA.TXT"; – указание пути к файлу

для чтения данных;

begin

– начало процесса;

din <=x"0000"; – запись нулевого начального значения сигнала

данных на входе фильтра;

while not endfile (vector_file) loop – проверка на достижение конца

файла, начало цикла моделирования;

readline(vector_file, L);

read(L, DIN_TXT);

переменную DIN_TXT;

wait for 9960 ns;

наносекунд;

din <= DIN_TXT;

сигнала на вход фильтра;

wait for 40 ns;

наносекунд;

end loop;

wait;

пользователем;

– чтение строки из файла;

– запись прочитанной строки в

–

ожидание

–

подача

–

ожидание

в

течение

значения

в

– конец цикла моделирования

–

ожидание

до

завершения

35

9960

тестового

течение

40

процесса

end process;

– конец процесса

После описания процесса чтения тестового сигнала из файла

остается описать процесс записи выходных данных моделируемого

цифрового фильтра в выходной текстовый файл:

write_process: process – создание процесса записи выходных данных

в текстовый файл;

variable i: integer range 0 to N := 0; – объявление вспомогательной

переменной i – количества возможных записей в файл (N = 30000000);

variable outLine : line; – объявление вспомогательной переменной

outLine;

begin

– начало процесса;

while i < N loop

– проверка на

операций записи данных;

количество проведенных

– ожидание в течение 10

wait for 10 us;

микросекунд;

write (outLine, dout);

– запись текущего значения

выходного сигнала цифрового фильтра в переменную outLine;

writeline (OUTPUT, outLine); –

запись

значения

переменной outLine в текстовый файл;

i := i + 1;

– наращивание значения счетчика

количество произведенных записей;

end loop;

– конец цикла записи;

end process;

– конец процесса записи.

Не следует забывать заканчивать описание программной оболочки

VHDL Test Bench командой «END;».

5.2 Моделирование цифровых

верификации логических схем

фильтров

с

помощью средства

После описания программной оболочки для моделирования VHDL

Test Bench остается запустить сам процесс моделирования. Это

осуществляется путем переключения среды Xilinx ISE Design Suite 14.4 в

режим Simulation, как это показано на рис.30.

36

Рис. 30. Переключение в режим симуляции в Xilinx ISE Design Suite 14.4

Далее необходимо запустить встроенное в среду Xilinx ISE Design

Suite 14.4 средство для верификации логических схем iSim Simulator

«двойным щелчком» по пункту меню Simulate Behavioral Model в области

доступных команд и процессов, как это показано на рис. 31.

Рис. 31. Запуск средства верификации логических схем iSim

Для запуска процесса симуляции остается задать время симуляции

(согласно частоте дискретизации моделируемого цифрового фильтра и

длительности входного сигнала в текстовом файле – 100 миллисекунд) и

нажать на кнопку «Run for the time specified on the toolbar», как это

показано на рис.32.

Рис. 32. Запуск процесса моделирования цифрового фильтра с помощью

средства верификации логических схем iSim

После этого начнется процесс моделирования цифрового фильтра,

который может продлиться несколько минут в зависимости от

37

быстродействия персонального компьютера пользователя и параметров

фильтра (разрядности, частоты дискретизации и т.д.). Ход процесса

моделирования показан на рис.33.

Рис. 33. Процесс моделирования цифрового фильтра с помощью средства

верификации логических схем iSim

Из рис.33 можно увидеть, что выходной сигнал с цифрового фильтра

представлен в виде цифровых отсчетов, меняющихся с периодичностью в

10 мксек, что соответствует выбранной частоте дискретизации 100 кГц.

После завершения моделирования – достижения временной отметки в 100

мсек, текстовый файл OUTPUT_DATA.TXT, содержащий цифровые

отсчеты выходного сигнала в формате two’s complement fixed-point

появится в указанной ранее директории.

Далее данные этого файла необходимо сконвертировать в формат,

удобный для анализа – signed integer. Для этого необходимо по аналогии с

созданием скрипта для генерации входного тестового сигнала написать в

программе Matlab скрипт, интерпретирующий данные текстового файла с

выходным сигналом. Пример такого скрипта приведен в Приложении C.

В результате выполнения такого скрипта на экран будет выведен

график выходного сигнала цифрового фильтра (см. рис.34),

реализованного в среде Xilinx ISE Design Suite 14.4 и отмоделированного с

помощью входного тестового сигнала с использованием средства для

верификации логических схем iSim.

38

Сигнал после фильтрации

9

Амплитуда, отн.ед.

3

x 10

2

1

0

-1

-2

-3

0

0.01

0.02

0.03

0.04

Амплитуда, отн.ед.

0.06

0.07

0.08

0.09

0.1

Спектр сигнала после фильтрации

9

3

0.05

Время, с

x 10

2.5

2

1.5

1

0.5

0

0

1000

2000

3000

4000

5000

6000

7000

8000

Частота, Гц

9000

10000

11000

12000

13000

14000

Рис. 34. Результат моделирования цифрового фильтра с помощью средства

верификации логических схем iSim

Согласно рис.34, в результате пропускания входного тестового

сигнала через сгенерированный в среде Xilinx ISE Design Suite 14.4

цифровой фильтр низких частот с полосой пропускания 2 кГц сигнал на

частоте 10 кГц был полностью отфильтрован.

Следует также отметить, что выходной сигнал цифрового фильтра на

частоте 1 кГц имеет теперь большую амплитуду, чем во входном тестовом

сигнале. Этот эффект усиления сигнала является следствием

целочисленного представления всех коэффициентов, созданных ранее в

среде Matlab. Так, в ходе создания файла коэффициентов *.coe

коэффициенты фильтра преобразуются в формат fixed-point, причем при

преобразовании учитываются только значащие разряды после запятой, что

при представлении этих коэффициентов в двоичном виде эквивалентно

умножению коэффициентов на 2N (N-разрядность коэффициентов фильтра,

в нашем случае N=16). Таким образом, для ПЛИС все коэффициенты

представляются как знаковые целые числа. По этой причине согласно

принципу работы цифрового фильтра (согласно разностному уравнению),

выходной сигнал цифрового фильтра усиливается. В связи с этим

возникает необходимость увеличения разрядности выходного сигнала

цифрового фильтра по сравнению с входной. Так, в нашем случае,

разрядность входного сигнала была равна 16, а выходного сигнала – 39.

Усиление фильтров следует обязательно учитывать в схемах

цифровой обработки сигналов на ПЛИС. Однако усиление фильтра можно

и полностью исключить путем «отбрасывания» младших разрядов

39

15000

выходного сигнала, что эквивалентно при представлении выходного

сигнала фильтра в двоичном виде делению на 2 M, где M – количество

«отбрасываемых» разрядов. Сама процедура «отбрасывания» может

осуществляться как с помощью специально разработанного средствами

языка VHDL программно-аппаратного блока, так и непосредственно с

помощью блока генерации цифровых фильтров Fir Compiler v5.0.

Блок генерации цифровых фильтров Fir Compiler v5.0 предлагает

несколько вариантов «отбрасывания» ненужных младших разрядов

выходного сигнала, основанных на различных методах округления (см.

рис.20 - параметр Output Rounding Mode). Возможны следующие варианты

округления значения выходного сигнала с отбрасыванием его младших

разрядов:

- Full Precision – без «отбрасывания» младших разрядов;

- Truncate LSBs – усечение младших разрядов (обеспечивает

наименьшую точность результата);

- Non Symmetric Rounding Down

– округление до наименьшего

целого;

- Non Symmetric Rounding Up – округление до наибольшего целого;

- Symmetric Rounding to Zero – симметричное округление к нулю;

- Symmetric Rounding to Infinity

– симметричное округление к

бесконечности;

Каждый из представленных методов округления имеет свои

преимущества, а выбор использования того или иного метода округления

завит от конкретной задачи.

5.3. Контрольные задания

Опишите программную оболочку для моделирования цифровых

фильтров, сгенерированных согласно п. 2.2 и 3.2 (см. Приложение B),

отмоделируйте цифровой фильтр в среде Xilinx ISE Design Suite 14.4 с

помощью средства верификации логических схем iSim и проанализируйте

результаты моделирования с помощью скрипта для анализа данных (см.

Приложение С) в среде Matlab.

40

Литература

1. Тарасов И.Е. Разработка цифровых устройств на основе ПЛИС

Xilinx с применением языка VHDL. – М.: Горячая линия – Телеком, 2005. –

252 с.

2. Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. –

М.: Издательский дом «Додэка-XXI», 2007. – 408 c.

3. Spartan 3 FPGA Family Data Sheet [Электронный ресурс]. – Режим

доступа: http://www.xilinx.com/support/documentation/data_sheets/ds099.pdf,

свободный. Яз. англ. (дата обращения 01.12.2013).

4. Fir Compiler 5.0 [Электронный ресурс]. – Режим доступа:

http://www.xilinx.com/support/documentation/ip_documentation/fir_compiler_d

s534.pdf, свободный. Яз. англ. (дата обращения 01.12.2013).

5. Официальный сайт фирмы Xilinx http://www.xilinx.com/

41

Приложение А. Скрипт генерации входных сигналов в среде Matlab

clc;

clear all;

% очистка экрана Matlab

% очистка переменных Matlab

fid = fopen('INPUT_DATA.txt','w');

записи данных

Fs = 100000;

A = 10000;

A1 = 4000;

f1 = 1000;

f2 = 10000;

T = 0.1;

N = T*Fs;

a = 0;

i = 0;

% открытие файла для

% частота дискретизации, Гц.

% амплитуда сигнала 1, отн. ед.

% амплитуда сигнала 2, отн. ед.

% частота сигнала 1, отн. ед.

% частота сигнала 2, отн. ед.

% длительность сигналов, сек.

% общее количество точек сигналов

% вспомогательная переменная

% вспомогательная переменная

struct.mode = 'fixed';

struct.roundmode = 'floor';

struct.overflowmode = 'saturate';

struct.format = [16 0];

бит

q = quantizer(struct);

% задание параметров структуры

% для представления данных

% в формате

% two's complement fixed-point 16

% Создание структуры для

% конвертации данных в формат

% two's complement fixed-point

t=0:1/Fs:T;

% генерация отсчетов времени

I=A*cos(2*pi*f1*t)+A1*cos(2*pi*f2*t);

% генерация входного

сигнала

M=fix(I);

% отбрасывание дробной части

for s=1:1:N

M1 = num2bin(q,M(s));

fprintf(fid,'%s\n',M1);

i=i+1;

% цикл конвертации

% данных в формат

% two's complement fixed-point

% запись сконвертированных

% данных в текстовый файл

42

if(i>N/100)

% цикл вывода на экран

% % выполненного задания

clc;

i=0;

a=(s/N)*100;

disp('Выполнено, %:');

disp(a);

end

end

Y = fft(M,N);

P = 2*abs(Y)/N;

P(1)=P(1)/2;

samp = Fs*(0:N/2)/N;

% расчет спектра

% входного сигнала

subplot (2,1,1);

plot (t,M);

title('Входной сигнал');

xlabel('Время, с');

ylabel('Амплитуда, отн.ед.');

% построение графика

% входного сигнала

% расчет частот спектра

subplot (2,1,2);

plot(samp,P(1:N/2+1));

title('Спектр входного сигнала');

xlabel('Частота, Гц');

ylabel('Амплитуда, отн.ед.');

% построение спектра

% входного сигнала

disp('Генерация тестового сигнала завершена');

fclose all;

% закрытие всех файлов

43

Приложение B. Пример программной оболочки для моделирования

фильтра в среде ISE Xilinx Design Suite 14.4

LIBRARY ieee; -USE ieee.std_logic_1164.ALL; -use IEEE.std_logic_arith.all; -use IEEE.std_logic_unsigned.all; -use ieee.numeric_std.all; -USE IEEE.STD_LOGIC_TEXTIO.ALL; -use std.textio.all;

-LIBRARY UNISIM; -USE UNISIM.Vcomponents.ALL;

ENTITY TEST_BENCH_FILTER IS -END TEST_BENCH_FILTER; --

--

ARCHITECTURE behavior OF TEST_BENCH_FILTER IS --- Component Declaration for the Unit Under Test (UUT)

COMPONENT LOWPASS_FILTER -PORT(

clk

: IN

std_logic;

nd

: IN

std_logic;

rfd

: OUT

std_logic;

rdy : OUT

std_logic;

din

: IN

std_logic_vector (15 downto 0);

dout : OUT

std_logic_vector (38 downto 0)

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

signal nd : std_logic := '0';

signal din : std_logic_vector (15 downto 0) := (others => '0');

--Outputs

signal rfd : std_logic;

signal rdy : std_logic;

signal dout

: std_logic_vector (38 downto 0);

44

-- Clock period definitions

constant clk_period : time := 40 ns;

constant N: integer := 30000000;

FILE INPUT

: TEXT OPEN READ_MODE IS

"D:\Xilinx_projects\TESTS\INPUT_DATA.TXT";

FILE OUTPUT : TEXT OPEN WRITE_MODE

"D:\Xilinx_projects\TESTS\OUTPUT_DATA.TXT";

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: LOWPASS_FILTER PORT MAP (

clk

nd

rfd

rdy

din

dout

=> clk,

=> nd,

=> rfd,

=> rdy,

=> din,

=> dout

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

Nd_process :process

begin

ND <= '0';

wait for 9960 ns;

ND <= '1';

wait for 40 ns;

end process;

-- Stimulus process

stim_proc: process

variable L: line;

45

IS

variable DIN_TXT : STD_LOGIC_VECTOR (15 DOWNTO 0) := x"0000";

file vector_file: text is in "D:\Xilinx_projects\TESTS\INPUT_DATA.TXT";

begin

-- //=======================

=======================//

din <=x"0000";

while not endfile (vector_file) loop

INPUT

DATA

FUNCTION

readline(vector_file, L);

read(L, DIN_TXT);

wait for 9960 ns;

din <= DIN_TXT;

wait for 40 ns;

end loop;

wait;

-//==========================

==================================//

end process;

--//====================== WRITE

==============================//

write_process: process

END

TO

OF

DATA

FILE

PROCESS

WRITE

PROCESS

variable i: integer range 0 to N := 0;

variable outLine : line;

begin

while i < N loop

wait for 10 us;

write (outLine, dout);

writeline (OUTPUT, outLine);

i := i + 1;

end loop;

end process;

--//======================== END

===============================//

END;

46

OF

Приложение C. Скрипт обработки данных в среде Matlab

clc;

% очистка экрана Matlab

data = fopen('OUTPUT_DATA.txt','rb');

fileinfo = load ('OUTPUT_DATA.txt');

[N m] = size(fileinfo);

data_out = fopen('DATAOUT.txt', 'wt');

% открытие файла для чтения

% загрузка содержимого файла

% определение размеров файла

% открытие файла для записи

Fs=100000;

k=0;

j=0;

% частота дискретизации данных

% вспомогательная переменная

% вспомогательная переменная

for j=1:N;

% цикл обработки данных

k=k+1;

data1 = fgetl(data);

[y z] = size(data1);

struct.mode = 'fixed';

struct.roundmode = 'floor';

struct.overflowmode = 'saturate';

struct.format = [z 0];

q = quantizer(struct);

c= bin2num(q,data1);

% чтение строки из файла

% определение размеров строки

% формирование структуры

% для преобразования данных

% в формат

% signed integer

% конвертация данных

fid2 = fprintf(data_out,'%d\n', c);

% запись данных в файл

if (k>N/100)

% цикл вывода на экран

% % выполнения

% конвертации

clc;

disp('Processing...');

disp(N);

disp(j);

disp(j/N*100);

k=0;

end

end

47

disp('Conversion is complete');

fclose all;

% закрытие всех файлов

M=load('DATAOUT.txt');

данных

t=0:1/Fs:(N-1)/Fs;

шкалы

Y = fft(M,N);

P = 2*abs(Y)/N;

P(1)=P(1)/2;

samp = Fs*(0:N/2)/N;

% загрузка сконвертированных

subplot (2,1,1);

plot (t,M);

title('Сигнал после фильтрации');

xlabel('Время, с');

ylabel('Амплитуда, отн.ед.');

% построение графика

% сконвертированного сигнала

% формирование временной

% расчет спектра сигнала

% расчет оси частот спектра

subplot (2,1,2);

plot(samp,P(1:N/2+1));

% построение спектра

title('Спектр сигнала после фильтрации'); % сконвертированного сигнала

xlabel('Частота, Гц');

ylabel('Амплитуда, отн.ед.');

fclose all;

% закрытие всех файлов

48

В 2009 году Университет стал победителем многоэтапного конкурса, в

результате которого определены 12 ведущих университетов России, которым присвоена категория «Национальный исследовательский университет». Министерством образования и науки Российской Федерации была утверждена программа его развития на 2009–2018 годы. В

2011 году Университет получил наименование «Санкт-Петербургский

национальный исследовательский университет информационных технологий, механики и оптики»

КАФЕДРА СВЕТОВОДНОЙ ФОТОНИКИ

Кафедра физики и техники оптической связи вошла в состав Инженерно-физического факультета в 1976 г. и в 2010 г. была переведена на

вновь созданный Факультет инфокоммуникационных технологий. Заведующим кафедрой является д.т.н., проф., заслуженный деятель науки

РФ И.К. Мешковский. На кафедре развились два научно-технических

направления: технология оптического волокна и создание новых композиционных оптических материалов. В 1982 г. кафедра первой в

стране стала осуществлять подготовку инженеров по специальности

«Волоконная и интегральная оптика». На базе кафедры были проведены первые в России разработки по технологии производства оптического волокна, оптических жгутов, различных волоконно-оптических

приборов и систем. Возникла научная школа в области фотоники дисперсных и нелинейных сред. В 1998 г. в связи с развитием систем телекоммуникации и высокими потребностями в специалистах по волоконно-оптической связи кафедра первой в Санкт-Петербурге стала осуществлять подготовку инженеров по специальности «Физика и техника

оптической связи», а с 2008 г. подготовку бакалавров и магистров по

направлению «Телекоммуникации». На кафедре проводятся студенческие научные семинары по телекоммуникации. Кафедра осуществляет

научные разработки совместно со многими зарубежными фирмами и

университетами.

С 2014 г. кафедра носит название "Кафедра Световодной фотоники".

Александр Александрович Макаренко

Михаил Юрьевич Плотников

Расчет цифровых фильтров методом автоматизированного

проектирования

Учебное пособие

В авторской редакции

Редакционно-издательский отдел НИУ ИТМО

Зав. РИО

Н.Ф. Гусарова

Лицензия ИД № 00408 от 05.11.99

Подписано к печати

Заказ №

Тираж 100 экз.

Отпечатано на ризографе

Редакционно-издательский отдел

Санкт-Петербургского национального

исследовательского университета

информационных технологий, механики

и оптики

197101, Санкт-Петербург, Кронверкский пр., 49