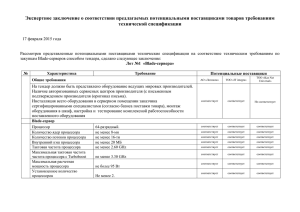

Разработка многоядерного потокового вычислителя

реклама

Студенческий проект

РАЗРАБОТКА МНОГОЯДЕРНОГО

ПОТОКОВОГО ВЫЧИСЛИТЕЛЯ

Участники:

Тодорук Евгений (361 гр.)

Солдатов Дмитрий (361 гр.)

Забранский Дмитрий (361 гр.)

Улитин Александр (361 гр.)

Щербаков Александр (244 гр.)

Демьяненко Илья (244 гр.)

Научный руководитель:

Кривошеин Борис Николаевич

2011/2012 год

Цель проекта

Разработка архитектуры вычислителя на базе

управляющего процессора и массива простых

вычислительных ядер, способных обрабатывать

параллельно потоки данных.

Разработка прототипа на ПЛИС с минимальным

количеством потоковых сопроцессоров и

масштабируемой архитектурой.

Структура многоядерного

потокового вычислителя

Этапы

1) Изучение языка VHDL и основ

2)

3)

4)

5)

программирования ПЛИС

Проектирование архитектуры простого

вычислительного процессора (ПВП, DSP-group)

Создание компонент DSP-group: DSP-ядро,

внутренняя память, контроллер памяти,

контроллеры входных и выходных данных

Создание слоя и сети DSP-group

Тестирование отдельных компонент и всей

модели

Архитектура

простого

вычислительного

процессора

Данный процессор

может выполнять

простые операции

такие как сложение,

вычитание,

умножение чисел.

Обладает внутренней

памятью команд,

позволяющей

запрограммировать

вычисление ряда

последовательных

операций.

Внутренняя структура простого

вычислительного процессора

Транслятор команд

Для программирования микропамяти

используется «Универсальный генератор

микрокоманд» (Полиэктов Андрей, 1998)

Типы команд

Вычисления (multab, addabc, subabc, xorabc …)

Записи в регистры (WR<i> <F>)

Выборки значений (abcd <A> <B> <C> <D>, a <A> …)

Разное (reset, nop, output)

Пример

{multab; a I1; b I2}; {nop;} {WR1 P; }

Структура DSP-сети

Технологии

FPGA Virtex-6

VHDL

DSP48E

Xilinx CORE Generator (LogiCORE)

Xilinx ISE

Xilinx Platform Studio

Универсальный генератор микрокоманд

дополнительный препроцессор на Perl

Список литературы

Проектирование систем на микросхемах

программируемой логики, P. Грушвицкий

Virtex-6 FPGA DSP48E1 Slice User Guide, Xilinx

Distributed Memory Generator v6.2, 2011 Product

Specification, Xilinx

Диплом «Универсальный генератор

микрокоманд», Андрей Полиэктов, 1998