Системная шина адреса/данных/управления

реклама

Информационные шины

обмена – ISA, PCI

Системотехника ЭВС, комплексы и сети

1

Структурная схема системной платы на основе 80286 процессора

8284 A

14 MHz

8

7

6

CLOCK

LA16 - LA23 SA0-SA19 SBHE

PCK

LOGIC

A0-A23

CLOCK

GENERATOR

SD0SD7

BUFFER

EXTERNAL

EXTERNAL

ADDRESS

ADDRESS

BUFFER

BUFFER

ALS245

ALS573

ALS573

ALS573

BHE

ALS245

CONVERT

DATA

BUFFER

I/O

ALS245

EXTERNAL

DATA

1 64 + 32 PIN I/O SLOT

BUFFER

F158

XD0-XD7

CS

8237A-5

CS

8237A-5

DECODER

LOCAL

CONTROL BUS

AND CNTL

LOGIC

ADDRESS

MUX

128K*9

128K*9

128K*9

3

128K*9

2

1

RAM BANK 0

ALS573

ALS573

ALS573

DMA

DMA

LS 648

D0-D15

80 287

MEMORY

DMA

XA8-XA15

ALS245

F158

MEMORY

REFRESH

XA0-XA7

LOCAL

DATA BUS

LOCAL

ADDRESS BUS

SD0-SD7

XA0-XA15

SYSTEM

ADDRESS

BUFFER

PROCESSOR

COPROCESSOR

2

SYSTEM CONTROL BUS

I/O CH CK

80 286

CLK READY RESET

PWR

GOOD

3

16 - BIT SYSTEM DATA BUS

CS

ALS245

SYSTEM

ALS245

ALS245

ADDRESS

82 284

4

24 - BIT SYSTEM ADDRESS BUS

SA0-SA15

NMI

NMI

5

ADDRESS

SYSTEM

DATA

BUFFER

LATCH

SD0-SD15

A17-A23

S0, S1

82 288

COD/INTA

IO/M RDY

ALS245

ALS245

MEMORY

DATA

BUFFER

WAIT

WAIT

STATE&

CONVERT

LOGIC

A0

BHE

A17-A23

PAGE

PARITY

LOGIC

REGISTER

BUS

CONTROLLER

CS

CS

CS (4)

CS

32К В

CS (4)

CS

32ROM

КВ

SPEAKER

LOGIC

(4)

ROM

32К В

(4)

ROM

32КВ

ROM

CS

MD0-MD15

CLK

RESET

F280

F280

LS612

DMA

CS

CS

MC 146616

CLK/CLDR

IRQ0

RAM&ROM

DECODE &

LATCH

RAM0, RAM1

LIMEG CS

LIMEG CS

CS

8259A

8259A

IRQ8

MEMR/

MEMW

80-12

ALS244

KEYBOARD

LOW

MEG

RD/WR

BUFFER

IRQ3 - IRQ13

SMEMR/

SMEMW

Условные графические обозначения:

BATTERY

W/RAM

CS

MD0 - MD13

KEYBOARD

LOGIC

IRQ1

EXTERNAL

DATA BUS (XD)

LA - локальная

шина адреса

LC - локальная

шина управления

LM - локальная

шина памяти

LD - локальная

шина данных

SA - системная

шина адреса

SC - системная

шина управления

SM - системная

шина памяти

SD - системная

шина данных

XA - периферийная

шина адреса

XC - периферийная

шина управления

XM - периферийная

Системотехника ЭВС, комплексы и сети

шина памяти

XD - периферийная

шина данных

2

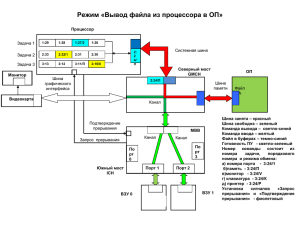

• По процессорной локальной шине (на структурной

схеме "Local Address, Data, Status and Control Bus")

микропроцессор взаимодействует с контроллером шины и

его периферией. Обычно сигналы на этой шине не имеют

дополнительных обозначений.

• Системная

шина

адреса/данных/управления

обозначена на структурной схеме "System Address, Data,

Control Bus". Она осуществляет взаимосвязь между

другими шинами компьютера, а также взаимодействие

системы с внешними устройствами.

• По внешней шине адреса/данных/управления

("External Address, Data, Control Bus") микропроцессор

взаимодействует

с

некоторыми

контроллерами,

микросхемами ПЗУ и отдельной периферией.

Системотехника ЭВС, комплексы и сети

3

http://web.znu.edu.ua/lab/MathDep/ApMath/ARCH&ASM/Shema/lect1.html

http://gzalevskij.narod.ru/Mikroprocessor.html

Системотехника ЭВС, комплексы и сети

4

Системотехника ЭВС, комплексы и сети

5

• генератор синхронизации 8284 разработан для

синхронизации работы микропроцессора.

собственная частота 14.318 МГц. делит на три

исходную частоту, чтобы получить сигнал

системной синхронизации CLK частотой 4.77

МГц, необходимый для работы

микропроцессора.

• Синхрогенератор используется в выработке

также сигнала готовности READY для

микропроцессора и сигнала сброса устройств

RESET, осуществляя синхронизацию сигналов

CLK, READY и RESET.

• Сигнал RESET формируется входным сигналом

PWR_GOOD, поступающим на синхрогенератор

с блока питания после включения компьютера

или нажатия кнопки сброса "RESET",

Системотехника ЭВС, комплексы и сети

6

Временные диаграммы циклов чтения или записи

на шине ISA

A0…15 сигналы адреса

D0…15 сигналы данных

BALE - разрешение защелки адреса. После его спада в каждом цикле процессора линии

CMD-обобщенный сигнал чтения или записи RD\WR

AEN - разрешение адресации портов (запрещает ложную дешифрацию адреса в цикле

DMA).

Системотехника ЭВС, комплексы и сети

7

• PCI (Peripheral Component Interconnect bus) шина для подсоединения периферийных

устройств.

• Имеет версии с питанием 5V, 3.3V и универсальную (с

переключением линий +VI/O c 5V на 3,3V).

• Шина PCI - первая шина в архитектуре IBM PC, которая не

привязана к этой архитектуре. Она является процессорнонезависимой.

• Автоконфигурирование устройств (выбор запросов

прерывания, каналов DMA) поддерживается средствами

BIOS материнской платы

• PCI является 64-битной шиной, хотя обычно выполняется

как 32-битная шина. Она может работать на частоте от 33

до 66 мегагерц. На 32 битах и 33 MHz шина дает скорость

133 мегабайт в секунду (MBps).

Системотехника ЭВС, комплексы и сети

8

Сигналы шины PCI

•

•

Знак - (минус) перед названием сигнала означает, что активный уровень этого сигнала логический ноль,

обозначение {XX:0} означает группу сигналов с номерами от 0 до XX.

AD{31:0} - мультиплексированная шина адреса/данных. Адрес передается по сигналу - FRAME, в

последующих тактах передаются данные.

•

-C/ BE{3:0} - команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла

шины (чтение-запись памяти, ввода/вывода или чтение/запись конфигурации, подтверждение

прерывания и другие) задается четырехбитным кодом в фазе адреса по сигналу - FRAME.

•

-FRAME - индикатор фазы адреса (иначе - передача данных).

•

-DEVSEL - выбор инициатором устройства назначения.

•

-IRDY - готовность инициатора к обмену данными.

•

-TRDY - готовность устройства назначения к обмену данными.

•

-STOP - запрос устройства назначения к инициатору на останов текущей транзакции.

•

-LOCK - используется для установки, обслуживания и освобождения захвата ресурса на PCI.

•

-REQ {3:0} - запрос от PCI-устройства на захват шины (для слотов 3:0).

Системотехника ЭВС, комплексы и сети

9

Временные диаграммы шины PCI

•

•

CLK

•

•

_______

_________

FRAME

|_________________________________|

___

___

___

___

___

___

___| |___| |___| |___| |___| |___| |___

•

•

•

AD

•

•

•

______ _______________________________

C/BE -------<______><_______________________________>--Команда Сигнал разрешения передачи байта

•

•

____________

___

IRDY

|________________________________|

•

•

_____________

___

TRDY

|________________________________|

•

•

______________

___

DEVSEL

|_______________________________|

______ _______ ______ ______ ______

-------<______><_______><______><______><______>--Адрес Данные1 Данные2 Данные3 Данные4

Системотехника ЭВС, комплексы и сети

10

Системотехника ЭВС, комплексы и сети

11

Контроллер 1821ВН59А

Системотехника ЭВС, комплексы и сети

12

Блок схема контроллера прерываний

Системотехника ЭВС, комплексы и сети

13

Системотехника ЭВС, комплексы и сети

14

Временная диаграмма контроллера прерываний

Системотехника ЭВС, комплексы и сети

15