Модуль 2. Синтез цифровых автоматов без элементах разной степени интеграции

реклама

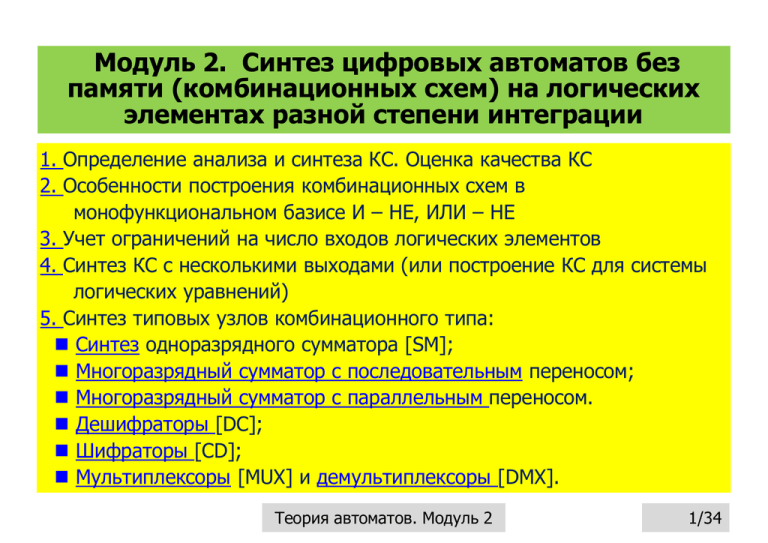

Модуль 2. Синтез цифровых автоматов без

памяти (комбинационных схем) на логических

элементах разной степени интеграции

1. Определение анализа и синтеза КС. Оценка качества КС

2. Особенности построения комбинационных схем в

монофункциональном базисе И – НЕ, ИЛИ – НЕ

3. Учет ограничений на число входов логических элементов

4. Синтез КС с несколькими выходами (или построение КС для системы

логических уравнений)

5. Синтез типовых узлов комбинационного типа:

Синтез одноразрядного сумматора [SM];

Многоразрядный сумматор с последовательным переносом;

Многоразрядный сумматор с параллельным переносом.

Дешифраторы [DC];

Шифраторы [CD];

Мультиплексоры [MUX] и демультиплексоры [DMX].

Теория автоматов. Модуль 2

1/34

Определение анализа и синтеза КС

x1

x2

x3

x4

&

x5

=1

1

x6

Анализ КС. Для каждого элемента необходимо выписать

функцию, отображающую его непосредственные связи, двигаясь от

выхода схемы в направлении её входов.

На втором этапе, применяем к полученной системе функций

y

метод подстановки до тех пор, пока для каждого выхода не получим

функцию, выраженную только через входные переменные:

y = x5 x6 = (x1x2) (x3+x4)

Синтез КС – построение схемы для некоторого функционального узла по заданным

условиям его работы в цифровом устройстве. Под заданными условиями понимается число

входов и выходов данного узла, а так же принцип соответствия двоичных наборов для

входных и выходных переменных.

Этапы синтеза:

формализация условий работы (функционирования) схемы или узла, сводящаяся к

составлению таблицы истинности для каждого выхода схемы;

получение булевых выражений, описывающих работу узла или схемы и их минимизация;

приведение полученных выражений к виду, соответствующему заданному логическому

базису или системе ЛЭ;

построение КС.

При проведении практических работ по синтезу КС могут выполняться не все действия

из указанных четырёх, так как некоторые могут быть уже выполненными или не быть

актуальными.

Теория автоматов. Модуль 2

2/34

Оценка качества КС. Быстродействие

Критериями оценки качества комбинационной схемы являются её быстродействие и

сложность (аппаратурные затраты). Быстродействие КС определяется интервалом

времени между фронтами сигналов на входах и выходах КС, измеренными на уровне

половины единичного уровня (0.5 U1).

ЛЭ без

Uвх

0,5U1

задержки

t

Uвых

t

,0

t 1зад

.р

0 ,1

t зад

.р

t зд. р

01

t 10

зр t зр

2

Временные диаграммы работы инвертора

x1

x2

ЛЭ

Задержка

y

x3

Модель элемента с учётом

задержки

При последовательном соединении ЛЭ задержка в распространении сигнала tзад. р

увеличивается и, в первом приближении, суммируется на число элементов цепи:

tзад. р. цепи = n х tзад. р. лэ.

a

x

b

y

Для КС с несколькими выходами задержка tзад. р указывается

для каждого выхода относительно соответствующего входа при

фиксированных значениях сигналов на других входах, например,

для схемы:

tзад(а→y)|b=const = ……

Теория автоматов. Модуль 2

3/34

Оценка качества КС. Сложность

Под глубиной КС понимается максимальное число элементов,

расположенных на пути распространения сигнала от входа к выходу.

Сложность КС оценивается по-разному, при этом при разработке КС

функциональных узлов вычислительной техники используются следующие

два критерия:

1. Сложность С по Квайну ( W.V. Quine):

С = «суммарное число входов используемых ЛЭ в КС».

Инверсный вход засчитается за два.

2. Если схема рассматривается на уровне простых ЛЭ, то её сложность М

можно оценить в виде суммарного числа используемых ЛЭ в КС.

Теория автоматов. Модуль 2

4/34

Закон отрицания

Логический базис функций ДНФ (дизъюнктивная нормальная форма) и КНФ

(конъюнктивная НФ), а именно элементы И, ИЛИ, НЕ, не являются естественными

для существующих транзисторных технологий, т. к. элементы И и ИЛИ являются

более сложными, чем элементы И-НЕ и ИЛИ–НЕ соответственно.

При выполнении логических преобразований полезно использовать закон

отрицания, в соответствии с которым для получения отрицания булевой функции

необходимо аргументы в двойственной ей функции заменить их отрицаниями.

f ( x 1 ,..., x n ) = f двойст ( x 1 ,..., x n )

Двойственная функция для искомой функции f получается взаимной заменой

операции И и ИЛИ, а также констант 1 и 0.

Теория автоматов. Модуль 2

5/34

Взаимные преобразования элементов И, ИЛИ, И-НЕ,

ИЛИ-НЕ на основе закона отрицания

x1

&

x2

1

x 1 ∨ x 2 = x 1x 2

x2

x1

x2

x1

x 1x 2

1

&

x 1x 2

x1

x 1x 2

1

x2

x2

x1

&

x 1 x 2 = x 1 ∨x 2

x1

&

x1

1

x 1 ∨x 2 = x 1x 2

x2

x1

x2

&

x1

x 1x 2

1

1

x1

x1 ∨ x 2

x2

x2

x1

x2

x1 ∨ x 2

x1

x2

x2

1

x 1x 2

x1 ∨ x 2

x 1x 2

……………………………………………………………………………

Операция инвертирования на элементах И-НЕ и ИЛИ-НЕ

x1

&

x1

x1

“1”

&

x1

x1

1

Теория автоматов. Модуль 2

x1

x1

1

x1

6/34

1. Построение комбинационных схем в

монофункциональном базисе И – НЕ, ИЛИ – НЕ

1. Исходное логическое выражения приведено в булевом базисе в форме ДНФ.

Произведём реализацию КС в базисах И-НЕ , ИЛИ-НЕ

x1

x2

X3

x4

Базис И-НЕ

y x1 x2 x3 x4

y x1x2 * x3x4

x1

1

y

x1

x2

x3

x4

Базис ИЛИ-НЕ

1

1

1

X3

x4

C=6

y x1 x2 x3 x4

x2

y x1 x 2 x3 x 4 x1 x 2 x3 x 4

y

1

y

C=6

y =y

y

C =7

Теория автоматов. Модуль 2

7/34

2. Построение комбинационных схем в

монофункциональном базисе И – НЕ, ИЛИ – НЕ

2. Исходное логическое выражения приведено в булевом базисе в форме КНФ.

Произведём реализацию КС в базисе ИЛИ-НЕ и в базисе И-НЕ

Базис ИЛИ-НЕ

y ( x1 x2 )( x3 x4 )

x1

x2

x3

x4

x1

1

&

$

у

x2

C= 6

x3

1

y ( x1 x2 )( x3 x4 )

y x1 x2 x3 x4

y ( x1 x 2 ) ( x3 x 4 )

Базис И-НЕ

x4

1

1

1

x1

x2

y x1x2 * x3x4

y y

x3

x4

Теория автоматов. Модуль 2

C= 6

у

y

1

C= 7

8/34

Заключение к вопросу

«Построение комбинационных схем в

многофункциональном базисе И – НЕ, ИЛИ – НЕ»

Если сложность исходных логических выражений в форме ДНФ

и КНФ одинакова, рекомендуется придерживаться следующего

простого правила:

– если схема строится на элементах И-НЕ, то исходное

выражение должно быть представлено в ДНФ,

– если схема реализуется на элементах ИЛИ-НЕ, то исходное

выражение должно быть представлено в КНФ

Теория автоматов. Модуль 2

9/34

Учет ограничений на число входов логических

элементов

Решение. Осуществляется декомпозиция логического терма на части или

подтермы. При этом ранг подтермов должен соответствовать числу входов

используемых ЛЭ. Решение усложняется, если исходный терм имеет групповое

отрицание.

В этом случае наиболее простой подход заключается в выделении подтермов с

нужным числом элементов p операцией двойного отрицания.

y x1x2 x3...x p x p 1... x1x2 ...x p * x p 1...x2 p * ...

Рассмотрим пример построения КС на элементах И-НЕ с двумя входами (2И-НЕ).

y x1 x 2 * x3 x4 * x1 x3 x 4

Не трудно подсчитать, что сложность

схемы, построенной без учёта

ограничения на число входов (инвертор,

2 элемента 2И-НЕ и 2 элемента 3И-НЕ),

равно 11. Итак: С1=11.

y x1 x 2 * x3 x4 * x1 x3 x 4

Число элементов 2И-НЕ с двумя входами,

необходимых для построения схемы – 6.

Дополнительно надо ещё два инвертора, поэтому

сложность реализации увеличилась с 11 до 15

(C2 = 15, C2 > C1).

Теория автоматов. Модуль 2

10/34

Минимизация не полностью определённых функций

Если значения функции на некоторых наборах не заданы, то она называется не

полностью определённой. Из такого рода функций практический интерес

представляет те из них, у которых некоторые наборы переменных никогда не

могут быть реализованы на практике, так как являются запрещёнными

(факультативные наборы). Этот факт можно использовать для создания благоприятных

условий их минимизации задаваясь соответствующими значениями функций на этих

наборах.

x 1x 2x 3x 4

F

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

….

1111

1

0

1

0

1

0

1

0

1

0

*

*

*

Пример. Построить КС, регистрирующую чётные десятичные числа

в диапазоне от 0 до 9, представленных кодом «8421».

F

x 3x 4

x 1x 2

00

01

11

10

00

1

1

01

1

1

11

*

10

1

*

*

*

*

*

Без учёта факультативных наборов:

F = x1 x4 ∨x2 x3 x4

С учётом факультативных наборов:

F = x4

Теория автоматов. Модуль 2

11/34

Синтез КС с несколькими выходами (или построение КС

для системы логических уравнений)

Пусть имеется некоторая система булевых функций

yi = fi (x1 ,…, xn); i = 1, …, m

(*)

Первый и достаточно простой способ сводится к задаче синтеза m комбинационных

схем с одним выходом:

x1

x2

.

.

.

.

xn

КС

y1

y2

.

.

.

.

ym

x1

x2

.

.

.

xn

КС1

y1

….

x1

x2

.

.

.

xn

КСm

ym

Недостаток этого подхода заключается в том, что, как правило, некоторые части схемы

будут дублироваться в различных КС.

Второй, оптимальный (с точки зрения минимизации оборудования) синтез КС с

несколькими выходами предполагает предварительно выполнение совместной

минимизации системы функций

Теория автоматов. Модуль 2

12/34

Продолжение содержания 12 слайда

Способ совместной минимизации системы функций на основе составления

импликативной матрицы, в силу его трудоёмкости, носит скорее академический

характер. При практической реализации синтеза КС с несколькими выходами часто

превалируют частные подходы выявления логических термов, являющихся общими для

нескольких функций. Иногда, в качестве такого терма выступает одна из функций

системы.

Рассмотрим простой пример совместной минимизации не требующей специальных

знаний.

Индивидуальная минимизация:

2 эл-т 2И, 2 эл-т 3И, 2 эл-т 2ИЛИ (С=14)

f1

x3 x4

00 01 11 10

x1 x2

00

1

01

11

10

1

1

1

1

f2

x3x4

00 01 11 10

x1x2

00

1

01

1

11

1 1

10

1

f1 = x3 x4 ∨x1 x2 x4

f 2 = x3 x4 ∨x1 x2 x3

Произведём минимизацию, при которой

многовыходовая импликанта x1x2x3x4

для произведения функций f1f2 остаётся

неизменной.

В этом случае получаем:

2 эл-т 2И, 1 эл-т 4И, 2 эл-та 2 ИЛИ (С=12)

x3x4

x1x2

00

01

11

10

f1 f2

00 01 11 10

f1 = x3 x4 ∨x1x2 x3 x4

1

f 2 = x3 x4 ∨x1x2 x3 x4

Теория автоматов. Модуль 2

13/34

Синтез типовых узлов комбинационного типа

К таким узлам относят:

– устройства арифметического типа: сумматоры, вычитатели,

умножители, делители;

– логические устройства и преобразователи кодов, например,

дешифраторы и шифраторы, мультиплексоры и демультиплексоры,

цифровые компараторы и др.

В лекциях будут рассмотрены:

Синтез одноразрядного сумматора [SM];

Многоразрядный сумматор с последовательным переносом;

Многоразрядный сумматор с параллельным переносом.

Дешифраторы [DC];

Шифраторы [CD];

Мультиплексоры [MUX] и демультиплексоры [DMX].

Теория автоматов. Модуль 2

14/34

Синтез одноразрядного сумматора [SM]

Одноразрядные сумматор имеет три входа (два – одноимённые разряды

слагаемых и перенос из предыдущего разряда) и два выхода (сумма и перенос в

следующий разряд). В свою очередь одноразрядные сумматоры строятся

на основе полусумматоров (half adder). Ниже приведены условные

обозначения одноразрядного сумматора, полусумматора и таблица истинности

его работы.

ai

a

bi

ci

b SM

ci

s

co

si

ai

ci+1

bi

a

HS

b

s

si

co

ci+1

ai

0

0

1

1

Уравнения, описывающие работу полусумматора:

S i ai bi ai bi v ai bi (1)

bi

0

1

0

1

si ci+1

0 0

1 0

1 0

0 1

Ci 1 aibi (2)

Представим уравнение (1) в формате И-НЕ/И-НЕ для построения КС, используя

обычный приём (3) и эмпирический подход, минимизирующий число переменных,

подвергающихся инверсии (4).

S i ai bi v ai bi ai bi ai b

i

(3)

Si ai bi ai bi ai b i bi ai bi ai ai bi bi ai bi a i

Теория автоматов. Модуль 2

(4)

15/34

Схема полусумматора

&

ai

bi

&

&

Si aibibi aibi ai

&

Ci 1 aibi

1

ai

bi

a

b

s

Si

HS co

Ci 1

co

Ci 1

ci +1 = ai bi

Ci 1 aibi

S i ai bi ai bi vaai b

i bii bi ai bi ai ai b i b i ai bi a i

Теория автоматов. Модуль

(2)

(4)

16/34

Схема одноразрядного сумматора

Таблица истинности

одноразрядного сумматора

ai

0

0

1

1

0

0

1

1

bi

0

1

0

1

0

1

0

1

ci

0

0

0

0

1

1

1

1

si

0

1

1

0

1

0

0

1

ci+1

0

0

0

1

0

1

1

1

Схема

одноразрядного

сумматора

Уравнения, описывающие работу

одноразрядного сумматора

Si ci (ai bi ) ci (ai bi ) ai bi ci

1

2

2

1

Ci +1 = aibi ∨ci ( ai ⊕bi ) = ai bi * ci (ai bi )

ci

a

HS

a i bi

ai

bi

a

s

HS co

co

b

b

s

co

aibi

si

ci ( ai ⊕bi )

&

ci+1

Pi =ai bi

Gi =ai bi

Теория автоматов. Модуль 2

17/34

Многоразрядный сумматор с последовательным

переносом

a3

s

c4

CO

SM

a

b

CI

a2

b3

s

c3

s3

CO

SM

a

b

CI

s2

a1

b2

s

c2

SM

CO

a

b

CI

s1

a0

b1

s

c1

CO

SM

a

b

CI

c0

s0

4-разрядный сумматор с последовательным переносом (сигнал распространяется

справа налево) реализует соотношение: S=A+B. Сигналы переноса при этом

вырабатываются последовательно: С1 – вырабатывается спустя время tзад относительно

задания младшей пары разрядов {a0,b0}, правильное значение С2 будет сформировано

спустя время tзад относительно пары разрядов {a1,b1} и т. д. Общее время сложения

определится временем распространением переноса (наихудший случай) от самого

младшего разряда к самому старшему. Легко доказать, что:

t зад 2 * t задЛЭ

Здесь

t задЛЭ

- время задержки, создаваемое одним ЛЭ.

Общее время суммирования в наихудшем случае равно:

Теория автоматов. Модуль 2

Tmax 2n * t зд. ЛЭ

18/34

Многоразрядный сумматор с параллельным

переносом

si

ci+1

s

SM

CO G

Gi

P

a

ai

b

bi

CI

ci

Pi

Представим одноразрядный сумматор следующим условным

обозначением (как и в предыдущем случае примем, что сигнал

распространяется справа налево):

Pi ai bi - функция распространения переноса

Gi ai bi - функция генерации переноса

ci 1 ai bi ci (ai bi ) Gi ci Pi

С целью формирования, одновременно во времени, переносов Ci+1 каждым

сумматором, представим поразрядные выражения для переносов в развёрнутом виде.

с1 G0 c0 P0

c2 G1 c1 P1 G1 G0 P1 c0 P0 P1

c3 G2 c2 P2 G2 G1P2 G0 P2 P1 c0 P0 P1P2

(*)

c4 G3 c3 P3 G3 G1 P2 P3 G0 P1 P2 P3 G2 P3 c0 P0 P1 P2 P3 G c0 P

Переменные Pi, Gi зависит от «первичных» сигналов ai и bi и появляются

одновременно спустя задержку, осуществляемую полусумматором HS , входящим в состав

SM. Независимо от вида выражения для переносов С1 … С4 каждая комбинационная

схема (КС), реализующая любое из выражений системы (*), является 2-х ступенчатой, типа

И-ИЛИ, поэтому время задержки сигналов каждой КС одно и то же. Комбинационная схема,

реализующая все выражения системы (*), получила название схемы ускоренных

переносов (СУП).

Теория автоматов. Модуль 2

19/34

Схема сумматора с параллельными переносами

(533,555ИМ6; SNxx283)

s3

a3

s

SM

CO G

C4

G3

P

P3

a

b3

s1

b

CI

a1

s

SM

CO G

c3

G2 P2 c2

G1

P

P1

a

b

CI

a0

b1

s0

s

CO G

c1

Схема ускоренных переносов (СУП)

155,531,533ИП4 (SNxx182)

G

P

SM

G0

P

P0

b0

a

b

CI

c0

c0

c 4 = G + c0 P

В схеме ускоренных переносов (СУП) помимо выходного переноса формируются и его

составляющие, функции G и P. Данные переменные G и P используются для обеспечения

интерфейса между 4-х разрядными секциями сумматора при наращивании разрядности.

16-разрядный сумматор будет включать четыре 4 -разрядных секции сумматора и одну

схему СУП.

Теория автоматов . Модуль 2

20/34

16-разрядный сумматор с параллельно-параллельным

переносом

s12 ,...,s15

s

b12 ,…,b15

a12 ,…,a15

4-х раз. a

SM

CO G

P

b

CI

s0 ,...,s3

C12

s

b0 ,…,b3

a0 ,…,a3

4-х раз. a

SM

CO G

P

b

CI

c0

C4

C16

G3

P3

c3

G2 P 2

c2

G1 P1

c1

Схема ускоренных переносов (СУП; SNxx182)

G

G0

P0

c0

c0

P

Теория автоматов . Модуль 2

21/34

Дешифраторы

x1

1

x2

x3

2

x4

8

DC

4

0

1

2

3

.

.

.

15

y0

y1

y2

y3

.

.

.

y15

Унарны

й код

m=2n

n-раз.

двоичный

код

Дешифратор (Decoder, DC) - это устройство, которое преобразует n -разрядный двоичный

код в унарный код разрядностью 2n. Унарный код - это такой код, который содержит 1 в

каком-либо одном разряде (в английской литературе именуется как код «1 из N», или OHE

(One-Hot-Encoding)).

x4 x3 x2 x1

0000

0001

0010

0011

...

1111

y0

1

0

0

0

y1 y 2

0 0

1 0

0 1

0 0

y3

0

0

0

1

…

0

y4 …. y15

0

0

0

0

0

0

0

0

Enable E

0 0 0

0

1

E

Рассмотрим построение схемы дешифратора DC (3 8) в двух логических базисах: И-НЕ

и ИЛИ-НЕ. Помимо традиционных вопросов, здесь дополнительно отметим следующие два:

1) Создание в типовом функциональном узле буферного каскада для обеспечения

«единичной кратности» нагрузки по каждому из входов схемы;

2) Взаимосвязь функциональной схемы узла с УГО этого узла.

Выходы дешифратора (таблица истинности DC (3 8) аналогична приведённой выше и

здесь опущена) определяются следующими выражениями:

y0 = x3 x2 x1

y2 = x3 x2 x1

y1 = x3 x2 x1

y3 = x3 x2 x1

.......... ....

Теория автоматов . Модуль 2

y6 = x3 x2 x1

y7 = x3 x2 x1

22/34

Дешифраторы (продолжение)

Входы DC

x1

x2

x3

1

1

1

x1

1

1

1

x1

x2

x2

x3

x3

Выходы для

ЛЭ

дешифратора

Реальная схема дешифратора DC (3→8), помимо элементов И-НЕ (или ИЛИНЕ) содержит блок из буферных инверторов для обеспечения «единичной

кратности» нагрузки по каждому из входов.

Функциональные схемы DC (3 8) в двух логических базисах вместе с УГО

приведены на следующем слайде. Обратите внимание, что указатель инверсного

входа или выхода для логического элемента на функциональной схеме, в общем

случае никак не связан с соответствующими обозначениями на УГО DC .

Теория автоматов . Модуль 2

23/34

Дешифраторы (продолжение)

Базис И-НЕ

Базис ИЛИ-НЕ

x1

x2

&

x3

y0 x3 x2 x1

Правило преобразования

одной схемы в другую:

использование двойственного

элемента с инверсными

сигналами на входах (закон

отрицания).

x1

x2

y1 x3 x2 x1

x3

x1

x2

x3

x1

x2

x3

y7 x3 x2 x1

a

a

Z

1

b

x1

x2

x3

1

y1 x3 x2 x1

1

x1

z

x2

x3

b

E

y0 x3 x2 x1

y7 x3 x2 x1

1

E

x1

x2

x3

E

1 DC 0

2 38 1

2

4

7

Е

y0

y1

y7

y2

y7

x1

x2

x3

E

Теория автоматов . Модуль 2

1 DC 0

2 38 1

2

4

7

Е

y0

y1

y2

y7

24/34

Шифраторы

Enable E

x0

x1

x2

x3

x4

x5

x6

x7

Enable E

0

1

2

3

4

5

6

7

E

0

1

2

3

4

5

6

7

E

CD 1

8->3

2

4

y1

y2

y3

n-раз. двоичный

код

x0

x1

x2

x3

x4

x5

x6

x7

Приоритетный шифратор вырабатывает на

выходе двоичный номер (выводы А2, А1, А0)

старшего запроса (старшей «1» во входном

двоичном коде). Вывод GS – выходной сигнал,

свидетельствующий о наличии хотя бы одного

возбуждённого входа.

а7 а6 а5 а4 а3 а2 а1 а0 GS A2 A1 A0

PRCD

8->3

1

А1

2

А2

4

А3

GS

двоичный код

старш. единицы

Унарный код

m=2n

Шифратор преобразует унарный код в выходной двоичный, при этом двоичный код

определяет номер активного входа. В “чистом” виде шифратор применяется редко, т.к.

если в схеме возбудить несколько входов, то её поведение непредсказуемо, поэтому на

практике используется приоритетный шифратор.

Групповой

сигнал

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

.

0

0

0

0

.

0

0

0

1

.

0

0

1

0

1

1

x

x

x

x

x

x

x

x

x

Теория автоматов. Модуль 2

0

1

x

x

x

0

1

1

1

x

x

x

x

1

1

0

0

0

0

0

0

0

1

…

1 1

1 1

0

0

1

0

0

1

25/34

Мультиплексоры [MUX]

Мультиплексором называется схема, осуществляющая передачу сигналов с одной из

входных линий на выход. Выбор входной (информационной) линии производится двоичным

кодом, поступающим на управляющие (адресные) входы мультиплексора. MUX с m

управляющими входами Am , .., A1 имеет 2 m информационных входов D0 ,D1,…,D2m-1 .

2m

m=2

D0

D1

D2

D3

m

А2

А1

E

E

D0

D1

D2

MUX

41

F

1

D3

А1

Функция, реализуемая одноразрядным

мультиплексором MUX “41”:

А2

E

F

1 DC 0

1

2

2

E

3

F E ( D0 * A2 A1 D1 * A2 A1 D2 * A2 A1 D3 * A2 A1 )

Для коммутации нескольких k- разрядных шин требуются уже «шинные» или

многоразрядные мультиплексоры, которые строятся на основе одноразрядных (требуется kодноразрядных MUX).

В цифровой схемотехнике MUX находят применение также в качестве универсальных

логических модулей для реализации произвольных булевых функций от n –переменных, где

n m , m – число адресных входов мультиплексора.

Теория автоматов . Модуль 2

26/34

Синтез комбинационных схем на

мультиплексорах

В общем случае на основе мультиплексора могут быть воспроизведены булевы

функции y=f (x3, x2, x1) от числа переменных n m, где m - число адресных

входов мультиплексора. Случай n =m считается тривиальным в отличие от

n > m. На практике используется несколько способов решения поставленной

задачи:

- классический способ,

- способ, основанный на сравнении таблиц истинности для функции

и мультиплексора,

- способ, основанный на сравнении карт Карно для функции и

мультиплексора.

Правило: На адресные входы задают переменные, характеризующиеся

наибольшей частотой вхождения в МДНФ функции

Теория автоматов . Модуль 2

27/34

1. Классический способ

Классический способ предусматривает предварительное разложение искомой

функции y=f (x3, x2, x1) в ряд Шеннона по m переменным. При этом разложение

выполняется по тем переменным, которые будут задаваться на адресные входы

мультиплексора. Пускай это будут переменные x2 и x1 (адресные входы A2 и A1

соответственно)

y f ( x 3 , x 2 , x1 ) x 2 x1 f0 ( x 3 ,0,0) x 2 x1 f1 ( x 3 ,0,1)

x 2 x1 f2 ( x 3 ,1,0) x 2 x1 f3 ( x 3 ,11

, ).

Здесь f0, f1, f2, f3 – остаточные функции от одного аргумента - переменной x3.

Если сравнить уравнение (1) с уравнением (2), описывающим работу MUX (2→1),

F E A2 A1D0 A2 A1D1 A2 A1D2 A2 A1D3

то не трудно прийти к выводу, что для обеспечения их тождественности необходимо

выполнить условия:

x2 A2 , x1 A1 , f 0 D0 , , f 3 D3

Итак, для построение схемы необходимо определить остаточные функции от

переменной x3 при заданных значений для переменных x2 и x1:

f 0 x3 ,0,0, f1 x3 ,0,1, f 2 x3 ,1,0, f 3 x3 ,1,1

Теория автоматов. Модуль 2

28/34

2. Способ, основанный на сравнении таблиц истинности

для функции и мультиплексора

Способ удобен для применения, если

функция f (xn , …, x1) задана

таблицей истинности.

В этом случае на таблицу

истинности функции как бы

«накладываем» таблицу

истинности работы MUX.

Рассматривая условия равенства

значения функции со значением

входной переменной, коммутируемой

MUX на выход для каждого адресного

кода, получаем необходимые условия

коммутации информационных входов

мультиплексора.

В данном примере переменная x1

оставлена для подачи на

информационные входы MUX .

A2

A1

x3

x2

x1

Функция

f(x3,x2,x1)

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

MUX

F

Условие

F=f

D0

D0=0

D1

D1=1

D2

D2=1

D3

D3=x1

Почему?

Теория автоматов. Модуль 2

29/34

3. Способ, основанный на сравнении карт Карно для

функции и мультиплексора

Итак пусть функция, рассматриваемая в предыдущем способе задана картой Карно.

x3

f

1 1 1 1 0

0 0 0 1 1 x2 x1

00 01 11 10

Вариант 1

x3

x2

A2

A1

f МДНФ x2 x3 x2 x3 x1x2

xi

Частота вх. В МДНФ

x1

1

x2

3

x3

2

Способ задания переменных функции на адресные входы MUX

!

Вариант 2

x2

x1

A2

A1

Вариант 3

x3

x1

A2

A1

Карта Карно для MUX с учётом способа задания переменных на адресные входы

A2

A2

x3

F

1 D2 D2 D3 D3

0 D0 D0 D1 D1 A1 x1

00 01 11 10

1 D0 D1 D3 D2

F

0 D0 D1 D3 D2 A2 A1

00 01 11 10

1 D2 D3 D3 D2

F

0 D0 D1 D1 D0 x2 A1

00 01 11 10

Уравнения для коммутации информационных входов MUX, полученные по результатам

сравнения карт Карно для MUX и функции:

D0=0, D1=1, D2=1, D3=x1

D0=x3, D1=x3, D2= ¬ x3, D3=1

D0=x2, D1=x2, D2= ¬ x2, D3=1

Правило: На адресные входы задают переменные, характеризующиеся наибольшей

частотой вхождения в МДНФ функции (Вариант 1)

Теория автоматов. Модуль 2

30/34

Схема включения MUX(4→1), реализующая

рассмотренную в примерах, функцию (Вар. 1)

x3

f

D0=0, D1=1, D2=1, D3=x1

1 1 1 1 0

0 0 0 1 1 x2 x1

00 01 10 11

Вариант 1

x3

x2

A2

A1

f МДНФ x2 x3 x2 x3 x1x2

x1

x2

x3

0

1

1

D0 MUX

D1 41

D2

F

D3

f(x3,x2,x1)

А2

А1

E

Теория автоматов. Модуль 2

31/34

Демультиплексоры [DMX]

Для передачи данных по общему каналу с разделением времени нужны не только

MUX, но и устройства обратного назначения – демультиплексоры DMX.

Одноразрядный демультиплексор имеет один информационный вход, k –адресных

(управляющих) входов, и 2 k выходов. Обычно в качестве DMX используются

дешифраторы, имеющие входы разрешения дешифрации. На рисунке представлена

схема включения дешифратора DC (38) в качестве DMX (18)

Адресные

входы (k)

A1

A2

A3

1

MUX

n

E

1 DC 0

1

2 38

2

4

y0

y1

y2

Е

y7

7

Выходы

(2k)

Информационный

вход

Адресная шина управления

MUX,

Теория автоматов

DMX

k log 2 n

n

32/34

Контрольные вопросы

1. Что предполагается под понятиями:

- анализ комбинационной схемы (КС),

- синтез КС.

2. Назовите критерии оценки качества комбинационной схемы.

3. Сформулируйте закон отрицания в булевой алгебре. Область практического

применения.

4. Сформулируйте рекомендации к выбору монофункционального базиса «И – НЕ»

(«ИЛИ – НЕ») при построении КС.

5. В чём заключается способ преобразования логических выражений, если не

удовлетворяются условия по числу входов, имеющихся в распоряжении

разработчика ЛЭ.

6. Назовите особенности синтез КС с несколькими выходами.

Теория автоматов. Модуль 2

33/34

Контрольные вопросы (продолжение)

7. Нарисуйте УГО одноразрядного сумматора (полусумматора).

8. Составьте таблицу истинности работы одноразрядного сумматора. Запишите

логические уравнения его работы.

9. Изобразите функциональную схему одноразрядного сумматора.

10. Какие дополнения необходимо внести в схему одноразрядного сумматора с целю его

использования в многоразрядном сумматоре с параллельными переносами.

11. Сформулируйте назначение схемы ускоренных переносов (СУП) в многоразрядном

сумматоре с параллельными переносами.

12. Объясните необходимость реализации условия обеспечения «единичной кратности»

нагрузки по каждому из входов интегральной схемы типовом функциональном узле.

13. Чем объясняются условия применения мультиплексора MUX в качестве

универсальных логических модулей для реализации произвольных булевых

функций от n –переменных, где n m , m – число адресных входов мультиплексора.

Какие способы такого использования вы знаете?

14. Возможно ли схемотехническое решение использования дешифратора (DC) в качестве

демультиплексора (DMX).

Теория автоматов. Модуль 2

34/34