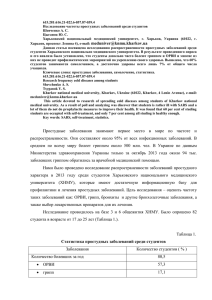

Структуры данных для поиска, распознавания

реклама

МЭС 2012, 8-12 октября МЕТОДЫ ВЫСОКОУРОВНЕВОГО И ЛОГИЧЕСКОГО МОДЕЛИРОВАНИЯ В САПР СБИС В.И. ХАХАНОВ, MURAD ALI ABBAS, Е.И. ЛИТВИНОВА, И.В. ХАХАНОВА, BAGHDADI AMMAR AWNI ABBAS Kharkov National University of Radio Electronics, Ukraine [email protected] Kharkov National University of Radio Electronics, Design Automation Department, hahanov.kture.kharkov.ua 1 МЭС 2012, 8-12 октября Agenda Метрика киберпространства для оценивания решения ; Структуры данных для поиска, распознавания и принятия решения; Архитектура логического ассоциативного мультипроцессора; Инфраструктура векторнологического анализа; Восстановление работоспособности. Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 2 МЭС 2012, 8-12 октября Итеративный характер проектирования $103 Уточнение требований на фазе RTLпроектирования $105 $107 = КРАХ Проблемы требований в момент готовности чипа к производству Уточнение RTLмодели на фазе размещения Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 3 МЭС 2012, 8-12 октября Роль функциональной верификации Проверка свойств Проверка эквивалентности Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 4 МЭС 2012, 8-12 октября Цели верификации на основе ассерций Улучшение наблюдаемости за внутренним состоянием системы Упрощение локализации функциональных нарушений Автоматическая активация и проверка Статистика активации ассерций как метрика функционального покрытия, Ассерции как строгая форма спецификации системы Статистика активации ассерций как критерий эффективности вычислительных затрат Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 5 МЭС 2012, 8-12 октября System-Level Verification Environment Modeling in SystemC TLM 2.0 Verification in SystemVerilog using SVA assertions •System-Level Verification Environment Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] МЭС 2012, 8-12 октября Fault Model • Data faults Generic payload’s data fields • Control faults • Generic payload’s data fields • Handshaking • Phase • Return status • Transport interfaces Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 7 МЭС 2012, 8-12 октября Fault Simulation •Memory 1 •Memory k •PE1 •PEm •PE3 •PEn •Switch •PE1 •PE2 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 8 МЭС 2012, 8-12 октября Testability & BIST Feed Back PE (5) ATE Memory ATE Memory PE 1 PE 2 PE 3 PE 4 BIST Controller Distribution Point Distribution Point PE 1 PE 2 Feed Back PE (5) PE 3 Collection Point PE 4 ATE Memory Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] Collection Point ATE Memory 10 МЭС 2012, 8-12 октября Связь ассерций с методами верификации Кроме того ассерции связаны с: Верификацией пересечений тактовых доменов (Clock Domain Crossing) Верификацией на уровне связи между TLM- и RTL-компонентами Ассерционными библиотеками (Open Verification Library) Верификационными IP Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 11 МЭС 2012, 8-12 октября Метрика киберпространства для оценивания решения Дискретное векторно-логическое пространство – киберпространство – совокупность взаимодействующих по соответствующей метрике информационных процессов и явлений, описываемых векторами (кортежами) логических переменных и использующих в качестве носителя компьютерные системы и сети. Метрика кибернетического пространства определяется единственным равенством (1), которое формирует нуль-вектор для xor-суммы расстояний между ненулевым и конечным числом n точек (объектов), замкнутых в цикл: β di 0. i 1 Классическое задание метрики для определения взаимодействия одной, двух и трех точек в векторном логическом пространстве, является частным случаем β -метрики при i=1,2,3 соответственно: d1 0 a b; M d1 d 2 0 d(a , b) d(b, a ); d1 d 2 d3 0 d(a , b) d(b, c) d(a , c). Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 12 МЭС 2012, 8-12 октября Triangle Cyber Space Имеется пять точек в векторном пространстве: (000111, 111000, 101010, 010101, 110011). Замыкание этих точек в цикл дает следующие стороны-расстояния в пятиугольнике: (111111, 010010, 111111, 100110, 110100). Покоординатное сложение всех векторов дает результат: (000000). Практическая значимость данного факта заключается в возможности восстановления любого расстояния в замкнутом цикле, если известны (n-1) сторона фигуры. Для треугольника это означает восстановление третьей стороны по известным двум. Если же создать из треугольников замкнутое логическое пространство (рис. 1), то можно сэкономить 66% от объема данных, который формирует все расстояния в логическом пространстве. Функциональная зависимость отношения восстанавливаемых сторон замкнутого в треугольник пространства к общему числу n слоев треугольной структуры определяется выражением: 1 2 (i 1) ( 1) (3 i) i 1,n 3 n 1 1 2 n 1 1 n 3 n 3 . 3 n 1 3 n 1 3(n 1) Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 13 МЭС 2012, 8-12 октября Метрика кибернетического многозначного векторнологического пространства Метрика кибернетического многозначного векторно-логического пространства, где каждая координата вектора, соответствующего объекту, определена в алфавите, составляющем булеан на универсуме примитивов мощностью p: n β Δ di i 1 Единственная координатная операция di, jΔdi 1, j , используемая, например, в четырехзначной модели Кантора, определяется соответствующей таблицей: Δ 0 1 x 0 x 1 0 1 x 0 1 x 1 0 x 0 1 x 0 1 x 0 0 0 1 1 1 x 0 1 x 0 1 x 0 0 x x 0 1 x 1 x 1 Мощность алфавита (булеана) определяется выражением x x x x x 0 1 x m 2p a 0 1 x ~ a 1 0 x , где p – число примитивов. Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 14 МЭС 2012, 8-12 октября Интегральная теоретико-множественная метрика для оценивания качества запроса Интегральная теоретико-множественная метрика для оценивания качества запроса есть функция взаимодействия многозначных по координатам векторов mA , которая определяется средней суммой трех нормированных параметров: кодовое расстояние d(m, A) , функция принадлежности μ (m A) и функция принадлежности : С учетом изоморфизма теоретикомножественных и логических операций арифметический критерий без усреднения функций принадлежности и кодового расстояния можно трансформировать к виду: Q d (m, A) μ (m A) μ (A m), k d (m, A) card (mi Ai U); i 1 1 [d ( m, A ) ( m A ) ( A m)], 3 k 1 d ( m, A ) [ n card ( m i A i )]; i 1 n ( m A ) 2 c a ; ( A m ) 2 c b ; Q k k μ (m A) card (Ai U) card ( mi Ai U); i 1 k μ (A m) card (mi U) card (mi Ai U); 1 {mi , Ai } {0,1}; U x {mi , Ai } {0,1, x}. ( A m) i 1 k a card ( A i x ); b card ( m i x ); i 1 i 1 k c card ( m i A i x ); i 1 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 15 МЭС 2012, 8-12 октября Интегральная теоретико-множественная метрика для оценивания качества запроса Для того, чтобы окончательно исключить арифметические операции при подсчете векторнологического критерия качества, необходимо логически объединить три оценки в одну: Q d(m, A) μ (m A) μ (A m) m A A m A m m A m A [A ( m A)] [m ( m A)] m A [Am AA mm mA ] (Am mA ) [Am AA mm mA ] Am mA Am AA mm mA m A. Процедура вычисления векторного критерия качества зависит от значности алфавита: m A {mi , Ai } {0,1}; Q mΔA {mi , Ai } {0,1, x}. Для двоичного алфавита таблица истинности координатной xor-операции имеет вид: 0 1 0 0 1 1 1 0 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 16 МЭС 2012, 8-12 октября Регистр сдвига и уплотнения единиц Процесс-модель поиска оценки лучшего решения с минимальным числом единичных координат из более, чем двух альтернатив, включает следующие операции: 1) Первоначально в вектор-результат Q, в котором будет сохранено лучшее решение, заносятся единичные значения во все координаты (худшее решение) и одновременно осуществляется операция slc сдвига влево с уплотнением единиц текущего вектора Q i 2) Выполняется сравнение двух векторов: Q и очередной оценки Q i из списка решений. 3) Реализуется векторная операция and (Q Q i ) Q Q( ((Q Qi ) Q)) Qi ( ((Q Qi ) Q)); а результат сравнивается с вектором Q. Y ((Q Qi ) Q); 4) Процедура поиска оценки лучшего Q QY Qi Y. решения повторяется n раз. Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 17 МЭС 2012, 8-12 октября Структуры данных для поиска, распознавания и принятия решения Метрика качества дает возможность оценивать близость пространственных объектов друг к другу или их взаимодействие. j i n P(m, A) min Qi (m Δ Ai ) [(Qi Q j ) Qi ] 0; i 1 j1, n Q(m, A) (Q1, Q 2 ,..., Qi ,..., Q n ); Взаимодействие P(m, A ) , A (A1, A 2 ,..., Ai ,..., A n ); входного вектора-запроса m (m1, m 2 ,..., m r ,..., mq ) с множеством A (A1, A 2 ,..., Ai ,..., A m ) формирует решения с выбором лучшего из них по минимальному критерию качества: Δ {and , or, xor , not , slc , nop}; Ai (Ai1, Ai 2 ,..., Aij ,..., Ais ); Aij (Aij1, Aij 2 ,..., Aijr ,..., A msq ); m (m1, m 2 ,..., m r ,..., m q ). Qi d(m, Ai ) μ (m Ai ) μ (Ai m), d(m, Ai ) m Ai ; μ (m Ai ) Ai m Ai ; μ ( A i m) m m A i . P(m, A) min Qi[m (A1 A2 ... Ai ... Am )] Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] МЭС 2012, 8-12 октября Архитектура логического ассоциативного мультипроцессора Логический ассоциативный мультипроцессор (ЛАМП) — это эффективная сеть процессоров, которая обрабатывает данные и обеспечивает обмен информацией между компонентами сети в процессе их решения. Базовая ячейка — векторный процессор для вычислителя может быть синтезирован на 200-х вентилях, что дает возможность сеть, содержащую 4096 вычислителей, легко реализовать в кристалле заказной СБИС, используя современную кремниевую технологию. Однако основное назначение ЛАМП — получение квазиоптимального решения в задаче поиска и (или) распознавания с использованием компонентов архитектуры, ориентированных на выполнение векторных логических операций: n P(m, A) min Qi (m Δ Ai ), m {m a , m b , m c , m d }. i 1 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 19 МЭС 2012, 8-12 октября Архитектура ЛАМП и структура УПУ Особенности реализации логического процессора заключаются в наличии трех бинарных (and, or, xor) и двух унарных (not, slc) операций. Последние можно присоединять к такту обработки регистровых данных, выбрав одну из трех операций (not, slc, nop — нет операции). Структура блока логических вычислений Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 20 МЭС 2012, 8-12 октября Инфраструктура векторно-логического анализа Для детализации структуры векторного процессора и УПУ далее рассмотрены аналитические и структурные процесс-модели, выполняющие анализ А-матрицы по столбцам или строкам. Первая из них предназначена для определения множества допустимых решений относительно входного запроса: n m mai [( m b Ai ) m b ]; i 1 n Ai (m b Ai ). i 1 Вторая осуществляет поиск оптимального решения на множестве строк, найденных с помощью первой модели в результате их анализа: m sb ( Ai ) ( mm b ( Ai ) ( m ai 1 m ai 1 Ai ) m ai 0 Ai ) m ai 0 Все операции, выполняемые двумя процесс-моделями — векторные. Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 21 МЭС 2012, 8-12 октября Восстановление работоспособности Процесс-модель поиска квазиоптимального покрытия: m b (m b Ai ); n [( m b Ai ) mb ]. m ai i 1 Восстановление работоспособности дефектных ячеек памяти: 1 . . . . 1 . . . . . Оптимальное решение: . . 1 . . 1 . . . . . . . . . 1 1 . . . . . . 1 . . . . 1 . . . . . . 1 . . . . 1 . . . . . . . 1 . . 1 . . . 1 . . . . . . . 1 . . . . 1 . . . . . . 1 . . 1 . . . . . . . . 1 . . . 1 . . . . . . 1 ma 1 1 1 1 1 0 0 0 0 0 0 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 22 МЭС 2012, 8-12 октября Процесс-модель встроенного сервисного обслуживания Оценка эффективности процессмодели: 1 E F(L, T, H) min [ (L T H)], 3 Y (1 P) n ; L 1 Y (1 k ) 1 (1 P) n (1-k) ; T (1 - k) H s s H H a ; H Ha s H H a . Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 23 МЭС 2012, 8-12 октября Векторный логический анализ информации 1) 2) 3) 4) 5) 6) 7) Семь параметров повышения производительности мозгоподобного компьютера: Исключение арифметических операций из системы команд процессора. Использование в вычислительных процедурах алгебры векторной логики. Компьютер выигрывает у человека в способности быстро анализировать большое число существенных логических переменных, сконкатенированных в вектор-запрос. Применение мультипроцессорной матрицы для распараллеливания вычислительных процедур. Использование векторного двоичного критерия качества для оценивания решения. Введение операции векторизации в целях генерирования ассоциации минимального S-вектора существенных переменных, необходимых для поиска решения. Создание вектор-бит D-оператора девекторизации для формирования двоичного решения на основе применения логических операций and, or, not или их комбинации к вектору (векторам) существенных переменных. Создание P-платформы логических процесс-моделей (IPcores) для поиска, распознавания и принятия решений. Infrastructure for logic decision making ESL – Electronic System Level Design Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 24 МЭС 2012, 8-12 октября Процесс-модели анализа ассоциативных структур данных Девекторизация есть автоматная, в общем случае, процедура формирования двоичного решения на основе определенных двоичных значений вектора (векторов) существенных переменных. Процесс-модель девекторизации логических условий, подготовленных для принятия решения, имеет две альтернативные структуры: Первая – комбинационная, формирует мгновенно двоичное решение, например, при наличии единичных значений на n входах элемента and. Вторая – последовательностная или автоматная, – накапливает совокупность единичных условий n переменных во времени с помощью, например, счетной структуры. Возможна комбинация в виде параллельно-последовательной или последовательнопараллельной схемы для принятия решения. В общем случае, девекторизатор, как цифровой формирователь решения, может быть представлен в виде автоматной модели первого рода: Y( t ) f [m( t ), Z( t 1)]; Z( t ) g[m( t ), Z( t 1)]. Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 25 МЭС 2012, 8-12 октября Примитивные процесс-модели принятия решений Каждому варианту взаимодействия можно поставить в соответствие теоретико-множественную диаграмму, а также логическую схему, которая соответствует процесс-модели принятия решения. На рынке электронных технологий наиболее распространенными являются две альтернативные модели данных: явная табличная и неявная аналитическая. Таблица истинности есть совокупность векторов, задающих поведение дискретного Y f ( X) объекта в многозначном (двоичном) алфавите с выраженным отношением координат входных и выходных переменных: C (C1, C 2 ,..., Ci ,..., C n ), Ci (X i , Yi ), Cij {1, 2 ,..., r ,..., k } Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 26 МЭС 2012, 8-12 октября Диаграммы Хассе для минимизации логической функции H-метод минимизации булевых функций. Процесс-модель минимизации булевой функции по избыточной таблице истинности может быть получена, если использовать диаграмму Хассе в качестве формы, позволяющей оптимально задавать иерархию и эволюцию любой ассоциативной логической структуры. На рисeyrt представлены три графа, где первый и второй соответствуют нулевым и единичным строкам таблицы истинности F, а третий является 1 результатом вычитания G G i \ G i0 Достоинства диаграммы Хассе в данном примере заключаются в эффективном формировании решения на основе теоретико-множественного вычитания содержимого вершин нулевого графа из соответствующих вершин единичного графа. X1 X 2 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 X3 0 1 0 1 0 1 0 1 X1X 2 00 00 01 01 10 10 11 11 X1X 3 00 01 00 01 10 11 10 11 X 2X3 00 01 10 11 00 01 10 11 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] X1X 2 X 3 000 001 010 011 100 101 110 111 mF 1 0 1 0 1 0 0 1 27 МЭС 2012, 8-12 октября Граф Хассе Граф Хассе – идеальное представление таблицы истинности любой теоретикомножественной операции. Она компактна, не избыточна, но взамен требует несколько тактов для своего выполнения. Если бы удалось построить предметные ассоциации в соответствии с графом, то все вопросы анализа и синтеза решались бы на уровне операций в головном мозге. Алфавит бинарных отношений Иерархия анализа сочетаний слов в предложении Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected] 28 МЭС 2012, 8-12 октября Выводы Предложен новый подход векторно-логической обработки ассоциативных данных с полным исключением арифметических операций, влияющих на быстродействие и аппаратную сложность, который может быть эффективно реализован на основе использования современной микроэлектронной аппаратуры в виде мультипроцессорной цифровой системы на кристалле. Фактическая реализация подхода основана на предложении моделей и методов, использующих общую идею векторно-логической метрики киберпространства: 1. Процесс-модели анализа ассоциативных таблиц ориентированные на достижение высокого быстродействия анализа информационных объектов и подсчета критериев качества их взаимодействия на основе векторных логических операций для поиска, распознавания образов, принятия и оценивания решений в киберпространстве. 2. Метод параллельного решения ассоциативно-логических задач с минимальным числом векторных логических операций и полным исключением арифметических команд, что обеспечивает высокое быстродействие, минимальную стоимость и незначительное энергопотребление вычислителя, реализованного на кристалле программируемой логики. 3. Новые векторно-логические процесс-модели встроенного диагностирования цифровых систем на кристаллах, поиска квазиоптимального покрытия, использующие средства логического ассоциативного мультипроцессора, параллельные операции вычислительных процессов и векторно-логический критерий качества. Практическая значимость полученных результатов подтверждена созданием встроенного компонента для диагностирования и восстановления работоспособности памяти в цифровой системе на кристалле. Дальнейшие исследования направлены на разработку прототипа логического ассоциативного мультипроцессора для решения актуальных задач поиска, распознавания и принятия решений с помощью векторного логического анализа. 29 Kharkiv National University of Radio Electronics, Design Automation Department, e-mail: [email protected]