Расширение возможностей МП «Эльбрус» по обработке

реклама

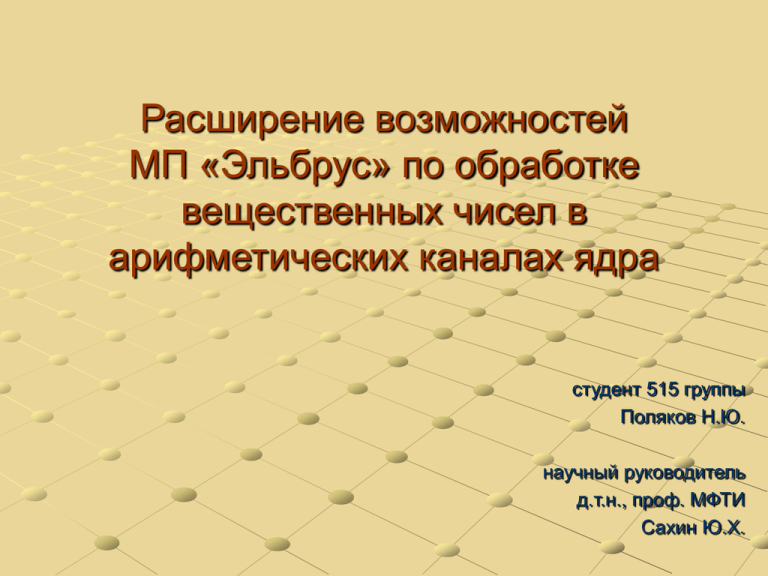

Расширение возможностей

МП «Эльбрус» по обработке

вещественных чисел в

арифметических каналах ядра

студент 515 группы

Поляков Н.Ю.

научный руководитель

д.т.н., проф. МФТИ

Сахин Ю.Х.

ОКР «Кубик-2»

ЗАО «МЦСТ» и ЗАО НТЦ «Модуль»

микропроцессор «Эльбрус-4С+»

4 универсальных ядра «Эльбрус»

4 ядра с архитектурой NeuroMatrix (DSP)

производительность МП - 250 Gflops

производительность 4 ядер «Эльбрус» - 90 Gflops

Производительность

существующего ядра «Эльбрус»

• каждый арифметико-логический канал (АЛК)

выполняет 4 операции за такт

• одно ядро содержит 6 АЛК, из которых 4

выполняют вещественные операции

• производительность МП с 4 ядрами «Эльбрус»

на частоте 1 ГГц:

4 ядра х 4 АЛК х 4 оп/такт х 1 ГГЦ = 64 Gflops

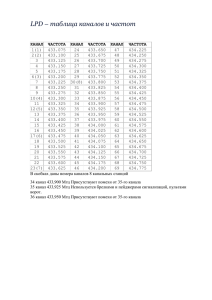

Оценка пропускной способности

каналов памяти

Процессор

Арх-ра

Кол-во ядер

Пропускная спос-ть

канала памяти,

Гбайт/с

Произв-ть МП на

64-битных

числах, Gflops

Отношение

пропускной

способности к

произв-сти,

байт/оп.

Intel Core i7-970

Nehalem

6

25.6

76.8

0,33

Intel Core i7-2600

Sandy

Bridge

4

21

54.4

0.39

AMD Thuban

K10

6

43

79

Godson-3A

Godson-3

4

25.6

8

Эльбрус-S

Эльбрус

1

8

4

Кубик

Эльбрус

2

12.8

8

Кубик-2

Эльбрус

4

51.2

48

0.54

3.2

2

1.6

1.07

Цель работы

Повышение производительности ядра

«Эльбрус» за счёт увеличения числа

арифметико-логических каналов,

обрабатывающих вещественные числа,

до 6

Структура ядра МП «ЭЛЬБРУС-S»

ALC

0

PLU

ALC

1

ALC

2

ALC

3

bypass A

CU

ALC

4

ALC

5

AAU

bypass B

PF

MMU

RF A

L1D$ A

L1D$ B

RF B

I$

Кластер А

data MX

Кластер В

L2$

APB

MAU

контроллер

системного

обмена

Арифметико-логические каналы

одного кластера(А)

CU

коды

операций

RF A

операнды

результаты

decode

операции

после

декодирования

байпас

целочисл.

АЛУ 0го

канала

целочисл.

АЛУ 1го

канала

целочисл.

АЛУ 2го

канала

результаты АЛУ

байпас

веществ.

АЛУ 0го

канала

веществ.

АЛУ 1го

канала

веществ.

АЛУ 2го

канала

целочисленный блок

результаты АЛУ

вещественный блок

Вещественный блок АЛК

кластер А

БАЙПАС

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

FPA

исполнительные

устройства

MMX

операнды и коды операций

FCM

FPA_sec

MUL

исполнительные

устройства

FPA

операнды и коды операций

0 канал

1 канал

2 канал

кластер В

БАЙПАС

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

операнды и коды операций

FPA

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

операнды и коды операций

3 канал

FPA

исполнительные

устройства

DIV

операнды и коды операций

4 канал

Функции байпаса:

• подготовка операндов для ИУ

• сбор, обработка и выдача результатов операций

5 канал

Содержание работы

доработка вещественных байпасов для

подготовки операндов

доработка механизма сбора результатов в

2 и 5 каналах

добавление в 2 и 5 каналы ИУ,

выполняющих наиболее часто

используемые операции:

FPA (сложение)

FPA_sec (трёхоперандные операции)

MUL (умножение)

верификация АЛК

Подготовка операндов

регистровый файл

(RF)

80

2 других канала

операнды из RF в формате 80

bps_fp

1 этап

2 этап

мультиплексирование

результатов FPU и

операндов из RF для

каждого формата

поотдельности

res_fp_pipe

очередь результатов на 7

позиций, преобразование

результата в формат 80 для

записи в RF и подачи на

шину, регистр W, хранящий

вышедший из очереди

результат

из FPU из RF и W из MMX

86

80

64

преобразование

форматов и конечное

мультиплексирование

выравни

вание

MMX и

FCM

FPA_sec

FPA

MUL

другие модули

АЛК

результаты

результаты

ИУ

ММХ

результаты

с регистра

W

rg_fp

результаты

для FPA_sec

модули байпасса

1 этап:

для каждого операнда из

каждого формата (64, 80, 86)

выбирается число, если оно

должно стать операндом,

или ноль в противном случае

2 этап

приведение формата чисел к

распакованному (86),

окончательное

мультиплексирование и

выдача операндов в ИУ

с учётом появления вещественных ИУ во 2 и 5 каналах

модули bps_fp и rg_fp для 0, 1, 3 и 4 каналов доработаны, а

для 2 и 5 каналов разработаны на их основе

Сбор результатов

регистровый файл

(RF)

80

2 других канала

операнды из RF в формате 80

bps_fp

res_fp_pipe

очередь результатов на 7

позиций, преобразование

результата в формат 80 для

записи в RF и подачи на

шину, регистр W, хранящий

вышедший из очереди

результат

из FPU из RF и W из MMX

86

80

64

rg_fp

преобразование

форматов и конечное

мультиплексирование

выравни

вание

MMX и

FCM

FPA_sec

FPA

MUL

другие модули

АЛК

результаты

результаты

ИУ

ММХ

результаты

с регистра

W

мультиплексирование

результатов FPU и

операндов из RF для

каждого формата

поотдельности

результаты

для FPA_sec

модули байпасса

1. результаты ИУ

принимаются в

очередь результатов

и складываются в

порядке поступления

операций в канал

2. результат выдаётся

из очереди в другие

каналы кластера и

записывается в RF

модули res_fp_pipe для 2 и 5 каналов разработаны на

основе модулей для других каналов

Сбор результатов

Очередь результатов

в RF

•

максимальная скорость

поступления операций в

канал – 1 оп./такт

•

максимальная скорость

выдачи результатов из

канала – 1 оп./такт

•

время исполнения

операций в ИУ одного

канал неодинаково

1 операция/такт

целочисленный

блок

очередь

результатов

2 такта

FCM

ММХ

MUL

FPA

2 такта

1-2 такта

4-6 тактов

4-5 тактов

FPA_sec

8-9 тактов

вещественные ИУ

из CU

1 операция/такт

Проблема:

выбрать минимальную длину очереди, при

которой не будет происходить потери

результатов

необходима очередь для сбора

результатов без обратной связи

Сбор результатов

Выбор длины очереди результатов. Упрощенная задача

Арифметико-логический канал

исполнительные устройства

aN

aN-1

1 оп/такт

ai

bN

bN-1

lN

lN-1

…

очередь

bi

li

…

a1

Упрощенная задача:

•

N исполнительных устройств

•

каждое имеет фиксированную длительность

выполнения операции li тактов

•

сводится к исходной, если заменить каждое

устройство исходной задачи на подустройства (1

подустройство на одну длительность) и

наложить ограничения на завершения операций

в подустройствах одного устройства

l1

b1

1 оп/такт

N входов

1 выход

Smax = lmax - lmin

за время ≥ max{ li+1 – li}

решение

исходной задачи

не больше Smax

Сбор результатов

Алгоритмы максимального заполнения очереди

Алгоритм 1

Алгоритм 2

lmin = 2, lmax = 7

время в

тактах

1

2

3

4

5

6

7

lmin = 2, lmid = 4, lmax = 7

8

9 10 11

7

1

2

3

4

5

6

7

8

9 10 11

7

7

7

7

7

7

4

7

4

2

4

2

4

2

4

2

2

2

количество

завершившихся

операций

2

2

2

2

2

2

S = 2*5 - 5 = 5

2

2

2

2

2

S = 2*5 - 5 = 5

Значит, минимальная длина очереди

для исходной задачи равна lmax - lmin

В итоге длина очередей для 0-4 каналов выбрана равной 7

для 5 канала выбрана равной 18

АЛК после доработки

кластер А

БАЙПАС

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

FPA

исполнительные

устройства

MMX

операнды и коды операций

FCM

FPA_sec

MUL

FPA

операнды и коды операций

0 канал

исполнительные

устройства

FPA_sec

MUL

FPA

операнды и коды операций

1 канал

2 канал

кластер В

БАЙПАС

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

операнды и коды операций

3 канал

FPA

исполнительные

устройства

MMX

FCM

FPA_sec

MUL

операнды и коды операций

4 канал

FPA

исполнительные

устройства

DIV

FPA_sec

MUL

FPA

операнды и коды операций

5 канал

Верификация

кластер А

АЛК

«Эльбрус-S»

АЛК 0

АЛК 1

кластер B

АЛК 3

кластер А

АЛК 4

АЛК 5

кластер B

новые

АЛК

АЛК 0

АЛК 1

АЛК 2

АЛК 3

АЛК 4

АЛК 5

0

Результаты

1. Разработано Verilog-описание доработанных

вещественных блоков АЛК, которые позволяют

повысить производительность ядер на

вещественных операциях на 50 %

•

производительность одного ядра равна

6(каналов) х 4(операции/такт) х 1 ГГц = 24 Gflops

•

производительность четырёхъядерного МП равна 96 Gflops

2. Произведена начальная верификация

разработанных модулей в составе СНК

«Эльбрус-S»

ai(t) равно 1, если операция поступает

в i-ое ИУ в момент времени t, 0 иначе.

bi(t) аналогично для результатов

li – длительность выполнения операции в устройстве

1,

если в момент t операция

поступает в i-ое устройство

0

иначе

1,

если в момент t i-ое устройство

выдаёт результат

0

иначе

ai(t) =

bi(t) =