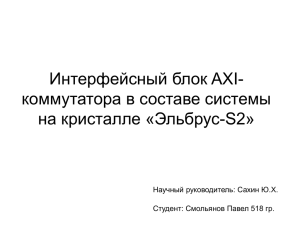

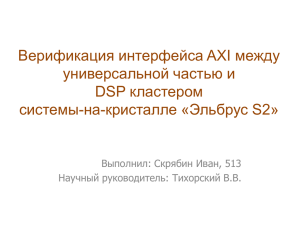

Разработка контроллера встроенного интерфейса AXI в составе системы на кристалле «Эльбрус-S2»

реклама

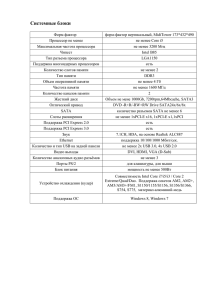

Разработка контроллера встроенного интерфейса AXI в составе системы на кристалле «Эльбрус-S2» Студент: Поляков Н.Ю. , ФРТК, 515 гр. Научный руководитель: д.т.н. Сахин Ю.Х. Система на кристалле «Эльбрус-S2» универсальные ядра ЭЛЬБРУС кристалл 0 (CPU 0) CPU Core 0 CPU Core 1 L2$ L2$ Межъядерный коммутатор (CIC) Контроллер системного обмена (SIC) Контроллер памяти 0 (MС0) Контроллер памяти 1 (MС1) к памяти Системный коммутатор (SC) Core 0 Core 2 Core 1 Core 3 DSP DMA DSP-кластер ГУП НПЦ «ЭЛВИС» интерфейсная часть Коммутатор данных (Data Box) Контроллер встроенных интерфейсов ввода-вывода (IOCOM) контроллер Контроллер канала ввода/ вывода Контроллер линков связи кристалл 1 (CPU 1) Контроллер линков связи кристалл 2 (CPU 2) Контроллер линков связи кристалл 3 (CPU 3) Контроллер ввода цифровой информации AXI-контроллер (AXI Box) универсальная часть ЗАО «МЦСТ» IO канал ADC канал 4-процессорная конфигурация системы на кристалле «Эльбрус-S2» Core 0 DSP 4 core DSP 4 core Core 0 Core 1 CPU 0 CPU 1 Core 1 Память SIC Память SIC IO IO Память SIC Память SIC Core 0 CPU 3 CPU 2 Core 0 Core 1 DSP 4 core DSP 4 core Core 1 Взаимодействие DSP c процессорными ядрами ЭЛЬБРУС (универсальной частью, УЧ) AXI-контроллер IO-Обмен (master) чтение запись AMBA 3.0 AXI 64 DMA-Обмен (slave) запись чтение 64 чтение запись IO-Обмен (slave) 64 64 запись чтение DMA-Обмен (master) DSP-кластер IO-обмен (Input/Output) : DSP-slave редкие короткие запросы DMA-обмен (Direct Memory Access) : DSP-master передача больших массивов данных Функциональное разделение AXI-контроллера AXI-контроллер Простейший интерфейс Универсальная часть МП контроллер (SIC IFace) непрерывная передача пакета 32 байта без маски 32 байта с маской 64 байта без маски интерфейсная часть (AXI IFace) AXI DSP произвольная длина пакета останов передачи после любой посылки Постановка задачи: Разработать AXI-контроллер для включения DSP в состав системы на кристалле «Эльбрус-S2» Требования: обеспечить минимальные задержки передачи данных DMA-обмена при максимальной загруженности канала обеспечить минимальное время выполнения коротких IO-обменов Структурная схема контроллера (SIC IFace) системный коммутатор (SC) коммутатор данных (Data Box) контроллеры межпроцессорных линков 64 64 32 X 3 мультиплексор данных из линков 64 DMA 32 X 3 + 64 IO модуль обработки IO запросов мультиплексор данных в CPU 64 SIC IFace 32 X 3 + 64 модуль DMA чтений (DMARD) модуль DMA записей (DMAWR) 64 64 модуль IO чтений (IORD) 64 AXI IFace модуль IO записей (IOWR) 64 Модуль выполнения DMA-записей (DMAWR) CPU0 CPU1 Контроллеры линков CPU2 CPU3 Номер запроса Коммутатор данных (Data Box) Этапы выполнения записи: • буферизация заявок от DSP • передача данных в коммутатор данных (Data Box) без буферизации • Преобразование управляющих сигналов отправка заявки на запись в контроллеры линков Достоинство: отсутствие буфера данных DMAWR Очередь запросов 40 Адрес Управляющие сигналы AXI IFace 64 Данные Модуль выполнения DMA-чтений (DMARD) Контроллеры линков 64 Запрос 32 32 32 № ответа Данные 40 в SC Запрос Буфер запросов на чтение Буфер данных 64 Этапы выполнения чтения: Коммутатор данных (Data Box) Запрос AXI IFace • буферизация запросов от DSP • формирование и отправка запросов на DMA-чтение в УЧ • сбор и буферизация когерентных ответов от кэшей • выдача ответов с данными в AXI IFace • отправка в УЧ сообщения о завершении DMA-чтения DMARD Очередь ответов о завершении Достоинство: Очередь ответов о завершении операции позволяет освободить ячейку буфера данных раньше, чем отправится сообщение Структурная схема контроллера (SIC IFace) системный коммутатор (SC) коммутатор данных (Data Box) контроллеры межпроцессорных линков 64 64 32 X 3 мультиплексор данных из линков модуль обработки IO запросов мультиплексор данных в CPU 64 32 X 3 + 64 IO 64 SIC IFace 32 X 3 + 64 модуль DMA чтений (DMARD) модуль DMA записей (DMAWR) 64 64 модуль IO чтений (IORD) 64 AXI IFace модуль IO записей (IOWR) 64 Модуль обработки IO-запросов (Input/Output Request’s Execution, IORE) Этапы обработки запроса: • • • прием запросов от SC во входную очередь запросов Системный коммутатор Сообщение «выдать данные» Очередь запросов на чтение чтение запись IORE Очередь запросов на запись Очередь ответов Коммутатор Данных Выдать ответ на чтение Счётчик ответов от DSP чтение запись Данные по записи 64 IORD IOWR 32 32 32 64 AXI IFace Контроллеры линков связи Достоинство: раздельные входные очереди для запросов на запись и чтение Сообщение «освободить регистр» чтение запись выдача запроса в исполнительные устройства и постановка в очередь ответов отправка команд исполняющим устройствам «выдать ответ» Запросы из SC Разделение входных очередей запись «выдать данные» чтение Входная очередь 0 1 1 Ожидание данных 4 - 16 Запись данных в AXI 0 Отправка запроса в AXI Входная очередь 1 Выходная очередь Ожидание данных 4-8 2 Выдача данных 4-8 чтение запись чтение Выдача данных Входная очередь Ожидание данных Выдача данных Выходная Ожидание данных очередь Выходная очередь ответ Ожидание данных конец 4 Выходная Ожидание данных очередь Выходная очередь Выдача данных ответ Раздельная входная очередь запись 4 Выдача данных 4-8 запрос Общая входная очередь 3 запрос конец 3 2 Выходная очередь 1 Выдача данных в DBox Выдача данных t Исполнительные устройства IO-обмена IO-чтение Коммутатор данных (Data Box) Выделить ячейку IORD Буфер данных 64 Коммутатор данных (Data Box) IORE Из входной очереди 64 IO-запись Выдать ответ Контроллеры линков 64 Из выходной очереди IORE Завершение записи 32 32 32 IOWR Текущий запрос Буфер данных Запрос на чтение 64 AXI IFace Данные AXI IFace Основная функция модулей – сбор и выдача данных 24 Адрес Оптимизация использования буфера данных 32 байта 64 байта 0 1 2 3 Запрос 0 Запрос 1 Запрос 2 Запрос 3 0 1 2 3 Запрос 0 Запрос 1 Запрос 3 Применяется в модулях IORD и IOWR Оптимизации Оптимизация форматного IO-чтения Запрос на 2 слова Запрос на 2 слова Буфер данных IORD AXI чтение 1 слова (1 такт) чтение 2 слов (2 такта) чтение 4 слов (4 такта) Применяется в модуле IORD Фактические характеристики Максимальная загруженность канала Одиночные запросы Результаты Разработано Verilog-описание контроллера встроенного интерфейса AXI, позволяющего минимизировать задержки передачи данных DMA-обмена при максимальной загруженности канала и обеспечивающего минимальное время выполнения коротких IO-обменов Пройдено автономное тестирование, позволившее проверить не только работу модуля AXI Box, но и правильность выполнения DSP-кластером обмена данными Модуль встроен в систему на кристалле “Эльбрус-S2”