Режим отладки Режим отладки СБИС

реклама

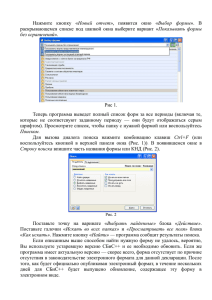

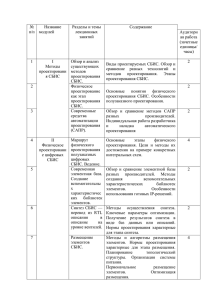

Универсальная система отладки СБИС по интерфейсу JTAG на основе скан-технологии Ладнушкин М.С. НИИ системных исследований РАН, Москва Москва 2014 Содержание • • • • • • • • • Введение Технологии встроенного тестирования Задачи Режим отбраковки Режим отладки Схема переключения синхросигналов Режим скан-через-JTAG Результаты сравнения архитектур отладки Заключение НИИСИ РАН 2 Введение • • • Поиск и отладка аппаратно-программных ошибок высокопроизводительных Системна-Кристалле является актуальной и дорогостоящей технологией, требующей специального инструментария для выполнения отладочных функций В высоконадежных системах задача эффективной отладки СнК приобретает особую актуальность Главная задача систем отладки - наблюдение внутреннего состояния СБИС в режиме работы НИИСИ РАН 3 Технологии встроенного тестирования • • • Скан-технология JTAG Технология встроенного логического анализа НИИСИ РАН 4 Задачи • • • • Разработка схемотехнического решения по использованию архитектуры отбраковки для целей тестирования и отладки проекта СБИС по интерфейсу JTAG Сохранение высокого тестового покрытия скан-архитектуры в режиме отбраковки Методика создания требуемой архитектуры Реализация методики в виде опции к рабочим сценариям синтеза RTL кода СБИС НИИСИ РАН 5 Режим отбраковки Выходы Входы Выходы Входы КП КП D D D D Q Q Q Q CLK ТП TCK 1 CLK TEST_MODE 0 TEST_SI D D D D Все триггеры СБИС Q Q Q Q TEST_SO ТП SCAN_EN Рабочий режим СБИС Режим отбраковки СБИС НИИСИ РАН 6 Режим отладки Выходы Входы КП Триггеры JTAG D D TCK CLK TEST_MODE Q Q TEST_SO D D D D СПС Q Q Q Q Остальные триггеры СБИС TEST_SI SCAN_EN Режим отладки СБИС НИИСИ РАН 7 Схема переключения синхросигналов Сигнал остановки и переключения синхросигналов Блок синхронизации (A) Логическое ядро СБИС CLK 0 CG TCK CK EN CLK_IN latch CLK D 1 Q CKOUT Сигнал готовности сдвига (B) • Схема переключения синхросигналов из рабочего режима в режим отладки по JTAG CLK TCK A B CKOUT CLK_IN НИИСИ РАН 8 Режим скан-через-JTAG Логическое ядро СБИС в режиме скан-через-JTAG КП TEST_SI • TEST_SO Структурная схема режима отладки скан-через-JTAG РУ РДС TDI bypass TDO ID REG Регистр инструкций TCK TMS TRST TAP НИИСИ РАН 9 Результаты сравнения архитектур отладки Характеристика Система сканчерез-JTAG Система Баэга EJTAG 110,40 110,38 110,92 Площадь тестовой логики, % 0,2 0,1 0,9 Возможность отладки «зависаний» СБИС да нет нет Возможность применения для любой СБИС Тестовое покрытие в режиме отбраковки, % да да нет 98,2 97,0 - да да да Площадь кристалла СБИС, мм2 Совместимость с JTAG НИИСИ РАН 10 Заключение • • • Разработана система отладки, осуществляющая «снимок» логического состояния всех узлов СБИС в момент работы и передачу информации по JTAG в тестирующее устройство Площадь тестовой логики составила 0,1% относительно исходного проекта, что в 9 раз меньше площади занимаемой EJTAG Система скан-через-JTAG была применена при разработке высокопроизводительного процессора, изготовленного по технологии КНИ с проектными нормами 0,25 мкм НИИСИ РАН 11