Логические основы устройства компьютера

реклама

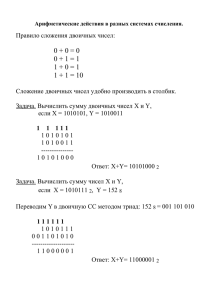

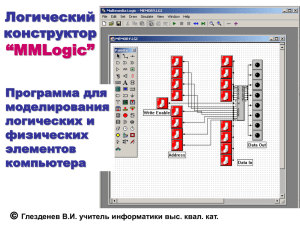

Логические основы устройства компьютера Угринович Н. Информатика и информационные технологии 10-11. п. 3.7. Логические основы устройства компьютера. – с.140. Базовые логические элементы Любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов («И», «ИЛИ», «НЕ») Логические элементы компьютера оперируют с сигналами, представляющими собой электрические импульсы. (Есть импульс – логический смысл сигнала – 1, нет импульса – 0.) Логический элемент Дискретный преобразователь, который после обработки входных двоичных сигналов выдает на выходе сигнал, являющийся значением одной из логических операций. Логический элемент «И» (конъюнктор) На входы А и В логического элемента подаются два сигнала (00, 01, 10 или 11). На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности операции логического умножения. А(0,0,1,1) В(0,1,0,1) И F(0,0,0,1) Логический элемент «ИЛИ» (дизъюнктор) На входы А и В логического элемента подаются два сигнала (00, 01, 10 или 11). На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности операции логического сложения. А(0,0,1,1) В(0,1,0,1) ИЛИ F(0,1,1,1) Логический элемент «НЕ» (инвертор) На вход А логического элемента подается сигнал 0 или 1. На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности инверсии. А(0,1) НЕ F(1,0) Сумматор двоичных чисел В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора являются сумматоры, которые обеспечивают такое сложение. Полусумматор Введем обозначения А,В – слагаемые Р – перенос S – сумма Таблица сложения одноразрядных двоичных чисел Слагаемые Перенос Сумма А 0 В 0 Р 0 S 0 0 1 1 1 0 1 0 0 1 1 1 0 Полусумматор Р=АΛВ Для определения суммы можно применить следующее логическое выражение: S=(AVB)Λ(AΛB) Задание. Построить таблицу истинности для данного логического выражения и убедиться в правильности нашего предположения. Схема сложения одноразрядных двоичных чисел А АΛВ И В АΛВ ИЛИ НЕ АΛВ И (АVВ)Λ(АΛВ) АVВ Данная схема называется полусумматором, т.к. реализует суммирование одноразрядных двоичных чисел без учета переноса их младшего разряда. Полный одноразрядный сумматор Должен иметь три входа: А,В – слагаемые и Р0 – перенос из младшего разряда и два выхода: сумму S и перенос Р. Логическое выражение для вычисления суммы в полном сумматоре принимает следующий вид: S=(A V B V P0) Λ P0 V (A Λ B Λ P0) Многоразрядный сумматор Состоит из полных одноразрядных сумматоров Триггер Важнейшая структурная единица оперативной памяти компьютера, а также внутренних регистров процессора. Это устройство, позволяющее запоминать, хранить и считывать информацию. Каждый триггер может хранить 1 бит информации. Схема триггера S(1) 1 0 R ИЛИ 1 НЕ 1 0 ИЛИ 0 НЕ Q