Приборы наноэлектроники

реклама

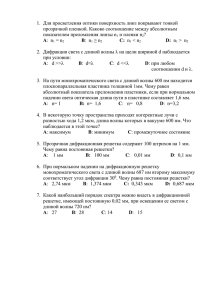

Mикроминиатюризация и приборы наноэлектроники История создания транзисторов • Биполярный транзистор 1947г. • МОП (МДП) транзистор 1960г. • Комплементарный МОП (КМОП) транзистор 1963г. МОП транзистор КМОП транзистор Технология производства комплементарных МОП транзисторов заключается в формировании n- и p- канальных транзисторов на одном кристалле КМОП транзистор Металлические межэлементные соединения Контакты Масштабирование МОП ИМС параметры Коэффициент масштабирования Длина канала L 1/αМ Ширина канала Z 1/αМ Толщина оксида dox 1/αМ Глубина p-n перехода hj 1/αМ Концентрация примеси Nпр Напряжение питания UDD αМ 1/αМ Масштабирование МОП ИМС параметры Электрическое поле в оксиде Eox Коэффициент масштабирования 1 Ширина ОПЗ Loj 1/αМ Емкость затвора Cox 1/αМ Задержка сигнала tзр 1/αМ Мощность постоянного тока Pстат 1/α2М Динамическая мощность Pдин 1/α2М Фактор качества F=Ptзр 1/α2М Площадь затвора Aзат 1/α2М Плотность тока J αМ Плотность мощности P/A 1 Сопротивление межсоединений r αМ Постоянная времени межсоединений rC 1 Падение напряжения на линии 1 Микроминиатюризация параметров МДП-приборов Параметр прибора n-МОП с обогащенной нагрузкой 1972 n-МОП с обедненной нагрузкой 1976 Высококачественный МОП 1979 МОП Коэффициент изменения 1980 Длина канала L, мкм 6 6 3,5 2 1/αМ Поперечная диффузия LD, мкм 1,4 1,4 0,6 0,4 1/αМ Глубина p-n переходов x, мкм 2,0 2,0 0,8 0,8 1/αМ Толщина затворного окисла dox, мкм 0,12 0,12 0,07 0,04 1/αМ Напряжение питания Vпит, В 4-15 4-8 3-7 2-4 1/αМ Минимальная задержка вентиля 12-15 τ, нс 4 1 0,5 1/αМ Мощность на вентиль P, мВт 1,5 1 1 0,4 1/α2М Произведение быстродействия на мощность, пДж 18 4 1 0,2 1/α3М Сравнение важнейших эксплуатационных показателей МОП ИС Размеры транзистора 10 1 Длина канала, мкм 0,1 0,01 1970 1980 1990 2000 год 2010 2020 Уменьшение длины канала Год Тех.процесс Длина затвора 1993 0,50 0,50 1995 0,35 0,35 1997 0,25 0,20 1999 0,18 0,13 2001 0,13 0,07 2003 0,10 0,05 2005 0,07 0,03 Минимальную длину канала ограничивает эффект, связанный со смыканием областей истока и стока при приложении напряжения к стоку VDS. Поскольку ширина lоб p-n-перехода, смещенного в обратном направлении, равна то минимальная длина канала должна быть больше удвоенной ширины p-n-перехода Lmin > 2lоб и быть прямо пропорциональна корню квадратному от напряжения питания и обратно пропорциональна корню квадратному от уровня легирования подложки. Уменьшение толщины подзатворного диэлектрика Важным параметром, ограничивающим уменьшение размеров подзатворного диэлектрика, является величина туннельного тока из затвора в канал транзистора Зависимость плотности тока через затвор от величины напряжения на затворе для различных толщин диэлектрика Миниатюризация процессоров Intel Модель Год Кол-во тр-ров Тех.процесс Тактовая частота 4004 1971 2 250 10 мкм 108 kHz 8008 1972 2 500 10 мкм 200 kHz 8080 1974 5 000 6 мкм 2 MHz 8086 1978 29 000 3 мкм 5-10 MHz 286 1982 120 000 1,5 мкм 6-12,5 MHz 386 1985 275 000 1,5-1 мкм 16-33 MHz 486DX 1989 1 180 000 1-0,6 мкм 25-100 MHz Pentium 1993 3 100 000 0,8-0,35 мкм 60-200 MHz Pentium II 1997 7 500 000 0,35-0,25 мкм 233-450 MHz Pentium III 1999 24 000 000 0,25-0,13 мкм 450-1300 MHz Pentium 4 2000 42 000 000 0,18-0,13 мкм >1400 MHz Миниатюризация процессоров Intel Физические ограничения микроминиатюризации Параметр Физическое ограничение Минимальная величина одного элемента, 0,03 нм Статистические флуктуации легирования подложки, разрешение фоторезиста, космические лучи и радиоактивность, конечная ширина p-n перехода Толщина подзатворного диэлектрика, 2,3 нм Туннельные токи через диэлектрик Минимальное напряжение питания 0,025 В Тепловой потенциал kT/q Минимальная плотность тока, 10-6 А/см2 Дискретность заряда электрона, флуктуации встроенного заряда Минимальная мощность, 10-12 Вт/элемент при f=1 кГц Шумы, тепловая энергия, диэлектрическая постоянная Предельное быстродействие, 0,03 нс Скорость света Физические ограничения микроминиатюризации Параметр Физическое ограничение Максимальное напряжение питания Пробой подзатворного диэлектрика, смыкания областей истока и стока Максимальное легирование подложки Туннельный пробой p-n перехода стока Максимальная плотность тока Электромиграция, падения напряжения на паразитных сопротивлениях контактов Максимальная мощность Теплопроводность подложки и компонентов схемы Количество элементов на кристалл, 109 Совокупность всех ранее перечисленных ограничений Транзисторы, созданные в лабораториях Intel Длина канала 30 нм Декабрь 2000 20 нм Июнь 2001 15 нм Декабрь 2001 Возможные направления для дальнейшей миниатюризации и повышения быстродействия • Уменьшение толщины подзатворного диэлектрика • Наращивание областей истока/стока • Технология «Кремний-на-изоляторе» (SOI) • Транзистор с SiGe-каналом Наращивание областей истока/стока уменьшается вероятность пробоя подзатворного диэлектрика Технология «Кремний-на-изоляторе» (SOI) Создание дополнительного слоя SiO2 сокращает паразитные емкости, а следовательно, позволяет добиться более высокой скорости переключения транзистора МОП транзистор с SiGe каналом Применение SiGe канала увеличивает скоростные характеристики транзистора за счет более высокой подвижности дырок. Однако преимущество уменьшается при сокращении длины канала. Важнейший процесс в микро- и наноэлектронных производствах – литография Виды нанолитографий : 1) Оптическая нанолитография 2) Электронная нанолитография 3) Наноимпринт 4) Применение приемов самосовмещения при использовании оптической литографии (например, i-линия) Оптическая нанолитография Длина волны, нм Достижимое разрешение, нм Преимущества Недостатки 193,4 (ArF) 90-70 Высокая производительность - 157 (F2) 13,4 65-50 30-10(?) Оптика должна строиться на GaF2, что увеличивает стоимость процесса литографии Пока нет источника излучения с нужными параметрами для промышленного применения Альтернативные методы нанолитографии Метод Достигнутое разрешение нм Примечание Электронная нанолитография 30-7 Энергия электронов 100-200 кэВ в пучке диаметром 1-10 нм. Низкая производительность Наноимпринт 10-6 Совмещение нескольких штампов проблематично 40-35 Только для наиболее критичных элементов топологии Применение приемов совмещения при использовании оптической литографии ( например, i-линия ) Гибридная интегральная микросхема Схема формирования суб-100 нм щели а - литография по фоторезисту, б - контролируемый подтрав металлической пленки под резист, в - нанесение металлической пленки, г - удаление фоторезиста методом "взрыва", д - фотография структуры на стадии (в)