Архитектура P6

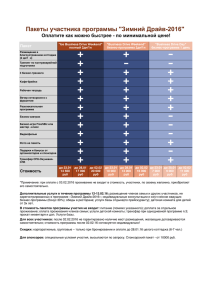

advertisement

Архитектура P6 Архитектура P6 Начало разработки: 1990 год Цель: Достигнуть производительности большей, чем процессоры архитектуры P5 и процессоры конкурентов. Процессоры • Pentium Pro (1995) до 200 МГц • Pentium II (1997) до 450 МГц • Pentium III (1999) до 1.3 ГГц • Pentium M (2003) до 2.26 ГГц Архитектура P6 Начало разработки: 1990 год Цель: Достигнуть производительности большей, чем процессоры архитектуры P5 и процессоры конкурентов. Процессоры • Pentium Pro (1995) до 200 МГц • Pentium II (1997) до 450 МГц • Pentium III (1999) до 1.3 ГГц • Pentium M (2003) до 2.26 ГГц Архитектура P6 Отличительные особенности ядра • 12-стадийный суперконвейер • Внешний интерфейс CISC, внутреннее ядро RISC • Двойная независимая шина • Динамическое исполнение команд – – – – – Предсказание ветвлений Переименование регистров Спекулятивное исполнение Исполнение вне порядка Суперскалярное исполнение Возможно исполнение до 3-х команд за такт. Упрощенная структура конвейера P6 • Входной блок упорядоченной обработки команд (In-order front end) • Исполнительное ядро с изменением порядка исполнения (Out-of-order execution core) • Блок упорядоченного завершения команд (Inorder retirement) Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Определение адреса следующей команды (на основании BTB). Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Чтение 2 кэш-строк, выборка пакета 16B, выравнивание пакета. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Декодирование: преобразование команд в uOPs. Обработка максимум 3-х команд x86 (6 uOPs: 4-1-1) за такт. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Декодирование: преобразование команд в uOPs. Максимум 1 команда перехода за такт. Информация о ветвлениях отправляется в BTB. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF На входе очереди максимум 6 uOPs за такт (4-1-1). На выходе очереди максимум 3 uOPs за такт. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Создается запись в Reorder Buffer. Отображение программных регистров на физические. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Чтение операндов для uOP. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Когда операнды готовы, uOP помещается в станцию резервации (RS) и ждет исполнения. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF В произвольном порядке uOP-ы запускаются на исполнение на различных исполнительных устройствах. Максимум 5 результатов за такт. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Операции чтения данных из памяти. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Операции записи данных в память. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Запись результатов в Reorder Buffer. Структура ядра P6 Стадии конвейера: 1. BTB0 2. BTB1 3. IFU0 4. IFU1 5. IFU2 6. ID0 7. ID1 8. RAT 9. ROB read 10. RS 11. Ex 12. ROB write 13. RRF Завершение. Запись результатов в выводящий регистровый файл (RRF). Удаление uOPs из ROB. Запись данных в память. Максимум 3 uOPs за такт. Блок неупорядоченного исполнения P6 Архитектура P7 NetBurst Архитектура NetBurst Цель: Достигнуть большой производительности за счет повышения тактовой частоты. Средства: • Большой конвейер с маленькими стадиями – Уменьшение задержек на ветвления – кэш трасс, большой BTB – Уменьшение задержек на обращение к памяти – быстрый кэш • Уменьшение команд, необходимых для выполнения задачи – Векторное расширение SSE2 Процессоры • Pentium 4 – Willamette – Northwood – Prescott до 2.4 ГГц до 3.2 ГГц до 3.х ГГц Архитектура NetBurst Отличительные особенности ядра • 20 или 31-стадийный гиперконвейер • Внешний интерфейс CISC, внутреннее ядро RISC • Динамическое исполнение команд – – – – – Предсказание ветвлений Переименование регистров Спекулятивное исполнение Исполнение вне порядка Суперскалярное исполнение • Кэш трасс (работает на половине частоты) • Небольшая кэш-память с быстрым доступом • Часть ядра работает на удвоенной частоте Возможно исполнение до 3-х команд за такт. Структура ядра архитектуры NetBurst Кэш трасс • Состоит из 2048 блоков по 6 ячеек (256 наборов по 8 блоков) • Все блоке в каждой трассе связаны в двунаправленный список • Темп чтения – 1 блок за 2 такта Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Определение адреса следующей uOP в кэше трасс. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Выборка из кэша трасс в очередь предвыборки до 6 uOPs за 2 такта, подстановка MROM векторов. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Продвижение… Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Выборка 3 uOPs из очереди. Выделение ресурсов процессора (места в очередях, буфере переупорядочивания, регистровом файле). Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Отображение логических регистров на физические. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Размещение uOP-ов в 2-х очередях uopQ: для операций с памятью и для остальных операций. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive 5 планировщиков в зависимости от типа операции выбирают uOPы из очередей uopQ каждый в свою очередь schQ (аналог RS). Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Распределение uOPs из 5-ти очередей schQ по 4-м портам исполнительных устройств в произвольном порядке. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Чтение операндов из регистрового файла. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Исполнение Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Установка флагов. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Проверка правильности предсказания переходов. Стадии конвейера P7 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. TC next IP 1 TC next IP 2 TC Fetch 1 TC Fetch 2 Drive Allocator Rename 1 Rename 2 Queue Schedule 1 Schedule 2 Schedule 3 Dispatch 1 Dispatch 2 Register file 1 Register file 2 Execute Flags Branch check Drive Перенос результата проверки перехода в декодер. Стадии конвейера P7 1. TC next IP 1 2. TC next IP 2 3. TC Fetch 1 4. TC Fetch 2 5. Drive 6. Allocator 7. Rename 1 8. Rename 2 9. Queue 10. Schedule 1 11. Schedule 2 12. Schedule 3 13. Dispatch 1 14. Dispatch 2 15. Register file 1 16. Register file 2 17. Execute 18. Flags 19. Branch check 20. Drive Далее uOP ждет отставки для освобождения ресурсов и записи результатов. Отставка происходит последовательно над теми же тройками uOPs, которые были сформированы на стадии Allocator. Конвейер NetBurst Исполнение в порядке поступления команд Исполнение вне порядка Исполнительные устройства Rapid Execution Engine • Работает на удвоенной частоте ядра • Включает: – 2 планировщика быстрых целочисленных операций – Целочисленный регистровый файл – Порты запуска 0 и 1 – Быстрые АЛУ. NetBurst Replay NetBurst Replay Изменения в ядре Prescott • • • • • • Длина конвейера увеличилась до 31 стадии Увеличился объем и латентность кэш-памяти Добавилось расширение SSE3 Улучшенная предвыборка данных Улучшенное предсказание ветвлений Дополнительные буферы комбинированной отложенной записи в память • Ускорение некоторых операций с целыми числами (умножение, …) Архитектура Core Архитектура Core Разработана на основе P6. Цель: увеличить производительность, снизить энергопотребление и тепловыделение. Процессорные ядра: • Merom, Conroe, Woodcrest • Kentsfield, Clovertown • … Пока до 2.93 ГГц Архитектура Core Реализованы новые технологии: • Intel Wide Dynamic Execution – выполнение до четырех инструкций за такт • Intel Intelligent Power Capability – снижается энергопотребление системы • Intel Advanced Smart Cache – общая для всех ядер кэш-память L2 • Intel Smart Memory Access – оптимизирует использование пропускной способности подсистемы памяти • Intel Advanced Digital Media Boost – позволяет обрабатывать все 128-разрядные команды SSE, SSE2, SSE3, … за один такт Intel Wide Dynamic Execution Разрешение конфликтов (между операциями чтения и записи) по адресам обращения к памяти.