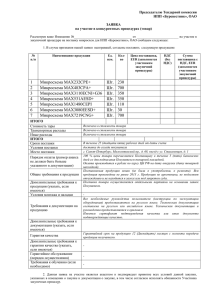

Логические схемы АЛУ К155ИП3

реклама

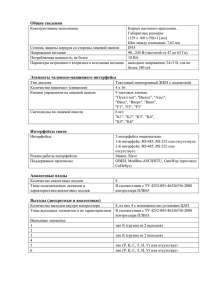

Арифметико-логическое устройство Микросхема К155ИП3 Схема К155ИП3 представляет собой скоростное четырехразрядное АЛУ. Может работать в двух режимах, выполняя 16 логических либо 16 арифметических операций. Для получения максимального быстродействия при арифметической обработке в модуле имеется внутренняя схема ускорения переносов. Микросхема выполнена в корпусе на 24 вывода. <A3,…,A0>,<B3,…,B0> - входы операндов A, B; С0 - инверсный вход переноса в младший разряд; <S3,…,S0> - сигналы настройки на выполнение той или иной функции данного типа; M (mode control) – сигнал настройки на арифметический (M=0) или логический (M=1) тип функции; <F3,…,F0> - выходы результата; С4– инверсный выход переноса из старшего разряда; G и P – инверсный выход генерации и распространения переноса. Служат для подключения микросхемы ускорения переносов. K – выход компаратора с открытым коллектором. Таблица настройки АЛУ Схема ускорения переносов Микросхема К155ИП4 Схема ускорения переносов на 4 корпуса АЛУ К155ИП3. Одновременно формирует переносы на входах всех тетрад 16разрядного сумматора, начиная со второй. Выход переноса отдельного корпуса АЛУ: Все функции переноса формируются 2-уровневыми схемами (т.е. параллельно) с задержкой 13 нс относительно поступления сигналов Gi , Pi. Эти сигналы генерируются всеми тетрадами одновременно, так как зависят только от значений битов слагаемых (но не от Сп). Формирование сигналов P и G происходит с задержкой 12 нс относительно момента поступления слагаемых. Две других задержки в АЛУ: tF=24 нс, = 12 нс. При этом, если к моменту поступления сигнала формирование сигналов P и G завершено, то tF уменьшается до 12 нс. Дешифраторы Дешифратор – комбинационная схема на М входов и 2М выходов (нумеруемых в натуральном порядке), такая , что в любой момент времени в активном состоянии (0 или 1) находится только один выход. Номер которого определен входным кодом. В состав различных серий ТТЛ входит 7 типов микросхем дешифраторов. Они различаются по числу дешифраторов в корпусе, по числу адресных входов в каждом, по формату адресного кода (двоичный или двоично-десятичный). Большинство дешифраторов способны выполнять функцию демультиплексора. В таком случае демультиплексивная функция выполняется при использовании тех же входов и выходов. Передаваемые данные поступают на один из входов разрешения. Микросхема К155 ИД3 Эта схема осуществляет дешифрацию кода, поданного на вход A3A2A1A0, с выдачей сигнала низким потенциалом на одном из 16 выходов, когда на обоих входах управления E0 и E1 низкий потенциал. Особенности микросхемы: 1) Инверсные выходы (активный 0). Такая выходов в практике применения микросхемами других типов предпочтительной. 2) Наличие двух инверсных выходов (разрешения) Е0 и Е1. организация с другими оказывается управления Активизация DC может произойти только при подаче на оба входа управления низкого потенциала. Эти входы также могут быть использованы для наращивания разрядности адреса, стробирования адресных входов и для трансформации DC в демультиплексор. Типовое среднее время задержки распространения 23 нс через три логических уровня, 16 нс – через входы управления. Средняя мощность рассеивания – 170 мВт. Возможности функционирования микросхемы К155ИД3 Работа схемы в режиме демультиплексора Наращивание разрядности A4 A3 A2 A1 A0 Акт. выход 0 1 0 1 1 DC1. 11 1 0 0 1 0 DC2. 2 Микросхемы контроля Наиболее распространенным способом контроля правильности высокоскоростных передач информации по линиям связи является проверка сохранения четности (нечетности) числа единиц передаваемого кода. Такая проверка называется контролем паритета. Она позволяет обнаружить одиночные ошибки. Микросхема К155ИП2 ИП2 – схема контроля четности и нечетности на 8 бит. Эта схема предназначена для выработки контрольного разряда дополнения до четности и нечетности восемь бит. Микросхема имеет два входа управления: четный EE (even enable) и нечетный OE (odd enable). Для целей проверки используется парафазная комбинация сигналов на этих выходах. Если сумма единиц проверяемого кода четно, то комбинация сигналов на выходах совпадает со входной. В нечетном варианте – наоборот. Средняя мощность рассеивания 170 мВт. Ток питания: номинальный 34, максимальный 56 мА. Номинальное время задержки распространения – 46 нс. Таблица сигналов функционирования схемы Входы Сумма высоких уровней на I0…I7 четная нечетная четная нечетная - Выходы EE E0 1 1 0 0 1 0 0 0 1 1 1 0 ΣE (четная) 1 0 0 1 0 1 Логическая схема модуля К155ИП2 Σ0 (нечетная) 0 1 1 0 0 1 Микросхемы мультиплексоров Мультиплексор – коммутатор входных каналов. Это комбинационная схема на М входов и 1 выход. М = m + 2m , где m - разрядность адреса, 2m – число входных коммутируемых каналов. Код адреса определяет номер информационного канала, который должен быть подключен к выходу. Всего в составе серий ТТЛ имеется более 11 типов микросхем MS. Они различаются по числу входных каналов, наличием парафазного выхода, специальных входов разрешения. Некоторые имеют три состояния для организации работы на общую шину. Микросхема К155КП2 Позволяет мультиплексировать с двух четырехразрядных каналов (I0a, I1a, I2a, I3a; I0c, I1c, I2c, I3c) в один двухразрядный канал (Ya, Yc). 1) Общие входы A1, A0 служат для указания адреса входного канала; 2) Ea, Ec – инверсные входы разрешения. При отсутствии разрешения выход пассивен (0); Если на входы A1, A0 последовательно подавать сигналы "00", "01", "10", "11", то на выходе будет последовательно появляться информация с 0-го по 3-ий входной канал. Таким образом, можно осуществить преобразование параллельного кода в последовательный. Типовое среднее время задержки распространения: передача данных – 17 нс, передача импульса выборки – 22 нс. Типовая мощность рассеивания – 180 мВт. Логические схемы АЛУ К155ИП3 (слева) и дешифратора К155ИД3 (справа) Регистр - это линейка из ряда триггеров, используемая для последовательного накопления, промежуточного хранения и сдвига данных. К155ИР9 Счетчики - это делители частоты. Если коэффициент деления равен 2n, то такие счетчики называют двоичными. Если деление осуществляется по основанию 10, то получаем десятичный счетчик. Это программируемый счетчик с входами для переключения коэффициента, на который можно разделить тактовую частоту. Выходную частоту можно рассчитать по уравнению: Fвых = (f/64) (Е5•25+ Е4•24 + Е3•23 + E2•22 + Е1•21 + E0•20). Здесь Е0-Е5 - данные на входах разрешения, значение каждого коэффициента Е может быть 1 или 0. EI - сигнал разрешения по входу. Остановить деление можно, подав на вход S напряжение высокого уровня. Активные напряжения низкого уровня, данные по входам EI и S, разрешают счет. Общий сброс с остановкой деления осуществляется высоким уровнем по входу R.

![[Kozvonina E.G.] Sbornik zadach. Osnovue cifrovoi (z-lib.org)](http://s1.studylib.ru/store/data/006389265_1-e143d69805fe8b70abed884d8b21d828-300x300.png)