Разработка контроллера последовательного канала с логическим протоколом NRZI-SPACE

реклама

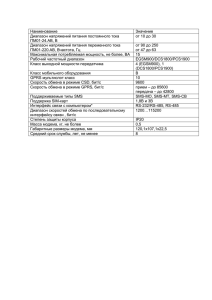

Разработка контроллера последовательного канала с логическим протоколом NRZI-SPACE для ВК “Эльбрус – 90 микро”. Студент 212 группы Самойлов Артем Александрович Проблема Существуют системы, объединяющие различные гидроакустические средства на основе принципов комплексирования и позволяющие наиболее полно и одновременно решать ряд задач в области гидроакустики, возникающих при эксплуатации морских средств – гидроакустические комплексы. Для связи различных станций с вычислительным комплексом понадобился контроллер последовательного канала, передающий данные по определенному протоколу. Цель работы: Разработать модуль синхронизатора и контроллера последовательных каналов обмена (МСПК) для обмена данными между управляющим вычислительным комплексом и абонентами гидроакустических комплексов (8шт.). Постановка задачи • 8 полнодуплексных каналов • электрический интерфейс соответствует стандарту RS-485 • шина SBus для обмена данными с вычислительным комплексом • скорость передачи информации – 2, 4 ,8 Мбит/c • количество абонентов на линии – 1 (точка-точка) • длина линии передачи при скорости 2, 4 Мбит/с не должна превышать 15 м и при скорости 8 Мбит/с - 10 м • передаваемые пакеты должны быть привязаны к импульсам синхронизации F2222 •данные кодируются по методу NRZI-Space • очередность передаваемых бит – младший вперед • проверка данных контрольной суммой CRC-CCITT • передача высокого логического уровня в состоянии покоя Параметры передачи данных NRZI-Space Формат кадра: n < 128, bit staffing (после 5 подряд идущих 1 вставляется 0), аварийное завершение (от 7 до 14 единиц), состояние покоя (>14 единиц), подсчет контрольной суммы с полиномом X16 + X12 + X5 + 1 Помехозащитное кодирование Содержимое регистра сдвигается влево на 1 бит, и в последнюю (нулевую) позицию заносится очередной, еще не обработанный бит данных Если из регистра был выдвинут бит со значением «1», то содержимое регистра комбинируется по XOR с полиномом. Если «0», XOR не выполняется Предыдущие два пункта выполняются, пока не закончатся данные Физический интерфейс линии связи Выполнен согласно стандарту EIA/TIA-485 Сигнал Направление Логические уровни RXC <- RS-485 RX <- RS-485 TXC -> RS-485 TX -> RS-485 F2222 -> LVDS Описание Входной тактовый импульс приема Линия приема данных Выходной тактовый импульс передачи Линия передачи данных Доп. Синхросигнал Fr0 -> LVDS Доп. Синхросигнал Fncp -> LVDS Доп. синхросигнал Структурная схема Функционирование модуля Запрос от драйвера на запись в контроллер SBus. Далее – в модуль на коммутатор адреса. В модуле запрос передается в блок управления, либо в один из 8-ми каналов и далее в управляющие регистры приемапередачи. Выдача в линию синхросигналов F2222 и TXC. При включении канала, когда схема приоритетов разрешает обмен данными, начинается подкачка данных в управляющий буфер и буфер передач и приема. В следующем такте F2222 происходит отсылка пакета и подкачка управляющего буфера и буфера передачи. Аналогично и для приемника. Диаграмма работы драйвера с одним каналом Основной режим работы Рабочий цикл: Ожидание прерывания Чтение регистра управления для получения флагов прерывания и обновления номера такта N В память пишутся (N+K) – (N+K+K-1) очередных буферов управления и данных Из памяти читаются (N) – (N+K-1) буферов управления и приема данных Производится анализ и разбор полученных данных Требуемые параметры Количество памяти – 132.608 бит : Один канал – 518x32 р. слов 1-8 каналы: всего 4352x32 р. слов или 139.264 бит или 17кб памяти Количество выводов ПЛИС – 128 шт = 7*8+71+1 : Выводов на 1 канал – 7 шт, контроллер SBUS ~ 71 шт. + 1 – внешняя частота 48 МГц. Примерное число логических элементов – 10000 шт.: 1500 шт. – SBUS-контроллер ~500 шт. – диспетчер приоритетов + генератор тактовых импульсов 8*1000 шт. = 8000 шт. – кол-во элементов с 8 каналов В результате был выбран Cyclone II EP2C35 кол-ва элементов - 33.216; кол-во памяти - 483.840; кол-во выводов(раб./всего) - 322 / 484 Верификация Verilog модели проверка корректной отработки управляющего буфера без признака данных (пустой пакет данных) тест пересылки больших массивов данных в разных режимах и скоростях по всем восьми каналам тест приема/посылки данных в канал на разных скоростях тест чтения ПЗУ ячейки, Registers R&W test - тест записи/чтения всех регистров ячейки определение максимального размера пакета данных, вмещающегося на данной скорости между двумя тактами сигнала F2222 тест останова отдельных каналов с последующим включением и возобновлением работы тест правильности генерирования синхросигналов F2222, FPNP, FNCP, FR0 проверка тестового режима обмена (в данном режиме возможно прямое чтение/запись буферов управления и данных каналов). Тестовый режим: Прямая запись и чтение буферов управления и информации канала Подкачка и откачка буферов в ручном режиме Снижение частоты выдачи синхроимпульса F2222 в восемь раз Заключение Разработана синтезируемая верилог модель. Произведена верификация модели. Добавлен тестовый режим для отладки готового модуля. Модуль находится в стадии изготовления. Спасибо за внимание