Микропроцессорные системы

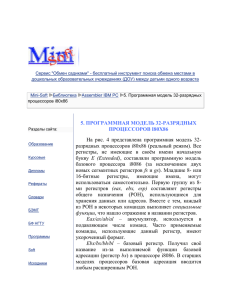

реклама

Микропроцессорные системы Лектор: М.А. Сонькин Лекционных часов: 32 Форма отчетности: экзамен Контроллер гибких дисков Шины: управляющая , адресная , данных Сканер Параллельные порты Принтер Последовательные порты Плоттер Порты ввода/ вывода Модем Дополнительные устройства Схемы Внутреннего управления Мышь Кэш-память Клавиатура Регистры Видеоадаптер Накопитель на гибких магнитных дисках Контроллер накопителя на жёстких магнитных дисках Динамик АЛУ Внутренняя память Схемы управления шиной Микропроцессор Накопитель на жёстких магнитных дисках Дополнительные слоты расширения Rom Ram Монитор Блок питания Структурная схема микропроцессорной системы Игровой порт Джойстик Микропроцессор — это тот узел, блок, который производит всю обработку информации внутри микропроцессорной системы. Остальные узлы выполняют всего лишь вспомогательные функции: хранение информации (в том числе и управляющей информации, то есть программы), связи с внешними устройствами, связи с пользователем и т.д. Процессор заменяет практически всю «жесткую логику», которая понадобилась бы в случае традиционной цифровой системы. Он выполняет арифметические функции (сложение, умножение и т.д.), логические функции (сдвиг, сравнение, маскирование кодов и т.д.), временное хранение кодов (во внутренних регистрах), пересылку кодов между узлами микропроцессорной системы и многое другое. Количество таких элементарных операций, выполняемых процессором, может достигать нескольких сотен. Процессор можно сравнить с мозгом системы. Современные процессоры выполняются в виде микропроцессоров. Физически микропроцессор представляет собой интегральную схему — тонкую пластинку кристаллического кремния прямоугольной формы площадью всего несколько квадратных миллиметров, на которой размещены схемы, реализующие все функции процессора. Кристалл-пластинка обычно помещается в пластмассовый или керамический плоский корпус и соединяется золотыми проводками с металлическими штырьками, чтобы его можно было присоединить к системной плате компьютера. Схема вычитателя числа A из числа B: Схема вычитателя числа B из числа A: Структурная схема арифметического устройства: Арифметико-логическое устройство - часть процессора, выполняющая операции над данными (машинные команды). В приведённой на рисунке 3 схеме используются четырёхвходовые коммутаторы, для управления каждым из которых достаточно двух бит. То есть для управления всей схемы в целом достаточно четырёх проводов управления. Попытаемся построить таблицу операций, которые будет выполнять эта схема. На результат операции будет влиять вход переноса сумматора PI, поэтому этот провод тоже включим в состав кода, управляющего схемой. Регистры процессора Регистры процессора Процессоры имеют регистры, подразделяющиеся на следующие категории: -регистры общего назначения; -указатель инструкций и регистр флагов; -регистры сегментов; -управляющие регистры; -системные адресные регистры; -регистры отладки; -регистры тестирования. РЕГИСТРЫ ОБЩЕГО НАЗНАЧЕНИЯ. Общие регистры данных и адресов Указатель инструкций и регистр флагов Регистры селекторов сегментов 31 0 16 15 0 15 0 31 AH AX AL EAX CS Код IP BH BX BL EBX SS Стек FLAGS CH CX CL ECX DS DH DX DL EDX ES SI ESI FS DI EDI GS BP EBP SP ESP Данные 16 15 EIP EFLAGS РЕГИСТРЫ ФЛАГОВ Назначение бит регистра EFLAGS: ID (Id Flag) - флаг доступности команды идентификации CPUID (Pentium+ и некоторые 486-е). VIP (Virtual Interrupt Pending) - виртуальный запрос прерывания (Pentium+). VIF (Virtual Interrupt Flag) - виртуальная версия флага IF (разрешения прерывания) для многозадачных систем (Pentium+). AC (Alignment Check) - флаг контроля выравнивания. При исполнении программ на уровне привилегий 3 в случае обращения к операнду, не выровненному по соответствующей границе (2, 4, 8 байт), и при установленном флаге АС произойдет исключение-отказ 17 с нулевым кодом ошибки. На уровнях привилегий О, 1, 2 контроль выравнивания не производится (486+). VM (Virtual 8086 Mode) - в защищенном режиме включает режим виртуального 8086. Попытка использования привилегированных инструкций в этом режиме вызовет исключение 13. Бит может устанавливаться только в защищенном режиме: инструкцией IRET на нулевом уровне привилегий или переключением задач на любом уровне привилегий. На бит не действуют инструкции POPF, a PUSHF в образ этого бита всегда заносит 0. Его единичное значение может сохраниться только в образе EFLAGS, сохраняемом при прерывании или переключении задач. RF (Resume Flag) - флаг возобновления, используется совместно с регистрами точек отладочного останова. IOPL (Input/output Privilege Level) - уровень привилегий ввода-вывода. NT (Nested Task Flag) - флаг вложенной задачи. OF (Overflow Flag) - флаг переполнения. Устанавливается, если результат арифметической операции не умещается в операнде назначения. DF (Direction Flag) - флаг управления направлением в строковых операциях. При единичном значении индексные регистры, участвующие в строковых операциях, автоматически декрементируются на количество байт операнда, при нулевом - инкрементируются. IF (Interrupt-enable Flag) - (флаг управления прерываниями. При единичном значении разрешается выполнение маскируемых аппаратных прерываний. TF (Trap Flag) - флаг трассировки (пошагового режима). При его установке после выполнения каждой команды вызывается внутреннее прерывание типа 1 (INT 1). SF (Sign Flag) - флаг знака. Указывает на единичное значение старшего бита результата признак отрицательного числа. ZF (Zero Flag) - флаг нулевого результата, AF (Auxiliary Flag) - флаг дополнительного переноса (займа) в тетраде для десятичной арифметики. PF (Parity Flag) - флаг паритета, устанавливается при четном числе единиц в результате. CF (Carry Flag) - флаг переноса (заема) старшего бита в арифметических операциях. РЕГИСТРЫ СЕГМЕНТОВ Содержат 16-битные указатели (в реальном режиме) или дескрипторы (в защищенном режиме) сегментов CS (Code Segment - сегмент кодов команд); SS (Stack Segment - сегмент стека); DS (Data Segment); ES, FS и GS - дополнительные сегменты. Использование сегментных регистров определяется типом обращения к памяти. Для многих типов обращений возможно применение альтернативных сегментных регистров, которое вводится префиксами команд CS:, SS:, DS:, ES: FS: или GS: (табл. 3.4). Размер сегмента - лимит - в реальном режиме фиксирован - 64 Кб, в защищенном может задаваться в пределах 1 байт - 4 Гб. С каждым из шести сегментных регистров связаны программно-недоступные регистры дескрипторов, автоматически загружаемые при загрузке соответствующих сегментных регистров. В защищенном режиме в регистры дескрипторов загружается 32-битный базовый адрес, 32-битный лимит и атрибуты сегментов. В реальном режиме лимит фиксирован, атрибуты не используются, а в качестве базового адреса заносится сдвинутое на 4 бита влево значение сегментного регистра. УПРАВЛЯЮЩИЕ РЕГИСТРЫ CRO, CR1, CR2, CR3 хранят признаки состояния процессора, общие для всех задач. Регистр CRO включает в себя биты регистра MSW процессора 80286. Для обеспечения программной совместимости команды LMSW и SMSW затрагивают только эти младшие 4 бита. Назначение бит регистра CRO: РЕ (Protection Enable) - разрешение защиты. Установка этого флага инструкцией LMSW или LOAD CRO переводит процессор в защищенный режим, возврат в реальный режим (сброс флага) возможен только по инструкции LOAD CRO. Сброс бита РЕ является частью довольно длинной последовательности инструкций, подготавливающих корректное переключение в реальный режим. МР (Monitor Processor Extension) - мониторинг сопроцессора, позволяет вызывать исключение 7 по каждой команде WAIT при TS=1. При исполнении программ для 286/287 и 386/387 на процессорах 486DX и старте бит МР должен быть установлен. ЕМ (Processor Extension Emulated) - эмуляция сопроцессора. Установка этого флага вызывает появление исключения 7 при каждой команде, относящейся к сопроцессору, что позволяет прозрачно осуществлять его программную эмуляцию. TS (Task Switch) - переключение задач. При установке этого флага следующая команда, относящаяся к сопроцессору, вызовет исключение 7, что позволяет программно определить, относится ли контекст сопроцессора к текущей задаче. Бит сбрасывается инструкцией CLTS. Сочетание МР=0 ЕМ=0 TS=0, устанавливаемое по аппаратному сбросу, обеспечивает полную совместимость с 8086/88 (исключение 7 не вырабатывается). Сочетание МР=1, ЕМ=0 используется при наличии сопроцессора, а МР=0, ЕМ==1 при его программной эмуляции. ЕТ (Extension Type) - индикатор поддержки инструкций математического сопроцессора. Используется в процессорах 486+; для 486SX ЕТ=0; для остальных процессоров ЕТ=1. NE (Numeric Error) - разрешение стандартного (для Intel, но не для PC) механизма сообщения об ошибке FPU через генерацию исключения (486+). При NE=0 и активном сигнале IGNNE# ошибки FPU игнорируются. При NE=0 и пассивном сигнале IGNNE# при возникновении ошибки FPU процессор останавливается и ждет прерывания, вводимого внешней логикой по сигналу на выходе FERR#. Таким образом эмулируется обработка ошибок FPU, принятая в PC со времен сопроцессоров 80287 и 80387. WP (Write Protect) - разрешение защиты от записи на уровне привилегий супервизора в страницы только для чтения. AM (Alignment Mask) - разрешение контроля выравнивания (контроль выравнивания выполняется только на уровне привилегий 3 при АМ=1 и флаге АС-1). NW (Not Writethrough) - запрет сквозной записи кэша и циклов аннулирования. CD (Cache Disable) - запрет заполнения кэша (кэш-попадания в ранее заполненные строки при этом не запрещаются). PG (Paging Enanable) - включение механизма страничной переадресации памяти. Регистр CR1 не используется. Регистр CR2 (Page Fault Linear Address) хранит 32-битный линейный адрес, по которому был получен последний отказ страницы памяти. Регистр CR3 (Page Directory Base Register) в старших 20 битах хранит физический базовый адрес таблицы каталога страниц. Из младших 12 бит используются следующие: PCD (Page-Level Cache Disable) - запрет кэширования страницы (один из источников сигнала PCD для управления внешним кэшем), 486+. PWT (Page-Level Writes Transparent) - кэширования страницы со сквозной записью (один из источников сигнала PWT для управления внешним кэшем), 486+. Регистр CR4 (присутствует в процессорах Pentium и старше) содержит биты разрешения архитектурных расширений. VME (Virtual-8086 Mode Extensions) - разрешение использования виртуального флага прерываний в режиме V86, что позволяет повысить производительность за счет сокращения излишних вызовов монитора виртуальных машин. PVI (Protected-Mode Virtual Interrupts) - разрешение использования виртуального флага прерываний в защищенном режиме. TSD (Time Stamp Disable) - превращение инструкции RDTSC (read from time stamp counter) в привилегированную. DE (Debugging Extensions) - разрешение точек останова по обращению к портам ввода-вывода. СИСТЕМНЫЕ РЕГИСТРЫ Системные адресные регистры предназначены для ссылок на сегменты и таблицы в защищенном режиме . 47 16 15 32-битные линейные базовые адреса Лимиты 0 GDTR IDTR Системные указатели 15 0 Селекторы TR 32-битные линейные 32-битные лимиты LDTR адреса сегментов Системные сегментные дескрипторов регистры. Атрибуты Автоматически загружаемые регистры РЕГИСТРЫ ОТЛАДКИ Предназначены для задания и управления отладочными точками останова. DRO...DR3 (Linear Breakpoint Address 0...3) хранят 32-битные линейные адреса точек останова; DR4, DR5 в 386-м и 486-м не используются, обращение к ним эквивалентно обращению к регистрам DR6, DR7. В процессоре Pentium при включенном расширении отладки обращение к этим регистрам вызывает исключение недопустимого кода операции; DR6 (Breakpoint Status) отражает состояние контрольной точки; DR7 (Breakpoint Control) управляет установкой контрольных точек. РЕГИСТРЫ ТЕСТИРОВАНИЯ Их состав варьируется в зависимости от типа процессора. Процессоры 386 имели только два регистра, предназначенных для тестирования кэша страничной переадресации - TR6 и TR7. Процессор Pentium имеет 12 тестовых регистров TR1...TR12. Их назначение привязывается к архитектуре - они входят в группу модельно-специфических регистров MSR (Model-Specific Register): TR3 ~ регистр данных внутреннего кэша, TR4 - тестовый регистр состояния кэша, TR5 управляющий регистр тестирования кэша, TR6 (Test Control) - управляющий регистр для теста кэширования страниц, TR? (Test Status) - регистр данных для теста кэширования страниц. Доступность регистров различных групп зависит от режима работы процессора и уровня привилегий задачи . Схема внутреннего управления Типовые значения ключевых параметров для кэш-памяти : РазмТиповые значения ключевых параметров для кэш-памяти : 4-128 байт ер блока (строки) Время попадания (hit time) Потери при промахе (miss penalty) (Время доступа - access time) (Время пересылки - transfer time) Доля промахов (miss rate) Размер кэш-памяти 1-4 такта синхронизации (обычно 1 такт) 8-32 такта синхронизации (6-10 тактов синхронизации) (2-22 такта синхронизации) 1%-20% 4 Кбайт - 16 Мбайт Если каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым отображением (direct mapped). Это наиболее простая организация кэш-памяти, при которой для отображение адресов блоков основной памяти на адреса кэш-памяти просто используются младшие разряды адреса блока. Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти, то кэш называется полностью ассоциативным (fully associative). Если некоторый блок основной памяти может располагаться на ограниченном множестве мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative). Обычно множество представляет собой группу из двух или большего числа блоков в кэше. Если множество состоит из n блоков, то такое размещение называется множественно-ассоциативным с n каналами (n-way set associative). У каждого блока в кэш-памяти имеется адресный тег, указывающий, какой блок в основной памяти данный блок кэш-памяти представляет. Эти теги обычно одновременно сравниваются с выработанным процессором адресом блока памяти. Когда выполняется запись в кэш-память имеются две базовые возможности: сквозная запись (write through, store through) - информация записывается в два места: в блок кэш-памяти и в блок более низкого уровня памяти. запись с обратным копированием (write back, copy back, store in) - информация записывается только в блок кэш-памяти. Модифицированный блок кэш-памяти записывается в основную память только когда он замещается. Для сокращения частоты копирования блоков при замещении обычно с каждым блоком кэш-памяти связывается так называемый бит модификации (dirty bit). Этот бит состояния показывает был ли модифицирован блок, находящийся в кэш-памяти. Если он не модифицировался, то обратное копирование отменяется, поскольку более низкий уровень содержит ту же самую информацию, что и кэш-память. При возникновении промаха, контроллер кэш-памяти должен выбрать подлежащий замещению блок. Как правило для замещения блоков применяются две основных стратегии: случайная и LRU. В первом случае, чтобы иметь равномерное распределение, блоки-кандидаты выбираются случайно. В некоторых системах, чтобы получить воспроизводимое поведение, которое особенно полезно во время отладки аппаратуры, используют псевдослучайный алгоритм замещения. Во втором случае, чтобы уменьшить вероятность выбрасывания информации, которая скоро может потребоваться, все обращения к блокам фиксируются. Заменяется тот блок, который не использовался дольше всех (LRU - Least-Recently Used). ШИНЫ Интерфейс — это средство сопряжения двух устройств, в котором все физические и логические параметры согласуются между собой. Если интерфейс является общепринятым, например, утверждённым на уровне международных соглашений, то он называется стандартным . Каждый из функциональных элементов (память, монитор или другое устройство) связан с шиной определённого типа — адресной, управляющей или шиной данных. Для согласования интерфейсов периферийные устройства подключаются к шине не напрямую, а через свои контроллеры (адаптеры) и порты примерно по такой схеме: Контроллеры и адаптеры представляют собой наборы электронных цепей, которыми снабжаются устройства компьютера с целью совместимости их интерфейсов. Контроллеры, кроме этого, осуществляют непосредственное управление периферийными устройствами по запросам микропроцессора, т.е. Контроллер это устройство, которое связывает периферийное оборудование или каналы связи с центральным процессором, освобождая процессор от непосредственного управления функционированием данного оборудования. Порты устройств представляют собой некие электронные схемы, содержащие один или несколько регистров ввода-вывода и позволяющие подключать периферийные устройства компьютера к внешним шинам микропроцессора. Портами также называют устройства стандартного интерфейса: последовательный, параллельный и игровой порты (или интерфейсы). Последовательный порт обменивается данными с процессором побайтно, а с внешними устройствами — побитно. Параллельный порт получает и посылает данные побайтно. Шинные интерфейсы: ISA - Industry Standard Architecture. Позволила связать все устройства системного блока между собой, обеспечила простое подключение новых устройств через стандартные разъемы (слоты). Пропускная способность низкая, но эта шина продолжает использоваться в компьютерах для подключения сравнительно "медленных" внешних устройств, напр. звуковых карт и модемов. PCI -Peripheral Component Interconnect - стандарт подключения внешних компонентов - был введен в ПК, выполненных на базе процессоров Intel Pentium. Интерфейс локальной шины, связывающей процессор с ОП, в которую врезаны разъемы для подключения внешних устройств. Поддерживает режим plug-and-play, в результате которого устройство автоматически получает номер используемого прерывания, адрес порта подключения и номер канала прямого доступа к памяти. FSB. Шина PCI сегодня используется только как шина для подключения ВУ, а для связи процессора и памяти, начиная с процессора Intel Pentium Pro, используется специальная шина, получившая название Front Side Bus. Эта шина работает на очень высокой частоте 100-125 МГц. В настоящее время внедряются материнские платы с частотой шины 133 МГц и выше. Пропускная способность шины при частоте 100 МГц составляет порядка 800 Мбайт/с. AGP. Видеоадаптер - устройство, требующее особенно высокой скорости передачи данных. Видеоадаптер всегда был первым устройством, врезаемым в новую шину. Для них разработана отдельная шина, получившая название AGP( Advanced Graphic Port - усовершенствованный графический порт). Частота этой шины соответствует частоте шины PCI(33 МГц или 66 МГц), но она имеет более высокую пропускную способность. USB (Universal Serial Bus -универсальная последовательная магистраль). Этот стандарт определяет способ взаимодействия компьютера с периферийным оборудованием. Он позволяет подключать до 256 различных устройств, имеющих последовательный интерфейс. Производительность шины относительно невелика, но для таких устройств, как клавиатура, мышь, модем, джойстик и т.п., этого достаточно. Она практически исключает конфликты между различным оборудованием, позволяет подключать и отключать устройства в "горячем режиме" (не выключая компьютер) и позволяет объединять несколько компьютеров в простейшую локальную сеть без применения специального оборудования и программного обеспечения. Чипсет: Чипсет (chipset) — это базовый набор микросхем, определяющий архитектуру взаимодействия всех основных подсистем компьютера. Фактически все функциональные возможности материнской платы определяются установленным на ней чипсетом. Выбор чипсетов на сегодняшний день еще более разнообразен, чем выбор процессоров. Чипсеты выпускают такие компании, как AMD, Intel, VIA, SiS, Intel, nVIDIA и ATi. Чипсет материнской платы определяет поддерживаемый тип процессора, тип памяти, а также функциональные возможности по подключению периферийных устройств. От чипсета в немалой степени зависит и производи-тельность материнской платы.Большинство чипсетов выпускаются на базе двух микросхем, называемых "Северный мост" и "Южный мост" . "Северный мост" управляет взаимосвязью четырех устройств: процессора, оперативной памяти, порта AGP и шины PCI. "Южный мост" выполняет функции контроллера жестких и гибких дисков, функции моста PCIISA, контроллера клавиатуры, мыши, шины USB. Северный мост с кулером: Южный мост: ВНУТРЕННЯЯ ПАМЯТЬ Под внутренней памятью современного компьютера принято понимать быстродействующую электронную память, расположенную на его системной плате. Сейчас такая память изготавливается на базе самых современных полупроводниковых технологий (раньше использовались магнитные устройства на основе ферритовых сердечников – лишнее свидетельство тому, что конкретная физические принципы значения не имеют). Наиболее существенная часть внутренней памяти называется ОЗУ - оперативное запоминающее устройство. Его главное назначение состоит в том, чтобы хранить данные и программы для решаемых в текущий момент задач. Наверное, каждому пользователю известно, что при выключении питания содержимое ОЗУ полностью теряется. В состав внутренней памяти современного компьютера помимо ОЗУ также входят и некоторые другие разновидности памяти, которые при первом знакомстве можно пропустить. Здесь упомянем только о постоянном запоминающем устройстве (ПЗУ), в котором в частности хранится инфор-мация, необходимая для первоначальной загрузки компьютера в момент включения пита-ния. Как очевидно из названия, информация в ПЗУ не зависит от состояния компью-тера (для лучшего понимания можно указать на некоторую аналогию между информацией в ПЗУ и “врожденными” безусловными рефлексами у живых существ). Раньше содержимое ПЗУ раз и навсегда формировалось на заводе, теперь же современные технологии позволяют в случае необходимости обновлять его даже не извлекая из компьютерной платы. ВНУТРЕННЯЯ ПАМЯТЬ: ROM К устройствам специальной памяти относятся постоянная память (ROM), перепрограммируемая постоянная память (Flash Memory), память CMOS RAM, питаемая от батарейки, видеопамять и некоторые другие виды памяти. Постоянная память (ПЗУ, англ. ROM, Read Only Memory — память только для чтения) — энергонезависимая память, используется для хранения данных, которые никогда не потребуют изменения. Содержание памяти специальным образом “зашивается” в устройстве при его изготовлении для постоянного хранения. Перепрограммируемая постоянная память (Flash Memory) — энергонезависимая память, допускающая многократную перезапись своего содержимого. Важнейшая микросхема постоянной или Flash-памяти — модуль BIOS. Функции: проверка работоспособности системы управления электропитанием; инициализация системных ресурсов и регистров чипсетов; тестирование оперативной памяти; подключение клавиатуры; тестирование портов; инициализация контроллеров, определение и подключение жестких дисков. ВНУТРЕННЯЯ ПАМЯТЬ: RAM Оперативная память (ОЗУ, англ. RAM, Random Access Memory — память с произвольным доступом) — это быстрое запоминающее устройство,основанное на триггерах , непосредственно связанное с процессором и предназначенное для записи, считывания и хранения выполняемых программ и данных, обрабатываемых этими программами. Оперативная память используется только для временного хранения данных и программ, так как, когда машина выключается, все, что находилось в ОЗУ, пропадает. Доступ к элементам оперативной памяти прямой — это означает, что каждый байт памяти имеет свой индивидуальный адрес.