приложения к отчету по умк-4

реклама

ПРИЛОЖЕНИЕ 4

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ «МИЭТ»

«УТВЕРЖДАЮ»

Ректор МИЭТ

чл.-корр. РАН

____________________ Ю.А. Чаплыгин

«_____» _____________________ 2011 г.

ПРОГРАММА ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

«ЭНЕРГОЭФФЕКТИВНОЕ ПРОЕКТИРОВАНИЕ НАНОЭЛЕКТРОННЫХ ИС

СРЕДСТВАМИ САПР CADENCE И SYNOPSYS»

2011 г.

Рабочая программа профессионального модуля утверждена на заседании учебно-методического

совета образовательных программ опережающей профессиональной подготовки (уровень - магистратура) и переподготовки в области проектирования и производства СБИС с топологическими

нормами 90 нм, протокол от 16 ноября 2011 г. № 2.

Организация-разработчик: Национальный исследовательский университет «МИЭТ»

Авторы:

Лосев В.В., к.т.н., доцент

Коршунов А.В., ассистент.

2

СОДЕРЖАНИЕ

1. ПАСПОРТ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ................................................ 4

2. РЕЗУЛЬТАТЫ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ............................................. 6

3. СТРУКТУРА И СОДЕРЖАНИЕ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ ...................................... 7

4. УСЛОВИЯ РЕАЛИЗАЦИИ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ .................. 11

5. КОНТРОЛЬ И ОЦЕНКА РЕЗУЛЬТАТОВ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО

МОДУЛЯ (ВИДА ПРОФЕССИОНАЛЬНОЙ ДЕЯТЕЛЬНОСТИ) ............................................... 13

3

1. ПАСПОРТ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

«ЭНЕРГОЭФФЕКТИВНОЕ ПРОЕКТИРОВАНИЕ НАНОЭЛЕКТРОННЫХ ИС

СРЕДСТВАМИ САПР CADENCE И SYNOPSYS»

1.1. Область применения программы

Программа профессионального модуля является частью профессиональной образовательной программы переподготовки специалистов по

профессии 210100 - «Электроника и наноэлектроника»

в части освоения вида профессиональной деятельности:

проектно- конструкторская деятельность

и соответствующих профессиональных компетенций (ПК):

знание основ физики современных полупроводниковых приборов и твердотельной электрони-

ки с наноразмерными топологическими нормами;

- знание основ теории автоматизированного проектирования, моделирования и характеризации

СБИС с топологическими нормами до 90 нм;

владение методами системотехнического, функционально-логического, схемотех-нического и

топологического проектирования СБИС с топологическими нормами 90 нм с использованием

САПР Cadence, Synopsys;

навыки проектирования, расчета, моделирования и конструирования приборов и устройств

электронной техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys, Agilent.

1.2.

Цели и задачи модуля - требования к результатам освоения модуля

С целью овладения указанным видом профессиональной деятельности и соответствующими профессиональными компетенциями обучающийся в ходе освоения профессионального модуля должен:

иметь практический опыт:

Владеть: навыками проектирования, расчета, моделирования и конструирования приборов и

устройств электронной техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys, Agilent.

Уметь: пользоваться методами системотехнического, функционально-логического, схемотехнического и топологического проектирования СБИС с топологическими нормами 90 нм с использованием САПР Cadence, Synopsys

Знать: основы теории автоматизированного проектирования, моделирования и характеризации

СБИС с топологическими нормами до 90 нм.

4

1.3.Рекомендуемое количество часов на освоение программы профессионального модуля:

всего - 70 часов, в том числе:

максимальной учебной нагрузки обучающегося - 70 часа, включая:

обязательной аудиторной учебной нагрузки обучающегося - 34 часа.

5

2. РЕЗУЛЬТАТЫ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

Результатом освоения программы профессионального модуля является овладение обучающимися

видом профессиональной деятельности - в области проектно- конструкторской деятельности, в

том числе профессиональными (ПК):

Код

Наименование результата обучения

БКП-1

Знание основ физики современных полупроводниковых приборов и твердотельной

электроники с наноразмерными топологическими нормами

Знание основ теории автоматизированного проектирования, модели-рования и характеризации СБИС с топологическими нормами до 90 нм

Владение методами системотехнического, функционально-логического, схемотехнического и топологического проектирования СБИС с топологическими нормами 90 нм с

использованием САПР Cadence, Synopsys

Навыки проектирования, расчета, моделирования и конструирования приборов и

устройств электронной техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys,

Agilent

БКП-3

БКП-5

БКП-6

6

3. СТРУКТУРА И ПРИМЕРНОЕ СОДЕРЖАНИЕ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

3.1. Тематический план профессионального модуля

Коды профессиональных компетенций

1

БКП-1, БКП-3,

БКП-5, БКП-6

Наименования разделов профессионального модуля

2

Раздел 1. "Энергоэффективное

проектирование наноэлектронных ИС средствами САПР

Cadence и Synopsys"

Всего:

Всего часов

(макс. учебная

нагрузка и

практики)

3

70

Объем времени, отведенный на освоение

междисциплинарного курса (курсов)

Обязательная аудиторная учебная

нагрузка обучающегося

Всего,

в т.ч. лабочасов

раторные

работы и

практические занятия,

часов

4

5

16

34

70

34

7

16

Самостоятельная работа обучающегося,

часов

Производственное обучение

(в т.ч. производственная

практика)

Учебная,

Производчасов

ственная,

часов

(если предусмотрена рассредоточенная

практика)

6

36

7

8

36

-

-

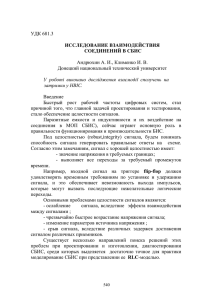

3.2. Содержание обучения по профессиональному модулю (ПМ)

Наименование разделов

профессионального модуля

(ПМ), междисциплинарных

курсов (МДК) и тем

1

Раздел «Энергоэффективное проектирование наноэлектронных ИС средствами САПР Cadence и

Synopsys»

МДК 1. …………………..

номер и наименование МДК

«МОП схема. Статическая

потребляемая мощность»

Тема 1.2.

«Динамическая потребляемая мощность»

Тема 1.3.

«Способы снижения статической потребляемой мощности»

Содержание учебного материала, лабораторные работы и практические занятия, самостоятельная работа обучающихся, курсовая работ (проект) (если предусмотрены)

Объем

часов

Уровень

освоения

2

3

*

4

*

Содержание (указывается перечень дидактических единиц)

1. Энергопотребление цифровых схем.

Лабораторные работы (при наличии, указываются темы)

1

Изучение источников статической потребляемой мощности.

Практические занятия (при наличии, указываются темы)

1.

Содержание (указывается перечень дидактических единиц)

1. Энергопотребление цифровых схем.

Лабораторные работы (при наличии, указываются темы)

1.

Практические занятия (при наличии, указываются темы)

1.

Содержание (указывается перечень дидактических единиц)

1. Способы снижения энергопотребления I. Метод clock gating.

2.

Лабораторные работы (при наличии, указываются темы)

1 Способы снижения динамической потребляемой мощности

Практические занятия (при наличии, указываются темы)

1

8

*2

*4

3**

*

*2

3**

*

*

*2

3**

3**

*4

*

Наименование разделов

профессионального модуля

(ПМ), междисциплинарных

курсов (МДК) и тем

Тема 1.4.

«Способы снижения статической и динамической потребляемой мощности. Обзор»

Тема 1.5.

«Метод clock gating. Метод

operand isolation»

Тема 1.6.

«Метод gate level optimization. Метод power domain»

Тема 1.7.

«Автоматизация процесса

энергоэффективного проекти-рования в САПР

Сadence»

Содержание учебного материала, лабораторные работы и практические занятия, самостоятельная работа обучающихся, курсовая работ (проект) (если предусмотрены)

Содержание (указывается перечень дидактических единиц)

1. Способы снижения энергопотребления I

Лабораторные работы (при наличии, указываются темы)

1.

Практические занятия (при наличии, указываются темы)

1.

Содержание (указывается перечень дидактических единиц)

1. Способы снижения энергопотребления II

Лабораторные работы (при наличии, указываются темы)

1. Способы снижения динамической потребляемой мощности. Метод operand isolation.

Практические занятия (при наличии, указываются темы)

1.

Содержание (указывается перечень дидактических единиц)

1. Способы снижения энергопотребления II

Лабораторные работы (при наличии, указываются темы)

1.

Практические занятия (при наличии, указываются темы)

1.

Содержание (указывается перечень дидактических единиц)

1. Автоматизация процесса энергоэффективного проектирования.

Лабораторные работы (при наличии, указываются темы)

1. Снижение потребляемой мощности на этапе функционально-логического проектирования.

2.

Практические занятия (при наличии, указываются темы)

1.

9

Объем

часов

Уровень

освоения

*2

3**

*

*2

3**

*4

*

*2

3**

*

*

*2

3**

4

*

Наименование разделов

профессионального модуля

(ПМ), междисциплинарных

курсов (МДК) и тем

Тема 1.8.

«Автоматизация процесса

энергоэффективного проекти-рования в САПР

Synopsys»

Содержание учебного материала, лабораторные работы и практические занятия, самостоятельная работа обучающихся, курсовая работ (проект) (если предусмотрены)

Содержание (указывается перечень дидактических единиц)

1. Автоматизация процесса энергоэффективного проектирования.

2.

Лабораторные работы (при наличии, указываются темы)

1.

Практические занятия (при наличии, указываются темы)

1.

Самостоятельная работа при изучении раздела ПМ 1. (при наличии, указываются задания)

Объем

часов

*4

3**

3**

*

*

36

Примерная тематика домашних заданий

………………………………………

Всего

**Для характеристики уровня освоения учебного материала используются следующие обозначения:

1 - ознакомительный (узнавание ранее изученных объектов, свойств);

2 - репродуктивный (выполнение деятельности по образцу, инструкции или под руководством);

3 - продуктивный (планирование и самостоятельное выполнение деятельности, решение проблемных задач).

10

Уровень

освоения

70

4. УСЛОВИЯ РЕАЛИЗАЦИИ ПРОГРАММЫ ПРОФЕССИОНАЛЬНОГО МОДУЛЯ

4.1. Требования к минимальному материально-техническому обеспечению

Реализация программы модуля предполагает наличие компьютерного класса.

Комплект учебно-методической документации (учебники и учебные пособия, лабораторный практикум, комплекты тестовых заданий).

Программное и коммуникационное обеспечение

Лицензионная САПР компании Cadence Design Systems и Synopsys

Оборудование и технологическое оснащение рабочих мест:

Моделирование выполняется на рабочих станциях HP XW8400 (2x Xeon 3ГГц, 16Гб) под управление Linux RHEL 5, с использованием САПР Cadence и Synopsys развернутых на базе высокопроизводительного сервера HP Proliant ML370. Рабочие станции и сервер объединены в локальную

вычислительную сеть с пропускной способностью не менее 100 Мбит/сек. Мультимедийный комплекс, включающий ноутбук, аудиосистему и проектор для мультимедийных образовательных ресурсов. Высокоскоростной доступ в сеть Интернет.

4.2. Информационное обеспечение обучения

Перечень рекомендуемых учебных изданий, Интернет-ресурсов, дополнительной литературы

Основные источники:

1. Siva G. Narendra, Anantha Chandrakasan, Leakage in nanometer CMOS technologies, Springer,2006

2. Changbo Long, Lei He, Distributed Sleep Transistor Network for Power Reduction, Proc. IEEE/ACM

Design Automation Conference, 2003

3. Jan M.Rabaey and Massound Pedram, Low power design methodologies, Kluwer Academic Pub.2002

4.3. Общие требования к организации образовательного процесса

Рекомендуемые образовательные технологии. Проведение лабораторного практикума на основе

компьютерных симуляций. Участие в тренингах компании Cadence и Synopsys (США).

Дисциплины, предшествующие освоению данного модуля:

- Проектирование и технология электронной компонентной базы;

- Компьютерные технологии в науке и технике

- Компоненты наноразмерных ИС и их модели;

- Методы математического моделирования.

11

4.4. Кадровое обеспечение образовательного процесса

Требования к квалификации педагогических кадров, обеспечивающих обучение по междисциплинарному курсу (курсам):

Наличие опыта преподавательской работы в области профессиональной специализации не менее

2-х лет.

Требования к квалификации педагогических кадров, осуществляющих руководство практикой.

Профессорско-преподавательский состав: наличие ученой степени в соответствующей научной

области.

12

5. КОНТРОЛЬ И ОЦЕНКА РЕЗУЛЬТАТОВ ОСВОЕНИЯ ПРОФЕССИОНАЛЬНОГО

МОДУЛЯ (ВИДА ПРОФЕССИОНАЛЬНОЙ ДЕЯТЕЛЬНОСТИ)

Реализация подготовки по программе профессионального модуля обеспечивается организацией и

проведением текущего и итогового контроля демонстрируемых обучающимися знаний, умений и

навыков. Текущий контроль проводится преподавателем в процессе обучения. Итоговый контроль

проводится в виде зачета после обучения по курсу.

Формы и методы текущего и итогового контроля по профессиональному модулю разрабатываются

и доводятся до сведения обучающихся в начале обучения.

Для текущего и итогового контроля образовательными учреждениями создаются фонды оценочных средств (ФОС).

ФОС включают в себя педагогические контрольно-измерительные материалы, предназначенные

для определения соответствия (или несоответствия) индивидуальных образовательных достижений основным показателям результатов подготовки (таблицы).

Раздел (тема) междисциплинарного

курса

№ 1.1

«МОП схема. Статическая потребляемая

мощность»

Результаты

(освоенные профессиональные

компетенции)

БКП-3. Знание основ теории автоматизированного проектирования,

моделирования и характеризации

СБИС с топологическими нормами

до 90 нм.

№ 1.2

«Динамическая потребляемая мощность»

БКП-3. Знание основ теории автоматизированного проектирования,

моделирования и характеризации

СБИС с топологическими нормами

до 90 нм.

13

Основные показатели

результатов подготовки

Выполнение

Демонстрация

Определение

Проектирование

Создание

Планирование

Выделение

Получение

Изложение

Решение

Обоснование

Формулирование

Изготовление

Нахождение

Например:

Определение базовых

понятий по способам и

методам снижения потребляемой мощности.

Формулирование основных принципов.

Формы и

методы контроля

Раздел (тема) междисциплинарного

курса

Результаты

(освоенные профессиональные компетенции)

№ 1.3

«Способы снижения

статической потребляемой мощности»

БКП-3. Знание основ теории автоматизированного проектирования, моделирования и характеризации СБИС с топологическими нормами до 90 нм.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования приборов и устройств электронной

техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys,

Agilent.

БКП-3. Знание основ теории автоматизированного проектирования, моделирования и характеризации СБИС с топологическими нормами до 90 нм.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования приборов и устройств электронной

техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys,

Agilent.

БКП-5. Владение методами системотехнического, функционально- логического, схемотехнического и топологического проектирования СБИС с

топологическими нормами 90 нм с использованием САПР Cadence, Synopsys.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования приборов и устройств электронной

техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys,

Agilent.

БКП-5. Владение методами системотехнического, функционально-логического,

схемотехнического и топологического

проектирования СБИС с топологическими нормами 90 нм с использованием

САПР Cadence, Synopsys.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования приборов и устройств электронной

техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys,

Agilent

№ 1.4

«Способы снижения

статической и динамической потребляемой мощности. Обзор»

№ 1.5

«Метод clock gating.

Метод operand isolation»

№ 1.6

«Метод gate level optimization. Метод

power do»

14

Основные показатели

результатов подготовки

Понимание основных

источников рассеяния

мощности в микроэлектронных схемах.

Выполнение лабораторного занятия по

теме «Метод clock

gating»

Выполнение лабораторного занятия по

теме «Метод gate level

optimization»

Формы и

методы

контроля

Раздел (тема) междисциплинарного

курса

Результаты

(освоенные профессиональные компетенции)

Основные показатели

результатов подготовки

№ 1.7

«Автоматизация

процесса энергоэффективного проектирования в САПР

Сadence»

БКП-5. Владение методами системотехнического, функционально-логического,

схемотехнического и топологического

проектирования СБИС с топологическими нормами 90 нм с использованием

САПР Cadence, Synopsys.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования

приборов и устройств электронной техники на схемотехническом и элементном уровне с использованием систем

автоматизированного проектирования

компаний Cadence, Synopsys, Agilent

БКП-5. Владение методами системотехнического, функционально-логического,

схемотехнического и топологического

проектирования СБИС с топологическими нормами 90 нм с использованием

САПР Cadence, Synopsys.

БКП-6. Навыки проектирования, расчета, моделирования и конструирования

приборов и устройств электронной техники на схемотехническом и элементном уровне с использованием систем

автоматизированного проектирования

компаний Cadence, Synopsys, Agilent

Владение методологией проектирования

энергоэффективных

ИС с использованием

САПР Cadence

№ 1.8

«Автоматизация

процесса энергоэффективного проектирования в САПР

Synopsys»

Раздел (тема) междисциплинарного

курса

№ 1.1

«МОП схема. Статическая потребляемая

мощность»

№ 1.2

«Динамическая потребляемая мощность»

Результаты

(освоенные общие компетенции)

ОК-1. Способность совершенствовать и развивать свой интеллектуальный и общекультурный уровень.

ОК-3. Способность свободно пользоваться русским и иностранным

языками, как средством делового

общения.

ОК-4. Способность использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении коллективом.

ОК-8. Способность позитивно воздействовать на окружающих с точки зрения соблюдения норм и рекомендаций здорового образа

жизни.

ОК-2. Способность к самостоятельному обучению новым методам исследования, к изменению

научного и научнопроизводственного профиля своей

профессиональной деятельности.

15

Формы и

методы

контроля

Владение методологией проектирования

энергоэффективных

ИС с использованием

САПР Synopsys.

Основные показатели

результатов подготовки

Демонстрация способностей использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении

коллективом

Демонстрация самостоятельности обучению новым методам исследования.

Формы и

методы контроля

Промежуточная аттестация

Промежуточная аттестация

Раздел (тема) междисциплинарного

курса

№ 1.3

«Способы снижения

статической потребляемой мощности»

№ 1.4

«Способы снижения

статической и динамической потребляемой мощности. Обзор»

№ 1.5

«Метод clock gating.

Метод operand isolation»

Результаты

(освоенные общие компетенции)

ОК-7. Способность адаптироваться

к изменяющимся условиям, переоценивать накопленный опыт, анализировать свои возможности.

ОК-4. Способность использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении коллективом.

ОК-5. Способность проявлять инициативу, в том числе в ситуациях

риска, брать на себя всю полноту

ответственности.

ОК-4. Способность использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении коллективом.

№ 1.6

«Метод gate level optimization. Метод

power do»

№ 1.7

«Автоматизация

процесса энергоэффективного проектирования в САПР

Сadence»

ОК-6. Готовность к активному общению с коллегами в научной, производственной и социальнообщественной сферах деятельности.

ОК-9. Готовность использовать

знания правовых и этических норм

при оценке последствий своей

профессиональной деятельности,

при разработке и осуществлении

социально значимых проектов.

№ 1.8

«Автоматизация

процесса энергоэффективного проектирования в САПР

Synopsys»

ОК-9. Готовность использовать

знания правовых и этических норм

при оценке последствий своей

профессиональной деятельности,

при разработке и осуществлении

социально значимых проектов.

Процент результативности (правильных ответов)

90 ÷ 100

80 ÷ 89

70 ÷ 79

Менее 70

Основные показатели

результатов подготовки

Понимание значимости

адаптации к изменяющимся условиям. Проведение анализа своих возможностей.

Демонстрация способностей использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении

коллективом

Демонстрация способностей использовать на

практике умения и навыки в организации исследовательских и проектных работ, в управлении

коллективом

Готовность к демонстрации междисциплинарной

деятельности в коллективе.

Демонстрация знаний

правовых и этических

норм при оценке последствий своей профессиональной деятельности,

при разработке и осуществлении социально

значимых проектов

Демонстрация знаний

правовых и этических

норм при оценке последствий своей профессиональной деятельности,

при разработке и осуществлении социально

значимых проектов

Формы и

методы контроля

Промежуточная аттестация

Промежуточная аттестация

Промежуточная аттестация

Промежуточная аттестация

Промежуточная аттестация

Промежуточная аттестация

Качественная оценка индивидуальных образовательных достижений

балл (отметка)

вербальный аналог

5

Отлично

4

Хорошо

3

Удовлетворительно

2

Не удовлетворительно

На этапе промежуточной аттестации по медиане качественных оценок индивидуальных образовательных достижений экзаменационной комиссией определяется интегральная оценка освоенных

обучающимися профессиональных и общих компетенций как результатов освоения профессионального модуля.

16

МЕТОДИЧЕСКИЕ МАТЕРИАЛЫ ДЛЯ ПРЕПОДАВАТЕЛЕЙ

Учебный модуль:

«Энергоэффективное проектирование наноэлектронных ИС средствами САПР Cadence и

Synopsys»

В рамках данного междисциплинарного курса образовательный процесс направлен на развитие следующих компетенций:

- знание основ физики современных полупроводниковых приборов и твердотельной электроники с наноразмерными топологическими нормами;

- знание основ теории автоматизированного проектирования, моделирования и характеризации СБИС с топологическими нормами до 90 нм;

- владение методами системотехнического, функционально-логического, схемотехнического

и топологического проектирования СБИС с топологическими нормами 90 нм с использованием

САПР Cadence, Synopsys;

- навыки проектирования, расчета, моделирования и конструирования приборов и устройств

электронной техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys, Agilent.

В результате изучения междисциплинарного курса слушатель должен:

Знать: основы теории автоматизированного проектирования, моделирования и характеризации СБИС с топологическими нормами до 90 нм.

Уметь: пользоваться методами системотехнического, функционально-логического, схемотехнического и топологического проектирования СБИС с топологическими нормами 90 нм с использованием САПР Cadence, Synopsys

Владеть: навыками проектирования, расчета, моделирования и конструирования приборов и

устройств электронной техники на схемотехническом и элементном уровне с использованием систем автоматизированного проектирования компаний Cadence, Synopsys, Agilent.

Тематическое содержание междисциплинарного курса должно включать следующие

дидактические единицы.

1. Энергопотребление цифровых схем.

2. Способы снижения энергопотребления I

3. Способы снижения энергопотребления II

4. Автоматизация процесса энергоэффективного проектирования.

Рекомендуемые образовательные технологии: Проведение лабораторного практикума на

основе компьютерных симуляций. Участие в тренингах компании Cadence и Synopsys (США).

1

УЧЕБНО-МЕТОДИЧЕСКИЕ МАТЕРИАЛЫ ДЛЯ СЛУШАТЕЛЕЙ

Учебный модуль:

«Энергоэффективное проектирование наноэлектронных ИС средствами САПР

Cadence и Synopsys»

Изучение учебного модуля направлено на ознакомление с современными программными

средствами

приборно-технологического

моделирования

и

обучение

методам

приборно-

технологического моделирования устройств с топологическими нормами 90 нм.

К задачам слушателя относится:

изучение общих подходов приборно-технологического моделирования субмикронных и

наноразмерных устройств;

изучение методики выбора моделей технологических процессов при моделировании

устройств с нормами 90 нм и менее;

изучение методики выбора моделей при приборном моделировании устройств с нормами

90 нм и менее;

изучение методики настройки и калибровки моделей.

При выполнении лабораторных работ необходимо руководствоваться следующими методическими указаниями.

Лабораторная работа № 1. Способы изучения источников статической потребляемой

мощности

Цель работы:

1) ознакомление с механизмами статического энергопотребления КМОП СБИС.

2) моделирование, средствами пакета HSPICE САПР Synopsys, различных схемотехнических

решений, использующих эффект влияния подложки, и оценка их влияния на статическую мощность.

Лабораторные задания и порядок выполнения работы:

1) Выбрать вариант лабораторного задания в соответствии с Таблицей 1.

2) Составить схему инвертора в соответствии с выбранным вариантом.

3) Провести логическую верификацию инвертора. Получить функциональные диаграммы.

4) Провести схемотехническое моделирование инвертора. Оценить среднее время задержки

переключения и мощность, потребляемую за период.

2

5) Составить схему одноразрядного полусумматора в соответствии с выбранным вариантом.

6) Провести логическую верификацию одноразрядного полусумматора. Получить функциональные диаграммы.

7) Провести схемотехническое моделирование одноразрядного полусумматора. Оценить

среднее время задержки переключения и мощность, потребляемую за период.

8) Оформить отчет о проделанной работе.

Таблица 1. Варианты заданий на лабораторную работу

Схемотехническое

решение

DTCMOS

MTCMOS

VTCMOS

DTCMOS

MTCMOS

№

1

2

3

4

5

Напряжение

питания, В

Температура,

˚С

№

0.90

1.00

1.10

0.90

1.00

-20

25

75

-20

25

6

7

8

9

10

Схемотехническое

решение

VTCMOS

DTCMOS

MTCMOS

VTCMOS

DTCMOS

Напряжение

питания, В

Температура, ˚С

0.90

1.00

1.10

0.90

1.00

-20

25

75

-20

25

Теоретическая часть

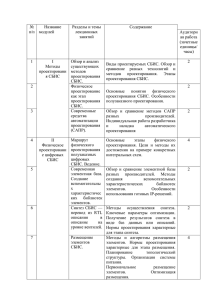

Ниже приведены основные схемотехнические решения для снижения статического энергопотребления МОП СБИС.

VDD

Vin

Vout

Схема

управления

Gnd

а

б

в

Рис.1. Схемотехнические решения для снижения статической мощности:

а - VTCMOS; б - DTCMOS; в - MTCMOS

Технология VTCMOS используется при построении энергоэффективных МОП СБИС. Используя эффект влияния подложки, эффективное пороговое напряжение можно контролировать за

счет смещения подложки. В результате данная технология позволяет получить высокое V TH в режиме ожидания и низкое VTH в активном режиме в одних и тех же МОП транзисторах.

На рис.1а изображен КМОП инвертор с применением технологии VTCMOS. Во время активного режима на подложку p канального МОП транзистора подается напряжение питания V dd, а

на подложку n-канального МОП транзистора - 0 В, обеспечивая, таким образом, низкое эффектинвое пороговое напряжение, а следовательно высокое быстродействие. Во время режима ожидания

3

на подложки p- и n- канальных МОП транзисторов подается напряжение 2Vdd и -Vdd соответственно. В результате эффективное пороговое напряжение увеличивается, приводя к уменьшению тока

утечки.

В схеме с динамическим пороговым напряжением DTCMOS достигается автоматическое изменение пороговых напряжений МОП транзисторов посредством соединения дополнительных

управляющих электродов с входами. На рис.1б приведена схема логического вентиля, воплощающая эту идею путем непосредственного соединения подложки с затвором.

При работе схемы, когда на входе имеет место напряжение логической единицы, равное

напряжению питания, эффективное пороговое напряжение уменьшается, и, следовательно, увеличивается ток, перезаряжающий нагруженную емкость, что приводит к повышению быстродействия. Когда же на входе имеет место напряжение логического нуля, равное нулю, пороговое

напряжение n-МОП транзистора не меняется, что дает малые токи утечки. Следовательно, схема с

динамическим порогом может демонстрировать как высокое быстродействие в активном режиме,

так и малые токи утечек (то есть малое энергопотребление) в неактивном режиме.

Токи утечки могут динамически контролироваться, используя схемы с множественным пороговым напряжением MTCMOS (рис.1в).

Такие схемы могут работать при малых напряжениях питания (около 1В). При этом используются транзисторы с разным пороговым напряжением - малым (VTH около 0,2 В) и большим (VTH

около 0,6 В). Блок, содержащий транзисторы с малым VTH, обеспечивает высокое быстродействие,

за счет малого времени переключения, а транзисторы с высоким VTH - транзистор М1 и транзистор

М2 - отключают схему в те моменты времени, когда она не должна выполнять какие-либо операции. Отключение обеспечивается за счет подачи на входы этих транзисторов sleep-сигнала (положительного для М1 и отрицательного для М2). Sleep-режим работы дает уменьшение статической

составляющей рассеиваемой мощности, которая довольно значительна, из-за больших токов утечек у транзисторов с малым значением VTH .

Недостатком этой технологии является дополнительная емкость, которую вносит в схему

Sleep транзистор, и как следствие - уменьшение быстродействия. Необходимо очень тщательно

производить выбор размеров Sleep-транзистора. Увеличение размеров этого транзистора больше

необходимой величины добавляет ненужную лишнюю емкость, что приводит к увеличению потребляемой мощности, в то время как слишком маленькие размеры Sleep-транзистора приводят к

ограничению питающего тока и ухудшению быстродействия.

Другим недостатком этой технологии является появление дополнительных помех в цепях

питания. Например, в шине «земли» помехи появляются в следствии того, что емкость виртуальной шины «земли» намного больше реальной земли. Такие помехи отрицательно сказываются на

запасе помехоустойчивости и задержках.

4

Экспериментальная часть

1) Составить схему КМОП инвертора, используя данные из таблицы вариантов

2) Получить описание схемы (inv.netl файл) и расположить его по следующему адресу:

/student_lab/digital_ic/variant_val/...

3) Необходимые входные файлы (список цепей и файл задания) для моделирования.

Для входных файлов принять:

Продолжительность входного фронта: 50 псек, для расчета мощности продолжительность

входного фронта берется 5 нс

Значение выходной емкостной нагрузки в соответствии с выбранным вариантом.

4) Создать необходимый входной файл для КМОП инвертора, используемый для измерения

задержек и времени переключения в переходном режиме с применением программного средства

схемотехнического моделирования. Задержку измерить по уровню 0,5·Vdd, а величину фронта по

уровням 0,1·Vdd - 0,9·Vdd

5) Получить графики входного и выходного сигналов - функциональные диаграммы зависимости напряжений входов и выходов от времени - при емкости нагрузки равной нулю, и равной 5 фФ.

6) Получить значения средней потребляемой за период мощности, средствами HSPICE.

7) Составить схему одноразрядного КМОП полусумматора

8) Получить описания схемы одноразрядного КМОП полусумматора, расположить их по адресу home/students/uxxx (номер по списку)/ далее рабочий каталог, из которого запускается программа моделирования.

9) Составить входные файлы (список цепей и файл задания) для моделирования полусумматора в среде HSPICE.

10) Для входного файла взять значения длительности входного фронта и нагрузки из таблицы вариантов (Таблица 1).

11) Составить функциональную таблицу (таблицу истинности) для данного элемента.

12) Получить графики входного и выходного сигналов - функциональные диаграммы зависимости напряжений входов и выходов от времени - при емкости нагрузки равной нулю, и равной

значению 5 фФ.

13) Получить значения средней потребляемой за период мощности средствами HSPICE.

1.5 Обработка результатов моделирования

1) Инвертор.

Сравнить функциональные диаграммы выходных сигналов при различных емкостях нагрузки. Сравнить значения потребляемой мощности и быстродействия инверторов, выполненных по

схемотехнике с изменяемым эффективным пороговым напряжения (DT -, VT- и MT- CMOS), со

стандартной реализацией КМОП.

5

2) Сумматор

Сравнить функциональные диаграммы выходных сигналов при различных С нагрузки. Убедиться в функциональной работоспособности схемы одноразрядного сумматора. Сравнить значения потребляемой мощности и быстродействия полусумматоров, выполненных по схемотехнике с

изменяемым эффективным пороговым напряжения (DT -, VT- и MT- CMOS), со стандартной реализацией КМОП.

Требования к содержанию отчета:

1) Исследованные схемы и их описания

2) Тексты входных файлов

3) Полученные путем моделирования электрические характеристики и функциональные диаграммы: средняя потребляемая за период мощность, задержки, функциональные диаграммы (зависимости выходного напряжения от входного).

4) Анализ результатов моделирования. Сравнение эффективности методик VT -, DT- и

MTCMOS.

5) Ответы на контрольные вопросы

6) Краткое заключение

Контрольные вопросы

1) Что такое эффект влияния подложки и каким образом он изменяет пороговое напряжение

МОП транзистора?

2) В чем заключается основная особенность DTCMOS схем?

3) В чем заключается основная особенность MTCMOS схем?

4) В чем заключается основная особенность VTCMOS схем?

5) Как изменяется ток утечки при уменьшении топологических размеров транзисторов?

6) Какова зависимость потребляемой мощности и задержек при от изменении топологических размеров транзисторов?

7) Какие еще методы снижения потребляемой мощности Вы знаете?

8) Почему при уменьшении топологических размеров возможно уменьшение напряжения

питания схемы?

Лабораторная работа № 2. Способы снижения динамической потребляемой мощности.

Метод clock gating

Цель работы:

1) ознакомление с механизмами, обуславливающими потребление энергии в динамическом

режиме работы КМОП схем.

6

2) реализация, средствами пакета Design Compiler САПР Synopsys, метода управления цепями синхронизации (clock gating) для снижения потребляемой мощности.

Лабораторные задания и порядок выполнения работы

В рамках работы необходимо:

1). Произвести настройку необходимых параметров в установочных файлах Synopsys DC.

2) Выполнить синтез HDL кода СФ-блока с использованием методики clock gating.

3) Получить файл результатов анализа схемы с управляемыми цепями синхронизации (clock

gating report).

4) Собрать комплект файлов необходимых для физического синтеза в IC Compiler.

Перед непосредственным выполнением лабораторной работы необходимо разработать HDL

описания СФ-блоков на языке Verilog. Функциональное назначение блока студент выбирает самостоятельно. Примерный уровень сложности - 1000 вентилей.

Теоретическая часть

До половины динамической мощности в МОП СБИС определяется цепями синхронизации. Когда логический элемент (например, D-триггер) не используется, изменение сигнала синхронизации

приводит к его постоянному переключению, что приводит к излишнему энергопотреблению.

Одним из самых распространённых методов решения проблемы большого энергопотребления заключается в отключении сигнала синхронизации в неработающих блоках, в иностранной

литературе данный метод получил название clock gating.

Методика clock gating нашла широкое применения в современных САПР для уменьшения потребляемой мощности разрабатываемых цифровых схем. Средства САПР Synopsys позволяют добавлять вентили отключения сигнала синхронизации при анализе RTL-описания или списка цепей после

первичной компиляции. Для реализации данной методики в САПР логического синтеза Synopsys

Design Compiler необходимо добавить специализированные директивы для RTL-модели СБИС. Эти

директивы указывают на необходимость анализа описания схемы и определения мест, где возможно

сократить энергопотребление за счет отключения сигнала синхронизации для блоков регистров.

Отметим, что реализация данной методики возможна на различных уровнях представления схемы. Во-первых, на уровне целого функционального блока, что позволяет достичь наибольшего снижения энергопотребления. Во-вторых, возможно отключение сигнала синхронизации для отдельного

регистра или блока регистров. Однако такой подход является эффективным тогда, когда разрядность

регистров больше трех. В-третьих, можно отключить сигнал синхронизации на уровне отдельной

ячейки. Данный подход используется при построении базовых элементов, например, блок регистров

может записывать данные только при изменении значения на шине данных. Причем использование

таких ячеек не вносит изменения в маршрут проектирования, правда приводит к росту площади кристалла, поскольку необходимо использовать специальные дополнительные ячейки.

7

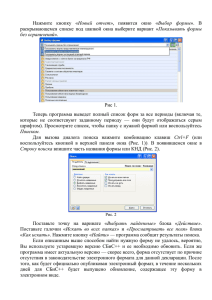

Рис.1. Отключение сигнала синхронизации

Сегодня большинство библиотек включает в свой состав специальные ячейки, которые позволяют синтезатору автоматически добавлять их в разрабатываемые схемы. Однако оптимальным

подходом с точки зрения снижения энергопотребления является комбинация автоматического

управления цепями синхронизации и определения отключаемых ячеек проектировщиком самостоятельно. Другим преимуществом использования данной методики в маршруте проектирования является то, что она позволяет упростить этап физического проектирования схемы, поскольку для

банков регистров исчезают обратные связи и, таким образом, упрощается топология кристалла.

Экспериментальная часть

Специальные директивы Synopsys DC для реализации метода clock gating:

set_clock_gating_style <-sequential_cell latch> <-minimum_bitwidth value>

<-control_point before|after> - данная команда позволяет определить параметры управления

цепями синхронизации;

insert_clock_gating - добавляет ячейки управления синхронизацией после первого этапа синтеза и перевода в представление GTECH. Для добавления ячеек после перевода в базис технологической библиотеки необходимо использовать ключ -gate_clock;

propagate_constraints -gate_clock - переносит временные ограничения с верхнего уровня

иерархии на данный уровень;

compile_ultra -gate_clock - автоматическое определение времен установки и удержания для

управляемого сигнала синхронизации.

report_clock_gating <-hier> <-ungated> - получения отчета с информацией о добавленных в

схему ячейках и изменении характеристик СБИС.

Далее может быть продолжен стандартный маршрут проектирования (uniquify).

Пример выполнения работы в Synopsys DC:

8

1) Выполнить начальную установку параметров для нормальной работы DC (файл

.synopsys_dc.setup)

2) Собрать комплект файлов с HDL описанием (.v or .vhdl) и проектными ограничениями

(.sdc)

3) Выполнить синтез в Synopsys DC. Использовать представленные выше директивы для реализации clock gating

4) Подготовить файлы для передачи данных на этап физического проектирования в IC

Compiler.

Образец скрипта для реализации методики clock gating в Synopsys DC:

analyze -library WORK -format verilog {<имя файла подблока 1> \ <имя файла подблока 2> \

… \ <имя файла подблока n>}

read_file -format verilog {<имя файла модуля верхнего уровня>}

source -echo <файл с проектными ограничениями>

set_clock_gating_registers -include_instances [all_registers -clock clock]

compile -exact_map -gate_clock

report_clock_gating

write -f verilog -h -out <имя выходного файла>

Обработка результатов

Сравнить функциональные диаграммы выходных сигналов с использованием методики clock

gating и без использования. Убедиться в функциональной работоспособности схемы. Сравнить

значения потребляемой мощности и быстродействия разработанной схемы, выполненного с использованием и без использования методики clock gating. Оценить потери в площади для реализации методики.

Требования к отчету

1) Исходный HDL код функционального блока на языке Verilog.

2) Скрипты для синтезатора, устанавливающих проектные ограничения.

3) Файлы с параметрами управления синхронизацией в функциональном блоке.

4) Полученные путем моделирования функциональные временные диаграммы.

5) Файлы отчета, включающие данные о задержках, потребляемой мощности и управлении

цепями синхронизации.

6) Анализ результатов моделирования. Сравнение по информации из файлов отчета параметров схемы (задержки, площадь и мощность).

7) Два варианта вентильного представления проекта - с управлением синхронизации и без него.

8) Ответы на контрольные вопросы

9) Краткое заключение

9

Контрольные вопросы

1) Что такое методика clock gating и как он влияет на параметры схемы?

2) Как реализуется методика clock gating на уровне всей системы?

3) Как реализуется методика clock gating на уровне функционального блока?

4) Как реализуется методика clock gating на уровне ячейки?

5) Как изменяется площадь схемы при использовании методика clock gating?

6) Как изменяются временные характеристики схемы при использовании методика clock gating?

7) Как изменяется энергопотребление схемы при использовании методика clock gating?

8) Какие еще методы снижения потребляемой мощности Вы знаете?

9) Возможно ли комбинация методики clock gating с другими методами уменьшения потребляемой мощности?

10) Какие директивы Synopsys для реализации методики clock gating вы знаете?

Лабораторная работа № 3. Основы энергетической оптимизации в пакете Cadence

Введение

Целью лабораторной работы является, изучить основные приемы работы в Conformal Low

Power (CLP) и оптимизации потребляемой мощности с последующей отладкой в среде CPF.

В данной лабораторной работе студент рассмотрит связь проектирования с потребляемой мощностью, выполнит оптимизацию в CPL на основе RTL описания, прозведет компиляцию проекта,

сборку проекта (elaborate) с последующей симуляцией проекта на Verilog и исправлением CPF.

Тестовые воздействия, как и испытуемые устройства (DUT) описаны на языке Verilog. DUT

содержит модуль контроля потребляемой мощности и 31-вых. КИХ (FIR) фильтр, как показано на

рисунке ниже.

10

Значение мощности / Контроль мощности

Требования показанные ниже будут использованы в первой и во второй части работы.

- КИХ фильтр (fir31) с возможностью отсечки

- Низкая изоляция активного операнда“dout”, Высокая изоляция активного операнда “ack_l”

- Удержание состояния в модуле Coefficient Register.

Выполнение моделирования потребляемой мощности

1. Часть 1. Подготовка моделирования потребляемой мощности. Имеется формат описания устройства в CPF. Для запуска моделирования, перейдите в директорию с шаблонами

“problem1/sim”. Для выполнения задачи наберите в терминале: “irun -f run.f”

Выполните командный скрипт restore.tcl для демонстрации результатов моделирования.

Моделирование потребляемой мощности выполнено с ошибками:

Описание устройства в формате CPF располагается в директории “cpf”. Инструкции для запуска CLP на описании RTL и CPF представлены в части 2.

11

Используя методику CLP, моделирование и Ваши инженерные способности - исправьте

ошибки процесса моделирования потребляемо мощности.

Опишите найденные проблемы и способы их устранения.

2. Запуск моделирования CLP на описании RTL и CPF.

Алгоритм CPL может быто выполнен из директории “problem1/clp”. Для выполнения наберите в терминале:

lec -lp -verify -do cpf_qual.do

После выполнения команды будет запушен графический интерфейс (GUI) CLP. Проанализируйте сообщения программы в окне ниже.

Также будет запушен Low Power Manager, как показано на рисунке ниже. Красные метки на

вкладках блоков устройства означают наличие ошибок. Проведите диагностику и устраните проблемы.

12

Ниже показан пример правильного функционирования устройства:

Лабораторная работа № 4. Современные методы энергетической оптимизации

в пакете Cadence

Усовершенствованные методы контроля потребляемой мощности

Введение

В данной лабораторной работе проводится моделирования потребляемой мощности для типовой системы на кристалле (SOC) используемой в беспроводных приложениях

Моделирование успешно выполняется без условий CPF, при моделировании направленном

на оптимизацию потребляемой мощности возникают ошибки.

13

Целью данной лабораторной работы является изучение основ использования методологии,

маршрута Conformal Low Power (CLP) и процесса моделирования мощности для исправления или

отладки CPF. В лабораторной работе студент исследует программный макет устройства и способы

контроля потребляемой мощности, выполнит методику программы CLP на описаниях RTL и CPF,

проводит крмпиляцию, сборку и моделирование проекта на языке Verilog.

Структурная схема

Структурная схема PFI SOC приведена на рисунке ниже:

Подсистема Цифровой Обработки Сигналов (DSP) обеспечивает работу Передающего и

Принимающего фильтров. Передающий и Принимающий фильтр (31-выводной КИХ фильтр)

идентичны друг другу и представлены на рисунке ниже.

В блоке Coefficient Register располагаются 16 регистров коэффициентов. Оба фильтра могут

быть выключены с целью снижения потребляемой мощности.

Модуль контроля мощности.Power Control Module (pcm).

Модуль контроля мощности (pcm) формирует сигналы изоляции операнда и сигналы отключения для КИХ фильтров. В пределах PCM, существуют два идентичных контролирующих блока

(power_control) используемые для формирования сигналов изоляции операнда и сигналов отключения КИХ фильтров.

14

Структурная схема блока представлена ниже:

Внутренняя Шина данных (ibus)

PFI SOC использует собственную шину известную как ”internal bus” или “ibus”. Шина ibus

используется для внутренних связей между Процессорной подсистемой, подсистемой DSP и модулем PCM. Таблица ниже показывает назначение сигналов ibus и их функции.

Фильтр коэффициентов загружается при помощи Write Operations по шине ibus, как для Передающего, так и для принимающего фильтров. Загрузка коэффициента фильтрации 0 показана на

рисунке ниже:

15

Модуль Контроля Мощности Power Control Module (PCM) и Сигналы Контроля Мощности

Модуль PCM располагается на шине ibus. Для данного блока, управление мощностью осуществляется посредством записи соответствующего операнда в регистр “power down” модуля

PCM. Втроеенное программное обеспечение на базе Пороцессорной подсистемы производит запись в регистр модуля PCM. Временные диаграммы работы приведены ниже:

Выполнение лабораторного задания

1. Conformal Low Power (CLP) - CPF Quality Checks

Для запуска CLP и выполнения процедуры CPF quality checking на основе RTL описания,

необходимо перейти в директорию cpl:

cd clp

lec -lp -verify -do cpf_qual.do

16

Если пакет CLP обнаружит ошибки описания, исправите их и повторите моделирование.

2. Low Power Simulation

Для выполнения процесса Low Power Simulation выполните следующие действия:

cd sim

irun -f run.f

С помощью пакета Simvision, выполните скрипт restore.tcl.svcf .

Моделирование выполненное без ошибок будет выглядеть как показано ниже:

17

Конспект лекций

Модуль 1. Энергопотребление цифровых схем.

В данном модуле будут рассмотрены вопросы энергопотребления цифровых схем. В первой

части будет проведен анализ причин потребления энергии цифровыми схемами в режиме ожидания. Мощность, потребляемая в этом режиме, получила название статической потребляемой мощности. Во второй части будут рассмотрены механизмы потребления энергии цифровыми схемами

в режиме переключения. Мощность, потребляемая в этом режиме, получила название динамической потребляемой мощности.

Лекция 1. МОП схема. Статическая потребляемая мощность.

При масштабировании субмикронной МОП-технологии появились проблемы, связанные с

увеличением динамической мощности, потребляемой МОП СБИС. С уменьшением проектных

норм до 90 нм статическая мощность, обусловленная токами утечек МОП транзисторов, также

значительно возрастает, а при технологических нормах 65 нм, становится соизмеримой с энергопотреблением в динамическом режиме. Эти проблемы привели к тому, что возникла необходимость в создании новых подходов к проектированию энергоэффективных высокопроизводительных МОП СБИС.

До недавнего времени проблема рассеивания мощности на кристалле стояла на втором

плане, тогда как на первом плане были такие критерии, как стоимость, площадь и временные ха18

рактеристики схемы. Однако при уменьшении технологических норм именно рассеиваемая мощность стала играть доминирующую роль.

Актуальность проблемы снижения потребляемой мощности в МОП СБИС обусловлена следующими причинами:

Расширение рынка портативных электронных устройств, питающихся от автономных источников питания, таких как батареи и аккумуляторы. Снижение энергопотребления даст возможность увеличить продолжительность времени работы электронного устройства без подзарядки, а

также уменьшить вес батарей или аккумуляторов.

Высокая стоимость используемых в настоящее время специальных подсистем охлаждения

СБИС. Результатом снижения энергопотребления может стать отсутствие необходимости в таких

подсистемах и, соответственно, уменьшение стоимости и габаритов микроэлектронных изделий.

Высокая стоимость теплоустойчивых корпусов СБИС. Снижение энергопотребления позволит использовать более дешевые корпуса.

Увеличение вероятности сбоя в работе СБИС, являющегося следствием перегрева схемы

из-за высокого энергопотребления. Снижение энергопотребления позволит повысить надежность

и долговечность СБИС.

Общая мощность, потребляемая кристаллом, складывается из динамической и статической

составляющей. Динамическая мощность - это мощность, которую потребляет устройство в активном режиме, т.е. при переключениях, когда сигналы меняют свои значения. Статическая мощность

- это мощность, потребляемая в том случае, когда устройство находится в режиме ожидания, переключения отсутствуют, и сигналы не меняют свои значения.

Рис.1. Уровень потребления мощности при масштабировании технологии

Рис.2. Источники потребляемой мощности в МОП

схемах

В статическом режиме отсутствуют переходные процессы, а потребление мощности вызвано

токами утечек через элементы СБИС. Теоретически, для идеального случая, в статике при отсутствии утечек токи должны полностью отсутствовать, а статическая мощность равняться нулю. Эта

19

ситуация практически осуществляется для относительно длинноканальных МОП транзисторов с

микронными топологическими нормами. Для субмикронных МОП транзисторов это утверждение

становится спорным, поскольку появляются утечки различного рода, а при переходе в наноразмерную область данное утверждение уже просто неверно, поскольку статическая мощность становится сравнима с динамической.

Существует три основные вида токов утечки (см. рис.3), в сумме составляющие общий ток

утечки Ileak: диодный ток утечки через обратно смещенные р-n переходы сток/исток-подложка, ток

через канал закрытого МОП транзистора (подпороговый ток) и туннельный ток через подзатворный диэлектрик.

Рис.3. Возникновение токов утечки в статическом состоянии

Сумма всех составляющих токов утечки - диодных токов, подпороговых токов и туннельных

токов через подзатворный диэлектрик, для средней СБИС составляет примерно 10 мкА, и напряжении питания 1 В приводит к тому, что потребляемая мощность составляет менее 10 мкВт. Эта

величина незначительна по сравнению с потреблением динамической мощности, но с совершенствованием технологии, увеличением степени интеграции и уменьшением топологических размеров вклад утечек в общее энергопотребление становится всё более существенным.

Лекция 2. Динамическая потребляемая мощность.

Причины потребления энергии в динамическом режиме работы СБИС по физической природе процессов можно разделить на два класса - протекание сквозных токов между шинами земли и

питания в КМОП структурах и заряд/разряд паразитных ёмкостей. Первый класс связан с переходом электрической энергии, обусловленной движением носителей заряда через инверсионные каналы n- и p- МОП транзисторов, в тепловую энергию, которая выделяется при протекании токов

через сопротивления тела каналов. Ко второму классу относятся потери энергии, возникающие

при накоплении заряда (или наоборот при рассасывании заряда) в ёмкостях элементов СБИС (см.

рис.4)

20

Рис.4. Схема инвертора при переключении из “0” в “1”

В динамическом режиме ряд величин, характеризующих состояние схемы (токи и напряжения), изменяются во времени. Можно выделить две группы процессов, служащих источником потребления динамической мощности: заряд/разряд ёмкостей транзисторов и сквозные токи (токи

короткого замыкания). Все элементы СБИС обладают определенной ёмкостью, и при изменении

напряжений на выводах элементов в этих ёмкостях происходит либо накопление, либо уменьшение заряда, что требует определённых затрат энергии и определяет величину потребляемой мощности. Эта составляющая потребляемой мощности зависит от интенсивности переходных процессов (частоты переключений), амплитуды изменения напряжений и величины самих ёмкостей.

В общем виде динамическая мощность (Pdyn), потребляемая вентилем, описывается следующим выражением:

Pdp = CL ∙ Vdd2 ∙ f ,

(1)

где CL - нагрузочная ёмкость вентиля; Vdd - напряжение питания; f - частота переключений.

Это выражение справедливо при определённых допущениях: входные ёмкости при переключении вентиля из “0” в “1” и из “1” в “0” в общем случае не равны, поэтому ёмкость должна быть

усреднена. Также необходимо, чтобы входной сигнал был периодическим, в противном случае

выражение для частоты должно быть более сложным для учёта всех составляющих непериодического сигнала. На рис.4 показана эквивалентная модель инвертора при переходе из “0” в “1”.

Строго говоря, ёмкость вентиля, участвующая в переключении и присутствующая в формуле

потребления мощности, состоит из нескольких компонент: ёмкость затворной области, ёмкости

межсоединений (металлическая или поликремневая разводка внутри вентиля) и барьерные ёмкости p-n переходов сток/исток-подложка МОП транзисторов.

Выражение 1 может быть применимо и к вычислению динамической мощности, потребляемой схемой из N вентилей. Для этого необходимо усреднить частоту переключений с учётом числа вентилей, переключающихся в единицу времени. Для этого используется коэффициент переключательной активности α (0 < α < 1), который показывает среднюю долю тактов, в которых

произошли переключения из “0” в “1” и из “1” в “0”. Использование подхода, связанного с тем

21

фактом, что не все вентили переключаются с одинаковой частотой, возможно только в схемах с

единой системой синхронизации. Иными словами, с помощью описанного метода можно учитывать различную частоту переключений вентиля (и, как следствие, различный вклад данного вентиля в общую ёмкость СБИС), только в том случае, если переключения всех вентилей синхронизируются одинаковым образом.

Вторым механизмом, который обуславливает потребление мощности в динамическом режиме работы, являются сквозные токи. Причиной их появления является наличие открытых последовательно соединенных n-канальных и p-канальных МОП транзисторов, подключенных к шинам

«земли» и «питания». Например, эта ситуация возникает в зоне переключения КМОП вентиля.

Сквозные токи короткого замыкания возникают, когда на выходе вентиля начинается логический переход, в то время как вход еще находится в процессе переключения. Обычно это происходит в тех случаях, когда время нарастания/спада на входе больше времени нарастания/спада на

выходе. В идеальном случае транзисторы изменяют состояние моментально, мгновенно включаясь

и выключаясь, при этом отсутствует резистивная связь между шинами «земли» и «питания». Однако для реальных схем входной сигнал имеет конечное время переключения и такая связь присутствует.

Рис.5. Возникновение сквозных токов

На рис.5 показан механизм возникновения тока короткого замыкания в тот момент, когда в

инверторе открыты оба транзистора и через них протекает ток ISC.

Для КМОП - инвертора мощность сквозных токов (Pdp) можно представить в следующем виде:

Pdp = Csc ∙ Vdd2 ∙ f ,

(2)

где Csc - эффективная емкость; Vdd - напряжение питания; f - тактовая частота.

Величина данной составляющей в основном зависит от соотношения фронтов переключения

входа и выхода. При согласованных (одинаковых) фронтах данная составляющая может быть минимизирована и составляет ~ 10% от всей динамической мощности. Если нагрузочная емкость мала, то основной составляющей динамической мощности являются мощность сквозных токов, а для

очень больших нагрузочных емкостей вся энергия тратится на перезарядку емкостей.

22

Модуль 2. Способы снижения энергопотребления I

В данном модуле будет рассмотрено общие подходы к снижению статической и динамической составляющей мощности, потребляемой цифровыми схемами.

Лекция 3. Способы снижения статической потребляемой мощности.

Потребление мощности в статическом режиме работы цифровых схем обусловлено токами

утечки. При относительно больших топологических нормах утечки в МОП-структурах пренебрежимо малы и статическая мощность практически равняется нулю. Для субмикронных размеров

утечки становятся достаточно существенными, в связи с чем появляется статическая составляющая потребляемой мощности. Особенно остро проблема уменьшения статической мощности встаёт при дальнейшем уменьшении топологических размеров элементов СБИС, когда эффекты преодоления носителями зарядов потенциальных барьеров начинают играть все большую роль.

Данная проблема - основное препятствие, которое мешает эффективно использовать преимущества, возникающие на пути дальнейшего уменьшения размеров элементов ИС.

Как было показано в предыдущих лекциях существует три основные вида токов утечки, в

сумме составляющих общий ток утечки Ileak: это ток утечки через обратно смещенный р-n переход

сток/исток-подложка, подпороговый ток и туннельный ток через подзатворный диэлектрик.

Выражение для мощности токов утечки (Pleak) имеет следующий вид:

Pleak = Ileak · Vdd ,

(3)

где Ileak - суммарный ток утечки; Vdd - напряжение питания.

Ток утечки на p-n переходе сток/исток-подложка возникает при подаче на сток высокого потенциала, при этом, что на затворе нулевой потенциал и транзистор закрыт. Другими словами, на

диоде сток-подложка возникает обратное смещение, приводящее к протеканию тока утечки

(начального тока p-n перехода).

Рассмотрим обычный КМОП инвертор. В случае, когда на входе инвертора низкий уровень

напряжения, на выходе устанавливается высокий уровень, при этом - р-МОП транзистор открыт,

n-МОП транзистор - закрыт, выход соединён с питанием через открытый канал р-МОП транзистора. На стоке n-МОП транзистора в этом случае устанавливается потенциал, равный напряжению

питания Vdd. Так как транзистор закрыт, диод сток-подложка оказывается обратно смещённым и

через него возникает ток утечки (ILD), который приблизительно равен:

ILD= AD JSD ,

где AD - площадь p-n перехода стоковой области; JSD - плотность тока утечки.

23

(4)

Максимум тока диода достигается при относительно небольшом обратном смещении, далее

ток утечки становится практически независимым от напряжения смещения. Плотность тока утечки

определяется технологией и зависит от температуры.

Подпороговая утечка возникает при тех же условиях, что и диодная. В приведенном выше

инверторе, n-МОП транзистор закрыт, но, даже при напряжении на затворе равном нулю, ток продолжает течь по каналу из-за наличия напряжения сток-исток, равного напряжению питания Vdd.

При масштабировании топологических размеров и уменьшении порогового напряжения подпороговый ток утечки закрытого транзистора увеличивается.

Подпороговый ток (ISUB) зависит от подвижности носителей заряда (μ), удельной емкости

области затвора (COX), ширины (W) и длины (L) канала, температурного потенциала (φT), напряжений затвор-исток (VGS), сток-исток (VDS) и порогового напряжения (VTH). Величина подпорогового

тока определяется следующим выражением:

I SUB

W

COX

e

L

2

T

VGS VTH

nT

VDS

1 e T

(5)

Туннельные токи возникают из-за эффекта туннелирования подвижных носителей заряда через тонкий подзатворный диэлектрик МОП-транзистора. Например, для технологии 90 нм подзатворный диэлектрик имеет толщину всего в несколько атомных слоев (~ 1.2 нм), дальнейшее его

уменьшение приводит к значительным утечкам за счет туннельного тока (проявление кван-товых

эффектов) и, как следствие, к увеличению потребления энергии. Обычно туннельные токи уменьшают за счет технологических приемов и увеличения толщины подзавторного окисла (tOX).

Рассмотрим методы снижения токов утечки на схемотехническом уровне. На данном уровне

основным подходом к снижению статической составляющей мощности является управление пороговым напряжением МОП-транзисторов в зависимости от режима работы схемы.

Одним из эффективных методов построения энергоэффективных МОП СБИС является использование технологии VTCMOS. Используя эффект влияния подложки можно изменять пороговое напряжение VTH, что позволяет получить высокое VTH в режиме ожидания и низкое VTH в активном режиме для транзистора.

На рис.6(а) приведена модификация электрической схемы КМОП-инвертора с применением

технологии VTCMOS. Во время активного режима на подложку p-канального МОП транзистора подается напряжение Vdd, а на подложку n-канального МОП транзистора - нулевое напряжение, обеспечивая низкое эффективное пороговое напряжение, и следовательно высокое быстродействие. Во время режима ожидания на подложку p- и n-канальных МОП транзисторов подается напряжение 2Vdd и Vdd соответственно, эффективное пороговое напряжение увеличивается, уменьшая тем самым ток

утечки. К недостаткам этой технологии можно отнести дополнительную схему управления смещением подложки.

24

а

б

в

Рис.6. Схемотехнические решения для снижения статической мощности:

а - VTCMOS; б - DTCMOS; в - MTCMOS

В схеме с динамическим управлением порогового напряжения (DTCMOS) достигается автоматическое изменение пороговых напряжений транзисторов посредством соединения дополнительных управляющих областей с входами. На рис. 6(б). приведена электрическая схема логического вентиля, реализующая эту идею путем непосредственного соединения подложки с затвором.

Методика построения вентиля с несколькими пороговыми напряжениями (MTCMOS) заключается в отключении вентилей внутри функционального блока от шин земли/питания с помощью специальных цепей, в те моменты времени, когда их работа не требуется.

Транзистор с высоким пороговым напряжением VTH (транзистор Т3 на рис. 6(в)) отключает

схему в те моменты, когда она не должна выполнять какие-либо операции. В этот период, за счет

подачи на вход транзистора sleep-сигнала, МОП транзистор Т3 закрыт. Sleep-режим работы обеспечивает уменьшение статической составляющей рассеиваемой мощности, которая может быть

довольно значительна из-за больших токов утечек у быстродействующих транзисторов с малым

значением VTH .

Лекция 4. Способы снижения статической и динамической потребляемой мощности. Обзор

Ниже будут рассмотрены основные методики и подходы, нашедшие практическое применения при проектировании энергоэффективных цифровых СБИС и СнК. Данные методики могут

быть реализованными в САПР с использованием специальных пакетов, но при этом от разработчика СБИС может потребоваться изменение маршрута проектирования.

Одним из способов снижения потребляемой мощности при создании энергоэффективных

блоков является использование, транзисторов с разной шириной затвора. Для вычисления оптимальных ширин транзисторов, с точки зрения энергоэффективности, существует ряд моделей.

25

Наиболее распространенными являются модели, основанные на простых RC-цепях и подходе

Logical Effort, для которых существует несколько эмпирических правил, позволяющих получить

оптимальное энергопотребление.

На схемотехническом уровне можно выделить несколько вариантов построения энергоэффективных решений: статическая КМОП логика, динамическая логика, логика на проходных транзисторах, адиабатическая логика, псевдо n-МОП логика, схемы с переменным пороговым напряжением, схемы с дополнительным источником питания, использование управления по

дополнительным затворам.

а

б

в

Рис.7. Схемотехнические решения базовых элементов:

а - КМОП-инвертор; б - Проходной вентиль; в - Динамическая логика

Одним из наиболее распространенных и эффективных методов уменьшения потребляемой

мощности МОП СБИС является уменьшение напряжения питания, при этом для получения оптимального энергоэффективного решения необходимо уменьшать и пороговое напряжение.

Для определения оптимальной величины напряжения питания может быть использована модель для мощности системы (PN) с фиксированной производительностью в зависимости от напряжения питания и степени параллелизма:

PN N Cref V 2 ( Fref / N ) Cip V 2 ( Fref / N ) Cint V 2 Fref ,

(6)

где Fref - номинальная тактовая частота; V - напряжение питания; N - число параллельных процессов;

Сref - емкость одного процессора; Сip - емкость межпроцессорных связей; Сint - емкость интерфейса.

При разработке цифровых СБИС субмикронных размеров, для которых основной составляющей является динамическая мощность, используются методики, связанные с уменьшением

напряжения питания на схемотехническом и функционально-логическом уровнях. Эта методика

является достаточно эффективной, поскольку при уменьшении напряжения питания квадратично

снижается динамическая мощность.

26

Реализация данного подхода возможна с использованием специализированных библиотек с

пониженным напряжением питания (low-voltage library), которые применяются в процессе логического синтеза для снижения потребляемой мощности конечного устройства.

Реализация метода снижения напряжения питания на системном уровне называется управлением питанием и предполагает отключение крупных функциональных блоков с помощью системного контроллера питания в те моменты, когда их работа не требуется. По характеру реализации

метод управления питанием подразделяется на два типа: динамический и статический.

Динамическое управление питанием предполагает выборочное отключение блоков СБИС,

которые не нужны для выполнения текущих операций. Например, можно отключить блок вычислений с плавающей запятой при выполнении целочисленных операций, что никак не повлияет на

быстродействие.

При статическом управлении питанием для схемы вводится специальный режим ожидания.

В этом режиме, при отсутствии запросов от системы, все блоки схемы кроме блоков памяти, которые хранят необходимые данные для перехода в активный режим, отключаются.

Также для уменьшения динамической мощности используется ряд методик, связанных с уменьшением переключательной активности. Эффективность данных методик обусловлена прямо пропорциональной зависимостью между динамической мощностью и переключательной активностью.

Отметим, что существенная доля (до 50%) динамической мощности в СБИС определяется

цепями синхронизации. Когда логический элемент (например, D-триггер) не используется, изменение сигнала синхронизации приводит к его постоянному переключению, что приводит к излишнему энергопотреблению.

Самый распространённый метод решения проблемы излишнего энергопотребления за счет

управления цепями синхронизации заключается в отключении тактового сигнала в неработающих

блоках. Данная методика получила название clock gating. Реализация данной методики возможна

на различных уровнях представления схемы. Во-первых, на уровне целого функционального блока, что позволяет достичь наибольшего уровня снижения энергопотребления. Во-вторых, возможно отключение сигнала синхронизации для отдельного регистра или блока регистров. Однако такой подход является эффективным, когда разрядность регистров больше трех. В-третьих, можно

отключить сигнал синхронизации на уровне отдельной ячейки.

Для нанометровых технологий получила широкое распространение реализация методики

MTCMOS на уровне функциональных блоков - power gating. Внутреннее управление питанием

осуществляется посредством специального контроллера питания и цепей отключения функциональных блоков от шин питания. Правда, для реализации методики power gating необходимы следующие дополнительные функциональные блоки: цепи отключения питания, контроллер питания,

изолирующие ячейки, блоки хранения и восстановления данных.

27

Модуль 3. Методы снижения рассеиваемой мощности на этапе проектирования блоков

высокопроизводительных микропроцессоров

Уменьшение проектных норм при разработке интегральных схем приводит к значительному

повышению рассеиваемой мощности. Это происходит из-за возрастания рабочей частоты, снижения порогового напряжения, увеличения плотности элементов на кристалле из-за усложнения схемотехнической составляющей устройств. Особенно остро эта проблема встает при переходе к проектным нормам 90нм и ниже.

Формула расчета мощности представлена ниже, первое слагаемое представляет собой динамическую мощность, второе мощность утечек, или статическую мощность:

P pt * fCLK * CL *VDD 2

VTH

I0

WT *10 S *VDD ,

W0

где pt - вероятность переключения, f CLK - рабочая частота, С L - емкость нагрузки, VDD - напряжение питания, VTH - пороговое напряжение, S - подпороговый коэффициент (обычно 0.1

V/decade), остальные параметры постоянны и определяются схемой, топологией и параметрами

устройства.

Статическая мощность - это мощность, рассеиваемая на элементе, когда он находится в статическом состоянии, т. е. не переключается. Статическая мощность рассеивается несколькими путями. Самый большой процент статической мощности является результатом подпороговых утечек

исток-сток, которые являются причиной уменьшения пороговых напряжений. Статическая мощность также рассеивается, когда ток протекает между диффузионными слоями и подложкой. По

этой причине статическую мощность называют часто мощностью утечек.

Динамическая мощность - это мощность, которая рассеивается, когда схема активна. Схема

активна в любое время, когда напряжения в цепях изменяется из-за какого-либо воздействия на

схему. Так как напряжение на входе может изменяться без какого-либо определенного отклика на

выходе схемы, то динамическая мощность может рассеиваться даже, когда на выходе не произошло логического изменения состояния.

Динамическая мощность схемы состоит из двух видов мощности: мощности переключения и

внутренней мощности.

Мощность переключения ячейки - это мощность, рассеиваемая с зарядкой и разрядкой

нагрузочной емкости на выходе ячейки. Общая нагрузочная емкость на выходе ячейки - это сумма

емкостей связей и элементов на выходе. Общая мощность переключения рассчитывается по следующей формуле:

28

Pc

V 2 dd

2

C

Loadi

TRi ,

nets ( i )

где Pc - мощность переключения схемы, TRi - коэффициент переключений на шине i (число в секунду), Vdd -напряжение питания, CLoad - общая нагрузочная емкость шины i.

Так как эта зарядка и разрядка являются результатом смены логического состояния на выходе ячейки, то мощность переключения возрастает с ростом числа смены логических состояний.

Отсюда, мощность переключения ячейки является функцией и от общей нагрузочной емкости на

выходе ячейки, и от числа смены логического состояния.

Внутренняя мощность - это любой вид мощности, рассеиваемый внутри ячейки. Во время

переключения схема рассеивает внутреннюю мощность из-за зарядки и разрядки всех существующих емкостей внутри ячейки. Внутренняя мощность комбинационной ячейки, представленной

на рисунке 1, рассчитывается по следующей формуле:

Pint

E{i Z} PW TR _ Z ,

i A, B

где E{i Z } - это внутренняя энергия для выхода Z, являющаяся функцией от выходной емкости

нагрузки, напряжения и времени изменения входного состояния, PW-весовой коэффициент времени изменения состояния для выхода, а TR_Z-коэффициент переключения выхода.

Рис.1. Комбинационная ячейка

Внутренняя мощность включает в себя также мощность, рассеиваемую моментально в короткой

цепи между P и N канальными транзисторами вентиля, называемую мощностью короткой цепи.

Разработчики программного обеспечения предлагают несколько методов уменьшения рассеиваемой мощности. Для снижения динамической составляющей используются методы clock

gating, operand isolation, gate level оптимизация, различное напряжение питания для некоторых

блоков схемы (multi-Vdd), для понижения значения статической составляющей предлагаются методы power gating, использование элементов с различными пороговыми напряжениями [1].

Суть метода clock gating состоит в том, что используются специальные элементы в цепи сигнала синхронизации. Их задача состоит в том, чтобы пропускать сигнал синхронизации по условию. Возможности введения clock gating могут быть найдены в RTL-коде, если существуют назначения по условию, то есть код выглядит, как if(co) out<=in .

29

На рис.2 представлена схема, соответствующая этому описанию и переход к аналогичной

схеме с установлением сигнала clock по условию без изменения функциональности. Таким образом, с использованием этого метода сохранение динамической мощности может достигать 25%.

Рис.2. Переход к схеме с использованием сигнала clock по условию

Следующий метод уменьшения мощности - это operand isolation метод. В проекте, нагруженном путями данных, сложные комбинационные схемы могут приводить к большому потреблению

мощности. Если на выходе схемы нет условия, по которому этот выход выдается, то operand

isolation метод может уменьшить динамическую мощность с помощью добавления изоляционной

логики (AND или OR) в соответствии с контрольным сигналом для сохранения значений входов.

Следовательно, постоянство на входах переносится сквозь схему и не вызывает лишних переключений [2]. Пример этого метода показан на рис.3.