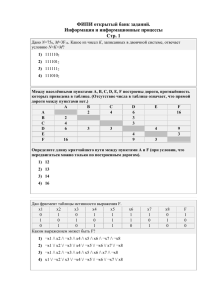

2. RLL – кодирование информации на магнитном носителе

реклама

Билет № 14 1. Суперскалярные процессоры с аппаратным механизмом выборки несвязных команд с памяти и параллельном запуском их на исполнение Было в ответах: В аппаратуру процессора закладываются средства, позволяющие одновременно выполнять две или более скалярные операции, т. е. команды обработки пары чисел. Суперскалярная архитектура базируется на многофункциональном параллелизме и позволяет увеличить производительность компьютера пропорционально числу одновременно выполняемых операций. Реализация суперскалярной обработки заключается в чисто аппаратном механизме выборки из буфера инструкций несвязанных команд и параллельном запуске их на исполнение. Суперскалярная аппаратура динамически строит план вычислений на основе последовательного кода программ. Хотя такой подход и увеличивает сложность физической реализации, скалярный процессор создает план, используя преимущества тех факторов, которые могут быть определены только во время выполнения. Этот метод хорош тем, что он «прозрачен» для программиста, составление программ для подобных процессоров не требует никаких специальных усилий, ответственность за параллельное выполнение операций возлагается в основном на аппаратные средства. Суперскалярная обработка широко используется в современных процессорах корпораций Intel, Advanced Micro Devices (AMD), International Business Machines (IBM), Sun Microsystems и др. Интернет (мое мнение, более правильно) Смысл суперскалярной обработки - наличие в аппаратуре средств, позволяющих одновременно выполнять две и более скалярных операций, т.е. команд обработки пары чисел. В самом деле, суть этого метода довольно проста: имеется в виду дублирование устройств процессора. Так например, Pentium имеет два конвейера выполнения команд При этом существуют различные способы реализации суперскалярной обработки. Первый способ чаще всего применяется в RISC-процессорах и заключается в чисто аппаратном механизме выборки из буфера инструкций (или кэша команд) несвязанных команд и параллельном запуске их на исполнение. Обычно процессор выполняет две несвязанные команды одновременно, как например, в процессорах DEC серии Alpha. Этот метод хорош тем, что он "прозрачен" для программиста составление программ для подобных процессоров не требует никаких специальных усилий, ответственность за параллельное выполнение операций возлагается в основном на аппаратные средства. Второй способ реализации суперскалярной обработки заключается в кардинальной перестройке всего процесса трансляции и исполнения программ. Уже на этапе подготовки программы компилятор группирует не связанные операции в пакеты, содержимое которых строго соответствует структуре процессора. Например, если процессор содержит функционально независимые устройства сложения, умножения, сдвига и деления, то максимум, что компилятор может "уложить" в один пакет - это четыре разнотипные операции: сложение, умножение, сдвиг и деление. Сформированные пакеты операций преобразуются компилятором в командные слова. До сих пор мы с вами рассматривали возможности увеличения производительности вычислительной системы на основе параллелизма на уровне команд. При этом к системе предъявлялись следующие требования: все обычные команды непосредственно выполняются аппаратным обеспечением, они не интерпретируются микрокомандами, устранение уровня интерпретации обеспечивает высокую скорость выполнения большинства команд; компьютер должен приступать к одновременному выполнению большого числа команд (при этом не имеет значения сколько времени занимает само выполнение этих команд); команды должны легко декодироваться (количество вызываемых команд в секунду зависит от процесса декодирования), для этого, например, используются регулярные команды с фиксированной длиной и небольшим количеством полей; к памяти должны обращаться только команды загрузки и сохранения (операнды для большинства команд берутся из регистров и возвращаются туда же), понятно, что это требование выдвигает необходимость иметь большое количество регистров. Недостатком суперскалярных микропроцессоров является необходимость синхронного продвижения команд в каждом из конвейеров. К тому же, как мы уже отмечали, кроме параллелизма на уровне команд существует параллелизм на уровне данных, реализация этого вида параллелизма требует применения многопроцессорной архитектуры. 2. RLL – кодирование информации на магнитном носителе Сегодня наиболее популярен метод кодирования с ограничением длины поля записи (Run Length Limited — RLL). Он позволяет разместить на диске в полтора раза больше информации, чем при записи по методу MFM, и в три раза больше, чем при FMкодировании. При использовании этого метода происходит кодирование не отдельных битов, а целых групп, в результате чего создаются определенные последовательности зон смены знака. Комбинирование в эти последовательности сигналов данных и синхронизации позволило повысить частоту синхронизации, сохранив то же базовое расстояние между зонами смены знака на магнитном носителе. Как уже отмечалось, при записи по методу RLL одновременно кодируются целые группы битов. Термин Run Length Limited (с ограничением длины пробега) составлен из названий двух основных параметров, которыми являются минимальное (длина пробега) и максимальное (предел пробега) число ячеек перехода, которые можно расположить между двумя зонами смены знака. Изменяя эти параметры, можно получать различные методы кодирования RLL-кодирование было шагом вперед по сравнению с MFM-кодированием. Этот метод кодирования рассматривает группы из нескольких бит, вместо рассмотрения одного бита в один промежуток времени. Идея кодирования состоит в том, чтобы смешивать клоковые смены полярности и смены полярности данных, чтобы допустить более плотную запись на поверхность магнитной пластины. Два параметра, описывающих RLL есть run length и run limit (отсюда и следует имя данного семейства кодирующих схем). Слово run здесь относится к последовательности записываемой информации без смены полярности. Параметр run length — это минимальная длина между двумя сменами полярности, в то время как run limit — это максимальная длина без смены полярности. Как и было сказано ранее, длина между двумя сменами полярности не может быть слишком длинной, иначе у нас потеряется синхронизация бит. Конкретная схема кодирования пишется как RLL(x,y) или x,y RLL, где x это run length, а y это run limit. Наиболее часто встречающаяся схема кодирования информации на накопителях это RLL(1,7) и RLL(2,7). Для того чтобы произвести кодирование, нужно иметь некий словарь, ставящий в соответствие входные данные выходным, давайте посмотрим на данный словарь в случае 2,7 RLL: Битовая последовательность Кодированная последовательность Количество смен полярности на бит Вероятность встречи в случайном потоке данных 11 RNNN 1/2 25% 10 NRNN 1/2 25% 011 NNRNNN 1/3 12.5% 010 RNNRNN 2/3 12.5% 000 NNNRNN 1/3 12.5% 0010 NNRNNRNN 2/4 6.25% 0011 NNNNRNNN 1/4 6.25% 0.4635 100% Взвешенное среднее Для примера, возьмем следующую последовательность бит: 10001111 (0х8Fh), эта последовательность будет представлена контроллером, как 10-0011011 и закодирована как NRNN-NNNNRNNN-RNNN. Следует заметить, что в данной схеме кодирования, каждая кодируемая последовательность из словаря оканчивается как NN, отсюда и видно, что минимальная длина между двумя сменами полярности равна 2. Максимальная длина, равная 7, будет достигаться в случае кодирования двух последовательностей 0011-0011. Сравнивая эту таблицу с такими же для FM и MFM, можно увидеть несколько интересных вещей. Наблюдается увеличивающаяся сложность кодирования: используется 7 различных последовательностей, и одновременно рассматривается до 4 бит. Среднее количество смен полярности на один бит равно 0.4635 или примерно 0.5. Это примерно одна треть от FM и примерно две трети от MFM. Так что, по сравнению с FMкодированием, мы можем записать втрое больше информации на один и тот же участок поверхности.